定时信号产生器

文献发布时间:2024-04-18 19:48:15

技术领域

本发明是涉及一种定时信号产生器,特别是指一种能校正定时信号的脉宽的定时信号产生器。

背景技术

在模拟电路中,模拟信号的值可以连续变化,在时间和值的幅度上都几乎没有限制,基本上可以取任何实数值,输入与输出也呈线性变化。所以在模拟电路中,电压和电流可直接用来进行控制对象,例如家用电器设备中的音量开关控制、采用卤素灯泡灯具的亮度控制等。但模拟电路有诸多的问题,例如控制信号容易随时间漂移,难以调节,功耗大,易受噪声和环境干扰等等。

与模拟电路不同,数字电路是在预先确定的范围内取值,在任何时刻,其输出只可能为ON和OFF两种状态,所以电压或电流会通路和断路方式的重复脉波序列加载到模拟负载。定时信号产生器是一种用于产生具有可调节时序的精确时钟信号的电路,为各种数字电路提供运作所需的“心跳”信号,可广泛应用于电子仪器和晶片系统,如晶片测试仪、脉宽调变产生器、逻辑分析器、示波器和时间数字转换器。以个人电脑为例,每套系统都会使用一或两套时钟产生器提供十多组参考信号,用来控制与调节处理速度、存储器存取、串流媒体、网络传输,以及无线通信等作业。定时信号产生器的应用现已超过电脑的范畴,为绝大多数的电子设备提供参考时钟计时,包括由局端的电信交换器,一直涵盖到住家的电视游乐器与数字相机。

随着集成电路技术的进步,定时信号产生器可以与其他模拟电路和数字电路结合在同一晶片内。然而,当定时信号产生器所产生的定时信号经过外部电路后,定时信号可能会因各种电路运作效应产生延迟或形变,造成定时信号的脉宽与预设不同。现今的高速电路运作时长皆为纳秒级距,定时信号的延迟或形变可能导致晶片内部电路不同步及进而引起其它误差。

发明内容

实施例提供一种定时信号产生器(timing generator),包含第一电流源、第一开关、第二电流源、第二开关、第三开关、电容、定时信号合成器、及时间差提取器。第一电流源用以根据输入电压产生第一电流。第一开关包含第一端耦接于第一电流源,第二端耦接于充电端,及控制端用以接收充电信号。第二电流源用以根据输入电压产生第二电流。第二开关包含第一端耦接于第二电流源,第二端耦接于充电端,及控制端用以接收时差信号。第三开关包含第一端耦接于充电端,第二端耦接于接地端,及控制端用以接收重置信号。电容耦接于充电端与接地端之间。信号合成器耦接于充电端,用以根据充电电压及参考电压产生定时信号。时间差提取器耦接于信号合成器及第二开关的控制端,用以根据定时信号及时差定时信号产生时差信号。

实施例提供另一种定时信号产生器,包含第一电流源、第一开关、第二开关、第二电流源、第三开关、第四开关、第一电容、第二电容、定时信号合成器及时间差提取器。第一电流源用以根据输入电压产生第一电流。第一开关包含第一端耦接于第一电流源,第二端耦接于充电端,及控制端用以接收充电信号。第二开关包含第一端耦接于偏压端,第二端,及控制端用以接收时差信号。第二电流源耦接于第二开关的第二端用以根据输入电压产生第二电流。第三开关包含第一端耦接于充电端,第二端耦接于接地端,及控制端用以接收重置信号。第四开关包含第一端,第二端耦接于偏压端,及控制端用以接收重置信号。第一电容耦接于充电端与接地端之间。第二电容耦接于偏压端,并用以接收参考电压。信号合成器耦接于充电端,用以根据充电电压及偏移参考电压产生定时信号。时间差提取器耦接于信号合成器及第二开关的控制端,用以根据定时信号及时差定时信号产生时差信号。

附图说明

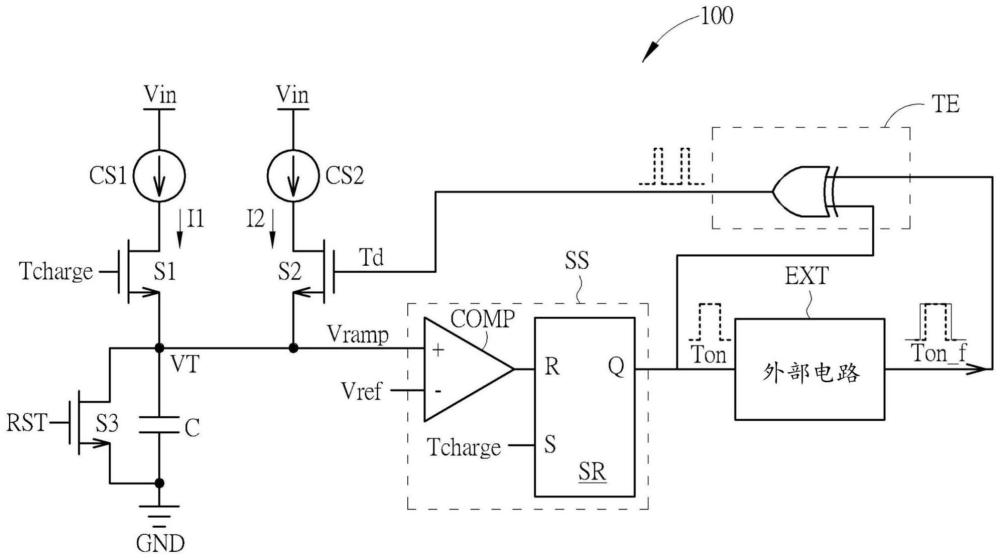

第1图是实施例的定时信号产生器的示意图。

第2图是第1图实施例的定时信号产生器的操作信号时序图。

第3图是另一实施例的定时信号产生器的示意图。

第4图是第3图实施例的定时信号产生器的操作信号时序图。

第5图是另一实施例的定时信号产生器的示意图。

第6图是第5图实施例的定时信号产生器的操作信号时序图。

第7图是另一实施例的定时信号产生器的示意图。

第8图是第7图实施例的定时信号产生器的操作信号时序图。

第9图是另一实施例的定时信号产生器的示意图。

第10图是第9图实施例的定时信号产生器的操作信号时序图。

第11图是另一实施例的定时信号产生器的示意图。

第12图是第11图实施例的定时信号产生器的操作信号时序图。

第13图是另一实施例的定时信号产生器的示意图。

第14图是第13图实施例的定时信号产生器的操作信号时序图。

具体实施方式

图示的架构、元件数量、层数、位置分布、比例等仅为举例,以助说明及理解实施例,而非用以限制实施例的样态与范围。本文中若有提及第一、第二等序数,仅为用以区分相异元件,而非限制先后或重要性。

本公开通篇说明书与权利要求中会使用某些词汇来指称特定元件。本领域技术人员应理解,制造商可能会以不同的名称来指称相同的元件。本文并不意在区分那些功能相同但名称不同的元件。在说明书与权利要求书中,“具有”与“包括”等词为开放式词语,因此其应被解释为“包括但不限定为…”之意。

第1图是实施例的定时信号产生器(timing generator)10的示意图。包含第一电流源(current source)CS1、第一开关S1、第二开关S2、电容C及信号合成器(signalsynthesizer)SS。第一电流源CS1用以根据输入电压Vin产生第一电流I1。第一开关S1包含第一端耦接于第一电流源CS1,第二端耦接于充电端VT,及控制端用以接收充电信号Tcharge。电容C耦接于充电端VT与接地端GND之间。信号合成器SS用以根据充电电压Vramp及参考电压Vref产生定时信号Ton。信号合成器SS包含比较器(comparator)COMP及锁存器(latch)SR。比较器COMP包含负输入端用以接收参考电压Vref,正输入端耦接于充电端VT,用以接收充电电压Vramp。锁存器SR包含设置端S用以接收充电信号Tcharge,重置端R耦接于比较器COMP的输出端,及输出端Q用以输出定时信号Ton。当定时信号Ton经过外部电路EXT之时,定时信号Ton可能会因各种电路运作效应产生延迟或形变,造成定时信号Ton的脉宽(pulse width)与预设脉宽不同,其结果在实施例中称为时差定时信号Ton_f。定时信号Ton的传输延迟可能使时差定时信号Ton_f的下降缘落后于定时信号Ton的下降缘,而定时信号Ton的启动延迟可能使定时信号Ton的上升缘落后于时差定时信号Ton_f的上升缘。

请参考第1图及第2图。第2图是第1图实施例的定时信号产生器10的操作信号时序图。在时间t1至t2之间,充电信号Tcharge为低电平(例如0V),使第一开关S1截止。充电电压Vramp电平低于参考电压Vref的电平(例如5V),使比较器COMP输出低电平信号。锁存器SR同时接收低电平的充电信号Tcharge及低电平的比较器COMP输出信号,使输出端Q输出低电平的定时信号Ton(例如0V)。当定时信号Ton经过外部电路EXT之时,定时信号Ton可能会因各种电路运作效应产生延迟或形变,造成定时信号Ton的脉宽与预设脉宽不同,使得在时间t1至t2之间的时差定时信号Ton_f就可能为高电平。

在时间t2至t3之间,充电信号Tcharge升至高电平,高电平的充电信号Tcharge使第一开关S1导通,第一电流源CS1开始以第一电流I1对电容C充电,使充电电压Vramp持续上升。锁存器SR同时接收高电平的充电信号Tcharge及低电平的比较器COMP输出信号,使输出端Q输出的定时信号Ton升至高电平(例如5V)。

在时间t3,充电电压Vramp达到参考电压Vref的电平,比较器COMP的输出信号升为高电平,同时充电信号Tcharge降为低电平。锁存器SR同时接收低电平的充电信号Tcharge及高电平的比较器COMP的输出信号,使输出端Q输出的定时信号Ton降至低电平。在理想情况下,充电信号Tcharge的脉宽实质上等于定时信号Ton的脉宽。此时,重置信号RST(为振幅快速暂态变化的脉冲信号)启动,导通第二开关S2一段很短的时间,释放在充电端VT累积的充电电压Vramp,使充电电压Vramp快速降至低电平。然而,在时间t3至t4之间,定时信号Ton为低电平,而时差定时信号Ton_f就可能因各种电路运作效应产生延迟而维持高电平,使得晶片内部电路不同步及进而引起其它误差,因此可藉由下述实施例的校正机制使时差定时信号Ton_f的脉宽回归至预设的定时信号Ton的脉宽。

第3图是实施例的定时信号产生器(timing generator)100的示意图。定时信号产生器100包含第一电流源CS1、第一开关S1、第二电流源CS2、第二开关S2、第三开关S3、电容C、比较器COMP、及时间差提取器TE。第一电流源CS1用以根据输入电压Vin产生第一电流I1。第一开关S1包含第一端耦接于第一电流源CS1,第二端耦接于充电端VT,及控制端用以接收充电信号Tcharge。第二电流源CS2用以根据输入电压Vin产生第二电流I2。第二开关S2包含第一端耦接于第二电流源CS2,第二端耦接于充电端VT,及控制端用以接收时差信号Td。第三开关S3包含第一端耦接于充电端VT,第二端耦接于接地端GND,及控制端用以接收重置信号RST。电容C耦接于充电端VT与接地端GND之间。信号合成器SS包含比较器COMP及锁存器SR。比较器COMP包含负输入端用以接收参考电压Vref,正输入端耦接于充电端VT,用以接收充电电压Vramp,及输出端Q。锁存器SR包含设置端S用以接收充电信号Tcharge,重置端R耦接于比较器COMP的输出端,及输出端Q用以输出定时信号Ton。时间差提取器TE用以根据定时信号Ton及时差定时信号Ton_f产生时差信号Td。时间差提取器TE包含第一输入端耦接于信号合成器SS的输出端,第二输入端用以接收外部电路EXT输出的时差定时信号Ton_f,及输出端用以输出时差信号Td。

在实施例中,第一开关S1、第二开关S2及第三开关S3可为N型晶体管,例如双极性晶体管(bipolar junction transistor,BJT)、金氧半导体场效晶体管(Metal-Oxide-Semiconductor Field-Effect Transistor,MOSFET)或鳍式场效晶体管(Fin Field-Effect Transistor,FinFET)。然而实施例不限于此,其它形式的晶体管也应属本发明的涵盖范围。时间差提取器TE可为异或门(XOR gate)。时差定时信号Ton_f与定时信号Ton的时间差由外部电路EXT所产生,亦即,当定时信号Ton经过外部电路EXT后,定时信号Ton可能会因各种电路运作效应产生延迟或形变,造成定时信号Ton的脉宽(pulse width)与预设不同,其结果在实施例中称为时差定时信号Ton_f。定时信号Ton的传输延迟可能使时差定时信号Ton_f的下降缘落后于定时信号Ton的下降缘,而定时信号Ton的启动延迟可能使定时信号Ton的上升缘落后于时差定时信号Ton_f的上升缘。现今的高速电路运作时长皆为纳秒(nanosecond)级距,定时信号Ton的延迟或形变可能导致晶片内部电路不同步及其它的误差。因此,时间差提取器TE便可用以将定时信号Ton以及时差定时信号Ton_f的时间差提取出来,其提取结果即为时差信号Td。定时信号产生器100具备回馈机制,可利用时差信号Td校正定时信号Ton的延迟或形变,进而使高速电路能准确运作。

请参考第3图及第4图。第4图是第3图实施例的定时信号产生器100的操作信号时序图。在时间t1至t2之间,充电信号Tcharge为低电平(例如0V),使第一开关S1截止。充电电压Vramp电平低于参考电压Vref的电平(例如5V),使比较器COMP输出低电平信号。锁存器SR同时接收低电平的充电信号Tcharge及低电平的比较器COMP的输出信号,使输出端Q输出低电平的定时信号Ton。此时,定时信号Ton为低电平(例如0V),时差定时信号Ton_f为高电平。时间差提取器TE将定时信号Ton以及时差定时信号Ton_f的脉宽差距进行异或运算(XORoperation)产生时差信号Td,因此在时间t1至t2之间,时差信号Td为高电平,使第二开关S2导通。第二电流源CS2以第二电流I2对电容C充电,使充电电压Vramp上升。

在时间t2至t3之间,充电信号Tcharge升至高电平(例如5V),锁存器SR同时接收高电平的充电信号Tcharge及低电平的比较器COMP输出信号,使输出端Q输出的定时信号Ton升至高电平(例如5V)。此时,定时信号Ton为高电平,并且时差定时信号Ton_f也为高电平,时间差提取器TE将定时信号Ton以及时差定时信号Ton_f的脉宽差距进行异或运算(XORoperation)产生时差信号Td,因此由时间差提取器TE产生的时差信号Td会降为低电平。高电平的充电信号Tcharge使第一开关S1导通,低电平的时差信号Td使第二开关S2截止。第二电流源CS2停止对电容C充电,而第一电流源CS1开始以第一电流I1对电容C充电,持续使充电电压Vramp上升。需特别说明,为使充电电压Vramp上升的速率一致,第一电流I1电流值实质上等于第二电流I2的电流值。

在时间t3,充电电压Vramp达到参考电压Vref的电平,比较器COMP的输出信号升为高电平,充电信号Tcharge降为低电平。锁存器SR同时接收低电平的充电信号Tcharge及高电平的比较器COMP的输出信号,使输出端Q输出的定时信号Ton降至低电平,而时差定时信号Ton_f仍为高电平。在理想情况下,充电信号Tcharge的脉宽实质上等于定时信号Ton的脉宽。此时,重置信号RST(为振幅快速暂态变化的脉冲信号)启动,导通第三开关S3一段很短的时间,释放在充电端VT累积的充电电压Vramp,使充电电压Vramp快速降至低电平。且在时间t3至t4之间,时间差提取器TE以上述操作方式产生的时差信号Td升至高电平,使第二开关S2再次导通,以第二电流I2对电容C充电,再次使充电电压Vramp上升。

在时间t4,时差定时信号Ton_f降为低电平,并且定时信号Ton维持低电平,时间差提取器TE以上述操作方式产生的时差信号Td降至低电平。低电平的充电信号Tcharge使第一开关S1截止,低电平的时差信号Td使第二开关S2截止,因此第一电流源CS1和第二电流源CS2皆停止对电容C充电。第三开关S3为关闭状态,因此充电电压Vramp维持在断电前的电平。

在时间t5,定时信号产生器100开始产生下一周期的定时信号。维持在低电平的充电信号Tcharge使第一开关S1截止。充电电压Vramp电平低于参考电压Vref的电平,使比较器COMP输出低电平信号。锁存器SR同时接收低电平的充电信号Tcharge及低电平的比较器COMP输出信号,使输出端Q输出低电平的定时信号Ton。此时定时信号Ton为低电平,时差定时信号Ton_f为高电平。时间差提取器TE将定时信号Ton以及时差定时信号Ton_f的脉宽差距进行异或运算(XOR operation)产生时差信号Td。因此在时间t5,时差信号Td为高电平,使第二开关S2导通。第二电流源CS2以第二电流I2对电容C充电,使充电电压Vramp由先前的电平上升。其后的操作过程重复时间t1至t4,在此不赘述。如此,定时信号产生器100即可根据电路功用及需求持续在每一周期产生定时信号Ton。

定时信号Ton的脉宽可由以下公式校正:

I2×Td=C×Vos

I1×Ton=C×(Vref-Vos)

I1为第一电流,I2为第二电流,C为电容值,Td为时差信号的脉宽(pulse width),Ton为定时信号的脉宽,Ton_f为时差定时信号的脉宽,Vos为偏移电压值(offsetvoltage),Vref为参考电压值。其中偏移电压Vos如第2图所标示,为第二电流源CS2以第二电流I2对电容C充电累积的电压。第一电流源CS1以第一电流I1对电容C充电累积的电压则为Vref-Vos。

由上述可知,在一运作周期中,以第二电流I2先对电容C充电,将充电电压Vramp提升至一电平,称为偏移电压Vos。因比较器COMP通过比较两个输入端的电流或电压的大小,在输出端输出不同电压结果,如此可减少第一电流I1提升充电电压Vramp(由正输入端接收)达到比较器COMP的负输入端所接收的电压电平的时间,用以校正定时信号Ton使其脉宽缩短。在定时信号Ton经过外部电路EXT时,所产生延迟可用来回归校正定时信号Ton,使时差定时信号Ton_f的脉宽实质上等于预设的定时信号Ton脉宽。因此机制可校正定时信号Ton因外部电路EXT所产生的延迟或形变,使高速电路能准确运作。

第5图是实施例的定时信号产生器200的示意图。定时信号产生器200包含第一电流源CS1、第一开关S1、第二开关S2、第三开关S3、第四开关S4、第二电流源CS2、第一电容C1、第二电容C2、比较器COMP及时间差提取器TE。第一电流源CS1用以根据输入电压Vin产生第一电流I1。第一开关S1包含第一端耦接于第一电流源CS1,第二端耦接于充电端VT,及控制端用以接收充电信号Tcharge。第二开关S2包含第一端耦接于偏压端OS,第二端,及控制端用以接收时差信号Td。第二电流源CS2耦接于第二开关S2的第二端用以根据输入电压Vin产生第二电流I2。第三开关S3包含第一端耦接于充电端VT,第二端耦接于接地端GND,及控制端用以接收重置信号RST。第四开关S4包含第一端,第二端耦接于偏压端OS,及控制端用以接收重置信号RST。第一电容C1耦接于充电端VT与接地端GND之间。第二电容C2的第一端耦接于偏压端OS,第二端用以接收参考电压Vref。信号合成器SS耦接于充电端VT,用以根据充电电压Vramp及偏移参考电压Vref_os产生定时信号Ton。信号合成器SS包含比较器COMP及锁存器SR。比较器COMP包含负输入端耦接于偏压端OS,用以接收偏移参考电压Vref_os,正输入端耦接于充电端VT,用以接收充电电压Vramp。锁存器SR包含设置端S用以接收充电信号Tcharge,重置端R耦接于比较器COMP的输出端,及输出端Q用以输出定时信号Ton。时间差提取器TE耦接于信号合成器SS的输出端及第二开关S2的控制端,用以根据定时信号Ton及时差定时信号Ton_f产生时差信号Td。时间差提取器TE包含第一输入端耦接于信号合成器SS的输出端,第二输入端用以接收外部电路EXT输出的时差定时信号Ton_f,及输出端用以输出时差信号Td。

在实施例中,第一开关S1、第二开关S2、第三开关S3及第四开关S4可为N型晶体管,例如双极性晶体管(bipolar junction transistor,BJT)、金氧半导体场效晶体管(Metal-Oxide-Semiconductor Field-Effect Transistor,MOSFET)或鳍式场效晶体管(FinField-Effect Transistor,FinFET)。然而实施例不限于此,其它形式的晶体管也应属本发明的涵盖范围。时间差提取器TE可为异或门(XOR gate)。时差定时信号Ton_f与定时信号Ton的时间差由外部电路EXT所产生,亦即,当定时信号Ton经过外部电路EXT后,定时信号Ton可能会因各种电路运作效应产生延迟或形变,造成定时信号Ton的脉宽(pulse width)与预设不同,其结果在实施例中称为时差定时信号Ton_f。现今的高速电路运作时长皆为纳秒(nanosecond)级距或更快速,定时信号Ton的延迟或形变容易导致晶片内部电路不同步及其它的误差。因此,时间差提取器TE便可用以将定时信号Ton以及时差定时信号Ton_f的时间差提取出来,其提取结果即为时差信号Td。定时信号产生器200为本发明另一实施例,其具备回馈机制,可利用时差信号Td校正定时信号Ton的延迟或形变,进而使高速电路能准确运作。

请参考第5图及第6图。第6图是第5图实施例的定时信号产生器200的操作信号时序图。在时间t1至t2之间,充电信号Tcharge为低电平,使第一开关S1截止。充电电压Vramp电平低于参考电压Vref的电平,使比较器COMP输出低电平信号。锁存器SR同时接收低电平的充电信号Tcharge及低电平的比较器COMP输出信号,使输出端Q输出低电平的定时信号Ton。此时,定时信号Ton为低电平,时差定时信号Ton_f为高电平。时间差提取器TE将定时信号Ton以及时差定时信号Ton_f的脉宽差距进行异或运算(XOR operation)产生时差信号Td,因此在时间t1,时差信号Td为高电平,使第二开关S2导通。第二电流源CS2以第二电流I2使第二电容C2放电,进而使偏移参考电压Vref_os下降。

在时间t2至t3之间,充电信号Tcharge升至高电平,锁存器SR同时接收高电平的充电信号Tcharge及低电平的比较器COMP输出信号,使输出端Q输出的定时信号Ton升至高电平。此时,定时信号Ton为高电平,并且时差定时信号Ton_f也为高电平,时间差提取器TE将定时信号Ton以及时差定时信号Ton_f的脉宽差距进行异或运算(XOR operation)产生时差信号Td,因此由时间差提取器TE产生的时差信号Td会降为低电平。高电平的充电信号Tcharge使第一开关S1导通,低电平的时差信号Td使第二开关S2截止。第二电流源CS2停止使第二电容C2放电,偏移参考电压Vref_os停止下降,而第一电流源CS1开始以第一电流I1对第一电容C1充电,使充电电压Vramp上升。需特别说明,为使充电电压Vramp上升及偏移参考电压Vref_os下降的速率一致,第一电流I1电流值实质上等于第二电流I2的电流值。

在时间t3,充电电压Vramp达到参考电压Vref的电平,比较器COMP的输出信号升为高电平,充电信号Tcharge降为低电平。锁存器SR同时接收低电平的充电信号Tcharge及高电平的比较器COMP输出信号,使输出端Q输出的定时信号Ton降至低电平,而时差定时信号Ton_f仍为高电平。在理想情况下,充电信号Tcharge的脉宽实质上等于定时信号Ton的脉宽。此时,重置信号RST(为振幅快速暂态变化的脉冲信号)启动,导通第三开关S3一段很短的时间,释放在充电端VT累积的充电电压Vramp,使充电电压Vramp快速降至低电平。同时,重置信号RST也导通第四开关S4一段很短的时间,使偏移参考电压Vref_os拉回参考电压Vref的电平。且在时间t3至t4之间,时间差提取器TE以上述操作方式产生的时差信号Td升至高电平,使第二开关S2再次导通,以第二电流I2使第二电容C2放电,再次使偏移参考电压Vref_os下降。

在时间t4,时差定时信号Ton_f降为低电平,并且定时信号Ton维持低电平,时间差提取器TE以上述操作方式产生的时差信号Td降至低电平。低电平的充电信号Tcharge使第一开关S1截止,低电平的时差信号Td使第二开关S2皆截止,第一电流源CS1停止对第一电容C1充电,且第二电流源CS2停止使第二电容C2放电。第三开关S3为关闭状态,因此偏移参考电压Vref_os维持在断电前的电平。

在时间t5,定时信号产生器200开始产生下一周期的定时信号。维持在低电平的充电信号Tcharge使第一开关S1截止。充电电压Vramp电平低于参考电压Vref的电平,使比较器COMP输出低电平信号。锁存器SR同时接收低电平的充电信号Tcharge及低电平的比较器COMP输出信号,使输出端Q输出低电平的定时信号Ton。此时定时信号Ton为低电平,时差定时信号Ton_f为高电平。时间差提取器TE将定时信号Ton以及时差定时信号Ton_f的脉宽差距进行异或运算(XOR operation)产生时差信号Td。因此在时间t5,时差信号Td为高电平,使第二开关S2导通。第二电流源CS2以第二电流I2使第二电容C2放电,使偏移参考电压Vref_os由先前的电平下降。其后的操作过程重复时间t1至t4,在此不赘述。如此,定时信号产生器200即可根据电路功用及需求持续在每一周期产生定时信号Ton。

定时信号Ton的脉宽可由以下公式校正:

I2×Td=C×Vos

I1×Ton=C×(Vref_os)=C×(Vref-Vos)

I1为第一电流,I2为第二电流,C为第一电容C1与第二电容C2的电容值(第一电容的电容值实质上等于第二电容的电容值),Td为时差信号的脉宽(pulse width),Ton为定时信号的脉宽,Ton_f为时差定时信号的脉宽,Vos为偏移电压值(offset voltage),Vref为参考电压值。其中偏移电压Vos如第4图所标示,为第二电流源CS2以第二电流I2使第二电容C2放电的电压(使参考电压Vref下降)。放电后参考电压Vref下降的幅度则为Vref-Vos。

由上述可知,在一运作周期中,以第二电流I2先使第二电容C2放电,使参考电压Vref下降提升至一电平,称为偏移参考电压Vref_os。因比较器COMP通过比较两个输入端的电流或电压的大小,在输出端输出不同电压结果,如此可减少以第一电流I1提升充电电压Vramp(由正输入端接收)达到比较器COMP的负输入端所接收的电压电平的时间,校正定时信号Ton使其脉宽缩短。在定时信号Ton经过外部电路EXT时,所产生延迟可用来回归校正定时信号Ton,使时差定时信号Ton_f的脉宽实质上等于预设的定时信号Ton脉宽。因此机制可校正定时信号Ton因外部电路EXT所产生的延迟或形变,使高速电路能准确运作。

第7图是实施例的定时信号产生器300的示意图。定时信号产生器300与定时信号产生器100的电路布局相似。不同之处在于,定时信号产生器300的所产生定时信号Ton经过外部电路EXT后形成的时差定时信号Ton_f与定时信号Ton的相位相反,因此定时信号产生器300的时间差提取器TE可用或非门(NOR gate)代替。其余元件皆与定时信号产生器100相同,在此不赘述。

第8图是第7图实施例的定时信号产生器300的操作信号时序图。定时信号产生器300的操作信号时序图与定时信号产生器100的操作信号时序图类似。不同之处在于,定时信号产生器300的时差定时信号Ton_f与定时信号产生器100的时差定时信号Ton_f的相位相反。时间差提取器TE将定时信号Ton以及时差定时信号Ton_f的脉宽差距进行或非运算(NOR operation)产生时差信号Td,因此定时信号产生器300的时差信号Td与定时信号产生器100的时差信号Td同相位。其余操作信号皆与定时信号产生器100的操作信号相同。

具体而言,在时间t1至t2之间,充电信号Tcharge为低电平,使第一开关S1截止。充电电压Vramp电平低于参考电压Vref的电平,使比较器COMP输出低电平信号。锁存器SR同时接收低电平的充电信号Tcharge及低电平的比较器COMP的输出信号,使输出端Q输出低电平的定时信号Ton。此时,定时信号Ton为低电平,时差定时信号Ton_f为低电平。时间差提取器TE将定时信号Ton以及时差定时信号Ton_f的脉宽差距进行或非运算(NOR operation)产生时差信号Td,因此在时间t1至t2之间,时差信号Td为高电平,使第二开关S2导通。第二电流源CS2以第二电流I2对电容C充电,使充电电压Vramp上升。在时间t2至t3之间,充电信号Tcharge升至高电平,锁存器SR同时接收高电平的充电信号Tcharge及低电平的比较器COMP输出信号,使输出端Q输出的定时信号Ton升至高电平。此时,定时信号Ton为高电平,而时差定时信号Ton_f为低电平,时间差提取器TE将定时信号Ton以及时差定时信号Ton_f的脉宽差距进行或非运算(NOR operation)产生时差信号Td,因此由时间差提取器TE产生的时差信号Td会降为低电平。高电平的充电信号Tcharge使第一开关S1导通,低电平的时差信号Td使第二开关S2截止。第二电流源CS2停止对电容C充电,而第一电流源CS1开始以第一电流I1对电容C充电,持续使充电电压Vramp上升。在时间t3,充电电压Vramp达到参考电压Vref的电平,比较器COMP的输出信号升为高电平,充电信号Tcharge降为低电平。锁存器SR同时接收低电平的充电信号Tcharge及高电平的比较器COMP的输出信号,使输出端Q输出的定时信号Ton降至低电平,而时差定时信号Ton_f仍为低电平。在理想情况下,充电信号Tcharge的脉宽实质上等于定时信号Ton的脉宽。此时,重置信号RST(为振幅快速暂态变化的脉冲信号)启动,导通第三开关S3一段很短的时间,释放在充电端VT累积的充电电压Vramp,使充电电压Vramp快速降至低电平。且在时间t3至t4之间,时间差提取器TE以上述操作方式产生的时差信号Td升至高电平,使第二开关S2再次导通,以第二电流I2对电容C充电,再次使充电电压Vramp上升。在时间t4,时差定时信号Ton_f升为高电平,并且定时信号Ton维持低电平,时间差提取器TE以上述操作方式产生的时差信号Td降至低电平。低电平的充电信号Tcharge使第一开关S1截止,低电平的时差信号Td使第二开关S2截止,因此第一电流源CS1和第二电流源CS2皆停止对电容C充电。第三开关S3为关闭状态,因此充电电压Vramp维持在断电前的电平。其后的操作过程重复时间t1至t4,在此不赘述

第9图是实施例的定时信号产生器400的示意图。定时信号产生器400与定时信号产生器200的电路布局相似。不同之处在于,定时信号产生器400的所产生定时信号Ton经过外部电路EXT后形成的时差定时信号Ton_f与定时信号Ton的相位相反,因此定时信号产生器400的时间差提取器TE可用或非门(NOR gate)代替。其余元件皆与定时信号产生器200相同,在此不赘述。

第10图是第9图实施例的定时信号产生器400的操作信号时序图。定时信号产生器400的操作信号时序图与定时信号产生器200的操作信号时序图类似。不同之处在于,定时信号产生器400的时差定时信号Ton_f与定时信号Ton的相位相反。时间差提取器TE将定时信号Ton以及时差定时信号Ton_f的脉宽差距进行或非运算(NOR operation)产生时差信号Td,因此定时信号产生器400的时差信号Td与定时信号产生器200的时差信号Td同相位。其余操作信号皆与定时信号产生器200的操作信号相同。

具体而言,在时间t1至t2之间,充电信号Tcharge为低电平,使第一开关S1截止。充电电压Vramp电平低于参考电压Vref的电平,使比较器COMP输出低电平信号。锁存器SR同时接收低电平的充电信号Tcharge及低电平的比较器COMP输出信号,使输出端Q输出低电平的定时信号Ton。此时,定时信号Ton为低电平,时差定时信号Ton_f为低电平。时间差提取器TE将定时信号Ton以及时差定时信号Ton_f的脉宽差距或非运算(NOR operation)产生时差信号Td,因此在时间t1,时差信号Td为高电平,使第二开关S2导通。第二电流源CS2以第二电流I2使第二电容C2放电,进而使偏移参考电压Vref_os下降。在时间t2至t3之间,充电信号Tcharge升至高电平,锁存器SR同时接收高电平的充电信号Tcharge及低电平的比较器COMP输出信号,使输出端Q输出的定时信号Ton升至高电平。此时,定时信号Ton为高电平,并且时差定时信号Ton_f仍为低电平,时间差提取器TE将定时信号Ton以及时差定时信号Ton_f的脉宽差距进行或非运算(NOR operation)产生时差信号Td,因此由时间差提取器TE产生的时差信号Td会降为低电平。高电平的充电信号Tcharge使第一开关S1导通,低电平的时差信号Td使第二开关S2截止。第二电流源CS2停止使第二电容C2放电,偏移参考电压Vref_os停止下降,而第一电流源CS1开始以第一电流I1对第一电容C1充电,使充电电压Vramp上升。在时间t3,充电电压Vramp达到参考电压Vref的电平,比较器COMP的输出信号升为高电平,充电信号Tcharge降为低电平。锁存器SR同时接收低电平的充电信号Tcharge及高电平的比较器COMP输出信号,使输出端Q输出的定时信号Ton降至低电平,而时差定时信号Ton_f仍为低电平。在理想情况下,充电信号Tcharge的脉宽实质上等于定时信号Ton的脉宽。此时,重置信号RST(为振幅快速暂态变化的脉冲信号)启动,导通第三开关S3一段很短的时间,释放在充电端VT累积的充电电压Vramp,使充电电压Vramp快速降至低电平。同时,重置信号RST也导通第四开关S4一段很短的时间,使偏移参考电压Vref_os拉回参考电压Vref的电平。且在时间t3至t4之间,时间差提取器TE以上述操作方式产生的时差信号Td升至高电平,使第二开关S2再次导通,以第二电流I2使第二电容C2放电,再次使偏移参考电压Vref_os下降。在时间t4,时差定时信号Ton_f升为高电平,并且定时信号Ton维持低电平,时间差提取器TE以上述操作方式产生的时差信号Td降至低电平。低电平的充电信号Tcharge使第一开关S1截止,低电平的时差信号Td使第二开关S2皆截止,第一电流源CS1停止对第一电容C1充电,且第二电流源CS2停止使第二电容C2放电。第三开关S3为关闭状态,因此偏移参考电压Vref_os维持在断电前的电平。其后的操作过程重复时间t1至t4,在此不赘述

第11图是实施例的定时信号产生器500的示意图。定时信号产生器500与定时信号产生器100的电路布局相似。不同之处在于,定时信号产生器500的锁存器SR的输出端Qb可输出反相的定时信号Ton,因此定时信号产生器500产生的定时信号Ton与定时信号产生器100产生的定时信号Ton的相位相反,且定时信号产生器500的所产生定时信号Ton经过外部电路EXT后形成的时差定时信号Ton_f与定时信号Ton的相位相反。因此定时信号产生器500的时间差提取器TE可用与门(AND gate)代替。其余元件皆与定时信号产生器100相同,在此不赘述。

第12图是第11图实施例的定时信号产生器500的操作信号时序图。定时信号产生器500的操作信号时序图与定时信号产生器100的操作信号时序图类似。不同之处在于,定时信号产生器500的锁存器SR的输出端Qb可输出反相的定时信号Ton,因此定时信号产生器500产生的定时信号Ton与定时信号产生器100产生的定时信号Ton的相位相反,且定时信号产生器500的所产生定时信号Ton经过外部电路EXT后形成的时差定时信号Ton_f与定时信号Ton的相位相反。时间差提取器TE将定时信号Ton以及时差定时信号Ton_f的脉宽差距进行与运算(AND operation)产生时差信号Td,因此定时信号产生器500的时差信号Td与定时信号产生器100的时差信号Td同相位。其余操作信号皆与定时信号产生器100的操作信号相同。

具体而言,在时间t1至t2之间,充电信号Tcharge为低电平,使第一开关S1截止。充电电压Vramp电平低于参考电压Vref的电平(例如5V),使比较器COMP输出低电平信号。锁存器SR同时接收低电平的充电信号Tcharge及低电平的比较器COMP的输出信号,使输出端Qb输出高电平的定时信号Ton。此时,定时信号Ton为高电平,时差定时信号Ton_f为高电平。时间差提取器TE将定时信号Ton以及时差定时信号Ton_f的脉宽差距进行与运算(ANDoperation)产生时差信号Td,因此在时间t1至t2之间,时差信号Td为高电平,使第二开关S2导通。第二电流源CS2以第二电流I2对电容C充电,使充电电压Vramp上升。在时间t2至t3之间,充电信号Tcharge升至高电平,锁存器SR同时接收高电平的充电信号Tcharge及低电平的比较器COMP输出信号,使输出端Qb输出的定时信号Ton降至低电平。此时,定时信号Ton为低电平,并且时差定时信号Ton_f为高电平,时间差提取器TE将定时信号Ton以及时差定时信号Ton_f的脉宽差距进行与运算(AND operation)产生时差信号Td,因此由时间差提取器TE产生的时差信号Td会降为低电平。高电平的充电信号Tcharge使第一开关S1导通,低电平的时差信号Td使第二开关S2截止。第二电流源CS2停止对电容C充电,而第一电流源CS1开始以第一电流I1对电容C充电,持续使充电电压Vramp上升。在时间t3,充电电压Vramp达到参考电压Vref的电平,比较器COMP的输出信号升为高电平,充电信号Tcharge降为低电平。锁存器SR同时接收低电平的充电信号Tcharge及高电平的比较器COMP的输出信号,使输出端Qb输出的定时信号Ton升至高电平,而时差定时信号Ton_f仍为高电平。在理想情况下,充电信号Tcharge的脉宽实质上等于定时信号Ton的脉宽。此时,重置信号RST(为振幅快速暂态变化的脉冲信号)启动,导通第三开关S3一段很短的时间,释放在充电端VT累积的充电电压Vramp,使充电电压Vramp快速降至低电平。且在时间t3至t4之间,时间差提取器TE以上述操作方式产生的时差信号Td升至高电平,使第二开关S2再次导通,以第二电流I2对电容C充电,再次使充电电压Vramp上升。在时间t4,时差定时信号Ton_f降为低电平,并且定时信号Ton维持高电平,时间差提取器TE以上述操作方式产生的时差信号Td降至低电平。低电平的充电信号Tcharge使第一开关S1截止,低电平的时差信号Td使第二开关S2截止,因此第一电流源CS1和第二电流源CS2皆停止对电容C充电。第三开关S3为关闭状态,因此充电电压Vramp维持在断电前的电平。其后的操作过程重复时间t1至t4,在此不赘述。

第13图是实施例的定时信号产生器600的示意图。定时信号产生器600与定时信号产生器200的电路布局相似。不同之处在于,定时信号产生器600的锁存器SR的输出端Qb可输出反相的定时信号Ton,因此定时信号产生器600产生的定时信号Ton与定时信号产生器200产生的定时信号Ton的相位相反,且定时信号产生器600的所产生定时信号Ton经过外部电路EXT后形成的时差定时信号Ton_f与定时信号Ton的相位相反。因此定时信号产生器600的时间差提取器TE可用与门(AND gate)代替。其余元件皆与定时信号产生器200相同,在此不赘述。

第14图是第13图实施例的定时信号产生器600的操作信号时序图。定时信号产生器600的操作信号时序图与定时信号产生器200的操作信号时序图类似。不同之处在于,定时信号产生器600的定时信号Ton与定时信号产生器200的定时信号Ton的相位相反。时间差提取器TE将定时信号Ton以及时差定时信号Ton_f的脉宽差距进行与运算(AND operation)产生时差信号Td,因此定时信号产生器600的时差信号Td与定时信号产生器200的时差信号Td同相位。其余信号皆与定时信号产生器200的操作信号相同。

具体而言,在时间t1至t2之间,充电信号Tcharge为低电平,使第一开关S1截止。充电电压Vramp电平低于参考电压Vref的电平,使比较器COMP输出低电平信号。锁存器SR同时接收低电平的充电信号Tcharge及低电平的比较器COMP输出信号,使输出端Qb输出高电平的定时信号Ton。此时,定时信号Ton为高电平,时差定时信号Ton_f为高电平。时间差提取器TE将定时信号Ton以及时差定时信号Ton_f的脉宽差距进行与运算(AND operation)产生时差信号Td,因此在时间t1,时差信号Td为高电平,使第二开关S2导通。第二电流源CS2以第二电流I2使第二电容C2放电,进而使偏移参考电压Vref_os下降。在时间t2至t3之间,充电信号Tcharge升至高电平,锁存器SR同时接收高电平的充电信号Tcharge及低电平的比较器COMP输出信号,使输出端Qb输出的定时信号Ton降至低电平。此时,定时信号Ton为低电平,并且时差定时信号Ton_f为高电平,时间差提取器TE将定时信号Ton以及时差定时信号Ton_f的脉宽差距进行与运算(AND operation)产生时差信号Td,因此由时间差提取器TE产生的时差信号Td会降为低电平。高电平的充电信号Tcharge使第一开关S1导通,低电平的时差信号Td使第二开关S2截止。第二电流源CS2停止使第二电容C2放电,偏移参考电压Vref_os停止下降,而第一电流源CS1开始以第一电流I1对第一电容C1充电,使充电电压Vramp上升。在时间t3,充电电压Vramp达到参考电压Vref的电平,比较器COMP的输出信号升为高电平,充电信号Tcharge降为低电平。锁存器SR同时接收低电平的充电信号Tcharge及高电平的比较器COMP输出信号,使输出端Qb输出的定时信号Ton升至高电平,而时差定时信号Ton_f仍为高电平。在理想情况下,充电信号Tcharge的脉宽实质上等于定时信号Ton的脉宽。此时,重置信号RST(为振幅快速暂态变化的脉冲信号)启动,导通第三开关S3一段很短的时间,释放在充电端VT累积的充电电压Vramp,使充电电压Vramp快速降至低电平。同时,重置信号RST也导通第四开关S4一段很短的时间,使偏移参考电压Vref_os拉回参考电压Vref的电平。且在时间t3至t4之间,时间差提取器TE以上述操作方式产生的时差信号Td升至高电平,使第二开关S2再次导通,以第二电流I2使第二电容C2放电,再次使偏移参考电压Vref_os下降。在时间t4,时差定时信号Ton_f降为低电平,并且定时信号Ton维持高电平,时间差提取器TE以上述操作方式产生的时差信号Td降至低电平。低电平的充电信号Tcharge使第一开关S1截止,低电平的时差信号Td使第二开关S2皆截止,第一电流源CS1停止对第一电容C1充电,且第二电流源CS2停止使第二电容C2放电。第三开关S3为关闭状态,因此偏移参考电压Vref_os维持在断电前的电平。其后的操作过程重复时间t1至t4,在此不赘述。

综上所述,本发明实施例的定时信号产生器可校正定时信号使其脉宽缩短。在定时信号经过外部电路时,所产生延迟可用来回归校正定时信号,使时差定时信号的脉宽实质上等于预设的定时信号脉宽。因此机制可校正定时信号因外部电路所产生的延迟或形变,使高速电路能准确运作。

以上所述仅为本发明的较佳实施例,凡依本发明申请专利范围所做的同等变化与修饰,皆应属本发明的涵盖范围。

【符号说明】

10,100,200,300,400,500,600:定时信号产生器

EXT:外部电路

CS1,CS2:电流源

S1~S4:开关

C,C1,C2:电容

SS:信号合成器

COMP:比较器

TE:时间差提取器

SR:锁存器

VT:充电端

GND:接地端

S:设置端

R:重置端

Q,Qb:输出端

OS:偏压端

Tcharge:充电信号

RST:重置信号

Ton:定时信号

Ton_f:时差定时信号

Td:时差信号

Vin:输入电压

Vref:参考电压

Vref_os:偏移参考电压

Vos:偏移电压

Vramp:充电电压

I1,I2:电流

t1~t5:时间