一种雷达控制模块及其使用方法

文献发布时间:2023-06-19 09:33:52

技术领域

本发明涉及雷达技术领域,具体的涉及一种雷达控制模块及其使用方法。

背景技术

随着微波技术的发展,传统的雷达所占用的频谱带宽也越来越宽,频谱资源也越来越紧张,这就需要雷达往更高的频率发展,然而现实中由于受功率放大器件发展的影响,频谱资源不可能无限地往更高频率发展,现阶段已经有太赫兹微波器件出现,但其输出功率小及设计难度大再次影响其大规模的运用。

当前阶段,除了通信雷达等小部分雷达以外,绝大部分雷达均采用以饱和放大作为放大方式的功率放大器件。由于功率放大器件的自身特性,当其工作在饱和状态时其频谱带宽会出现展宽的现象,从而导致此时雷达所占用的频谱带宽会比实际所需要的宽,浪费了频谱资源。

另外,在当前雷达设计中,绝大部分雷达均为多级放大,即输入功率通过多级功率放大后得到输出功率,而每个功率放大器件的工作时间受功率管的栅压控制,栅压由TTL调制电路生成,输入的小功率信号经过多级功率放大后得到输出信号,功率放大模块的工作时间由TTL电平控制。由于功率放大器的特性,放大后的信号前沿将会出现过冲,并且前沿后沿不一致。现有的雷达只包括调制模块和放大模块,没有将时序控制手段应用于雷达上。

申请公布号为CN 102170277 A的中国专利文件于2011.08.31 公开了“基于移相相与获取皮秒精度窄脉宽TTL信号的方法”将TTL信号一分为二,对其中一路信号进行延迟后使两路信号经过逻辑与门进行逻辑相与操作,从而压缩脉宽,实现了对距离选通成像中脉冲激光器触发信号或ICCD触发信号的脉宽压缩,是对两路TTL信号分开处理,并不是对前沿和后沿的时序处理,电路稍显复杂且没有应用于雷达领域,没有解决雷达多级放大信号的过冲和频谱不对称问题。

申请公布号为CN 109743045 A的中国专利文件于2019.05.10 公开了“逻辑电平跳变检测及可调宽度窄脉冲发生电路”,通过逻辑电平跳变检测及可调宽度窄脉冲发生电路的输出信号从异或门的输出端口输出,以得到脉冲宽度一定的窄脉冲信号,以解决无线传输信号的抗干扰性,使用了逻辑电路控制脉冲信号,与单一地控制TTL时序不同,电路稍微复杂,并且也没有应用于雷达领域,没有解决雷达占用的频谱带宽过宽,浪费频谱资源的问题。

授权公告号为CN 106059522 B的中国专利文件公开了“一种控制功率放大器无过冲的方法和电路”通过对电调衰减器置一个较大的衰减值,使信号衰减到合适水平,解决了避免输出功率产生过冲的问题,但是引入了电调衰减器,提高了成本。

授权公告号为CN 104777457 B的中国专利文件公开了“一种频率扫描波束时序控制装置及其控制方法”通过信号处理机以及通讯装置实现时序控制以及波束控制。时序控制必然会对波形产生影响,该专利并未公开控制模块,也并未将时序控制应用到调制雷达的电压上,同时也未解决雷达占用的频谱带宽过宽,浪费频谱资源的问题。

发明内容

本发明针对雷达工作在饱和状态时占用频谱带宽大的情况,提供一种雷达控制模块及其使用方法,旨在通过控制TTL电平信号的时序以控制放大后的信号频谱,达到减小频带宽度的目的。

本发明的方案如下:

一种雷达控制模块,包括放大模块,控制模块还包括FPGA模块和调制模块;

FPGA模块包括I/O单元和时序单元,所述I/O单元用于将一路TTL电平输入信号转化为n路TTL电平输出信号,所述时序单元控制TTL电平输出信号的时序;

调制模块接收FPGA模块传输的n路TTL电平输出信号,并通过该TTL电平输出信号的时序控制输出信号Vd的时序;

放大模块接收调制模块的输出信号Vd并作为该放大模块的工作电压,输出RFout信号。

作为优选,FPGA模块包括TTL电平输入端口以及n个TTL电平输出端口,并通过n个TTL电平输出端口连接n个调制模块。

作为优选,FPGA模块还包括同步时钟CLOCK信号,通过同步时钟CLOCK信号端口输入一个时钟CLOCK方波信号,用于实现控制模块的时序同步。

作为优选,调制模块还包括VCC输入端口、VIN输入端口和VD输出端口,VCC输入端口连接电源电压,VIN输入端口连接信号电压,VD输出端口连接放大模块。

作为优选,放大模块包括RFout输出端口,n个放大模块通过输出端口RFout依次级联,实现多级放大。

本发明还提供一种雷达控制模块的使用方法,使用本发明公开的雷达控制模块,

步骤一,为FPGA模块的TTL电平输入端口接入信号宽度为t1的TTL电平信号,并通过同步时钟CLOCK信号实现信号同步;

步骤二,在第1个TTL电平输入信号上升沿到来时,延时T1时间后输入高电平,在TTL电平下降沿到来时,延时T1时间后输入低电平,在下个周期进行同样变换,得到TTL

步骤三,在第2个、第3个……第n-1个TTL电平输入信号上升沿到来时,输入高电平,在第2个、第3个……第n-1个TTL电平输入信号下降沿到来时,输入低电平,在下个周期进行同样变换,得到TTL

步骤四,在第n个TTL电平上升沿到来时,输入高电平并保持t1-T2时间,在下一个周期进行同样变换,得到TTL

步骤五,将FPGA生成的n路TTL输出信号及输入电压VIN

步骤六,将Vd

作为优选,TTL

作为优选,TTL

作为优选,调制脉冲信号Vd

作为优选,TTL电平上升沿的时间与过冲时间的和为H1,n级放大的TTL电平下降沿时间为L1,T1=H1,T2=T1-L1。

有益效果:

(1)本发明将TTL时序控制应用于雷达上,巧妙地控制了雷达调制模块的输出信号Vd,只需外加FPGA模块,设计成本低,易于工业推广。

(2)本发明通过调节T1时间将雷达输出信号中过冲的部分裁切掉,从而减小了雷达实际工作时所占用的频谱带宽,大大节约了频谱资源。

(3)本发明通过调节T2时间,使得雷达输出信号的上升沿与下降沿趋于对称,即在频域内使频谱左右趋于对称,输出的频谱质量优。

(4)本发明只需调整TTL

附图说明

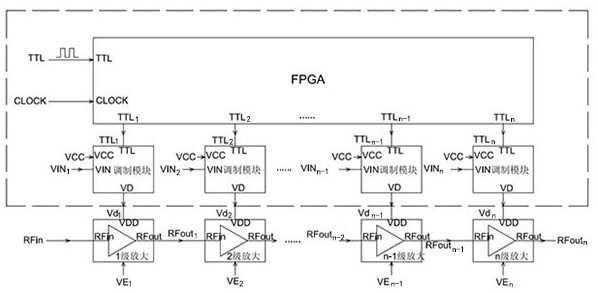

图1为本发明的一个实施例的雷达控制电路示意图;

图2为本发明的一个实施例的TTL

图3为本发明的一个实施例的TTL

图4为本发明的一个实施例的TTL

图5为本发明的一个实施例的调制模块电路示意图;

图6为本发明的一个实施例的调制模块信号示意图;

图7为本发明的一个实施例的n路调制脉冲示意图;

图8为本发明的一个实施例的未经处理时RFout检波信号示意图;

图9为本发明的一个实施例的RFout

图10为本发明的一个实施例的RFout

图11 为本发明的一个实施例的RFout

图12 为本发明的一个实施例的RFout

具体实施方式

下面将结合本发明实施例中的附图,对本发明实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例仅仅是本发明一部分实施例,而不是全部的实施例。基于本发明中的实施例,本领域普通技术人员在没有做出创造性劳动前提下所获得的所有其他实施例,都属于本发明保护的范围。

本发明针对雷达工作在饱和状态时占用频谱带宽大的情况,提供一种减小雷达工作带宽的系统及方法,旨在通过控制TTL电平信号以改变每个功率放大模块的工作时间,从而控制放大后的信号的频谱,达到减小频带宽度的目的。

如图1所示,为本发明的雷达控制模块的工作原理图。一种雷达控制模块,包括FPGA模块、调制模块和放大模块。FPGA模块包括TTL电平输入端口、同步时钟CLOCK端口以及n个TTL电平输出端口,FPGA模块的I/O单元用于将输入的TTL电平输入信号转化为n个TTL电平输出信号,并经过时序单元的同步时钟CLOCK信号进行整个电路的时钟同步。调制模块包括TTL电平输入端口,VCC输入端口、VIN输入端口以及VD输出端口,其中TTL电平输入端口连接FPGA模块输出的n路TTL电平输出端口,VCC输入端口连接电源电压,VIN输入端口连接信号电压,VD输出端口连接放大模块。放大模块包括RFin输入端口、RFout输出端口以及VE输入端口,RFin连接射频输入信号,VE连接发射级电压,RFout输出端口输出射频输出信号,n个放大模块通过输出端口RFout依次级联,实现多级放大。

本发明还提供一种雷达控制电路的使用方法,使用本发明公开的雷达控制模块:

步骤一,为FPGA模块的TTL电平输入端口接入信号宽度为t1的TTL电平信号,并通过同步时钟CLOCK信号实现信号同步。

步骤二,在第1个TTL电平输入信号上升沿到来时,延时T1时间后输入高电平,在TTL电平下降沿到来时,延时T1时间后输入低电平,在下个周期进行同样变换,得到TTL

步骤三,在第2个、第3个……第n-1个TTL电平输入信号上升沿到来时,输入高电平,在第2个、第3个……第n-1个TTL电平下降沿到来时,输入低电平,在下个周期进行同样变换,得到TTL

步骤四,在第n个TTL电平上升沿到来时,输入高电平并保持t1-T2时间,在下一个周期进行同样变换,得到TTL

步骤五,将FPGA生成的n路TTL输出信号及输入电压VIN

步骤六,将Vd

如图8所示,为未经处理时的RFout检波信号示意图,输入射频信号RFin为正弦波,输出的RFout射频信号出现了过冲现象,RFout信号经过检波后的信号图像为上升沿有过冲,且不对称的脉冲信号。此时频谱信号将会出现展宽,导致频谱资源浪费。

使用本发明公开的方法,利用各个Vd作为各级放大模块的工作电压。

首先,控制TTL

将延时的TTL

如图9所示,为RFout

其次,控制TTL

将与TTL同步的TTL

如图10所示,为RFout

最后,控制TTL

将导前的TTL

如图11所示,为RFout

如图12所示,为RFout

为验证本专利的正确性,本专利利用三级放大进行实验,频率范围为2.7~3.1GHz,测试频点为2.7GHz。其中,1级放大的上升沿与过冲时间的和约为90ns,3级放大的下降沿时间约为20ns。理论上,T1=90ns,T2=70ns。实际应用时可根据测试结果进行微调,使得下降沿与上升沿趋于对称即可。

通过调节,T1最终设置为100ns,T2最终设置为80ns。

实际测试结果对比结果见表1:

表1 处理前后频宽对比结果

根据对比结果,可见输出信号在经过处理后,在输出主频宽度不变的情况下, 6dB、20dB、40dB等带宽明显减小,节约了频谱资源。

最后应说明的是:以上所述仅为本发明的优选实施例而已,并不用于限制本发明,尽管参照前述实施例对本发明进行了详细的说明,对于本领域的技术人员来说,其依然可以对前述各实施例所记载的技术方案进行修改,或者对其中部分技术特征进行等同替换。凡在本发明的精神和原则之内,所作的任何修改、等同替换、改进等,均应包含在本发明的保护范围之内。

- 一种雷达控制模块及其使用方法

- 一种雷达控制模块安装板用落料凸模