一种适合于星载XILINX V2 FPGA刷新方法

文献发布时间:2023-06-19 09:33:52

技术领域

本发明涉及一种适合于星载XILINX V2 FPGA刷新方法。

背景技术

星载电子设备在轨运行时,必须考虑宇宙高能射线对电子设备产生的影响。单粒子翻转会改变静态存储元素的逻辑状态。FPGA的功能取决于FPGA百万配置寄存器中存储的数据。配置存储阵列中的单粒子翻转会对期望的功能产生明显的影响。配置存储空间的单粒子翻转有可能影响功能,也有可能不会影响功能。可以采用三模冗余设计技术实现单粒子翻转效应的消除。

V2系列FPGA SelectMap接口通过对配置存储阵列读或写来实现最有效的后配置控制。回读是配置存储后配置读操作,部分重配是配置存储后配置写操作。回读和部分重配可以在不影响用户应用的前提下,检测和修复配置存储空间的单粒子翻转。如果影响用户应用的单粒子翻转现象发生,那么只能通过重新配置FPGA来纠正。

发明内容

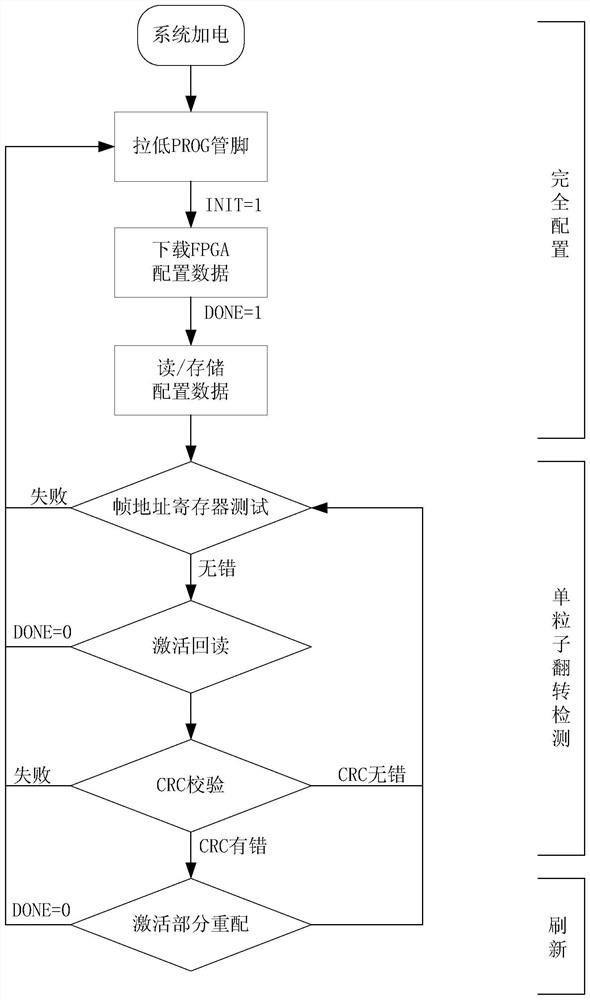

本发明要解决的技术问题是:星载电子设备在轨运行过程中,若受到单粒子翻转,但是没有发生单粒子功能中断,则可以通过刷新来纠正单粒子效应,避免单粒子效应的累积,同时,不中断用户功能。本发明克服现有技术的不足,提供了一种适合于星载XILINX V2FPGA刷新方法,非单粒子功能中断单粒子翻转可以通过刷新来纠正;单粒子功能中断单粒子翻转只能通过拉低PROG管脚,重新配置FPGA来恢复。刷新功能可以避免单粒子效应累积,延长星载信号处理FPGA的工作时长,提高星载设备的可靠性。单粒子效应导致单粒子功能中断时,需要重新配置信号处理FPGA。单粒子效应没有导致单粒子功能中断时,需要通过刷新来纠正,刷新不会影响信号处理FPGA的功能。本发明还给出了刷新时帧地址递增步骤和基于帧的刷新命令。

本发明目的通过以下技术方案予以实现:

一种适合于星载XILINX V2 FPGA刷新方法,包括如下步骤:

S1、对FPGA进行加电;

S2、将FPGA PROG管脚拉低最少300ns;

S3、从非易失性存储设备下载配置数据配置FPGA;

S4、对帧地址寄存器进行测试,如果测试失败返回S2;否则转入S5;

S5、进行激活回读,如果回读数据与配置数据一致转入S6,否则返回S2;

S6、进行CRC校验,如果CRC校验失败返回S2,如果CRC校验有错转入S7,如果CRC校验无错转入S4;

S7、进行激活部分重配,如果重配正常转入S4,否则返回S2。

上述适合于星载XILINX V2 FPGA刷新方法,优选的,在S4和S5之间,监测状态寄存器,如果正常转入S5,否则返回S2。

上述适合于星载XILINX V2 FPGA刷新方法,优选的,S2中,将FPGA的PROG管脚拉低最少300ns,直到FPGA的INIT管脚变高。

上述适合于星载XILINX V2 FPGA刷新方法,优选的,S3中刷新配置选项寄存器的DriveDone、PWRDWN_Stat,以及控制寄存器的Persist、Security Level。

上述适合于星载XILINX V2 FPGA刷新方法,优选的,S4中,帧地址寄存器测试首先向帧地址寄存器写入预定义值,然后回读帧地址寄存器。

上述适合于星载XILINX V2 FPGA刷新方法,优选的,S5中,第一个回读序列覆盖了所有的GCLK、IOI、CLB,以及除最后一个IOB帧以外的IOB;第二个回读序列只回读缓冲中的最后一个IOB帧;第三个回读序列验证所有剩余的控制BRAM互连的配置帧。

上述适合于星载XILINX V2 FPGA刷新方法,优选的,刷新时,帧地址递增的顺序为最小地址,列地址,块地址;即当最小地址递增到最大帧数时,最小地址复位为0,列地址开始递增,当列地址递增到最大列时,列地址复位为0,块地址开始递增,当块地址递增到最大块时,块地址复位为0。

本发明相比于现有技术具有如下有益效果:

(1)星载电子设备在轨工作时,配置管理引擎对星载信号处理FPGA刷新,避免单粒子效应的累积,提高星载设备工作时的可靠性,延长星载电子设备寿命。

(2)当发生了单粒子功能中断单粒子翻转,通过重新配置信号处理FPGA来恢复功能,如果发生了非单粒子功能中断单粒子翻转,则可以通过刷新来纠正,刷新不会影响信号处理FPGA的功能。

(3)在帧地址寄存器测试和激活回读之间添加监测状态寄存器,如果正常,激活回读,否则拉低PROG管脚,重新配置FPGA。避免了不必要的回读,延长了星载电子设备无故障工作时间。

(4)配置选项寄存器的DriveDone,PWRDWN_Stat,控制寄存器的Persist,SecurityLevel影响单粒子功能中断的检测。因此,刷新这两个寄存器以提高单粒子功能中断的检测概率。

(5)如果使用了查找表,例如,SRL16或分布式RAM(LUTRAM),回读或部分重配将会毁坏这部分原语的内容。SRL16或分布式RAM(LUTRAM)的问题,BRAM也会碰到。因此,本发明回读和重配时,回避了BRAM块地址。

(6)如果FPGA设计没有使用任何BRAM,那么配置管理引擎将使用一个序列回读整个的配置存储空间。否则,完整回读需要三个回读序列以避免破坏BRAM内容。本发明第一个回读序列覆盖了所有的GCLK、IOI、CLB、部分IOB。省略最后一个IOB帧,防止第一个BRAM帧进入缓冲,从而破坏BRAM。第二个回读序列只回读缓冲中的最后一个IOB帧。第三个回读序列验证所有剩余的控制BRAM互连的配置帧。在第二个回读序列中,帧地址寄存器指向未使用的地址。回读这个未使用的地址时,回读的第一个虚拟帧是第一个回读序列缓冲中存储的最后一个IOB帧。

附图说明

图1为V2配置存储空间架构;

图2为V2列级配置存储图;

图3为单粒子效应消除电路示意图;

图4为单粒子翻转检测和纠正算法流程图;

图5为帧地址递增流程图。

具体实施方式

为使本发明的目的、技术方案和优点更加清楚,下面将结合附图对本发明的实施方式作进一步详细描述。

一种适合于星载XILINX V2 FPGA刷新方法,包括如下步骤:

S1、对FPGA进行加电;

S2、将FPGA PROG管脚拉低最少300ns;

S3、从非易失性存储设备下载配置数据配置FPGA;

S4、对帧地址寄存器进行测试,如果测试失败返回S2;否则转入S5;

S5、进行激活回读,如果回读数据与配置数据一致转入S6,否则返回S2;

S6、进行CRC校验,如果CRC校验失败返回S2,如果CRC校验有错转入S7,如果CRC校验无错转入S4;

S7、进行激活部分重配,如果重配正常转入S4,否则返回S2。

作为本发明的一种优选方案,在S4和S5之间,监测状态寄存器,如果正常转入S5,否则返回S2。

作为本发明的一种优选方案,S2中,将FPGA的PROG管脚拉低最少300ns,直到FPGA的INIT管脚变高。

作为本发明的一种优选方案,S3中刷新配置选项寄存器的DriveDone、PWRDWN_Stat,以及控制寄存器的Persist、Security Level。

作为本发明的一种优选方案,S4中,帧地址寄存器测试首先向帧地址寄存器写入预定义值,然后回读帧地址寄存器。

作为本发明的一种优选方案,S5中,第一个回读序列覆盖了所有的GCLK、IOI、CLB,以及除最后一个IOB帧以外的IOB;第二个回读序列只回读缓冲中的最后一个IOB帧;第三个回读序列验证所有剩余的控制BRAM互连的配置帧。

作为本发明的一种优选方案,刷新时,帧地址递增的顺序为最小地址,列地址,块地址;即当最小地址递增到最大帧数时,最小地址复位为0,列地址开始递增,当列地址递增到最大列时,列地址复位为0,块地址开始递增,当块地址递增到最大块时,块地址复位为0。

实施例:

1、配置存储架构

V2架构中最基本的配置单元是帧。配置帧组由CLB、IOB、IOI、GCLK、BRAM、BRAMInterconnects列组成。列分成了三个块类型:CLB(包括GLKC、CLB、IOB1&2)、BRAM和BRAMInterconnects。V2配置存储空间架构如图1所示。

V2帧地址从0x00000000h开始(设备中间GCLK列的起始地址),帧地址开始递增,一直递增到最左边的IOB列,然后向右递增。帧地址寄存器由三部分构成,块地址、主地址和较小地址。当FDRI或FDRO命令要求配置多帧或回读多帧,帧地址寄存器自动递增较小地址、主地址和块地址。块地址00覆盖了所有的GCLK、IOB、IOI和CLB列,块地址01包含了所有的BRAM列,块地址10包含了所有的BRAM Interconnects列。主地址是设备大小的函数,由设备的列数决定。V2列级配置存储图如图2所示。

针对回读和部分重配操作,设计实现时需要有特殊的考虑。如果使用了查找表,例如,SRL16或分布式RAM(LUTRAM),回读或部分重配将会毁坏这部分原语的内容。SRL16或分布式RAM(LUTRAM)的问题,BRAM也会碰到。因此,回读和重配时,必须回避BRAM块地址。然而,BRAM Interconnect帧仅包含了配置信息,没有包含特殊RAM原语,因此,可以像CLB帧那样自由接入。

配置存储的单粒子翻转可能毁坏用户设计,也可能对用户设计没有任何影响。配置存储的大部分翻转将不会对用户设计有任何的影响,因为大部分配置存储与用户设计无关。路由控制比特在配置比特中占了60%多,而典型设计仅使用了10%-20%的路由资源。回读配置存储,并将回读的数据与存储的配置数据进行对比,以决定配置存储比特是否发生了翻转。

V2单粒子翻转检测方法

(1)监测DONE信号

设备配置成功后,DONE管脚应该保持高电平。如果DONE变低,则表明加电部分电路发生了单粒子翻转,导致配置存储全局或部分清空,需要重新配置。

(2)写和读帧地址寄存器

每次刷新和回读操作之前,应该写和读帧地址寄存器,以快速识别SelectMAP接口问题或其他配置逻辑干扰。

(3)计算和比较回读CRC

当回读时,回读数据可以用来计算CRC值。如果不进行CRC的比较,不正确的CRC值将导致错误的SEFI检测,因此,CRC不一致时,需要重配,以获得正确的CRC值。

(4)监测BUSY信号

写操作中,BUSY管脚应该保持低电平。读操作中,BUSY管脚应该保持高电平。当BUSY管脚由高电平转为低电平时,表明数据线上的数据为正确的数据。写操作转换成读操作时,如果BUSY管脚保持高电平的时间超过了32个时钟周期,则表明发生了SMAP SEFI。

(5)验证回读数据

回读中,回读数据与配置数据相比较以确保没有差别。CRC值可以从回读的数据中计算出来。

(6)监测状态寄存器

状态寄存器存储了关键设备状态。比特12是DONE管脚的状态。比特7指示了GHIGH状态,GHIGH控制信号的内部上拉。比特6是全局写使能,比特5是全局三态状态。

2、配置管理引擎

对于大部分在轨应用来说,需要配置管理引擎阻止配置存储空间单粒子翻转的累积,检测和恢复配置控制逻辑单粒子功能中断。单粒子效应消除电路示意图如图3所示。单粒子翻转检测和纠正算法流程图如图4所示。

2.1完全配置

单机加电后,配置管理引擎将FPGA PROG管脚拉低最少300ns。当检测到INIT管脚变高后,说明FPGA初始化完成,准备好配置了。配置管理引擎应该从非易失性存储设备(例如,PROM)下载配置数据配置FPGA。配置选项寄存器的DriveDone,PWRDWN_Stat,控制寄存器的Persist,Security Level影响单粒子功能中断的检测。因此,这两个寄存器应该被刷新以保证单粒子功能中断的检测。出于刷新目的,控制寄存器的典型值为X“00 00 00 0D”,配置选项寄存器的典型值为X“00 04 3F E5”。回读配置选项寄存器或控制寄存器的推荐序列如表1所示。

表1

2.2单粒子翻转检测

FPGA配置成功后,就可以进行单粒子翻转检测了。单粒子翻转检测首先从帧地址寄存器测试开始。帧地址寄存器测试首先向帧地址寄存器写入预定义值,然后回读帧地址寄存器。如果回读值与期望值一致,配置管理引擎可以回读整个配置存储空间。如果帧地址寄存器回读数据与期望值不一致,说明可能发生了单粒子功能中断,配置引擎需要重新配置数据。帧地址寄存器测试失败后,也有可能没有发生单粒子功能中断,而是单粒子翻转导致了回读数据的错误。帧地址寄存器测试序列如表2所示。

表2

帧地址寄存器测试成功后,应该回读和验证状态寄存器。如果状态寄存器的比特5或6变为0,设备将有三态输出或者更新同步设备部件能力失效。为了消除此问题,必须关机再重新启动设备。读状态寄存器的序列如表3所示。

表3

帧地址寄存器和状态寄存器校验通过后,应该执行设备回读。设备回读能够检测通用单粒子翻转,保证刷新的完整性。如果设备没有包含任何SRL16或LUTRAM原语,那么回读数据可以和非易失性存储中的配置数据比对。如果FPGA设计没有使用任何BRAM,那么配置管理引擎将使用一个序列回读整个的配置存储空间。否则,完整回读需要三个回读序列以避免破坏BRAM内容。第一个回读序列覆盖了所有的GCLK、IOI、CLB、部分IOB。省略最后一个IOB帧,防止第一个BRAM帧进入缓冲,从而破坏BRAM。第二个回读序列只回读缓冲中的最后一个IOB帧。第三个回读序列验证所有剩余的控制BRAM互连的配置帧。在第二个回读序列中,帧地址寄存器指向未使用的地址。回读这个未使用的地址时,回读的第一个虚拟帧是第一个回读序列缓冲中存储的最后一个IOB帧。

回读数据既可以与非易失性存储中的配置数据进行比对,也可以进行CRC校验。CRC和校验既可以基于单帧,也可以基于设备。应该进行回读校验以保证单粒子翻转被纠正。未纠正的单粒子翻转指明单粒子功能中断导致了配置存储写入失效。

如果CRC校验通过,并且没有任何回读错误,那么配置存储中没有翻转。设计者既可以选择重复回读直到发现单粒子翻转错误,再进行刷新,也可以选择自动连续刷新。回读序列如表4所示。

表4

2.3刷新

检测到非单粒子功能中断单粒子翻转事件后,需要刷新FPGA以阻止单粒子翻转的累积。刷新完成后,应该进行回读以保证单粒子翻转被纠正。回读操作或刷新操作可能破坏LUT存储原语,例如:SRL16s和LUTRAM。因此,设计不应该包含SRL16或LUTRAM以简化刷新过程。使用BRAM时,需要两个刷新过程:第一个刷新序列覆盖所有的GCLK、IOB、IOI和CLB列,第二个刷新序列只覆盖BRAM互连列。刷新序列如表5所示。

表5

3帧地址递增方法

XILINX V2 FPGA支持第零个、第二个类型块的刷新。刷新时,帧地址递增的顺序为最小地址,列地址,块地址。当最小地址递增到最大帧数时,最小地址复位为0,列地址开始递增,当列地址递增到最大列时,列地址复位为0,块地址开始递增,当块地址递增到最大块时,块地址复位为0。刷新时帧地址递增流程图如图5所示。

帧地址递增步骤如下所述:

(1)初始化,帧地址为0;

(2)较小地址递增;

(3)较小地址递增到所对应列类型的最大值,较小地址复位为0,列地址递增;否则,返回步骤(2);

(4)列地址递增到最大值,列地址复位为0,块地址递增;否则,返回步骤(2);

(5)块地址为1或2,返回步骤(2);块地址为3,结束。

本发明说明书中未作详细描述的内容属本领域技术人员的公知技术。

本发明虽然已以较佳实施例公开如上,但其并不是用来限定本发明,任何本领域技术人员在不脱离本发明的精神和范围内,都可以利用上述揭示的方法和技术内容对本发明技术方案做出可能的变动和修改,因此,凡是未脱离本发明技术方案的内容,依据本发明的技术实质对以上实施例所作的任何简单修改、等同变化及修饰,均属于本发明技术方案的保护范围。

- 一种适合于星载XILINX V2 FPGA刷新方法

- 一种适用于星载FPGA的刷新方法