遮蔽栅金属氧化物半导体场效晶体管及其制造方法

文献发布时间:2023-06-19 09:36:59

技术领域

本发明涉及一种半导体结构及其制造方法,特别是涉及一种遮蔽栅金属氧化物半导体场效晶体管(shield gate MOSFET)及其制造方法。

背景技术

遮蔽栅极金属氧化物半导体场效晶体管是沟槽式栅极金属氧化物半导体结构的一种改良型结构。相较于现有的金属氧化物半导体结构,遮蔽栅极金属氧化物半导体场效晶体管可有效降低栅极至漏极的电容(C

然而,随着元件缩小以及操作电压增加的发展,亟需寻求增加元件击穿电压的技术方案。

发明内容

本发明提供一种遮蔽栅金属氧化物半导体场效晶体管,可改善漏极至源极的击穿电压(Drain-Source Breakdown Voltage,BVDss)。

本发明提供一种遮蔽栅金属氧化物半导体场效晶体管的制造方法,能整合于现有制作工艺制作出高击穿电压的遮蔽栅金属氧化物半导体场效晶体管。

本发明的遮蔽栅金属氧化物半导体场效晶体管,包括具有第一导电态的一外延层、位于外延层中的数个沟槽、位于沟槽内的遮蔽栅极、位于沟槽内的遮蔽栅极上的控制栅极、位于遮蔽栅极与外延层之间的一绝缘层、位于控制栅极与外延层之间的一栅极氧化层、位于遮蔽栅极与控制栅极之间的栅间氧化层、位于沟槽底部的外延层内的一第一掺杂区与位于沟槽底部与第一掺杂区之间的一第二掺杂区。所述第一掺杂区具有第二导电态,所述第二掺杂区具有所述第一导电态。

在本发明的一实施例中,上述第一导电态为N型,第二导电态为P型。

在本发明的一实施例中,上述第一导电态为P型,第二导电态为N型。

在本发明的一实施例中,上述遮蔽栅极被所述栅间氧化层覆盖的顶面具有圆角。

在本发明的一实施例中,上述遮蔽栅金属氧化物半导体场效晶体管还包括配置于所述外延层的表面的源极区,且所述第二掺杂区的掺杂浓度小于所述源极区的掺杂浓度。

在本发明的一实施例中,上述第一掺杂区的掺杂浓度为均匀浓度。

在本发明的一实施例中,上述沟槽还可包括延伸至外延层的一连线区,所述遮蔽栅极延伸至所述连线区的沟槽内,且所述连线区的所述沟槽内还可包括一凸出部,作为电连接所述遮蔽栅极的接触窗。

在本发明的一实施例中,上述控制栅极并未延伸至所述连线区。

本发明的遮蔽栅金属氧化物半导体场效晶体管的制造方法包括形成具有第一导电态的一外延层;在所述外延层中形成数个沟槽;依序于每个沟槽的底部的外延层内形成具有第二导电态的一第一掺杂区与具有所述第一导电态的一第二掺杂区;在每个沟槽内形成具有遮蔽栅极的金属氧化物半导体场效晶体管。

在本发明的另一实施例中,上述第一导电态为N型,第二导电态为P型。

在本发明的另一实施例中,上述第一导电态为P型,第二导电态为N型。

在本发明的另一实施例中,形成具有上述遮蔽栅极的金属氧化物半导体场效晶体管的步骤包括于每个沟槽内的外延层的表面形成一绝缘层;在每个沟槽内的绝缘层上形成一导体层;移除部分导体层以形成遮蔽栅极并露出部分绝缘层;移除露出的绝缘层;在沟槽内形成一栅间氧化层与一栅极氧化层,其中所述栅间氧化层覆盖所述遮蔽栅极的顶面,且所述栅间氧化层覆盖外延层的表面;然后于所述沟槽内的栅间氧化层上形成一控制栅极。

在本发明的另一实施例中,移除部分上述导体层之后还可包括对所述遮蔽栅极的顶面进行圆角化。

在本发明的另一实施例中,上述制造方法还可包括于外延层的表面形成一源极区,且第二掺杂区的掺杂浓度小于源极区的掺杂浓度。

在本发明的另一实施例中,上述第一掺杂区的掺杂浓度为均匀浓度。

在本发明的另一实施例中,上述外延层包括一连线区,因此形成沟槽的同时,会在所述连线区内也形成所述沟槽,且于移除部分导体层的步骤中,在所述连线区上形成一保护层以保留所述连线区内的导体层。

基于上述,本发明通过在沟槽底部的外延层中形成导电态不同的第一与第二掺杂区,与外延层不同导电态的第一掺杂区能提供均匀的场分布,而与外延层相同导电态的第二掺杂区则介于第一掺杂区与沟槽底部之间,以减少漏电路径,进而改善漏极至源极的击穿电压。

为让本发明的上述特征和优点能更明显易懂,下文特举实施例,并配合所附的附图作详细说明如下。

附图说明

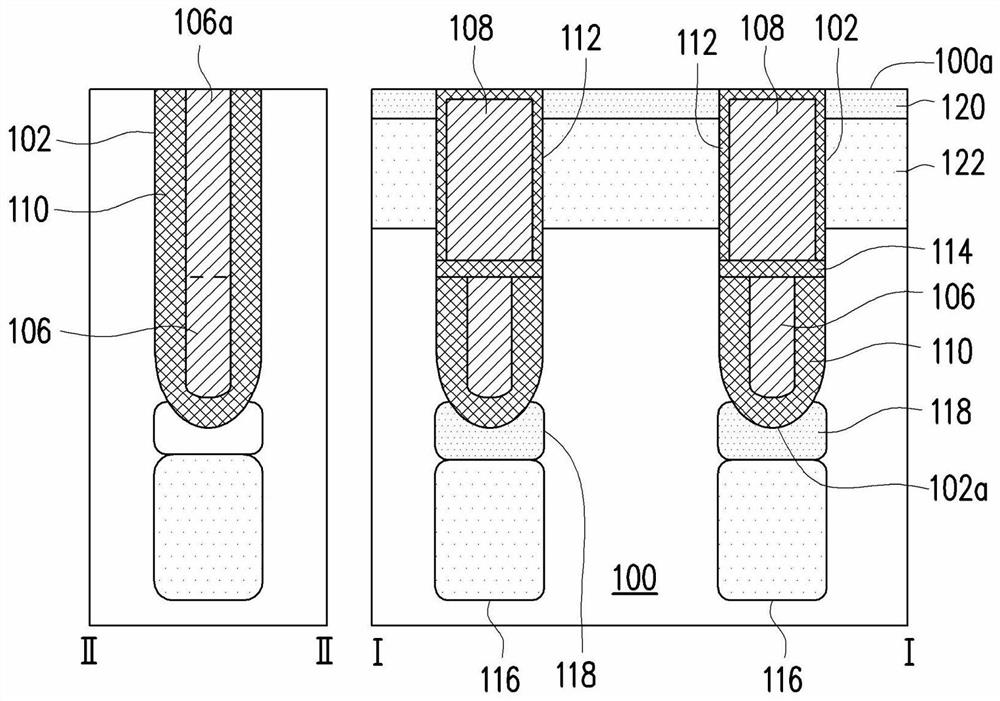

图1A为本发明的第一实施例的一种遮蔽栅金属氧化物半导体场效晶体管的上视示意图;

图1B是图1A的I-I线段与II-II线段的结构剖面示意图;

图2是第一实施例的另一种遮蔽栅金属氧化物半导体场效晶体管的剖面示意图;

图3A至图3L为本发明的第二实施例的一种遮蔽栅金属氧化物半导体场效晶体管的制造流程剖面示意图;

图4是模拟实验例1的第二掺杂区的掺杂剂量与击穿电压的曲线图。

符号说明

100、300:外延层

100a、300a、300c:外延层表面

100b、300b:外延层底面

102、302:沟槽

102a、302a:沟槽底部

104、304:连线区

106、312a:遮蔽栅极

106a、312b:凸出部

108、200、320:控制栅极

110、310:绝缘层

112、204、318:栅极氧化层

114、202、316:栅间氧化层

116、206、306:第一掺杂区

118、308:第二掺杂区

120、322:源极区

122、324:阱区

200a、312c:顶面

312:导体层

314:保护层

326:介电层

328:接触窗

330a、330b:内连线

具体实施方式

以下实施例中所附的附图是为了能更完整地描述发明概念的示范实施例,但是,仍可使用许多不同的形式来实施本发明,且其不应该被视为受限于所记载的实施例。在附图中,为了清楚起见,膜层、区域及/或结构元件的相对厚度及位置可能缩小或放大。此外,本文使用「第一」、「第二」、「第三」等来描述不同的区域、膜层及/或区块,但是这样的用语仅用于区别一个区域、膜层或区块与另一个区域、膜层或区块。因此,以下所讨论的第一区域、膜层或区块可以被称为第二区域、膜层或区块而不违背实施例的教示。此外,相同或相似的标号表示相同或相似的元件,以下段落将不再赘述。

图1A是依照本发明的第一实施例的一种遮蔽栅金属氧化物半导体场效晶体管的上视示意图。图1B是图1A的I-I线段与II-II线段的结构剖面示意图。

请先参照图1A,第一实施例的遮蔽栅金属氧化物半导体场效晶体管基本上是形成于具有第一导电态的一外延层100中的数个沟槽102内。由虚线圈住的区域是一连线区104,用于线路的连接,但本发明并不限于此,还可利用现有技术进行线路的连接,而省略连线区104。

请同时参照图1A和图1B,本实施例的遮蔽栅金属氧化物半导体场效晶体管包括外延层100、位于外延层100中的沟槽102、位于沟槽102内的遮蔽栅极106、位于沟槽102内的遮蔽栅极106上的控制栅极108、位于遮蔽栅极106与外延层100之间的一绝缘层110、位于控制栅极108与外延层100之间的一栅极氧化层112、位于遮蔽栅极106与控制栅极108之间的栅间氧化层114、位于沟槽底部102a的外延层100内的一第一掺杂区116以及位于沟槽底部102a与第一掺杂区116之间的一第二掺杂区118。其中,第一掺杂区116具有第二导电态,第二掺杂区118具有第一导电态。也就是说,第二掺杂区118与外延层100是相同导电态、第一掺杂区116与外延层100是不同导电态。在一实施例中,第一导电态为N型,第二导电态为P型。在另一实施例中,第一导电态为P型,第二导电态为N型。在本实施例中,第一掺杂区116与第二掺杂区118的掺杂浓度可分别为不同的均匀浓度。至于第二掺杂区118的深度例如小于0.5μm,而第一掺杂区116的深度范围例如在0.5μm~1.5μm之间,且第一掺杂区116的深度范围取决于第二掺杂区118的范围为基准。文中的「深度」是从沟槽底部102a算起,所以第二掺杂区118的深度如果是0.5μm,则是指第二掺杂区118的分布范围从沟槽底部102a到其下方0.5μm之间。然而,本发明并不限于此,一旦遮蔽栅金属氧化物半导体场效晶体管的尺寸设计或电压值V

在图1B中还显示了配置于外延层表面100a的源极区120与接近源极区120的阱区122,其中源极区120具有第一导电态、阱区122具有第二导电态。在一实施例中,第二掺杂区118的掺杂浓度小于源极区120的掺杂浓度。

请同时参照图1A与图1B,外延层100若具有连线区104,则其中的结构可包含延伸至连线区104的沟槽102、延伸至连线区104的沟槽102内的遮蔽栅极106以及一凸出部106a,这个凸出部106a可通过制作工艺,保留连线区104的遮蔽栅极106,作为后续电连接遮蔽栅极106的接触窗。在这种样态中,控制栅极108并未延伸至连线区104。

图2是第一实施例的另一种遮蔽栅金属氧化物半导体场效晶体管的剖面示意图,其中使用与图1B相同的元件符号来表示相同或近似的构件,且相同或近似的构件也可参照上述,不再赘述。

在图2中,遮蔽栅极200被所述栅间氧化层202覆盖的顶面200a具有圆角,可改善上面的栅间氧化层202的沉积品质。而且,根据制作工艺顺序的不同,譬如先热氧化形成栅极氧化层204,再沉积较致密的栅间氧化层202,而使栅间氧化层202与栅极氧化层204的部分位置与图1B不同。

图3A至图3L是依照本发明的第二实施例的一种遮蔽栅金属氧化物半导体场效晶体管的制造流程剖面示意图,且第二实施例的上视图对应图1A的结构。

请先参照图3A,第二实施例的方法是先形成具有第一导电态的一外延层300,再于所述外延层300中形成数个沟槽302。通常形成外延层300的方式是在一基板(未绘示)上利用外延制作工艺形成外延层300。随后,在外延层表面300a形成图案化掩模层(未绘示)定义出沟槽302的位置,再利用图案化掩模层作为掩模,蚀刻外延层300,以得到如图所示的多个沟槽302。而且,形成沟槽302的同时,外延层300的一连线区304内也会形成所述沟槽302。然而,本发明并不限于此,第二实施例也可不具有连线区304;或者,在连线区304之外还具有其他隔离结构,则沟槽302也可形成于连线区304之外,作为其他隔离结构的沟槽。

然后请参照图3B,在每个沟槽底部302a的外延层300内形成具有第二导电态的第一掺杂区306。通常形成第一掺杂区306的方式是在上述图案化掩模层(未绘示)未移除的情况下,对外延层300进行离子注入制作工艺,且注入的是第二导电态的掺质,并利用热制作工艺以驱入掺质;在本实施例中,上述第一导电态为N型,第二导电态为P型。在另一实施例中,上述第一导电态为P型,第二导电态为N型。第一掺杂区306的掺杂浓度可为均匀浓度;或者,形成第一掺杂区306的方法也可以是利用多段式掺杂,以使第一掺杂区的掺杂浓度如图2所示为自沟槽302端到外延层底面300b递增的梯形浓度。

之后,请参照图3C,在每个沟槽底部302a的外延层300内的第一掺杂区306上形成具有第一导电态的第二掺杂区308。形成第二掺杂区308的方式例如是在上述图案化掩模层(未绘示)尚未移除的情况下,对外延层300进行另一离子注入制作工艺,且注入的是第一导电态的掺质,并利用热制作工艺以驱入掺质。因此,第二掺杂区308形成于沟槽底部302a与第一掺杂区306之间。至于第一掺杂区306与第二掺杂区308的示例性的深度范围与浓度范围,均可参照第一实施例的记载,故不再赘述。

接着,为了在每个沟槽302内形成具有遮蔽栅极的金属氧化物半导体场效晶体管,可施行以下制作工艺,但本发明的范围并不限于下列步骤。根据设计需求,也可具有额外的步骤或是省略部分步骤。

请先参照图3D,在每个沟槽302内的外延层表面300c形成一绝缘层310,且绝缘层310的形成例如利用热氧化制作工艺形成一厚氧化层,用以增加击穿电压。

接着请参照图3E,在每个沟槽302内的绝缘层310上形成一导体层312,且导体层312的形成例如在外延层300上沉积一层导体材料(如多晶硅),再利用平坦化制作工艺(如CMP)去除沟槽302以外的导体材料。

然后请参照图3F,移除部分导体层312以形成遮蔽栅极312a并露出部分绝缘层310,且移除方式例如干式蚀刻或者有方向性的湿式蚀刻。此外,可在移除部分导体层312的步骤之前,在连线区304上形成一保护层314,以保留连线区304内的导体层312,其包括遮蔽栅极312a以及一凸出部312b作为后续电连接遮蔽栅极312a的接触窗。

接着请参照图3G,移除露出的绝缘层310,使沟槽302内的部分外延层表面300c暴露出来,且绝缘层310可略低于遮蔽栅极312a的顶面。所述移除方式例如干式蚀刻或湿式蚀刻。

之后请参照图3H,为了改善后续沉积层的品质,可选择性地对遮蔽栅极312a的顶面进行圆角化,而得到略呈半圆的顶面312c。所述圆角化的制作工艺例如先氧化遮蔽栅极312a的顶面,再移除该处的氧化物,其中移除方式例如湿式浸泡(wet dip)。而且,进行圆角化之前可先去除连线区304的保护层314,因此凸出部312b的顶面也会被圆角化,并由连线区304的沟槽302暴露出来。

随后请参照图3I在沟槽302内形成一栅间氧化层316与一栅极氧化层318,其中所述栅间氧化层316覆盖遮蔽栅极312a的顶面312c,且栅极氧化层318覆盖沟槽302内的外延层表面300c。而且,根据制作工艺顺序的不同,譬如先热氧化形成栅极氧化层318,再沉积较致密的栅间氧化层316,则会使栅间氧化层316与栅极氧化层318的部分位置与图3I不同。此时,依据制作工艺顺序的不同,在连线区304的凸出部312b表面可以形成栅间氧化层316或是栅极氧化层318,并且在金属氧化物半导体场效晶体管形成后才会进行后续连线的制作。

接着请参照图3J,于沟槽302内的栅间氧化层316上形成一控制栅极320,且控制栅极320的形成例如在外延层300上沉积一层导体材料(如多晶硅),再利用平坦化制作工艺(如CMP)去除沟槽302以外的导体材料,以完成具有遮蔽栅极312a的金属氧化物半导体场效晶体管。

然后,请参照图3K,在外延层表面300a可形成一源极区322,且源极区322具有第一导电态。在一实施例中,第二掺杂区308的掺杂浓度小于源极区322的掺杂浓度。而在外延层300中还可形成有阱区324,阱区324具有第二导电态,并位于源极区322底下以及栅间氧化层316的上方。

最后,请参照图3L,可在外延层表面300a上依序形成介电层326、介电层326内的接触窗328以及连接接触窗328的不同内连线330a、330b,来进行金属氧化物半导体场效晶体管的连线制作工艺。然而,本发明并不限于此,还可采行其它现有技术来制作。

以下列举几个实验来验证本发明的功效,然而本发明的范围并不局限于以下实验内容。

〈模拟实验例1〉

模拟结构如图1B的遮蔽栅金属氧化物半导体场效晶体管(EPI阻值为0.35Ω·cm/厚度4μm),进行150V

从图4可得到,本发明的结构具有高于152V的击穿电压,且第一掺杂区的掺杂剂量在4E12cm

〈模拟对照例〉

采用与模拟实验例1相同的方式进行模拟,但是并无第二掺杂区。也就是说,例如图1B中沟槽底部仅有与外延层不同导电态的第一掺杂区,并具有下表2所示的掺杂剂量变化与模拟结果。

表2

从表2可得到,没有第二掺杂区的存在,将使整体击穿电压降至143V以下。

综上所述,本发明在遮蔽栅金属氧化物半导体场效晶体管的底部的外延层内形成导电态不同的第一与第二掺杂区,与外延层相同导电态的掺杂区直接接触沟槽底部、与外延层不同导电态的掺杂区则在其下方提供均匀的场分布。因此,能通过与外延层相同导电态的掺杂区来减少元件的漏电路径,进而改善漏极至源极的击穿电压。

虽然结合以上实施例公开了本发明,然而其并非用以限定本发明,任何所属技术领域中具有通常知识者,在不脱离本发明的精神和范围内,可作些许的更动与润饰,故本发明的保护范围应当以附上的权利要求所界定的为准。

- 遮蔽栅金属氧化物半导体场效晶体管及其制造方法

- 金属氧化物半导体场效晶体管及其制造方法