导电通孔的制备方法

文献发布时间:2023-06-19 09:44:49

技术领域

本公开主张2019/07/30申请的美国正式申请案第16/526,007号的优先权及益处,该美国正式申请案的内容以全文引用的方式并入本文中。

本公开涉及一种导电通孔的制备方法。特别涉及一种具有高深宽比的导电通孔的制备方法。

背景技术

半导体元件对于许多现代应用至关重要。随着电子技术的进步,半导体元件的尺寸越来越小的同时,也具有更多的功能和更大量的集成电路。由于半导体元件的小型化,执行不同功能的各种类型和尺寸的半导体元件被整合并封装到单一模块中。此外,实行多种制造操作以将各种类型的半导体元件整合在一起。

然而,半导体元件的制造和整合涉及许多复杂的步骤和操作。半导体元件中的整合变得越来越复杂。半导体元件在制造和整合上复杂性的增加可能引起缺陷,例如导电元件之间的信号干扰。因此,需要持续改进半导体元件的制造制程,才能解决所述缺陷。

上文的“现有技术”说明仅是提供背景技术,并未承认上文的“现有技术”说明公开本公开的标的,不构成本公开的现有技术,且上文的“现有技术”的任何说明均不应作为本公开的任一部分。

发明内容

本公开的一实施例提供一种导电通孔的制备方法。该制备方法包括:形成一第一导电结构于一基板之上;形成一第一介电结构于该第一导电结构之上;将该第一导电结构的一侧壁部分转换为一第一介电部分;以及移除该第一介电部分,使得该第一介电结构的一宽度大于该第一导电结构的一剩余部分的一宽度。

在本公开的一些实施例中,其中在转换该第一导电结构的该侧壁部分之前,该第一导电结构的一侧壁与该第一介电结构的一侧壁实质上共平面。

在本公开的一些实施例中,其中转换该第一导电结构的该侧壁部分的步骤还包括:对该第一导电结构进行一热处理制程,以形成该第一介电部分于该第一导电结构的该剩余部分的相对侧壁之上,其中该第一介电部分的一材料与该第一介电结构的一材料不同。

在本公开的一些实施例中,该热处理制程为一氧化制程或一氮化制程,且该第一介电结构覆盖该第一介电部分。

在本公开的一些实施例中,该导电通孔的制备方法还包括:形成层间介电(inter-layer dielectric;ILD)层,覆盖该第一介电结构的一侧壁,从而形成一第一空气间隔物(air spacer)于该ILD层和该第一导电结构的该剩余部分之间。

在本公开的一些实施例中,该第一空气间隔的一底表面高于该第一导电结构的该剩余部分的一底表面。

在本公开的一些实施例中,该ILD层延伸至该第一导电结构的该剩余部分的一较低侧壁之上且直接接触该第一导电结构的该剩余部分的一较低侧壁。

在本公开的一些实施例中,该导电通孔的制备方法还包括:形成一第二导电结构于该基板之上;形成一第二介电结构于该第二导电结构之上;在形成该第一介电部分期间,将该第二导电结构的一侧壁部分转换为一第二介电部分;以及移除该第二介电部分,使得该第一导电结构的该剩余部分和该第二导电结构的一剩余部分之间的一距离大于该第一介电结构和该第二介电结构之间的一距离。

在本公开的一些实施例中,该导电通孔的制备方法还包括:形成一层间介电(ILD)层,覆盖该第一介电结构的一侧壁,从而形成一第一空气间隔物于该ILD层和该第一导电结构的该剩余部分之间。

在本公开的一些实施例中,该第一空气间隔物的一底表面高于该第一导电结构的该剩余部分的一底表面。

在本公开的一些实施例中,该ILD层覆盖该第二介电结构的一侧壁,从而形成一第二空气间隔物于该ILD层和该第二导电结构的该剩余部分之间,其中该第一介电结构和该第二介电结构分别完全地覆盖该第一空气间隔物和该第二空气间隔物。

本公开的另一实施例提供一种导电通孔的制备方法。该制备方法包括:形成一导电层于一基板之上;形成一介电层于该导电层之上;图案化该介电层和该导电层以形成一第一介电结构、一第二介电结构、一第一导电结构和一第二导电结构,其中一第一开口形成于该第一介电结构和该第二介电结构之间,且一第二开口形成于该第一导电结构和该第二导电结构之间;以及部分地移除该第一导电结构和该第二导电结构以形成一扩大的第二开口。

在本公开的一些实施例中,该扩大的第二开口部分地暴露出该第一介电结构的一底表面和该第二介电结构的一底表面。

在本公开的一些实施例中,该扩大的第二开口的一宽度大于该第一开口的一宽度。

在本公开的一些实施例中,导电通孔的制备方法还包括:在形成该扩大的第二开口之后,沉积一层间介电(ILD)层于该第一开口中,使得该第一导电结构的一较高侧壁通过一第一空气间隔物与该ILD层分离。

在本公开的一些实施例中,该第二导电结构的一较高侧壁通过一第二空气间隔物与该ILD层分离,以及其中该第一介电结构完全地覆盖该第一空气间隔物和该ILD层之间的一界面,且该第二介电结构完全地覆盖该第二空气间隔物和该ILD层之间的一界面。

在本公开的一些实施例中,该第一导电结构的一较低侧壁和该第二导电结构的一较低侧壁直接接触该ILD层。

在本公开的一些实施例中,该ILD层沉积于该第一开口和该扩大的第二开口中,且该第一导电结构的该较高侧壁、该第一介电结构和该ILD层封闭该第一空气间隔物。

在本公开的一些实施例中,该ILD层的一最底表面高于该第一导电结构的一底表面。

本公开的实施例公开的导电通孔结构的制备方法将一导电结构的一侧壁部分转换为一介电部分,再移除该介电部分。将该介电部分移除之后,导电结构之上的介电结构的宽度大于导电结构的剩余部分的宽度,而导电结构的高度则维持相同。换句话说,导电结构的深宽比变得更高,亦即,本公开可制备具有高深宽比(aspect ration)的导电结构作为导电通孔。

上文已相当广泛地概述本公开的技术特征及优点,从而使下文的本公开详细描述得以获得较佳了解。构成本公开的权利要求标的的其它技术特征及优点将描述于下文。本公开所属技术领域中技术人员应了解,可相当容易地利用下文公开的概念与特定实施例可作为修改或设计其它结构或制程而实现与本公开相同的目的。本公开所属技术领域中技术人员亦应了解,这类等效建构无法脱离后附的权利要求所界定的本公开的精神和范围。

附图说明

参阅实施方式与权利要求合并考量附图时,可得以更全面了解本公开的公开内容,附图中相同的元件符号是指相同的元件。

图1是根据本公开的一些实施例的流程图,例示导电通孔的制备方法。

图2至图8是根据本公开的一些实施例的示意图,例示通过图1的制备方法制备导电通孔的各阶段的剖面结构。

图9是根据本公开的一些实施例的示意图,例示半导体元件的剖面结构。

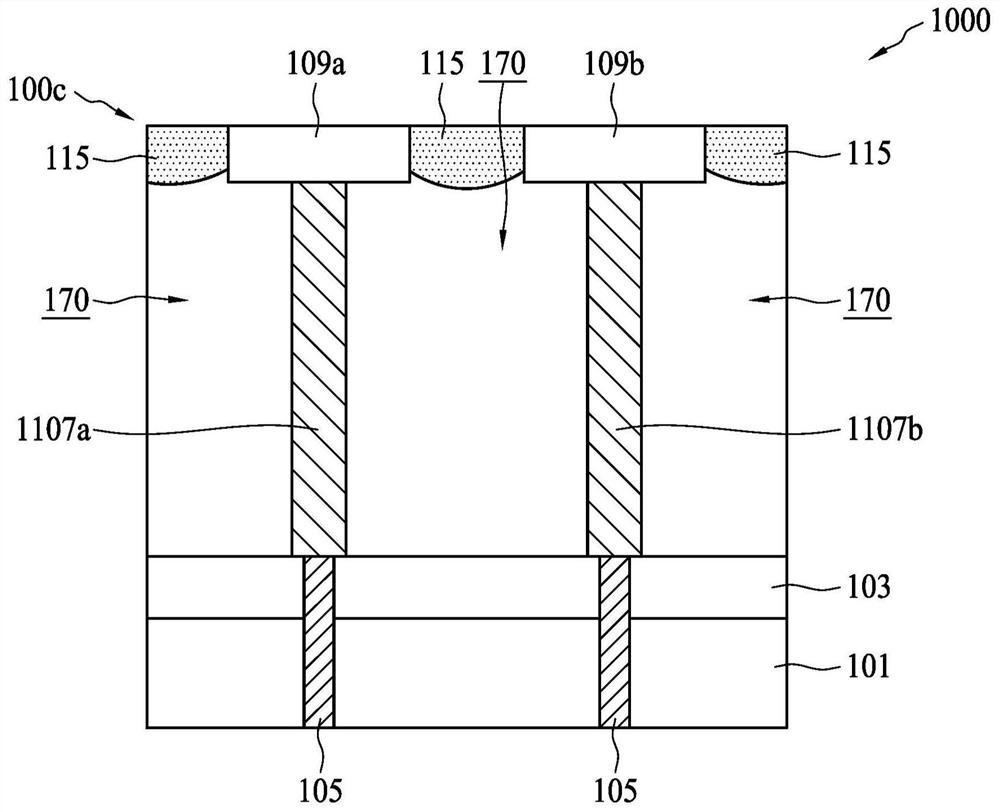

图10是根据本公开的一些实施例的示意图,例示半导体元件的剖面结构。

附图标记说明:

10 制备方法

100a 半导体元件

100b 半导体元件

100c 半导体元件

101 基板

103 介电层

105 导电插塞

107 导电层

107a 导电结构

107b 导电结构

107a' 导电结构的剩余部分

107b' 导电结构的剩余部分

107a” 导电结构的剩余部分

107b” 导电结构的剩余部分

109 介电层

109a 介电结构

109b 介电结构

110 开口

111a 罩幕图案

111b 罩幕图案

113a 介电部分

113b 介电部分

115 层间介电(ILD)层

150 空气间隔物

160 空气间隔物

170 空气间隔物

210 开口

213a 介电部分

213b 介电部分

310' 扩大的开口

1000 第一区域

1107a 导电结构的剩余部分

1107b 导电结构的剩余部分

1310 开口

2000 第二区域

D1 距离

D2 距离

W1 宽度

W2 宽度

W3 宽度

W4 宽度

S11 步骤

S13 步骤

S15 步骤

S17 步骤

S19 步骤

具体实施方式

本公开的以下说明伴随并入且组成说明书的一部分的附图,说明本公开的实施例,然而本公开并不受限于该实施例。此外,以下的实施例可适当整合以下实施例以完成另一实施例。

“一实施例”、“实施例”、“例示实施例”、“其他实施例”、“另一实施例”等是指本公开所描述的实施例可包含特定特征、结构或是特性,然而并非每一实施例必须包含该特定特征、结构或是特性。再者,重复使用“在实施例中”一语并非必须指相同实施例,然而可为相同实施例。

为了使得本公开可被完全理解,以下说明提供详细的步骤与结构。显然,本公开的实施不会限制该技艺中的技术人士已知的特定细节。此外,已知的结构与步骤不再详述,以免不必要地限制本公开。本公开的优选实施例详述如下。然而,除了详细说明之外,本公开亦可广泛实施于其他实施例中。本公开的范围不限于详细说明的内容,而是由权利要求定义。

图1是根据本公开的一些实施例的流程图,例示导电通孔的制备方法。制备方法10包括步骤S11、S13、S15、S17、和S19。

首先简要地介绍图1的步骤S11到S19,接着结合图2到图8进行详细说明。制备方法10始于步骤S11,形成一导电层于一基板之上。在一些实施例中,基板包括各种被动和主动微电子装置,且导电层用来在微电子装置和形成于导电层之上的其他装置之间形成电连接。于步骤S13,形成一介电层于导电层之上。

于步骤S15,图案化介电层和导电层以形成多个介电结构和多个导电结构。在一些实施例中,在介电层之上使用罩幕,以对介电层和导电层进行图案化制程。在图案化制程之后,介电结构的侧壁和导电结构的侧壁实质上(substantially)共平面。于步骤S17,将导电结构的侧壁部分转换为介电部分。在一些实施例中,通过进行热处理制程来形成介电部分。

于步骤S19,移除介电部分。在一些实施例中,介电部分相对于介电结构的蚀刻选择性高。在一些实施例中,在步骤S19之后,形成一层间介电(ILD)层,覆盖介电结构的侧壁。在一些实施例中,形成空气间隔物于ILD层和导电结构的剩余部分之间。

图2-图8是根据本公开的一些实施例的示意图,例示通过图1的制备方法10制备半导体元件100a的各阶段剖面结构。

如图2所示,提供或接收一基板101。在一些实施例中,基板101可包括一半导体基板,像是一硅基板。在一些实施例中,基板101包括其他元素半导体,像是锗(Ge)。在一些实施例中,基板101包括一化合物半导体,像是砷化镓、磷化镓、磷化铟、及/或锑化铟。在一些实施例中,基板101包括一合金半导体,像是SiGe、GaAsP、AlInAs、AlGaAs、GaInAs、GaInP、及/或GaInAsP。或者,基板101可为一绝缘体上半导体(semiconductor-on-insulator)基板,像是绝缘体上覆硅(silicon-on-insulator;SOI)基板、绝缘体上覆硅锗(silicongermanium-on-insulator;SGOI)基板、或绝缘体上覆锗(germanium-on-insulator;GOI)基板。可使用氧植入隔离(separation by implantation oxygen;SIMOX)、晶圆接合、及/或其他合适的方式形成绝缘体上半导体基板。

此外,基板101可为集成电路(IC)芯片的一部分,所述集成电路芯片包括各种被动和主动微电子装置,像是电阻器、电容器、电感器、二极管、p-型场效晶体管(p-type field-effect transistors;pFETs)、n-型场效晶体管(n-type field-effect transistors;nFETs)、金属氧化物半导体场效晶体管(metal-oxide semiconductor field-effecttransistors;MOSFETs)、互补式金属氧化物半导体(complementary metal-oxidesemiconductor;CMOS)晶体管、双极性接面晶体管(bipolar junction transistor;BJT)、横向扩散MOS(laterally-diffused MOS;LDMOS)、高电压晶体管(high-voltagetransistor)、高频率晶体管(high-frequency transistor)、鳍状场效晶体管(fin field-effect transistors;FinFETs)、其他合适的IC元件、或前述的组合。

取决于IC的制造阶段,基板101可包括配置以形成IC部件(例如:掺杂区域、隔离部件、栅极部件、源/漏极部件、内连线部件、其他部件、或前述的组合)的各种材料层(例如:介电层、半导体层、及/或导电层)。例如,如图2所示,介电层103形成于基板101之上。在一些实施例中,介电层103是由氧化硅(SiO

为了清楚起见,简化了图2的基板101。要强调的是,可在基板101中加入额外的部件,且可在其他实施例中置换、修饰、或移除下述的一些部件。

在所述实施例中,形成多个导电插塞105于基板101和介电层103中。更具体地,形成穿过介电层103和基板101的导电插塞105。然而,在其他实施例中,导电插塞105并未穿过基板101。在一些实施例中,设置导电插塞105以在半导体基板101中的装置和形成于介电层103之上的其他装置之间形成电连接。

在一些实施例中,导电插塞105是由铜(Cu)、铝(Al)、银(Ag)、钨(W)、另一种导电材料、或前述的组合构成,且通过蚀刻制程和后续的沉积制程形成导电插塞105。此外,根据一些实施例,导电插塞105可为硅穿孔(through-silicon vias)或基板穿孔(through-substrate vias;TSVs)。

此外,基板101包括一第一区域1000和一第二区域2000。在一些实施例中,基板101的第一区域1000的图案密度大于第二区域2000的图案密度。因此,在这些实施例中,第一区域1000可被称为图案密集区域,像是DRAM中的单元区域(cell region),而第二区域2000可被称为图案稀疏区域,像是DRAM中的外围电路区域。

依然参照图2,制备方法10在步骤S11形成一导电层107于介电层103之上,且制备方法10在步骤S13形成一介电层109于导电层107之上。在一些实施例中,导电层107是由多晶硅(polysilicon)、钨(W)、铝(Al)、铜(Cu)、另一种导电材料、或前述的组合构成,且介电层109是由氧化硅(SiO

因为在第一区域1000(亦即,图案密集区域)中邻近的导电结构之间的交扰(crosstalk)问题(亦即,信号干扰)比第二区域2000(亦即,图案稀疏区域)更为严重,因此对第一区域1000进行接下来的制程。然而,这些仅为示例而非意图用以限制本公开。例如,在一些其他实施例中,同样对第二区域2000进行接下来的制程。

参照图2和图3,制备方法10在步骤S15对介电层109和导电层107进行图案化制程。在一些实施例中,图案化制程始于在介电层109之上形成包括罩幕图案111a和罩幕图案111b的罩幕,其中一开口110形成于罩幕图案111a和111b之间,如图2所示。可通过沉积覆盖介电层109的一罩幕层(未显示)来形成罩幕图案111a和111b。接着,可在罩幕层之上形成图案化光刻胶层(未显示)。

可通过沉积制程或图案化制程来形成图案化光刻胶层。用来形成图案化光刻胶层的沉积制程可包括CVD制程、高密度等离子体化学气相沉积(high-density plasmachemical vapor deposition;HDPCVD)制程、旋涂制程、溅镀制程、或另一种合适的制程。用来形成图案化光刻胶层的图案化制程可包括微影制程和蚀刻制程。微影制程可包括光刻胶涂布(例如:旋涂式涂布)、软烤、光罩对准、曝光、曝光后烘烤、光刻胶显影、冲洗和干燥(例如:硬烤)。蚀刻制程可包括干蚀刻如反应性离子蚀刻(reactive-ion etching;RIE)、湿蚀刻及/或其他蚀刻方法。

在一些实施例中,罩幕层是由氧化硅、氮化硅、氮氧化硅、或另一种合适的材料构成,且可通过一沉积制程来形成罩幕层,所述沉积制程可包括CVD制程、HDPCVD制程、旋涂制程、溅镀制程、或另一种合适的制程。在形成图案化光刻胶层之后,使用该图案化光刻胶层作为罩幕来蚀刻罩幕层。其结果,得到包括罩幕图案111a和111b且在两者之间具有开口110的罩幕。接着,可将该图案化光刻胶层移除。

接下来,如图3所示,使用罩幕图案111a和111b作为罩幕来蚀刻介电层109和导电层107。其结果,介电结构109a和介电结构109b之间形成有开口210,且导电结构107a和导电结构107b之间形成有开口310。在一些实施例中,开口310暴露出介电层103的顶表面。在一些实施例中,同样在第二区域2000中进行步骤S11、S13和S15以在第二区域2000中形成导电结构107a于导电插塞105之上。

要强调的是,使用相同的罩幕对介电层109和导电层107进行蚀刻。因此,在一些实施例中,导电结构107a的侧壁和介电结构109a的侧壁实质上共平面,且导电结构107b的侧壁和介电结构109b的侧壁实质上共平面。在本公开的上下文中,用词“实质上”意味着优选为至少90%、优选为95%、进一步优选为98%、且最佳为99%。

更具体地,介电结构109a和109b完全地覆盖导电结构107a和107b的顶表面。在一些实施例中,如图3的剖面图所示,介电结构109a的宽度和导电结构107a的宽度实质上相同,且被定义为宽度W1。类似地,介电结构109b的宽度和导电结构107b的宽度实质上相同。在形成开口210和310之后,将包括罩幕图案111a和111b的罩幕移除。

如图4所示,制备方法10在步骤S17将导电结构107a的侧壁部分和导电结构107b的侧壁部分转换为介电部分113a和113b。其结果,在导电结构的剩余部分107a'的相对侧壁之上形成介电部分113a,且在导电结构的剩余部分107b'的相对侧壁之上形成介电部分113b。

在一些实施例中,介电结构109a覆盖介电部分113a,且介电结构109b覆盖介电部分113b。在一些实施例中,介电部分113a从介电结构109a的侧壁突出,且介电部分113b从介电结构109b的侧壁突出。然而,介电结构109a和109b分别至少部分地覆盖介电部分113a和113b。

此外,在一些实施例中,通过进行热处理制程来形成介电部分113a和113b,所述热处理制程包括氧化制程、氮化制程、另一种合适的制程、或前述的组合。为了在后续的蚀刻制程期间提供高蚀刻选择性,介电部分113a和113b的材料应不同于介电结构109a和109b的材料。因此,根据介电结构109a和109b的材料来选择应用于热处理制程期间的气体。

例如,如果介电结构109a和109b是由氧化硅构成,氮气可在热处理制程(亦即,氮化制程)期间扩散至导电结构107a和107b的侧壁表面中,且介电部分113a和113b可由氮化物构成,像是氮化硅。

此外,如果介电结构109a和109b是由氮化硅构成,氧气可在热处理制程(亦即,氧化制程)期间扩散至导电结构107a和107b的侧壁表面中,且介电部分113a和113b可由氧化硅(SiO

如图5所示,制备方法10在步骤S19移除介电部分113a和113b。在一些实施例中,通过蚀刻制程来移除介电部分113a和113b。蚀刻制程可包括干蚀刻(例如:RIE)、湿蚀刻及/或其他蚀刻方法。

在一些实施例中,选择介电部分113a、113b和介电结构109a、109b的材料,使得介电部分113a、113b相对于介电结构109a、109b具有高蚀刻选择性。因此,在移除介电部分113a、113b的时候,介电结构109a、109b可实质上保持完整。

在移除介电部分113a、113b之后,得到一扩大的开口310'。要强调的是,导电结构的剩余部分107a'和107b'之间的距离D2(亦即,扩大的开口310'的宽度)大于介电结构109a和109b之间的距离D1(亦即,开口210的宽度),且介电结构109a的宽度W1大于导电结构的剩余部分107a'的宽度W2。类似地,介电结构109b的宽度大于导电结构的剩余部分107b'的宽度。

根据一些实施例,在移除介电部分113a和113b之后,可对导电结构的剩余部分107a'和107b'的侧壁进行第二热处理制程,如图6所示。可选择性地进行第二热处理制程。例如,在一些实施例中,在移除介电部分113a和113b之后,如果达到了导电结构的剩余部分107a'和107b'的预期宽度,则可省略第二热处理制程。

参照图6,在进行第二热处理制程之后,将导电结构的剩余部分107a'和107b'的侧壁部分转换为介电部分213a和213b。其结果,在导电结构的剩余部分107a”和107b”的侧壁之上分别形成介电部分213a和213b。在一些实施例中,导电结构的剩余部分107a”的宽度W3小于在进行第二热处理制程之前的导电结构的剩余部分107a'的宽度W2(如图5所示),且宽度W2小于介电结构109a的宽度W1。

根据一些实施例,在第二热处理制程之后,通过蚀刻制程来移除介电部分213a和213b。接下来,可选择性地进行另一个热处理制程,直到达到导电结构的剩余部分107a”和107b”的预期宽度。

如图7所示,一旦达到预期的宽度,则得到导电结构的剩余部分1107a和1107b。在一些实施例中,导电结构的剩余部分1107a和1107b为硅穿孔(through-silicon vias)或基板穿孔(through-substrate vias;TSVs)。在一些实施例中,导电结构的剩余部分1107a具有一宽度W4,其小于介电结构109a的宽度W1。类似地,导电结构的剩余部分1107b的宽度小于介电结构109b的宽度。

此外,在一些实施例中,开口1310隔离了导电结构的剩余部分1107a和1107b,所述开口1310比图6中扩大的开口310'宽。要强调的是,介电结构109a和109b分别完全地覆盖导电结构的剩余部分1107a和1107b,且导电结构的剩余部分1107a和1107b覆盖导电插塞105。

在一些实施例中,在以硬罩幕覆盖第二区域2000的同时,在第一区域1000中进行步骤S17和S19;因此,第二区域2000中位于导电插塞105之上的导电结构107a保持得与图3所示相同。换句话说,在第一区域1000中作为导电通孔的导电结构的剩余部分1107a和1107b的深宽比高于在第二区域2000中作为导电通孔的导电结构的剩余部分的深宽比。

如图8所示,制备方法10可进一步进行至形成一层间介电(ILD)层115,覆盖介电结构109a和109b的侧壁。因为介电结构109a的宽度W1(参照图7)大于导电结构的剩余部分1107a的宽度W4,ILD层115形成有封闭在介电结构109a、导电结构的剩余部分1107a和ILD层115之间的空气间隔物150。类似地,介电结构109b、导电结构的剩余部分1107b和ILD层115具有封闭在他们之间的空气间隔物150。

要强调的是,导电结构的剩余部分1107a和1107b的较低侧壁直接接触ILD层115,使得空气间隔物150的底表面高于导电结构的剩余部分1107a和1107b的底表面。在一些实施例中,ILD层115形成于开口210和扩大的开口1310中,ILD层115完全地填充开口210,且ILD层115部分地填充扩大的开口1310。更具体地,根据一些实施例,每一个空气间隔物150的宽度沿着介电结构109a和109b到基板101的方向逐渐减小。

此外,通过一沉积制程来形成ILD层115,所述沉积制程像是CVD制程、流动式CVD(flowable CVD;FCVD)制程、HDPCVD制程、ALD制程、旋涂制程、另一种可应用的制程、或前述的组合。在一些实施例中,ILD层115是由氧化硅、氮化硅、氮氧化硅、磷硅玻璃(phosphosilicate glass;PSG)、硼磷硅玻璃(borophosphosilicate glass;BPSG)、低介电常数(low-k)介电材料、及/或其他可应用的介电材料构成。低介电常数介电材料的例子包括但不限于:氟硅玻璃(fluorinated silica glass;FSG)、碳掺杂氧化硅、非晶质氟化碳、聚对二甲苯、双苯基环丁烯(bis-benzocyclobutenes;BCB)、及聚酰亚胺。

在进行用来形成ILD层115的沉积制程之后,可进行一平坦化制程来移除部分的ILD层115和部分的介电结构109a和109b,以校正在之前的蚀刻制程期间形成于介电结构109a和109b中的缺陷。在平坦化制程之后,得到半导体元件100a。

图9是根据本公开的一些实施例的示意图,例示一半导体元件100b的剖面结构。除了空气间隔物的轮廓不同之外,半导体元件100b类似于图8的半导体元件100a。

如图9所示,ILD层115直接接触介电结构109a和109b的底表面,且半导体元件100b的每一个空气间隔物160所占据的面积小于半导体元件100a的每一个空气间隔物150所占据的面积。要强调的是,在选择ILD层115的材料以获得较好的台阶覆盖率(例如,比图8中ILD层115的材料的台阶覆盖率好)时,可得到空气间隔物160的轮廓。

图10是根据本公开的一些实施例的示意图,例示半导体元件100c的剖面结构。除了ILD层的位置不同之外,半导体元件100c类似于图8的半导体元件100a。

如图10所示,ILD层115并未直接接触介电层103的顶表面或导电结构的剩余部分1107a和1107b。此外,ILD层115的底表面高于导电结构的剩余部分1107a和1107b的底表面,且空气间隔物170由介电结构109a和109b、ILD层115、导电结构的剩余部分1107a和1107b、和介电层103所封闭。要强调的是,在选择ILD层115的材料以获得较低的台阶覆盖率(例如,比图8中ILD层115的材料的台阶覆盖率低)时,可得到空气间隔物170的轮廓。

提供半导体元件及用以形成所述半导体元件的实施例。半导体元件(例如:半导体元件100a、100b和100c)的形成方法包括通过进行一个或多个重复的热处理制程将导电结构107a和107b的侧壁部分转换为介电部分(例如:介电部分113a、113b、213a和213b)并移除前述的介电部分,使得每一个介电结构(例如:介电结构109a和109b)的宽度大于每一个导电结构的剩余部分(例如:导电结构的剩余部分107a'、107b'、107a”、107b”、1107a和1107b)的宽度。其结果,在形成覆盖介电结构的侧壁的ILD层115之后,在ILD层115和导电结构的剩余部分之间形成了空气间隔物(例如:空气间隔物150、160和170)。

在导电结构的侧壁之上形成空气间隔物避免了邻近导电结构之间的交扰(亦即,信号干扰),且可改善半导体元件的性能。此外,因为ILD层是在导电结构形成之后才形成于导电结构的相对侧壁之上,故可避免靠近导电结构顶部的夹止(pinch-off)问题并避免在导电结构中产生空隙或接缝。

本公开的一实施例提供一种导电通孔的制备方法。该制备方法包括:形成一第一导电结构于一基板之上;形成一第一介电结构于该第一导电结构之上;将该第一导电结构的一侧壁部分转换为一第一介电部分;以及移除该第一介电部分,使得该第一介电结构的宽度大于该第一导电结构的一剩余部分的宽度。

本公开的实施例公开的导电通孔结构的制备方法将一导电结构的一侧壁部分转换为一介电部分,再移除该介电部分。将该介电部分移除之后,导电结构之上的介电结构的宽度大于导电结构的剩余部分的宽度,而导电结构的高度则维持相同。换句话说,导电结构的深宽比变得更高,亦即,本公开可制备具有高深宽比的导电结构作为导电通孔。

虽然已详述本公开及其优点,然而应理解可进行各种变化、取代与替代而不脱离权利要求所定义的本公开的精神与范围。例如,可用不同的方法实施上述的许多制程,并且以其他制程或其组合替代上述的许多制程。

再者,本公开的范围并不受限于说明书中该的制程、机械、制造、物质组成物、手段、方法与步骤的特定实施例。该技艺的技术人士可自本公开的公开内容理解可根据本公开而使用与本文该的对应实施例具有相同功能或是达到实质上相同结果的现存或是未来发展的制程、机械、制造、物质组成物、手段、方法、或步骤。据此,这些制程、机械、制造、物质组成物、手段、方法、或步骤是包含于本公开的权利要求内。

- 一种TSV导电通孔结构制备方法

- 陶瓷基板导电通孔制备方法