具有CDS功能的Cyclic ADC结构

文献发布时间:2023-06-19 09:57:26

技术领域

本发明涉及CMOS(互补金属氧化物半导体)图像传感器读出电路领域,主要应用于高速高精度的数字域累加型CMOS图像传感器中,尤其涉及Cyclic ADC(循环模数转换电路)读出电路设计。

背景技术

由于工艺和温度等因素,CMOS图像传感器像素单元中晶体管之间存在着一定程度的失配,这些失配会导致像素单元内的固定模式噪声,一般通过CDS(相关双采样)结构来对像素输出的模拟信号进行处理,消除这部分噪声,再将处理后的模拟信号送入ADC(模数转换电路)内进行模数转换。目前的Cyclic ADC读出电路中大部分都是在ADC的前面单独加入一个CDS电路,完成对像素输出信号的CDS和放大处理,但是这部分电路会额外增加读出电路的面积和功耗;还有一部分电路将CDS功能加入到ADC电路中去,节省了面积和功耗,但是转换速度和精度不够高。

发明内容

针对现有技术存在的问题,本发明提出了一种具有CDS功能的Cyclic ADC结构,旨在以尽可能小的面积和功耗来实现高速高精度的Cyclic ADC读出电路。提出的这种读出电路不仅具有基本的CDS功能,还可以通过可编程的电容阵列来实现对信号的增益调节功能。

(1)整体结构框架

Cyclic ADC的整体结构如下,主要包括一个1.5bit的比较器即子ADC、一个1.5bit的数模转换电路即子DAC、一个乘二运算放大器和一个RSD编码电路,其中子DAC和乘二运算放大器共同组成了MDAC即乘法DAC,本发明所提出的CDS功能就是通过改进的MDAC电路结构来实现的;

Cyclic ADC的具体工作方式如下:在第一个循环时开关打到V

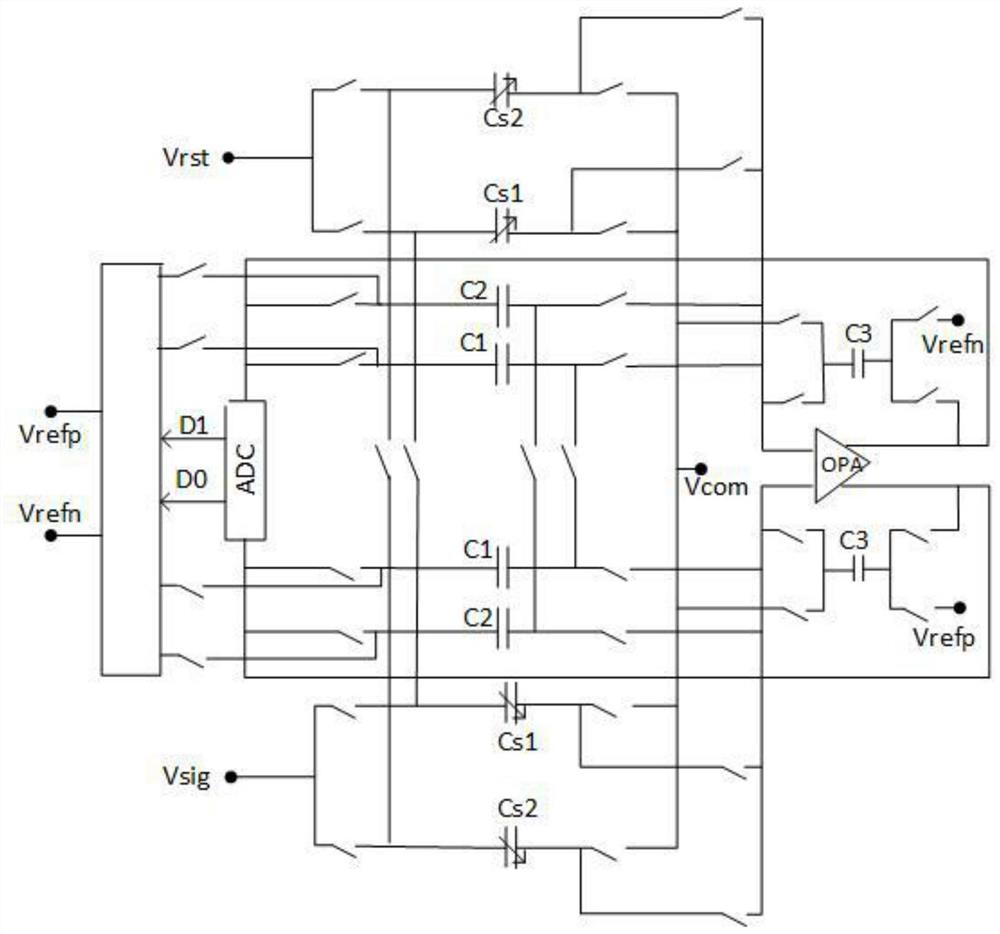

(2)MDAC结构及工作原理

第一级和第二级ADC的MDAC采用相同的电路结构,由若干开关和采样保持电容组成。信号采样和量化流水进行,采样电容Cs1和Cs2交替采样信号,当Cs1采样前端输入的复位信号和曝光信号的同时,Cs2对前一组采样的信号进行放大和模数转换,实现了信号的采样和处理的交替进行。由于同时采样了像素的复位信号和曝光信号,在放大阶段对其进行了放大处理,因此实现了CDS操作。另外可以通过控制Cs1和Cs2的大小来实现增益调节的功能。

(3)运放设计

两级运算放大器均采用全差分折叠式共源共栅结构来实现,其中第一级运放在折叠式共源共栅结构的基础上另外添加增益提升结构即Gain-boosting结构来进一步增大第一级运放的增益和精度。

(4)比较器

本发明采用了一种可以降低等效输入失调电压的动态比较器结构,Latch的高低电平控制晶体管的状态,通过正反馈结构放大晶体管状态引起的电流失配,最终输出数字量。该比较器结构简单、无静态功耗且速度很快。

该发明将CDS功能集成在14位的Cyclic ADC中,不仅实现了ADC的高速和高精度,而且比传统的Cyclic ADC节省了面积和功耗。

附图说明

图1是Cyclic ADC整体结构框架图;

图2是MDAC电路结构图;

图3是全差分折叠式共源共栅结构运放电路图;

图4是Gain_boosting结构电路图;

图5是动态锁存型比较器电路图。

具体实施方式

以下根据附图和实施例对本发明进行详细说明,但是本发明的保护范围不限于此。

图1以结构框图的方式阐明Cyclic ADC的工作方式:在第一个循环时开关打到V

本ADC实现的位数是14位,分为两级实现,第一级ADC完成高6位的信号转换;第二级ADC完成低8位的信号转换。每一级都分别按照上述的工作方式实现。

图2为本发明的核心电路,即实现了CDS功能的MDAC电路部分。电路由若干电容和开关组成。通过时钟控制开关的交替通断,使采样电容Cs1和Cs2交替采样信号,实现了信号采样和量化的流水操作。由于同时采样了像素的复位信号和曝光信号,在放大阶段对其进行了放大处理,因此实现了CDS操作。另外可以通过控制Cs1和Cs2的大小来实现增益调节的功能。在采样阶段,连接Vrst和Vsig的开关导通,将输入信号电压存储在采样电容Cs上;而量化阶段,输入连接到DAC模块输出的余差信号端口,采样上一周期输出的余差信号,从而实现Cyclic的量化操作。

运算放大器采用全差分折叠式共源共栅结构,如图3所示。第一级运放的要求较高,经计算,需满足带宽

本发明中比较器采用动态锁存型比较器结构,如图5所示,当latch变为高电平时,M6—M7处于线性区,而晶体管M2—M5都处于饱和区,M2—M5的失调是产生比较器失调的主要因素,但由于其增益较大,因此可以降低比较器的等效输入失调电压。

该发明采用3.3V的Vdd电源,正参考电压Vrefp为2.3V,负参考电压Vrefn为1V,共模电压1.65V,最终可以实现-1.3V~+1.3V的差分摆幅。第一级ADC每个循环用时160ns,第二级ADC信号采样用时160ns,之后的每个循环用时100ns。第一级运放尾电流取70uA,每个Gain_boosting预计消耗10uA电流;第二级运放尾电流取35uA。在这样大致的设计参数下,预计该Cyclic ADC可以实现14位的高速高精度数据转换。

- 具有CDS功能的Cyclic ADC结构

- 一种具有浮渣检测功能的CD测试结构