检测处理器运行状态的装置和方法

文献发布时间:2023-06-19 10:02:03

技术领域

本公开涉及一种检测处理器运行状态的装置和方法。

背景技术

诸如车用芯片等芯片在功能安全方面具有很高的要求,并且要求能够检测出单点故障。始终期望能够具有更加高效的故障检测手段。

发明内容

根据本公开的一个方面,提供了一种检测处理器运行状态的装置。该装置可以包括:随机数发生器;多个多路选择器,每个多路选择器的第一数据输入端和第二数据输入端分别耦接到前述装置的数据输入端和前述随机数发生器的输出端,并且每个多路选择器被配置为响应于测试使能信号,选择经由该多路选择器的数据输出端输出经由该多路选择器的第二数据输入端输入的数据;多个多路分配器,每个多路分配器的第一数据输出端和第二数据输出端分别耦接到前述装置的数据输出端和检测电路,并且每个多路分配器被配置为响应于前述测试使能信号,选择经由该多路分配器的第二数据输出端输出经由该多路分配器的数据输入端输入的数据;运算器阵列,包括多个运算器,前述多个运算器中的每个运算器的每个数据输入端耦接到对应的多路选择器的数据输出端,并且每个运算器的数据输出端耦接到对应的多路分配器的数据输入端;以及前述检测电路,被配置为根据经由前述多个多路分配器接收的数据检测前述处理器的运行状态。

根据本公开的另一个方面,还提供了一种检测处理器运行状态的方法。该方法可以包括:响应于测试使能信号,将由随机数发生器产生的随机数传送给运算器阵列中的每个运算器;响应于前述测试使能信号,将每个运算器基于前述随机数执行运算所得到的数据传送给检测电路;以及响应于前述测试使能信号,启动前述检测电路,以根据所接收的数据检测前述处理器的运行状态。

根据本公开的另一个方面,还提供了一种计算机可读存储介质。该存储介质存储有用于执行上述方法的计算机程序。

根据本公开的另一个方面,还提供了一种电子设备。该电子设备可以包括处理器和用于存储处理器可执行指令的存储器,其中,处理器可以用于从存储器中读取用以实现上述方法的可执行指令。

根据本公开的实施例的装置和方法,能够以较低的成本高效率地实现处理器和/或处理器中的运算器阵列的硬件自动检测,而不会降低处理器的处理性能,并且不会消耗额外的存储资源。

附图说明

通过结合附图对本公开实施例进行更详细的描述,本公开的上述以及其他目的、特征和优势将变得更加明显。附图用来提供对本公开实施例的进一步理解,并且构成说明书的一部分,与本公开实施例一起用于解释本公开,并不构成对本公开的限制。在附图中,相同的参考标号通常代表相同部件或步骤。

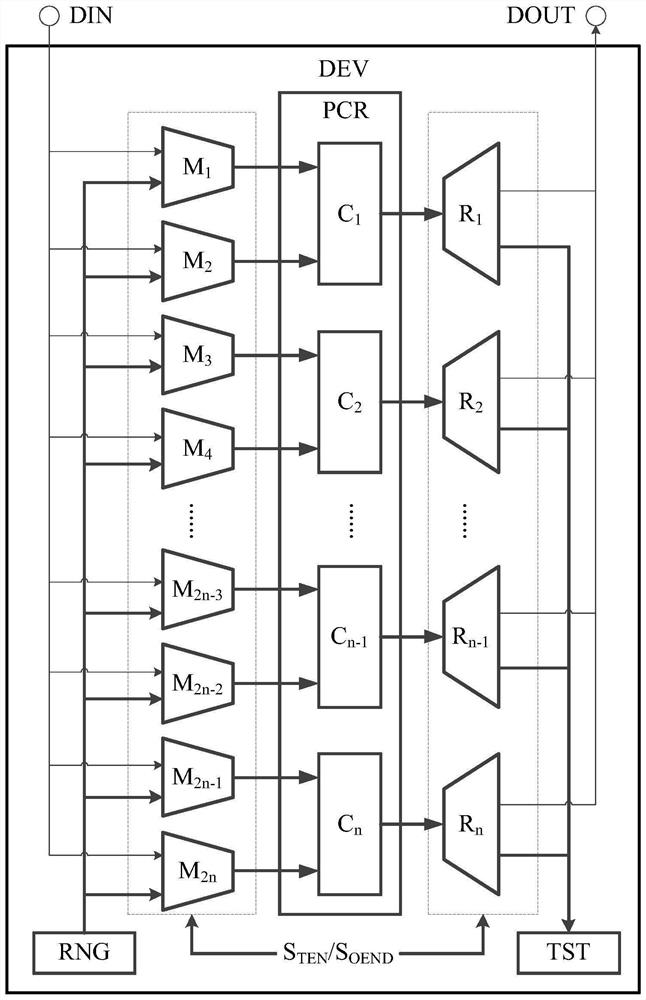

图1是根据本公开的实施例的装置的示例。

图2是根据本公开的实施例的装置的示例。

图3是根据本公开的实施例的装置的示例。

图4是根据本公开的实施例的装置的示例。

图5是根据本公开的实施例的信号的示例。

图6是根据本公开的实施例的装置的示例。

图7是根据本公开的实施例的装置的示例。

图8是根据本公开的实施例的方法的示例。

图9是根据本公开的实施例的方法的示例。

图10是根据本公开的实施例的方法的示例。

图11是根据本公开的实施例的电子设备的示例。

具体实施方式

下面,将参考附图详细地描述根据本公开的示例实施例。显然,所描述的实施例仅仅是本公开的一部分实施例,而不是本公开的全部实施例,应理解,本公开不受这里描述的示例实施例的限制。

对于芯片的单点故障,已经提出例如基于逻辑内建自检测(Logic Build-in SelfTest,LBIST)技术、基于双核(Dual-core)技术或基于软件等不同的故障检测手段。

LBIST能够检测永久型单点故障,但是运行时间较长,对于芯片性能的影响较为明显。基于双核技术的检测手段能够实时地检测瞬时型单点故障,但是对于例如神经网络加速器这样的可能包括大量运算器(例如,神经网络加速器中的乘加单元数量通常可以是数千个),采用双核技术将显著地增加硬件成本。基于软件的检测手段无法实时地检测故障且无法确保检测的覆盖率。另外,故障检测软件的运行影响芯片的处理器/处理模块的正常功能的执行,并且用于中间数据的存储成本较高。

根据本公开的实施例的装置和方法旨在解决或缓解上述的一个或多个技术问题。

图1示出根据本公开的实施例的检测处理器运行状态的装置的示例。

如图1所示,根据本公开的实施例的检测处理器PCR运行状态的装置DEV可以包括:随机数发生器RNG;多个多路选择器M

根据不同的实施例,装置DEV中的运算器阵列可以是装置DEV中的处理器PCR的一部分,也可以对应于装置DEV的处理器PCR。

如图1所示,在装置DEV中,对于处理器PCR中的多个运算器C

处理器PCR中的运算器阵列可以具有任何适当的结构。在一个实施例中,每个运算器C

在一个实施例中,装置DEV的处理器PCR中的多个运算器C

在另外的实施例中,装置DEV的处理器PCR中的多个运算器C

在装置DEV中,对于多个多路选择器M

在一个实施例中,每个多路选择器M

根据不同的实施例,装置DEV中的随机数发生器RNG可以包括一个或多个相同或不同的硬件随机数发生器(也称为真随机数发生器)和/或一个或多个相同或不同的伪随机数发生器(例如,线性同余发生器等)。本公开不局限于随机数发生器RNG的类型和实现方式。

根据不同的实施例,随机数发生器RNG可以被配置为针对每个多路选择器M

在一个实施例中,装置DEV中的运算器阵列可以在一个或多个周期(在下文中也称为“输入周期”)接收输入,并在随后的一个或多个周期(在下文中也称为“输出周期”)输出运算结果。相应地,随机数发生器RNG还可以被配置为按时序产生与运算器阵列的输入周期中的每个周期相对应的一个多个随机模式(pattern)或随机数据,使得运算器阵列可以在相应的输入周期中的各个周期经由对应的多路选择器从随机数发生器RNG接收对应的随机模式或随机数据,并且根据所接收的各个随机模式或随机数据执行运算,然后在输出周期中的各个周期经由对应的多路分配器向测试电路TST输出运算结果或运算结果的各个部分。

根据不同的实施例,随机数发生器RNG可以直接或间接地耦接到多路选择器M

在一个实施例中,随机数发生器RNG也可以被配置为响应于测试使能信号S

在装置DEV中,对于多个多路分配器R

在一个实施例中,每个多路分配器R

装置DEV中的检测电路TST可以被配置为根据经由来自多路分配器的数据检测处理器PCR的运行状态。例如,检测电路TST可以被配置为检测来自各个多路分配器的数据是否一致(例如,是否相同,经过求和运算后得到的值是否为零,来自运算器阵列的数据序列中的数据项的次序是否一致,等等),并且可以在确定存在不一致的数据的情况(例如,来自某两个多路分配器的数据不相同,或者来自各个多路分配器的数据之和不为零,等等)下,可以输出指示处理器PCR和/或处理器PCR中的运算器阵列发生故障的信号。

在不同的实施例中,根据预定的检查规则,检测电路TST可以包括例如加法器、数值比较器、计分板电路等各种适当的电路或元件。另外,根据不同的实施例,检测电路TST可以被配置为响应于在输入端检测到输入信号(输入数据)和/或测试使能信号S

在图1所示的装置DEV中,通过设置随机数发生器RNG和多路选择器阵列,允许处理器PCR中的运算器基于来自随机数发生器RNG的随机数而不是来自装置DEV的数据输入端DIN的数据执行运算。另外,还通过设置检测电路TST和多路分配器阵列,允许将处理器PCR或处理器PCR中的各个运算器的运算结果输出到检测电路TST以便进行数据一致性检测,而不是经由装置DEV的数据输出端DOUT输出。而且,通过信号(例如,测试使能信号S

由于可以不需要额外的软件控制,根据本公开的实施例的装置能够确保处理器PCR的处理性能不降低,且不需要额外的存储开销,并且能够实时地进行故障检测。

另外,根据本公开的实施例的装置DEV中的每个多路选择器M

因此,根据本公开的实施例的装置能够通过成本较低的硬件,自动且快速地检测处理器PCR和/或处理器PCR中的运算器的永久型单点故障和瞬间型单点故障。

在一个实施例中,对于第一类运算器阵列,如图1所示,测试使能信号S

根据本公开的实施例的装置DEV中的处理器PCR可以根据预定的指令序列执行操作,或者说,处理器PCR可以根据预定的指令序列控制其内部的运算器阵列执行操作。因此,总是可以确定处理器PCR或处理器PCR中的运算器阵列的期望运算/处理的操作/指令序列何时开始、何时结束。

例如,可以针对处理器PCR中的运算器阵列发出阵列操作结束信号S

然后,可以将由处理器PCR或处理器中的运算器阵列发出的阵列操作结束信号S

由此,能够利用已有的信号设计来允许处理器PCR或处理器PCR中的运算器阵列从操作/运算模式自动且无缝地转换到故障检测模式,无需额外的触发信号或控制指令或信号触发电路。

在另一个实施例中,装置DEV还可以包括信号触发电路。

如图2所示,对于第一类运算器阵列,该信号触发电路SGC可以被配置为响应于测试指令信号和被设置的测试使能标志中的至少一个以及由运算器阵列发出的阵列操作结束信号S

例如,可以在程序设计阶段,在用于控制处理器PCR或处理器PCR中的运算器执行操作的程序指令中插入测试指令。然后,例如装置DEV或处理器PCR中的指令解析器可以在检测到测试指令时向信号触发电路SGC发出测试指令信号。例如,可以在装置DEV或处理器PCR中设置测试使能标志寄存器,并且例如装置DEV或处理器PCR中的指令解析器可以在检测到测试指令时在测试使能标志寄存器中设置测试使能标志。另外,测试使能标志也可以根据来自装置DEV外部的输入或者针对装置DEV的硬件或软件上的预先或实时的配置来设置。然后,信号触发电路SGC可以被配置为响应于测试指令信号和被设置的测试使能标志中的至少一个以及由运算器阵列发出的阵列操作结束信号S

由此,可以通过结合另外的控制(例如,软件控制)来有计划地启动针对处理器PCR或处理器中的运算器阵列的故障检测,从而能够避免使处理器PCR或处理器中的运算器阵列总是在执行运算/处理或自检测操作,能够有效地控制功耗,并且有利于延长元件寿命。

在另外的实施例中,例如针对前述的第二类运算器阵列,信号触发电路SGC可以被配置为在处理器PCR的运算器阵列中的每个运算器均处于空闲状态的期间,触发测试使能信号S

例如,可以针对每个运算器设置一个标志位,该标志位可以响应于对应的运算器发出的操作结束信号而被置1,并且可以响应于向对应的运算器提供操作开始信号或者对应的运算器接收到操作开始信号而被置0。然后,信号触发电路SGC可以在所有运算器的标志位均为1(例如,可以通过与门进行判断)的情况下,触发测试使能信号(例如,与门的输出为1),并且可以在有一个或多个标志为0的情况下,触发测试停止信号(例如,与门的输出为0)。

于是,测试周期是运算器阵列中的各个运算器同时处于空闲期间的交集。由此,即使在例如第二运算器阵列这样的包括多个不具有重复性的计算资源的运算器阵列的情况下,也能够确保故障检测的正确执行,并且能够确保检测的覆盖率。

进一步地,信号触发器还可以被配置为在每个运算器均处于空闲状态的期间,响应于测试指令信号和被设置的测试使能标志中的至少一个,触发测试使能信号S

例如,如前文所述,测试指令信号可以对应于测试指令的解析结果。例如,可以针对操作指令和测试指示设置相应的指令码或指令位。例如,某个比特为1表示“操作指令”,为0表示“测试指令。然后,可以使用例如与门和/或非门等逻辑元件确定指令类型。例如,可以用高电平信号表示测试指令信号。然后,可以使用与门元件等确定是否同时接收到测试指令和操作结束信号。

另外,针对前述的第二类运算器阵列,信号触发电路SGC还可以与运算器阵列中的每个运算器或包括每组运算器的子阵列耦接在一起,以针对各个运算器或各组运算器,独立地发送测试使能信号S

通过在装置DEV中包括信号触发电路,允许结合另外的控制(例如,软件控制)来有计划地启动针对处理器PCR或处理器中的运算器阵列的故障检测,从而能够避免过多的功耗,并有利于延长元件寿命。

如前文所述,每个多路选择器M

对应地,在一个实施例中,如图3中的粗线箭头所示,每个多路选择器M

由此,使得根据本公开的实施例的装置能够从检测模式切换至常规的运算/操作模式,以便根据经由数据输入端DIN接收的数据执行预定运算/操作,并经由数据输出端DOUT输出运算/操作结果,从而实现常规运算/操作。

在一个实施例中,如图3所示,测试停止信号S

如前文所述,装置DEV中的处理器PCR可以根据预定的指令序列执行操作,或者说,处理器PCR可以根据预定的指令序列控制其内部的运算器阵列执行操作。因此,总是可以确定处理器PCR或处理器PCR中的运算器阵列的期望运算/处理的操作/指令序列何时开始、何时结束。

阵列操作开始信号S

通过使用提供给运算器阵列的阵列操作开始信号S

如前文所述,根据本公开的实施例的装置DEV还可以包括信号触发电路SGC。

装置DEV中的处理器PCR或处理器PCR中的运算器阵列或运算器阵列中的运算器可以被配置为知道当前所处的模式是操作/运算模式还是测试模式,例如,可以通过设置相应的模式标志寄存器等。在这样的情况下,在模式切换时,处理器PCR或处理器PCR中的运算器阵列或运算器阵列中的运算器可以根据要切换到的模式向信号触发电路SGC发出对应的信号,也可以通过设置/修改对应的标志以使信号触发电路SGC能够知道接下来要触发测试使能信号S

在另外的示例中,装置DEV中的处理器PCR或处理器PCR中的运算器阵列或运算器阵列中的运算器也可以被配置为不必关心当前所处的模式如何。在这样的情况下,至少在运算器阵列内部,操作/运算模式和测试模式实质上是没有差异。在这样的情况下,如图4所示,信号触发电路SGC可以被配置为在触发测试使能信号S

也就是说,例如,如图5所示,信号触发电路SGC可以响应于第一阵列操作结束信号S

在该情况下,信号触发电路SGC或运算器阵列的操作还可以包括重置测试使能标志(如果有)等,以便在第二阵列操作结束信号S

应当理解,图5的信号触发(下降沿触发)仅为示例。根据本公开的实施例的装置的信号及信号触发方式不局限于上述示例,例如,也可以使用上升沿触发的方式等。另外,如前文所述,由于测试使能信号S

如前文所述,通过在装置DEV中包括信号触发电路,允许结合另外的控制(例如,软件控制)来有计划地启动和停止针对处理器PCR或处理器中的运算器阵列的故障检测,从而能够避免过多的功耗,并有利于延长元件寿命。

根据处理器PCR或处理器PCR中的运算器阵列或运算器阵列中的运算器要执行的运算类型、输出的数据类型等,检测电路TST可以被配置为实现任何适当的比对规则,并且相应地,根据不同的实施例,可以包括加法器、数值比较器、一个或多个逻辑门元件、计分板电路等一个或多个适当的电路模块或元件。

例如,检测电路可以包括一个或多个异或门元件,每个异或门可以具有两个或更多的输入端,所有异或门的所有输入端的数量可以与装置DEV中的所有多路分配器R

例如,在经由多路分配器从至少两个运算器接收的至少两个运算结果是否一致的情况下,如图6所示,检测电路TST可以包括至少一个加法器(图6中示出在TST中包括至少两个加法器,在另外的示例中也可以只有一个加法器),并且检测电路TST可以被配置为在检测到这样的至少一个加法器中的任何加法器的输出结果不是零的情况下输出指示处理器PRC或处理器PRC中的运算器阵列发生故障的信号。

例如,可以控制随机数发生器RNG生成适当的一个或多个随机数,使得在各个运算器C

在某个运算器发生故障的情况下,例如在图6的示例中,运算器C

在一个实施例中,代替加法器或在加法器的基础上,检测电路TST可以包括常规的计分板电路。

在一些实施例中,指示运算器阵列发生故障的信号还可以包括与故障有关的任何息,例如还可以包括用于指示运算器阵列中的哪个(些)或者可能哪个(些)运算器发生了故障的信息。例如,在图6的示例中,指示运算器阵列发生故障的信号可以进一步指示运算器C

对于例如卷积神经网络芯片等包括很多加法器的芯片/装置/模块来说,在通过加法器来配置检测电路TST的情况下,可以重用卷积加速模块中的加法器阵列来实现检测电路TST,因此能够在不增加硬件成本和芯片尺寸的情况下实现故障的自检测,因此是非常有利的。

例如,在装置DEV是例如卷积加速模块这样的装置的情况下,装置DEV的处理器PCR或处理器PCR中的运算器阵列中的每个运算器可以包括乘法器。

在这样的情况下,在一个实施例中,随机数发生器RNG的第一数据输出端可以经由对应的多路选择器耦接到运算器阵列中的第一运算器的第一数据输入端和第二运算器的第一数据输入端。

例如,如图7所示,随机数发生器RNG输出a的第一数据输出端可以经由对应的多路选择器M

随机数发生器RNG的第二数据输出端可以经由对应的多路选择器耦接到第一运算器的第二数据输入端,并且随机数发生器RNG的第二数据输出端可以经由取反逻辑和对应的多路选择器耦接到第二运算器的第二数据输入端。例如,在图7的示例中,随机数发生器RNG输出b的第二数据输出端可以经由在RNG与M

然后,如图7所示,第一运算器C

在一个实施例中,检测电路TST中的加法器可以重用运算器阵列中的加法器(未示出)来实现。

由此,装置DEV能够以较低的成本高效率地实现处理器和/或处理器中的运算器阵列的硬件自动检测,而不会降低处理器的处理性能,并且不会消耗额外的存储资源。

应当理解,根据本公开的实施例的装置不局限于上述示例。例如,运算器阵列中的每个运算器可以是用于从至少两个输入数据中确定最大值或最小值的处理电路或模块。在这样的情况下,在检测电路TST中,代替加法器,可以设置例如异或门(或者能够实现异或逻辑的电路,或者能够与异或逻辑获得相同或等效的比对结果的逻辑电路)或数值比较器等模块/电路/元件,并且在来自作为当前检测对象的至少两个运算器的处理结果不一致的情况下,输出处理器PRC或处理器PRC中的运算器阵列或某个(些)运算器发生故障的信号。另外,在上述示例中,运算器阵列中的各个运算器被示为具有2个输入端,但是在另外的实施例中,运算器阵列中的各个运算器也可以具有1个、3个或更多的输入端,并且相应地,与每个运算器相连的多路选择器的数量也可以是例如1个、3个或更多个,而不局限于上述示例中的2个。另外,在上述示例中,运算器阵列中的各个运算器被示为具有1个输出端,但是在另外的实施例中,运算器阵列中的各个运算器也可以具有2个、3个或更多的输入端,并且相应地,与每个运算器相连的多路分配器的数量也可以是例如2个、3个或更多个,而不局限于上述示例中的1个。

图8示出根据本公开的实施例的检测处理器运行状态的方法的示例流程。该方法可以用于控制前文所述的根据本公开的实施例的装置进行处理器运算状态的自检测,或者说,前文所述的根据本公开的实施例的装置可以按照与该方法的步骤相对应的过程自动或受控地进行处理器运算状态的自检测。

如图8所示,根据本公开的实施例的方法可以包括:

步骤S110,响应于测试使能信号,将由随机数发生器产生的随机数传送给运算器阵列中的每个运算器;

步骤S120,响应于前述测试使能信号,将每个运算器基于前述随机数执行运算所得到的数据传送给检测电路;以及

步骤S130,响应于前述测试使能信号,启动检测电路,以根据所接收的数据检测处理器的运行状态。

在一个实施例中,运算状态的检测可以包括由检测电路检测来自各个运算器的运算结果数据是否一致(例如,是否相同,经过求和运算后得到的值是否为零,等等),并且可以在确定存在不一致的数据的情况(例如,数据不相同,或者数据之和不为零,等等)下,可以输出指示处理器和/或处理器中的运算器阵列和/或运算器阵列中的某个(些)运算器发生故障的信号。

如前文针对根据本公开的实施例的装置的描述中所述,检测电路的启动和停止可以根据信号自动无缝地切换,也可以在此基础上进一步根据另外的软件控制来切换。

例如,图9示出控制检测电路在进行和停止故障检测之间进行切换一个示意过程。在该示例中,测试使能信号S

图10示出控制检测电路在进行和停止故障检测之间进行切换另一个示意过程。在该控制过程中,加入了额外的软件控制,即,可以在程序设计阶段,在用于控制处理器或处理器中的运算器执行操作的程序指令中插入测试指令。然后,例如装置或处理器中的指令解析器可以在检测到测试指令时向信号触发电路发出测试指令信号S

控制根据本公开的实施例的装置的方法或者根据本公开的实施例的装置的操作过程不局限于上述示例。例如,根据另外的实施例,还可以根据被设置的测试使能标志中的至少一个以及由运算器阵列发出的阵列操作结束信号,来触发测试使能信号S

图11示出根据本公开的实施例的电子设备的示例。

如图11所示,该电子设备ED包括前文所述的根据本公开的实施例的装置DEV。

另外,电子设备ED还可以包括一个或多个另外的处理器(未示出),这些另外的处理器可以是中央处理单元(CPU)或者具有数据处理能力和/或指令执行能力的其他形式的处理单元,并且可以控制电子设备ED中的其他组件以执行期望的功能和/或与装置DEV相配合以实现期望的功能。

如图11所示,电子设备ED还可以包括存储器STR。存储器STR可以存储一个或多个计算机程序产品,并且可以包括各种形式的计算机可读存储介质,例如易失性存储器和/或非易失性存储器。易失性存储器例如可以包括随机存取存储器(RAM)和/或高速缓冲存储器(cache)等。非易失性存储器例如可以包括只读存储器(ROM)、硬盘、闪速存储器等。

装置DEV或者前述的另外的一个或多个处理器可以读取例如在STR中存储的一个或多个计算机程序指令并运行,以实现上文所述的本公开的各个实施例的方法以及/或者其他期望的功能。

如图11所示,在一些实施例中,电子设备ED还可以包括输入装置INP和输出装置OUTP,其中,这些组件通过总线系统和/或其他形式的连接机构(未示出)互连。根据不同的实施例,输入设备INP可以包括例如键盘、鼠标等,并且输出装置OUTP可以并且可以包括例如显示器、扬声器、打印机、以及通信网络及其所连接的远程输出设备等以便向外部输出各种信息。

为了简化,图11中仅示出了该电子设备ED中的一些示例性部件,而省略了诸如总线、输入/输出接口等的其他组件。除此之外,根据具体应用情况,电子设备ED还可以包括任何其他适当的组件。

除了上述方法和设备以外,本公开的实施例还可以是计算机程序产品,其包括计算机程序指令,该计算机程序指令在被处理器运行时使得处理器执行本说明书上述“示例性方法”部分中描述的根据本公开各种实施例的方法中的步骤。

计算机程序产品可以以一种或多种程序设计语言的任意组合来编写用于执行本公开实施例操作的程序代码,程序设计语言可以包括面向对象的程序设计语言,诸如Java、C++等,还包括常规的过程式程序设计语言,诸如“C”语言或类似的程序设计语言。程序代码可以完全地在用户计算设备上执行、部分地在用户设备上执行、作为一个独立的软件包执行、部分在用户计算设备上部分在远程计算设备上执行、或者完全在远程计算设备或服务器上执行。

此外,本公开的实施例还可以是计算机可读存储介质,例如计算机可读取的非临时性存储介质,其上存储有程序指令,程序指令在被处理器运行时使得处理器执行本说明书上述“示例性方法”部分中描述的根据本公开各种实施例的方法中的步骤。

计算机可读存储介质可以采用一个或多个可读介质的任意组合。可读介质可以是可读信号介质或者可读存储介质。可读存储介质例如可以包括但不限于电、磁、光、电磁、红外线、或半导体的系统、装置或器件,或者任意以上的组合。可读存储介质的更具体的例子(非穷举的列表)包括:具有一个或多个导线的电连接、便携式盘、硬盘、随机存取存储器(RAM)、只读存储器(ROM)、可擦式可编程只读存储器(EPROM或闪速存储器)、光纤、便携式紧凑盘只读存储器(CD-ROM)、光存储器件、磁存储器件、或者上述的任意合适的组合。

以上结合具体实施例描述了本公开的基本原理,但是,需要指出的是,在本公开中提及的优点、优势、效果等仅是示例而非限制,不能认为这些优点、优势、效果等是本公开的各个实施例必须具备的。另外,上述公开的具体细节仅是为了示例的作用和便于理解的作用,而非限制,上述细节并不限制本公开为必须采用上述具体的细节来实现。

本公开中涉及的器件、装置、设备、系统的方框图仅作为例示性的例子并且不意图要求或暗示必须按照方框图示出的方式进行连接、布置、配置。如本领域技术人员将认识到的,可以按任意方式连接、布置、配置这些器件、装置、设备、系统。诸如“包括”、“包含”、“具有”等等的词语是开放性词汇,指“包括但不限于”,且可与其互换使用。这里所使用的词汇“或”和“和”指词汇“和/或”,且可与其互换使用,除非上下文明确指示不是如此。这里所使用的词汇“诸如”指词组“诸如但不限于”,且可与其互换使用。

还需要指出的是,在本公开的装置、设备和方法中,各部件或各步骤是可以分解和/或重新组合的。这些分解和/或重新组合应视为本公开的等效方案。

在本文中,诸如“第一”、“第二”等不带有量词的修饰词旨在用于区分不同的元件/部件/电路/模块/装置/步骤,而不用于强调次序、位置关系、重要程度、优先级别等。与此不同,诸如“第一个”、“第二个”等带有量词的修饰词可以用于强调不同的元件/部件/电路/模块/装置/步骤的次序、位置关系、重要程度、优先级别等。

提供所公开的方面的以上描述以使本领域的任何技术人员能够做出或者使用本公开。对这些方面的各种修改对于本领域技术人员而言是非常显而易见的,并且在此定义的一般原理可以应用于其他方面而不脱离本公开的范围。因此,本公开不意图被限制到在此示出的方面,而是按照与在此公开的原理和新颖的特征一致的最宽范围。

为了例示和描述的目的已经给出了以上描述。此外,此描述不意图将本公开的实施例限制到在此公开的形式。尽管以上已经讨论了多个示例方面和实施例,但是本领域技术人员将认识到其某些变型、修改、改变、添加和子组合。

- 检测处理器运行状态的装置和方法

- 处理器运行状态监视诊断方法及装置