半导体器件及其形成方法

文献发布时间:2023-06-19 10:06:57

技术领域

本发明涉及半导体制造技术领域,尤其涉及一种半导体器件及其形成方法。

背景技术

在目前的半导体产业中,集成电路产品主要可以分为三大类型:逻辑、存储器和模拟电路,其中存储器在集成电路产品中占了相当大的比例。随着半导体技术的发展,对存储器进行更为广泛的应用,需要将存储器与其他器件同时形成在一个芯片上,以形成嵌入式半导体存储装置。例如将存储器内嵌置于中央处理器平坦进行兼容,并且保持原有的存储器的规格及对应的电学性能。

一般地,需要将存储器与嵌入的标准逻辑装置进行兼容。对于嵌入式半导体器件来说,其通常分为逻辑区和存储器,逻辑区通常包括逻辑器件,存储区则包括存储器件。随着存储技术的发展,出现了各种类型的半导体存储器,例如静态随机存储器(SRAM,StaticRandom Access Memory)、动态随机存储器(DRAM,Dynamic Random Access Memory)、可擦除可编程只读存储器(EOROM,Erasable Programmable Read-Only Memory)、和闪存(Flash)。由于静态随机存储器具有低功耗和轻快工作速度等优点,使得静态随机存储器及其形成方法越来越受到关注。

在半导体器件的制造方法中,为了调整静态随机存储器(SRAM)的α比率、β比率以及γ比率以获得更好的器件性能,现有技术中一般存在两种方法。一种是为上拉晶体管(PU)、传输晶体管(PG)和下拉晶体管(PD)分别选用不同数量的鳍部,例如分别为1、1、1或1、1、2或1、2、3。此外一种方法是采用不同高度的鳍部结构来调整静态随机存储器(SRAM)的α比率、β比率以及γ比率。

在为上拉晶体管(PU)、传输晶体管(PG)和下拉晶体管(PD)分别选用不同数量的鳍部来调整静态随机存储器(SRAM)的α比率、β比率以及γ比率过程中,β比率是不可以改变的。在调整β比率时,需要在传输晶体管(PG)和下拉晶体管(PD)形成不同的掩膜层,通过阈值电压调整注入改变β比率,但是由于静态随机存储器的尺寸不断的缩小,很难通过在传输晶体管(PG)和下拉晶体管(PD)形成不同的掩膜层来调整β比率。

发明内容

本发明解决的问题是提供一种半导体器件及其形成方法,使得β比率的调整变得容易,改善静态随机存储器的写入冗余度,从而提高形成的半导体器件的整体性能。

为解决上述问题,本发明提供一种半导体器件的形成方法,包括:提供衬底,所述衬底包括上拉晶体管区、下拉晶体管区以及传输晶体管区;在所述衬底上形成若干分立排布鳍部,所述鳍部包括同时位于所述传输晶体管区和所述下拉晶体管区的第一鳍部、位于所述下拉晶体管区的第二鳍部和位于所述上拉晶体管区的第三鳍部;在所述衬底上形成掩膜层,所述掩膜层同时暴露出所述第二鳍部的表面和所述第三鳍部的表面,或所述掩膜层暴露出所述第一鳍部的表面;通过离子注入对暴露出所述鳍部的表面进行阈值电压的调整。

可选的,当所述掩膜层同时暴露出第二鳍部的表面和所述第三鳍部的表面时,对所述第二鳍部的表面和所述第三鳍部的表面进行N型离子注入。

可选的,所述N型离子包括P、As或Sb。

可选的,所述N型离子注入的参数包括:注入的能量为4keV至15keV,注入剂量为1E12atom/cm

可选的,当所述掩膜层暴露出所述第一鳍部的表面时,对所述第一鳍部的表面进行P型离子注入。

可选的,所述P型离子包括B、Ga或In。

可选的,所述P型离子注入的参数包括:注入的能量为2keV至4keV,注入剂量为1E11atom/cm

可选的,在所述衬底上形成掩膜层之前,还包括:在所述衬底上以及所述鳍部的表面形成牺牲氧化层。

可选的,通过离子注入对暴露出所述鳍部的表面进行阈值电压的调整之后,还包括:去除所述掩膜层。

可选的,在所述衬底上形成横跨所述鳍部的栅极结构。

可选的,采用湿法刻蚀或干法刻蚀或灰化工艺去除所述掩膜层。

相应的,利用上述形成方法,本发明还提供一种半导体器件,包括:衬底,所述衬底包括上拉晶体管区、下拉晶体管区以及传输晶体管区;若干鳍部,分立排布于所述衬底上,包括第一鳍部、第二鳍部、第三鳍部,其中:所述第一鳍部,同时位于所述传输晶体管区和所述下拉晶体管区,所述第二鳍部,位于所述下拉晶体管区;所述第三鳍部,位于所述上拉晶体管区;掩膜层,位于所述衬底上,同时暴露出第二鳍部的表面和所述第三鳍部的表面,或暴露出所述第一鳍部的表面;注入离子,位于第二鳍部内和所述第三鳍部内或位于所述第一鳍部内。

可选的,所述第二鳍部内和所述第三鳍部内具有相同类型的注入离子。

与现有技术相比,本发明的技术方案具有以下优点:

在衬底上形成若干分立排布的鳍部,鳍部包括同时位于所述传输晶体管区和所述下拉晶体管区的第一鳍部、位于所述下拉晶体管区的第二鳍部和位于所述上拉晶体管区的第三鳍部,在衬底上形成掩膜层,利用掩膜层同时暴露出第二鳍部和第三鳍部的表面或暴露出第一鳍部的表面,在通过离子注入对暴露出的鳍部表面进行阈值电压的调整时,第二鳍部和第三鳍部的表面能够进行相同类型的离子注入,这样第二鳍部与第一鳍部之间具有不同电学性质,从而下拉晶体管区上的鳍部和传输晶体管区上的鳍部具有不同的电学性质,这样可以实现β比率的调节;同时由于掩膜层同时暴露出第二鳍部和第三鳍部或暴露出第一鳍部(即同时覆盖第二鳍部和第三鳍部),这样利用形成一种掩膜层就可以实现β比率的调节,节约成本;另外第二鳍部和第三鳍部之间的距离较大,容易形成覆盖质量好的掩膜层,使得掩膜层的形成工艺变得简单,从而使得β比率的调整变得容易,改善了静态随机存储器的写入冗余度,提高形成的半导体器件的整体性能。

附图说明

图1至图9是本发明第一实施例中半导体器件形成过程的结构示意图;

图10至图14是本发明第二实施例中半导体器件形成过程的结构示意图。

具体实施方式

目前调整静态随机存储器(SRAM)的α比率、β比率以及γ比率常用的方法是为上拉晶体管(PU)、传输晶体管(PG)和下拉晶体管(PD)分别选用不同数量的鳍部,此时β比率就等于下拉晶体管(PD)鳍部的数量与传输晶体管(PG)鳍部的数量的比值。

发明人发现,利用这种方法形成的β比率是不可变化的,这样需要调整β比率时,需要在下拉晶体管(PD)和传输晶体管(PG)上形成不同的掩膜层来进行阈值电压的调整,但是随着静态随机存储器的尺寸缩小,利用在下拉晶体管(PD)和传输晶体管(PG)上形成不同的掩膜层来进行阈值电压的调整实现起来很困难,这样静态随机存储器的写入冗余度得不到改善,限制了半导体器件的使用。

发明人研究发现,利用掩膜层同时暴露出第二鳍部和第三鳍部的表面或暴露出第一鳍部的表面(即同时覆盖第二鳍部和第三鳍部),第二鳍部和第三鳍部的表面能够进行相同类型的离子注入,这样第二鳍部与第一鳍部之间具有不同电学性质,从而下拉晶体管区上的鳍部和传输晶体管区上的鳍部具有不同的电学性质,这样可以实现β比率的调节;同时由于掩膜层同时暴露出第二鳍部和第三鳍部或暴露出第一鳍部(即同时覆盖第二鳍部和第三鳍部),第二鳍部和第三鳍部之间的距离较大,掩膜层成形变得容易,简化了掩膜层的成形难度的同时调整了β比率,改善了静态随机存储器的写入冗余度,从而提高形成的半导体器件的整体性能。

为使本发明的上述目的、特征和优点能够更为明显易懂,下面结合附图对本发明的具体实施例做详细地说明。

第一实施例

图1至图9是本发明第一实施例中半导体器件形成过程的结构示意图。

首先参考图1,提供衬底100,所述衬底100包括上拉晶体管区110、下拉晶体管区120以及传输晶体管区130。

所述衬底100可以是单晶硅,多晶硅或非晶硅;所述衬底100也可以是硅、锗、锗化硅、砷化镓等半导体材料;本实施例中,所述衬底100的材料为单晶硅。

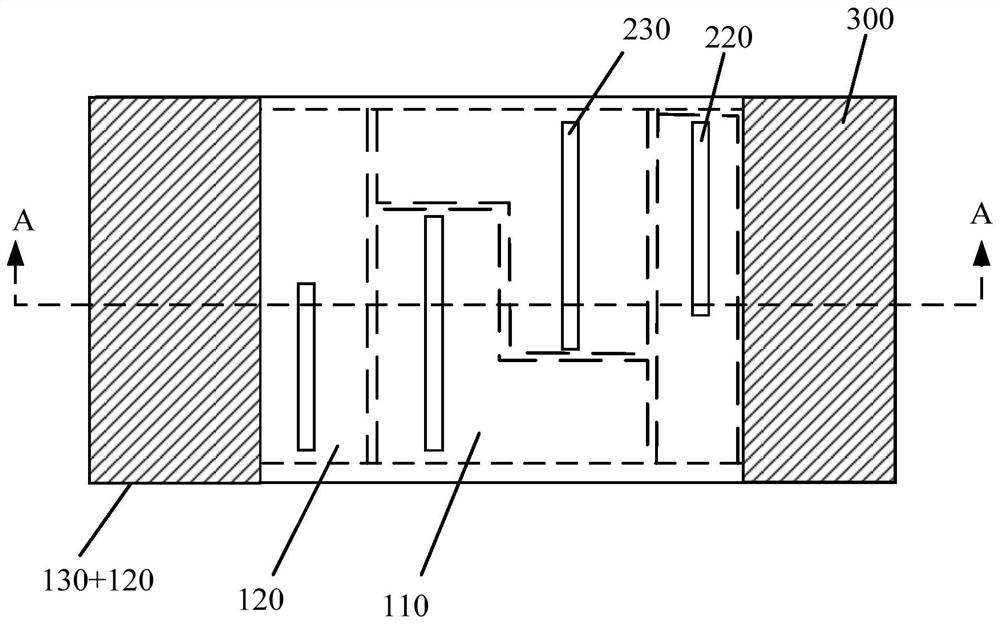

参考图2至图3,在所述衬底100上形成若干分立排布鳍部200,所述鳍部200包括同时位于所述传输晶体管区130和所述下拉晶体管区120的第一鳍部210、位于所述下拉晶体管区120的第二鳍部220和位于所述上拉晶体管区110的第三鳍部230。

图2是图3沿着剖线A-A的剖视图,图3是图2的俯视图。

本实施例中,以Fin121SRAM为例说明;其他实施例中,还可是Fin131SRAM或Fin132SRAM等;其中Fin121SRAM表示SRAM中上拉晶体管区上具有1个鳍部;下拉晶体管区上有2个鳍部;传输晶体管区上有1个鳍部。那么Fin131SRAM或Fin132SRAM表示的含义以此类推。

本实施例中,形成所述鳍部200的方法为:先在所述衬底100上形成光刻胶层;曝光、显影工艺后,在所述光刻胶层内形成光刻胶图案;之后以图案化后的光刻胶层为掩膜刻蚀所述衬底100,从而在衬底100上形成鳍部200。

其他实施例中,形成所述鳍部200的方法还可为:在所述衬底100上形成鳍部材料层,在鳍部材料层上形成光刻胶层;曝光、显影工艺后,在所述光刻胶层内形成光刻胶图案;之后以图案化后的光刻胶层为掩膜刻蚀所述鳍部材料层,从而在衬底100上形成鳍部200。

参考图4至图5,在所述衬底100上形成掩膜层300,所述掩膜层300同时暴露出所述第二鳍部220的表面和所述第三鳍部230的表面。

图4是图5沿着剖线A-A的剖视图,图5是图4的俯视图。

本实施例中,所述掩膜层300的材料为氟化氪(KrF);其他实施例中,所述掩膜层300的材料还可以采用氟化氩(ArF)。

本实施例中,由于所述掩膜层300同时暴露出所述第二鳍部220的表面和所述第三鳍部230的表面,在后续离子注入的时候,所述第二鳍部220和所述第一鳍部210具有不同的电学性质,从而使得β比率得到改变;另外所述掩膜层300同时暴露出所述第二鳍部220和所述第三鳍部230,由于所述第二鳍部220和所述第三鳍部230之间的距离较大,这样形成的所述掩膜层300的开口较大,容易形成所述掩膜层300,简化了形成所述掩膜层300的工艺过程;同时由于所述掩膜层300同时暴露出所述第二鳍部220和所述第三鳍部230,就可以实现所述第一鳍部210和所述第二鳍部220之间具有不同的电学性质,不需要额外的掩膜层,节约了成本。

参考图6,通过离子注入对暴露出所述鳍部200的表面进行阈值电压的调整。

图中带箭头的线表示离子流向。

本实施例中,通过离子注入对暴露出所述第二鳍部220的表面和所述第三鳍部230的表面进行阈值电压调整。

本实施例中,对所述第二鳍部220的表面和所述第三鳍部230的表面进行N型离子注入。

本实施例中,所述N型离子为As;其他实施例中,所述N型离子还可为P或Sb。

本实施例中,所述第二鳍部220和所述第三鳍部230内被注入相同类型的离子。

本实施例中,所述N型离子注入的参数包括:注入的能量为4keV至15keV,注入剂量为1E12atom/cm

本实施例中,由于所述第二鳍部220的表面和所述第三鳍部230表面被同时暴露出来,都被注入N型离子,后续对所述第一鳍部210进行阈值电压调整时,所述第一鳍部210注入的离子类型与所述第二鳍部220注入的离子类型不同,这样所述第一鳍部210和所述第二鳍部220具有不同的电学性质,从而实现了β比率的调节,改善了静态随机存储器的写入冗余度,提高形成的半导体器件的整体性能。

参考图7,去除所述掩膜层300。

本实施例中,采用干法刻蚀去除所述掩膜层300;其他实施例中,还可采用湿法刻蚀或灰化的工艺去除所述掩膜层300。

本实施例中,干法刻蚀的工艺参数包括:采用刻蚀气体包括HCl,稀释气体包括N

参考图8至图9,在所述衬底100上形成横跨所述鳍部200的栅极结构400。

图9是图8在剖线A-A的剖视图,图8是图9的俯视图。

本实施例中,所述栅极结构400包括位于所述鳍部200表面的栅氧化层(图中未示出)以及位于栅氧化层上的栅介质层。

本实施例中,采用常规的方法形成所述栅极结构400,这里不再累赘说明。

相应的,本发明还提供一种利用上述方法形成的半导体器件,包括:衬底100,所述衬底100包括上拉晶体管区110、下拉晶体管区120以及传输晶体管区130;若干鳍部200,位于所述衬底100上,包括第一鳍部210、第二鳍部220、第三鳍部230,其中:所述第一鳍部210,同时位于所述传输晶体管区130和所述下拉晶体管区120;所述第二鳍部220,位于所述下拉晶体管区120;所述第三鳍部230,位于所述上拉晶体管区110;掩膜层300,位于所述衬底上100,同时暴露出第二鳍部220的表面和所述第三鳍部230的表面;注入离子,位于第二鳍部220内和所述第三鳍部230内;栅极结构400,位于所述衬底100,且横跨所述鳍部200。

本实施例中,所述第二鳍部220内和所述第三鳍部230内具有相同类型的注入离子。

第二实施例

图10至图14是本发明第二实施例中半导体器件形成过程的结构示意图。

本实施例中,从提供衬底至在衬底上形成若干分立排布鳍部的过程与第一实施例相同,具体参考图1至图3。

参考图10,在所述衬底100以及所述鳍部200的表面形成牺牲氧化层500。

本实施例中,在衬底上形成掩膜层之前,在所述衬底上以及所述鳍部的表面形成牺牲氧化层500;其他实施例中,在衬底上形成掩膜层之前,还可不再在所述衬底上以及所述鳍部的表面形成牺牲氧化层500。

本实施例中,形成所述牺牲氧化层500可以防止阈值电压离子注入隧道效应,隔离所述衬底100和后续形成的掩膜层,防止掩膜层中的有机物与所述衬底100接触,污染所述衬底100,也可以捕获所述衬底100表面的缺陷,改善所述衬底100表面界面态。同时生长牺牲氧化层500可以改善白带效应对器件的影响

参考图11至图12,在所述衬底100上形成掩膜层600,所述掩膜层600暴露出所述第一鳍部210的表面。

图11是图12沿着剖线A-A的剖视图,图12是图11的俯视图。

本实施例中,所述掩膜层600暴露出所述第一鳍部210的表面上的所述掩膜层600。

本实施例中,所述掩膜层600的材料为氟化氩(ArF)。

本实施例中,利用所述掩膜层600暴露出所述第一鳍部210的表面,即覆盖所述第二鳍部220和所述第三鳍部230的表面,这样在后续对所述第一鳍部210离子注入进行调整阈值电压时,使得所述第一鳍部210和所述第二鳍部220具有不同的电学性质,从而实现了β比率的改变,且不需要额外的掩膜层就可以实现β比率的改变,节约了成本;另外,由于所述第二鳍部220和所述第三鳍部230之间的距离较大,容易形成所述掩膜层600,且所述掩膜层600的特征尺寸大小和覆盖范围都容易控制,简化了所述掩膜层600的形成工艺。

参考图13,通过离子注入对暴露出所述鳍部200进行阈值电压的调整。

图中带箭头的线表示离子流向。

本实施例中,通过离子注入对暴露出的所述第一鳍部210进行P型离子注入。

本实施例中,所述P型离子为B;其他实施例中,所述P型离子还可为Ga或In。

本实施例中,所述P型离子注入的参数包括:注入的能量为2keV至4keV,注入剂量为1E11atom/cm

本实施例中,由于所述第二鳍部220和所述第三鳍部230被同时覆盖住,所述第一鳍部210被暴露出来,进行注入P型离子,后续使得形成所述第一鳍部210和所述第二鳍部220内具有不同类型的注入离子,这样所述第一鳍部210和所述第二鳍部220就具有不同的电学性质,从而实现了β比率的调节,这样改善了静态随机存储器的写入冗余度,提高形成的半导体器件的整体性能。

参考图14,通过离子注入对暴露出所述鳍部200进行阈值电压的调整之后,去除所述掩膜层600的和所述牺牲氧化层500。

去除所述掩膜层600之后,所述衬底上形成横跨鳍部的栅极结构400的过程与第一实施例相同,具体参考图8至图9。

相应的,本发明还提供一种利用上述方法形成的半导体器件,包括:衬底100,所述衬底100包括上拉晶体管区110、下拉晶体管区120以及传输晶体管区130;若干鳍部200,位于所述衬底100上,包括第一鳍部210、第二鳍部220、第三鳍部230,其中:所述第一鳍部210,同时位于所述传输晶体管区130和所述下拉晶体管区120;所述第二鳍部220,位于所述下拉晶体管区120;所述第三鳍部230,位于所述上拉晶体管区110;牺牲氧化层500,位于所述衬底100上和所述鳍部200的表面上;掩膜层600,位于所述衬底上100,同时暴露出所述第一鳍部210的表面;注入离子,位于所述第一鳍部210内;栅极结构400,位于所述衬底100,且横跨所述鳍部200。

本实施例中,所述第二鳍部220内和所述第三鳍部230内具有相同类型的注入离子。

虽然本发明披露如上,但本发明并非限定于此。任何本领域技术人员,在不脱离本发明的精神和范围内,均可作各种更动与修改,因此本发明的保护范围应当以权利要求所限定的范围为准。

- 半导体膜的形成方法、半导体器件的形成方法和半导体器件

- 栅极结构的形成方法、半导体器件的形成方法以及半导体器件