一种提高共模抑制比的差分采样电路及方法

文献发布时间:2023-06-19 10:08:35

技术领域

本申请属于电压采样技术领域,特别涉及一种提高共模抑制比的差分采样电路及方法。

背景技术

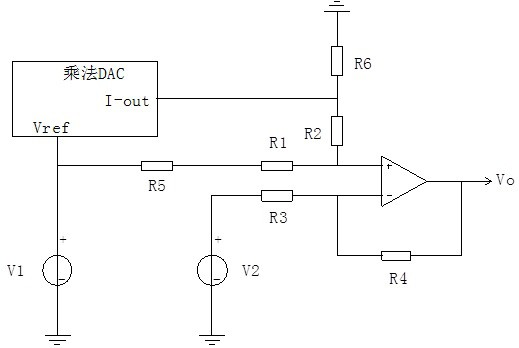

如图1所示为一种典型结构的差分采样电路,对于差分电压信号的采样,其主要是通过差分转单端电路将差分电压转换成单端电压输出。

在理论情况下,差分采样电路中的电阻会满足R2/R1=R4/R3,由此使得输出电压

令:

则电压V1与电压V2的差分电压为Vd,共模电压为Vc,输出电压Vo整理后为:

则,共模抑制比为:

以差分增益等于1,电阻比例匹配度0.01%为例,此时共模抑制也只能达到86dB左右。对于一些超高精度的应用来说,存在精度不够的问题。

因此,希望有一种技术方案来克服或至少减轻现有技术的至少一个上述缺陷。

发明内容

本申请的目的是提供了一种提高共模抑制比的差分采样电路及方法,以解决或减轻现有技术中存在的至少一个问题。

本申请的第一个方面提供了一种提高共模抑制比的差分采样电路,所述差分采样电路包括第一电源、第二电源、第一电阻、第二电阻、第三电阻、第四电阻、阻值可调模块以及差分放大器,其中,

所述第一电阻的第一端连接所述第一电源,所述第一电阻的第二端连接所述差分放大器的同相输入端;

所述第二电阻的第一端连接所述第一电阻的第二端以及所述差分放大器的同相输入端,所述第二电阻的第二端接地;

所述第三电阻的第一端连接所述第二电源,所述第三电阻的第二端连接所述差分放大器的反向输入端;

所述第四电阻的第一端连接所述第三电阻的第二端以及所述差分放大器的反向输入端,所述第四电阻的第二端连接所述差分放大器的输出端;以及

所述阻值可调模块的第一端连接所述第一电源以及所述第一电阻的第一端,所述阻值可调模块的第二端连接所述第二电阻的第二端。

可选地,所述阻值可调模块为乘法数模转换器。

可选地,还包括第五电阻,所述第五电阻的第一端连接所述第一电源以及所述阻值可调模块的第一端,所述第五电阻的第二端连接所述第一电阻的第一端。

可选地,还包括第六电阻,所述第六电阻的第一端连接所述第二电阻的第二端以及所述阻值可调模块的第二端,所述第六电阻的第二端接地。

可选地,所述第五电阻与第一电阻的阻值满足R5< 可选地,所述第六电阻与第二电阻的阻值满足R6< 可选地,所述第五电阻与第六电阻的阻值满足R5>R6。 本申请的第二个方面提供了一种提高共模抑制比的方法,基于如上所述的提高共模抑制比的差分采样电路,包括: 通过调节所述阻值可调模块的阻值使得共模引起的输出电压接近于零。 可选地, 令:

则,所述差分放大器的输出电压为:

则,共模增益Gc为:

其中,

通过调节所述阻值可调模块的阻值Rx,使得共模电压Vc的共模增益Gc接近于0; 其中,Vd为差分电压,Vc为共模电压,V1为第一电源的电压,V2为第二电源的电压,Vo为差分放大器的输出电压,R1为第一电阻的阻值,R2为第二电阻的阻值,R3为第三电阻的阻值,R4为第四电阻的阻值,R5为第五电阻的阻值,R6为第六电阻的阻值,Rx为阻值可调模块的阻值。 可选地,当所述阻值可调模块为乘法数模转换器时:

则:

通过调节所述乘法数模转换器的Code,使得共模电压Vc的共模增益Gc接近于0。 本申请所提供的提高共模抑制比的差分采样电路,能够通过调节阻值可调模块的阻值,使得共模引起的输出电压接近于零,从而使得差分放大后的输出电压趋近于一稳定值,从而提高了输出精度。 附图说明 为了更清楚地说明本申请提供的技术方案,下面将对附图作简单地介绍。显而易见地,下面描述的附图仅仅是本申请的一些实施例。 图1为典型的差分采样电路示意图; 图2为本申请一个实施方式的提高共模抑制比的差分采样电路示意图; 图3为典型乘法DAC内部结构示意图。 具体实施方式 为使本申请实施的目的、技术方案和优点更加清楚,下面将结合本申请实施例中的附图,对本申请实施例中的技术方案进行更加详细的描述。在附图中,自始至终相同或类似的标号表示相同或类似的元件或具有相同或类似功能的元件。所描述的实施例是本申请一部分实施例,而不是全部的实施例。下面通过参考附图描述的实施例是示例性的,旨在用于解释本申请,而不能理解为对本申请的限制。基于本申请中的实施例,本领域普通技术人员在没有作出创造性劳动前提下所获得的所有其他实施例,都属于本申请保护的范围。下面结合附图对本申请的实施例进行详细说明。 为了克服现有技术中差分采样电路的输出电压精度不高的问题,本申请提供了一种可以共模抑制比的差分采样电路及方法,通过在原有差分电压采样电路中增加一阻值可调模块来校正差分采样电路的输出,从而使得共模引起的输出电压接近于零,实现差分放大电压的稳定输出。 下面结合附图2至图3对本申请做进一步详细说明。 本申请的第一个方面提供了一种提高共模抑制比的差分采样电路,该差分采样电路包括第一电源V1、第二电源V2、第一电阻R1、第二电阻R2、第三电阻R3、第四电阻R4、阻值可调模块Rx以及差分放大器。 具体的,如图2所示,第一电阻R1的第一端连接第一电源V1,第一电阻R1的第二端连接差分放大器的同相输入端;第二电阻R2的第一端连接第一电阻R1的第二端以及差分放大器的同相输入端,第二电阻R2的第二端接地;第三电阻R3的第一端连接第二电源V2,第三电阻R3的第二端连接差分放大器的反向输入端;第四电阻R4的第一端连接第三电阻R3的第二端以及差分放大器的反向输入端,第四电阻R4的第二端连接差分放大器的输出端;以及阻值可调模块Rx的第一端连接第一电源V1以及第一电阻R1的第一端,阻值可调模块Rx的第二端连接第二电阻R2的第二端。 有利的是,本实施例中,阻值可调模块Rx可以为乘法数模转换器(Digital toAnalog Converter,即乘法DAC)。 在本申请的优选实施方案中,还设置有第五电阻R5和第六电阻R6,第五电阻R5与第一电阻R1串联,使得第一电源V1的输出电压同时输入乘法数模转换器的参考输入端和第五电阻R5;第二电阻R2与第六电阻R6串联,乘法数模转换器的参考输出端耦接到第六电阻R6与第二电阻R2串联的节点上。具体的,第五电阻R5的第一端连接第一电源以及阻值可调模块Rx的第一端,第五电阻R5的第二端连接第一电阻R1的第一端,第六电阻R6的第一端连接第二电阻R2的第二端以及阻值可调模块Rx的第二端,第六电阻R6的第二端接地。 本实施例中,第五电阻的阻值R5远小于第一电阻的阻值R1,即R5< 基于上述的提高共模抑制比的差分采样电路,本申请的第二个方面提供了一种提高共模抑制比的方法,包括:通过调节阻值可调模块的阻值Rx使得共模引起的输出电压接近于零。 当上述的差分采样电路中未引入阻值可调模块,只引入第五电阻R5、第六电阻R6的情况下,会造成基本匹配的电阻网络的匹配精度偏向一边,由此会导致差分放大后的输出电压Vo偏小。 令,差分电压:

共模电压:

此时,差分放大器的输出电压为:

则,共模增益为:

其中,

假设设计时:

则此时共模增益必定小于零,代表此时共模增益引起的误差必定为负值。 此时引入一个阻值可调模块来补偿共模引起的误差,则,此时的差分放大器的输出电压为:

则,共模增益Gc为:

其中,

通过调节阻值可调模块的阻值Rx,使得共模电压Vc的共模增益Gc接近于0,从而能够使得共模引起的输出电压接近于零; 其中,Vd为差分电压,Vc为共模电压,V1为第一电源的电压,V2为第二电源的电压,Vo为差分放大器的输出电压,R1为第一电阻的阻值,R2为第二电阻的阻值,R3为第三电阻的阻值,R4为第四电阻的阻值,R5为第五电阻的阻值,R6为第六电阻的阻值,Rx为阻值可调模块的阻值。 在本申请的优选实施方案中,引入一个乘法DAC作为阻值可调模块,来补偿共模引

起的误差,典型乘法DAC的内部结构大致如图3所示。在此电路中,乘法DAC可以看成一个可

调电阻,该电阻的阻值与给定的DAC码值相关,即可调电阻 则,本实施例中,差分放大器的输出电压为:

则,共模增益Gc为:

其中,

最后,通过软件校准,可以找到合适的乘法DAC的Code的码值,使得共模电压Vc的共模增益Gc接近于0,从而能够使得共模引起的输出电压接近于零。 本申请所提供的提高共模抑制比的差分采样电路及方法,通过设置一个阻值可调的乘法数模转换器,设置不同的DAC输出电流,校正该差分采样电路的输出,提高该差分采样电路的共模抑制比。本申请的提高共模抑制比的差分采样电路及方法,能够使得共模引起的输出电压接近于零,从而使得差分放大后的输出电压趋近于一稳定值,相比于现有技术大大提高了输出精度。 以上所述,仅为本申请的具体实施方式,但本申请的保护范围并不局限于此,任何熟悉本技术领域的技术人员在本申请揭露的技术范围内,可轻易想到的变化或替换,都应涵盖在本申请的保护范围之内。因此,本申请的保护范围应以所述权利要求的保护范围为准。

- 一种提高共模抑制比的差分采样电路及方法

- 一种采样电路和提高采样电路采样分辨率的方法