半导体刻蚀方法

文献发布时间:2023-06-19 10:19:37

技术领域

本发明涉及半导体工艺领域,具体地,涉及一种半导体刻蚀方法。

背景技术

无晶圆自动清洁工艺(Waferless Auto Clean,WAC)是半导体集成电路刻蚀设备中常用的工艺技术。WAC工艺技术通常用于晶圆刻蚀之后,当晶圆在工艺腔室内完成刻蚀,并且移出腔室之后,在工艺腔室中通入相应的工艺气体,然后利用工艺气体电离形成的等离子体进行腔室的无晶圆自动清洁处理,WAC可以清洁腔室内刻蚀上一片晶圆的产物并预设下一片晶圆的刻蚀环境,在WAC完成后传入下一片晶圆继续进行刻蚀,刻蚀后再进行WAC,如此循环实现晶圆刻蚀制程的量产工作。

然而,现有的采用WAC工艺的刻蚀设备在进行刻蚀工艺时,常出现晶圆刻蚀均匀性差的问题,产品良率较低。因此,如何提供一种能够提高晶圆刻蚀均匀性的半导体刻蚀方法,成为本领域亟待解决的技术问题。

发明内容

本发明旨在提供一种半导体刻蚀方法,能够提高半导体刻蚀工艺的均匀性,并提高产品良率。

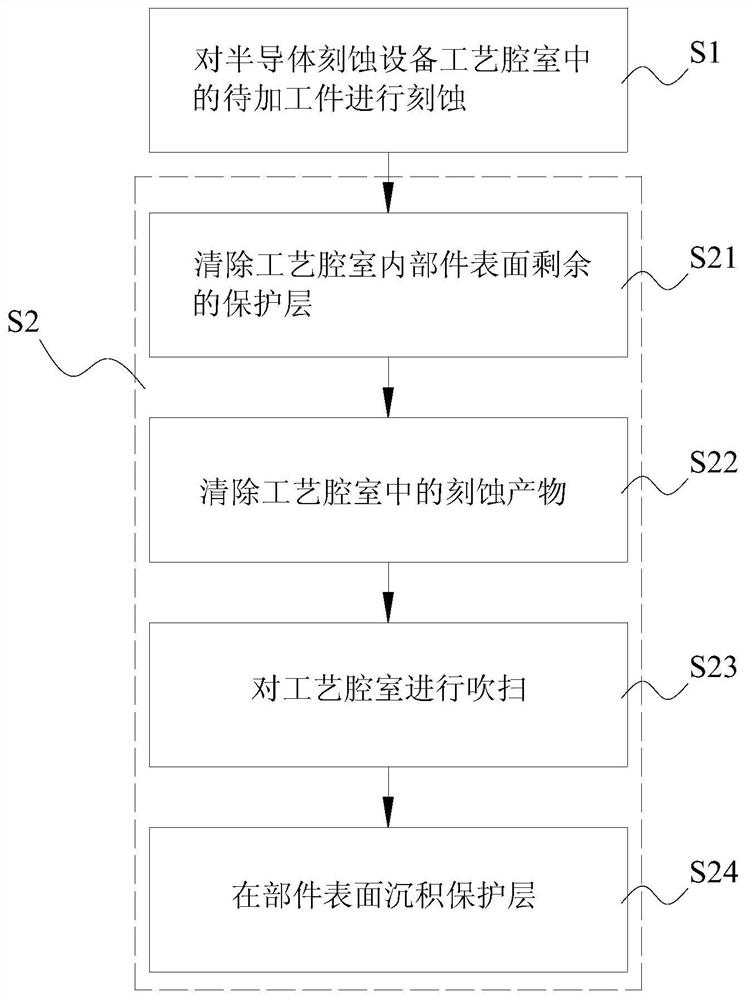

为实现上述目的,本发明提供一种半导体刻蚀方法,包括:

刻蚀步骤,对半导体刻蚀设备工艺腔室中的待加工件(如,晶圆)进行刻蚀;

清洁步骤,清除所述工艺腔室中的刻蚀产物;

交替执行所述刻蚀步骤和所述清洁步骤;

其中,所述清洁步骤包括:

清除所述工艺腔室内部件表面剩余的保护层;

清除所述工艺腔室中的所述刻蚀产物;

对所述工艺腔室进行吹扫;

在所述部件表面沉积所述保护层。

可选地,所述在所述部件表面沉积所述保护层,包括:

向所述工艺腔室中通入沉积气体;

将所述沉积气体电离为等离子体,以在所述部件表面沉积所述保护层。

可选地,所述沉积气体包括四氯化硅、氮气、一氧化碳、氧气中的一种或多种。

可选地,所述部件包括介质窗,沉积在所述介质窗上的所述保护层的厚度沿所述介质窗中心向边缘的方向逐渐增大。

可选地,所述清除所述工艺腔室内部件表面剩余的保护层,包括:

向所述工艺腔室中通入第一刻蚀气体;

将所述第一刻蚀气体电离为等离子体,以清除所述部件表面剩余的所述保护层。

可选地,所述第一刻蚀气体包括六氟化硫、三氟化氮、四氟化碳、氯气中的一种或多种。

可选地,所述清除所述工艺腔室中的所述刻蚀产物,包括:

向所述工艺腔室中通入第二刻蚀气体;

将所述第二刻蚀气体形电离成离子体,以清除所述工艺腔室中的所述刻蚀产物。

可选地,所述第二刻蚀气体包括氧气、六氟化硫、三氟化氮、四氟化碳、氯气中的一种或多种的混合气体。

可选地,所述对所述工艺腔室进行吹扫:

向所述工艺腔室中通入吹扫气体。

可选地,所述吹扫气体包括惰性气体。

在本发明实施例提供的半导体刻蚀方法中,半导体刻蚀设备每一轮工艺循环的清洁步骤最后都包括沉积保护层的步骤,即,对工艺腔室进行清扫后,在工艺腔室内的部件表面上沉积保护层,从而可以消除工艺腔室内部各种结构的表面性质之间的差异对半导体刻蚀工艺的影响,提高刻蚀步骤中刻蚀待加工件的均匀性,进而提高产品良率。

附图说明

附图是用来提供对本发明的进一步理解,并且构成说明书的一部分,与下面的具体实施方式一起用于解释本发明,但并不构成对本发明的限制。在附图中:

图1(a)至图1(f)是本发明提供的半导体刻蚀方法中依次进行一次刻蚀步骤和在清洁步骤的过程示意图;

图2是采用现有的刻蚀方法刻蚀晶圆的刻蚀速率分布示意图;

图3是本发明提供的半导体刻蚀方法中保护层10的厚度分布示意图;

图4是采用沉积有图3所示保护层10的刻蚀设备刻蚀晶圆的刻蚀速率分布示意图;

图5是采用现有技术和本发明提供的刻蚀方法刻蚀晶圆的对比方案示意图;

图6是本发明实施例中保护层10的沉积时间与关键尺寸之间的函数关系示意图;

图7是图5所示对比方案中采用现有技术和本发明提供的刻蚀方法产生的反应产物的光谱对比分析图;

图8是本发明实施例提供的半导体刻蚀方法的流程图。

具体实施方式

以下结合附图对本发明的具体实施方式进行详细说明。应当理解的是,此处所描述的具体实施方式仅用于说明和解释本发明,并不用于限制本发明。

本发明的发明人在研究中发现,现有的刻蚀工艺中出现晶圆刻蚀均匀性不佳的原因在于,利用工艺气体电离形成的等离子体进行清洁处理后,腔室内部的部件(如,介质窗、腔室内壁等)表面均无膜层残留,各部件表面直接裸露于腔室环境中。而在刻蚀工艺中,不同部件表面对于晶圆刻蚀速率的影响是不同的,从而导致晶圆刻蚀均匀性差,产品良率低。

为解决上述技术问题,本发明提供一种半导体刻蚀方法,包括:

在刻蚀步骤S1中,对半导体刻蚀设备工艺腔室中的待加工件进行刻蚀,如图1(a)至图1(c)所示;

在清洁步骤S2中,清除工艺腔室中的刻蚀产物20,如图1(c)至图1(f)所示;

交替执行刻蚀步骤S1和清洁步骤S2。

其中,清洁步骤S2包括:

S21、清除工艺腔室内部件表面剩余的保护层10,如图1(c)至图1(d)所示;

S22、清除工艺腔室中的刻蚀产物20,如图1(d)至图1(e)所示;

S23、对工艺腔室进行吹扫;

S24、在部件表面沉积保护层10,如图1(e)至图1(f)所示。

需要说明的是,在本发明实施例提供的半导体刻蚀方法中,保护层10仅用于改善刻蚀工艺的效果,在完成半导体刻蚀工艺后,为提高清扫效果,需在清扫工艺腔室前先将保护层10去除,如图1(c)至图1(d)所示。

在本发明实施例提供的半导体刻蚀方法中,半导体刻蚀设备每一轮工艺循环的清洁步骤S2最后都包括沉积保护层10的步骤S24,即,对工艺腔室进行清扫(步骤S22和步骤S23)后,在工艺腔室内的部件(如,介质窗、腔室内壁等)表面上沉积保护层10(优选为通过调节沉积气体、气体压力、射频功率、电极电流等工艺参数实现在除卡盘30外的所有部件上沉积保护层10),从而可以消除工艺腔室内部各种结构的表面性质之间的差异对半导体刻蚀工艺的影响,提高刻蚀步骤S1中刻蚀待加工件的均匀性,进而提高产品良率。

并且,保护层10在覆盖工艺腔室内部部件表面的同时,还可参与后续的半导体刻蚀工艺,与刻蚀工艺中的刻蚀气体进行反应,在此基础上可以根据刻蚀速率均匀性的需要对保护层10沉积厚度的分布进行优化,以调节晶圆不同位置刻蚀速率之间的大小关系,从而进一步提高半导体刻蚀工艺的均匀性。

图1(a)至1(f)为本发明实施例提供的半导体刻蚀方法中半导体刻蚀设备在一个循环周期中先后进行半导体刻蚀工艺和清扫工艺腔室的步骤示意图,如图1(a)至图(b)所示,在工艺腔室中将刻蚀气体电离产生等离子体40,以完成刻蚀工艺。在此过程中,工艺腔室内部部件表面覆盖有在上一轮循环工艺结束时沉积的保护层10,该保护层10也可参与进刻蚀工艺中,与刻蚀气体进行反应,同时,刻蚀工艺产生的刻蚀产物20也附着在工艺腔室中的各部件上。需要说明的是,为便于理解,本发明附图中仅在工艺腔室顶部绘出保护层10,实际上保护层10优选形成于工艺腔室中除卡盘30外的所有部件表面。

为进一步提高产品良率,优选地,在第一次进行刻蚀前(即进行第一次刻蚀步骤S1前),可先单独执行一次步骤S24,预先在工艺腔室内的部件表面上形成保护层10,以提高第一次刻蚀步骤S1中刻蚀工艺的均匀性。

本发明实施例对如何在工艺腔室中沉积保护层不做具体限定,例如,作为本发明的一种可选实施方式,在部件表面沉积保护层10的步骤S24包括:

S241、向工艺腔室中通入沉积气体;

S242、将沉积气体电离为等离子体,以在部件表面沉积保护层10。

本发明实施例对该沉积气体的成分不做具体限定,例如,该沉积气体可以包括四氯化硅(SiCl

本发明实施例对如何根据刻蚀速率均匀性的需要对保护层10沉积厚度的分布进行优化不做具体限定,例如,如图2所示,现有的采用WAC工艺的刻蚀设备在进行刻蚀工艺时,晶圆中心位置的刻蚀往往低于边缘处的刻蚀速率。

为解决上述技术问题,作为本发明的一种优选实施方式,如图3所示,该工艺腔室内的部件包括介质窗,沉积在介质窗上的保护层10的厚度沿介质窗中心向边缘的方向逐渐增大。

如图4所示为本发明实施例采用图3中保护层10厚度分布方案时刻蚀晶圆的速率分布图,在本发明实施例中,保护层10的厚度沿介质窗中心向边缘的方向逐渐增大,从而使晶圆边缘上方的刻蚀气体与更多的保护层10材料反应,提高了边缘位置刻蚀气体的消耗量,从而降低了晶圆边缘位置的刻蚀气体浓度,进而降低了晶圆边缘位置的刻蚀速率,提高了半导体刻蚀工艺的均匀性(由图4与图2比较可知刻蚀速率分布曲线趋于平缓,即均匀性提高)。

本发明实施例对步骤S21中如何清除工艺腔室内部件表面剩余的保护层10不作具体限定,例如,作为本发明的一种可选实施方式,清除工艺腔室内部件表面剩余的保护层10的步骤S21可以包括:

向工艺腔室中通入第一刻蚀气体;

将第一刻蚀气体电离为等离子体,以清除部件表面剩余的保护层10。

本发明实施例对该第一刻蚀气体的材料不做具体限定,例如,第一刻蚀气体可以包括六氟化硫、三氟化氮、四氟化碳、氯气中的一种或多种。

本发明实施例对步骤S22中如何清除工艺腔室中的刻蚀产物20不作具体限定,例如,作为本发明的一种可选实施方式,清除工艺腔室中的刻蚀产物20的步骤S22可以包括:

向工艺腔室中通入第二刻蚀气体;

将第二刻蚀气体形电离成离子体,以清除工艺腔室中的刻蚀产物20。

本发明实施例对该第二刻蚀气体的材料不做具体限定,例如,该第二刻蚀气体可以包括氧气、六氟化硫、三氟化氮、四氟化碳、氯气中的一种或多种的混合气体。

可选地,对工艺腔室进行吹扫的步骤S23可以包括:向工艺腔室中通入吹扫气体,以排出工艺腔室中的气体。

本发明实施例对该吹扫气体的材料不做具体限定,例如,作为本发明的一种可选实施方式,该吹扫气体可以包括惰性气体。例如,该吹扫气体可以包括氩气和氦气中的至少一者。

为了验证本发明提供的含有沉积步骤的自动清洁工艺对刻蚀速率的影响,本发明还提供了两种不同清洁工艺对多晶硅图形wafer的刻蚀结果,如图5所示:其中,传统的不含沉积步骤的清洁工艺标记为WAC1,本发明提供的含有沉积保护层步骤的清洁工艺标记为WAC2。其中,WAC2的相关步骤及各步骤的工艺参数如下表1-1所示。其中,WAC2第五步沉积保护层的时间是12秒,此步的工艺参数(如时间、功率等等)可以进行调整,从而影响刻蚀速率。

表1-1

在分别通过WAC1和WAC2对同种基片进行清洁并刻蚀后,分别对二者的刻蚀工艺结果进行量测,WAC1刻蚀后的图形关键尺寸为78nm,WAC2刻蚀后的图形关键尺寸为93nm,即,结果表明本发明实施例提供的WAC2使得刻蚀速率降低。在本发明实施例中,保护层10的沉积时间越长,则关键尺寸越大,即可以通过沉积步骤的时间来控制关键尺寸。沉积步骤时间与关键尺寸的函数关系如图6所示。

如图7所示为WAC1和WAC2的光谱对比分析图,结果表明,使用了保护层10的WAC2清洁技术在工艺的前两步光谱强度明显高于传统无保护层的WAC1,因为腔室清洁后图形晶圆前两步的刻蚀材料其主要成分含有碳,光谱520nm对应刻蚀产物20一氧化碳的跃迁波长,可用于反应腔室的产物浓度,WAC2在520nm波段的强度比WAC1高,即,其刻蚀反应产物的浓度更大。这是因为WAC2的保护层10参与了反应,增加了产物的量。由此可知,根据基片实际刻蚀效果,可在需要降低刻蚀速率的腔室位置上沉积更多的保护层10,以进一步优化晶圆内刻蚀速率的均匀性。

可以理解的是,以上实施方式仅仅是为了说明本发明的原理而采用的示例性实施方式,然而本发明并不局限于此。对于本领域内的普通技术人员而言,在不脱离本发明的精神和实质的情况下,可以做出各种变型和改进,这些变型和改进也视为本发明的保护范围。

- 硅半导体基板的刻蚀方法、半导体装置的制造方法以及刻蚀液

- 半导体刻蚀装置及半导体结构的刻蚀方法