用于编码准循环低密度奇偶校验码的方法及设备

文献发布时间:2023-06-19 10:35:20

本申请案主张在2018年8月3日申请的第62/714,607号临时申请案的权益,所述申请案中的每一者的全部内容特此宛如在本文中完全陈述那样以引用方式并入。

技术领域

本发明大体上涉及用于信息传输、存储及处理系统的错误校正编码,例如有线及无线通信系统,例如光学通信系统、计算机存储器、大容量数据存储系统。更特定来说,其涉及用于例如低密度奇偶校验(LDPC)码的块码的编码方法及设备,且更明确来说,涉及具有块奇偶校验矩阵的LDPC码,称为准循环(QC)LDPC码。

背景技术

低密度奇偶校验(LDPC)码

错误校正码通过保证数据的完整性来在通信、计算机、及存储系统中发挥着重要作用。在过去的十年中,编码理论方面的研究激增,这导致基于低密度奇偶校验(LDPC)码的高效编码方案的发展。已展示迭代消息传递解码算法与经适当设计的LDPC码集合一起接近在无限码字长度的极限下的信息理论信道容量。LDPC码在例如无线网络、卫星通信、深空通信、及电力线通信的数个应用中已标准化。

针对具有长度N、维度K的(N,K)LDPC码,大小为M×N=(N-K)×N的奇偶校验矩阵(PCM)H(假设H是满秩)由少量1组成。由d

当H的列及行中的1的数目恒定时,LDPC码称为规则,否则LDPC码被认为不规则。针对规则LDPC码,使γ=d

如果标示为x=[x

准循环LDPC码

本发明特定涉及准循环LDPC码(QC-KDPC)的类别。在QC-LDPC码中,PCM H由大小为L×L的方块或子矩阵组成,如方程式(2)中描述,其中每一块H

CPM被定义为循环群的本原元素的幂。本原元素例如通过L×L矩阵α定义,在针对L=8的情况的方程式(3)中展示。因此,CPMα

QC-LDPC码的PCM可由具有含有整数值的M

其中I=α

一般循环矩阵

在本发明中,块H

未局限于单个CPM的一般循环矩阵可在根据H计算G的过程期间出现。循环矩阵C通过w具有不同幂的CPM的和来定义:

其中i

编码

本发明涉及LDPC码及其编码器且可适用于任何QC-LDPC码类别,规则的或不规则的。

LDPC码的码字x=[x

其中r=[r

一般来说,生成矩阵G可通过用高斯消元(GE)计算H的简化行阶梯形式从奇偶校验矩阵H获得。因为H由循环行列式组成,且已知循环矩阵的逆也是循环矩阵,则G也是由循环行列式组成,尽管不一定简化到CPM。编码方程式变成:

其中P是由一般循环行列式组成的稠密矩阵。

针对QC-LDPC码,GE过程可在循环级下执行,从而仅利用对循环矩阵的运算(乘法、加法、逆)。此还意味着用于在GE期间枢转矩阵的首项系数本身就是循环矩阵。两个运算可增加循环行列式的权重:

·当首项系数被找到时,需要计算其逆以在主对角线上的枢转位置处创建恒方程式块。如果首项系数不是CPM,那么其逆通常是大权重循环行列式,

·在首项系数变成恒方程式之后,对应块行与其它剩余块行合并以便建立块行阶梯形式。块行的此组合还创建大权重循环。

使用矩阵H的直接逆的替代例是使用贪婪稀疏高斯消元将其变换成上三角矩阵。在GE中,当块行梯形形式已被找到时,即,当所得矩阵呈上三角形式时,可停止所述过程。针对含有全零块及少量CPM的矩阵,高斯消元算法可经约束使得所得上三角矩阵是最稀疏的。实际上,如果简化块行梯形形式是唯一的且对应于原矩阵的逆,那么其块行梯形形式不是唯一的且取决于用于执行高斯消元的首项系数序列。换句话来说,取决于首项系数序列,可获得具有不同稀疏性的不同编码矩阵。编码方程式变成:

其中H

总而言之,矩阵P或(H

1.首先,在(7)及(8)中涉及的运算的数目随着矩阵P及(H

2.矩阵P及(H

因此,考虑其中编码矩阵是稀疏的、由具有低权重的循环块组成的编码程序是高度有益的。编码矩阵的稀疏性不能通过经典编码方法来保证。在本发明中提出一种使用编码矩阵的十分稀疏表示以便获得具有低复杂性同时具有高吞吐量的编码架构的方法。

QC-LDPC码的层及广义层

针对大小为(M

基矩阵中的层的概念可进一步扩展到广义层(GL)的概念。定义如下:

·广义层被定义为基矩阵的两个或更多个层的串接,使得在广义层的每一块列中存在最多一个CPM而其其它元素是全零块。

·全广义层进一步具有每一块列仅含有一个CPM的性质。

此定义保证了针对具有最大列度γ的QC-LDPC码,PCM可用至少γ个GL来组织。为了简单起见,将假设GL的数目总是等于最大列度γ。

图1展示组织于γ=4个全GL中的PCM的实例,由101、102、103及104指示。在此实例中,针对基矩阵中的总共M

在具有广义层结构的PCM中,每一广义层的块行可按任意顺序组织,且不一定含连续块行。在图2中,展示图1的矩阵的实例,针对所述实例,每一GL的块行已进行规则交织。尽管GL的块行不是连续的,但PCM的此组织仍具有每一GL的每个GL列含最多一个非零块的性质。举例来说,以灰色展示的块行201指示组成GL

PCM的GL组织的目的是能够在不发生数据存取冲突的情况下并行执行至少γ个PCM块的处理。此在编码器/解码器算法中允许更大并行度,且会导致更高处理吞吐量。尽管在文献中引入了QC-LDPC的层及广义层的概念来改进LDPC解码器的效率,但在本发明中展示了此结构对QC-LDPC编码器也是有益的。

在循环行列式之间具有最小行间隙的QC-LDPC

提出了在广义层中组织H以改进编码器的吞吐量。然而,为了达到十分高的吞吐量,PCM需要具有关于CPM在每一块行中的位置的其它约束。将用于本发明的描述中的此约束称为间隙约束,且反映了在H的同一块行中的两个连续CPM之间的全零块的数目。关于图1,展示H的第一块行中通过三个全零块分离的两个连续循环行列式的实例。这两个循环行列式之间的间隙是间隙=4个块。

使b

gap

举例来说,针对(4)中的矩阵,使b

针对整个QC-LDPC矩阵,最小间隙被定义为:

显而易见,任何QC-LDPC码具有最小gap

发明内容

本发明涉及LDPC码的编码。特定来说,其涉及其奇偶校验矩阵组织成块的LDPC码的编码。更明确来说,其涉及作为循环置换矩阵的块矩阵,在此情况中,所述码称为准循环(QC)QC-LDPC码。

本发明涉及一种用于实施LDPC编码器以便实现高编码吞吐量同时实现硬件资源使用的方法及硬件设备。此通过在根据信息位计算冗余位并将其合并成码字的过程中对奇偶校验矩阵的结构强加各种约束及剪裁硬件处理单元以高效利用这些特殊结构性质来实现。

本发明的方法涉及利用将QC-LDPC码的奇偶校验矩阵组织成块行及块列。奇偶校验矩阵的块行称为层。

本发明的方法可用于实施QC-LDPC码的编码算法及装置硬件架构。在其奇偶校验矩阵还含全零块的码的类别中,在奇偶校验矩阵内部具有全零块及非零块的规则或不规则分布的码可使用本发明进行编码。

另外,在一些实施例中,本发明的方法强加关于在每一块行中的非零块的相对位置的约束。更明确来说,所述约束涉及必须分离任何给定块行中的任何两个连续非零块的最小数目个全零块。此分离称为间隙约束。所述间隙约束的优点在于改进了处理吞吐量。

另外,在一些实施例中,本发明的方法将奇偶校验矩阵组织成由若干块行的串接组成的广义层。奇偶校验矩阵的每一广义层在每一块列中含有最多一个非零块。广义层的优点是其允许在不发生数据存取冲突的情况下并行地处理奇偶校验矩阵的块,此又增加了编码吞吐量。

在一些实施例中,每一广义层含有相同数目个块行,且在优选实施例中,奇偶校验矩阵具有与最大块列度一样多的广义层。组成广义层的块行可以任意方式选取:连续、交织或不规则。

本发明的方法通过将称为三区域结构的额外特定结构强加到奇偶校验矩阵并利用用于根据适应于此特定结构的信息位计算冗余位实现了高吞吐量及低硬件使用。

本发明中描述的奇偶校验矩阵的三区域结构是将所述矩阵分解成三个区域(R

本发明的各种特征涉及通过利用QC-LDPC码的三区域结构用硬件高效编码器设备降低处理复杂性。另外,其利用间隙约束,还利用广义层的组成、结构及位置。从实施方案角度来看,本发明的三区域编码方法具有减少实施编码器所需的资源量的优点。

在本发明中,奇偶校验矩阵的N

根据本发明的一个实施例,冗余位的计算涉及奇偶校验位的计算,其中信息位的块被并行处理,从而产生奇偶校验位的M

本发明的额外特征涉及减少逆S

因为矩阵S含有循环置换矩阵的块及全零块,所以其逆A由循环矩阵及全零块组成,但A中的循环矩阵的权重通常可较大,通常大约是循环行列式大小的一半。本发明的方法涉及使用具有低权重逆、比循环行列式大小小得多的矩阵。

本发明的一个实施例利用A的第j块列中的最大循环权重不大于w

本发明的一个特征是编码方法可针对三个区域R

在详细公开中将可见,高效地实现了上文陈述的目标,且因为可在不背离本发明的精神及范围的情况下在实施所提出的方法时作出一些改变,所以希望在描述中所含且在附图中展示的标的物应被解译为说明性的而非限制性的。

附图说明

为了更完全地理解本发明,参考以下描述及附图,其中:

图1展示在d

图2展示在具有交织行的广义层中PCM H的组织;

图3说明所揭示奇偶校验矩阵的结构;

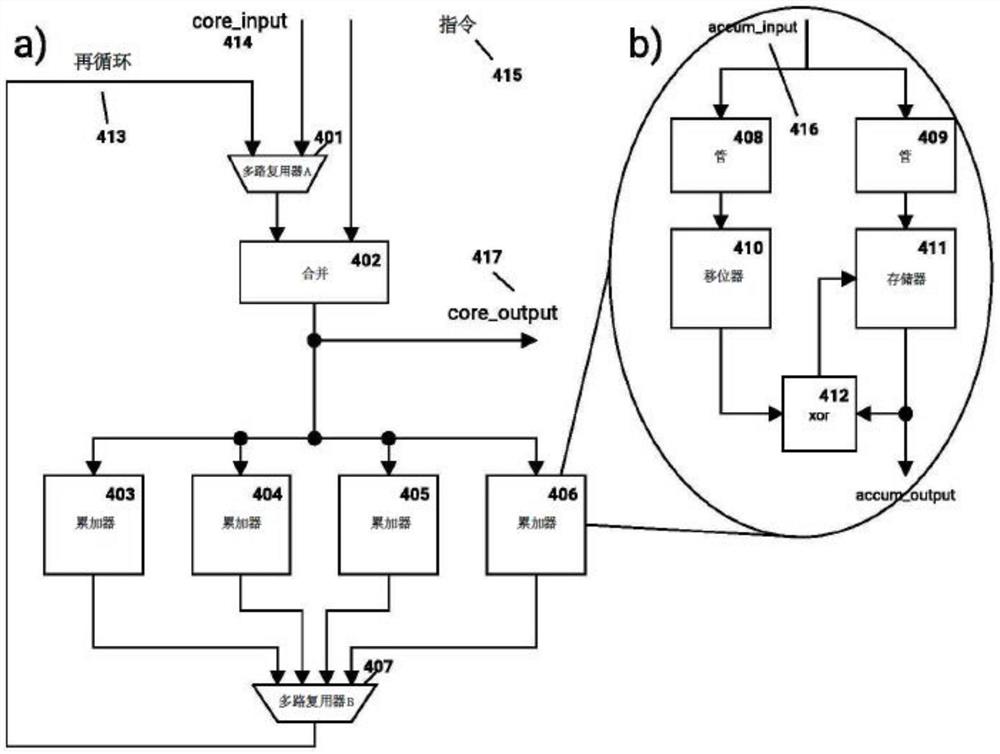

图4描述用于实施编码器的顶级共同硬件,其具有两个部分:a)核心编码硬件;及b)累加器硬件;

图5描述区域R

图6描述区域R

图7说明将稠密块循环矩阵展开成稀疏表示的程序;

图8描述在区域R

图9描述在区域R

具体实施方式

奇偶校验矩阵H的稀疏结构

在本发明中,QC-LDPC码的奇偶校验矩阵将用以下形式组织

其中

类似于PCM H,矩阵(U,T,S)由循环块组成,且为了便于呈现,子矩阵的维度在数个循环块中指示。此意味着,遵循段落0004的注释,

M

N

K

PCM被组织成三个区域:

·区域R

·区域R

·区域R

具有此结构的PCM的实例在图3中展示。展示关于300的矩阵H,其分解成子矩阵:块矩阵U 301、上三角矩阵T 302、方阵矩阵S 303、及最终全零矩阵0(M

本发明还包括通过任何块行及/或块列置换从(11)中展示的结构推导的PCM。

广义层中的PCM的组织,具有最小间隙

在本发明的优选实施例中,PCM H被组织于广义层中,此又强加子矩阵(U,T,S)也被组织于广义层中的约束。

出于说明目的,遵循在段落0007中呈现的交织广义层的组织,其它布置可为可能的,且通过块行的置换获得的GL中的块行的任何其它组织也被本发明覆盖。作为非限制性说明性实例,在γ=4个GL的情况中,组织于GL中的PCM的结构在图3中展示为各自由恰好M

在图3的实例中,第k广义层GL

矩阵(U,T,S)中的相同块行指标组成对应子矩阵的广义层GL

在本发明的优选实施例中,矩阵U及T在其块行上进一步具有间隙约束以帮助改进编码器的吞吐量。针对矩阵U,假设每一及每个块行具有最小间隙≥2。针对矩阵T,假设在每一及每个块行中,对角块与前一块之间的间隙是至少间隙≥3。在图3的实例中,T的对角块的最小间隙是针对行块j=6、j=8、j=11、j=12及j=16达到的间隙=3。不假设T的非对角块的任何间隙约束。

GL组织与间隙约束的合并允许导出区域R

码字结构

码字x可被写为

其中x

将本发明中的所有运算描述为GF(2)中的仅使用L×L个循环块的块计算,例如,H

H

运算(18)的硬件实施方案通常使用桶形移位器进行,使得H

在本发明中,码字遵循在段落0036中描述的PCM的结构进一步进行组织。将方程式(16)重写为

其中u是信息位的向量,

二进制列向量u

奇偶校验向量结构

编码过程涉及奇偶校验的向量的计算,所述向量由c标示:

类似于码字向量的结构,奇偶校验的向量也是在块级下进行定义,级,c

进一步定义临时奇偶校验的/向量,其标示为c

临时奇偶校验的向量将用于解释编码过程的三个循序步骤。应注意,根据PCM的定义,最终临时奇偶校验向量等于全零向量,

具有广义层的奇偶校验向量结构

在本发明的优选实施例中,PCM被组织于γ个GL中。此意味着临时奇偶校验的向量可被划分成γ个部分,每一及每个部分对应于一个GL。作为说明性实例,对应于图3的PCM的临时奇偶校验c

因为根据图3,GL

在此优选实施例中,临时奇偶校验向量的每一部分可经存储于单独存储器中,且使用单独电路用方程式(23)来计算。

使用H的结构的编码

在此段落中,描述构成本发明的主要目的的全局编码过程,且将在接下来的段落中详细描述每一步骤。

根据方程式(11),PCM由三个区域(R

在段落0036及0038的注释下,方程式(17)现在可被写为

K

编码过程的三个循序步骤被定义如下:

·步骤1:第一步骤仅使用区域R

·步骤2:第二步骤仅使用区域R

·步骤3:第三步骤仅使用区域R

在上述三个步骤完成之后,冗余位的向量[t;s]由子向量t及s组合而成,且获得经编码码字x=[u;t;s]。

用于编码区域R

如在段落0041中提及,编码器被分解成三个步骤,每一步骤基于H的对应子矩阵的不同结构。针对编码器的高效硬件实现,可期望设计针对所有区域使用相同硬件单元的架构,这是因为其允许将相同电路重用于三个步骤的循序处理。

本发明提出在此段落中描述的用于编码器的所有三个区域的单个架构。此单个架构明确经定向朝向在段落0037中描述的本发明的优选实施例,即,当PCM被组织于γ个GL中,且矩阵U的最小间隙是gap

图4展示编码器的核心(用a)指示)连同累加器实施方案的细节(用b)指示)的示意图。针对γ=4的情况展示了特定实例。此相同硬件模型将用于所有三个区域。编码器的核心由多路复用器401及407、合并逻辑402及γ个累加器(403、404、405、406)组成。其还含有再循环流413,其经包含以使硬件一般足以用于所有三个区域。关于再循环流在每一区域中如何不同的细节在稍后段落中给出。

核心输入414由数据组成,其性质取决于正被处理的区域。在区域R

合并器块402处理从指令流415接收的指令且使其与来自401的数据相关联。合并器块含有用于存储数据的一组寄存器,以备其需要由若干指令使用。指令还可指示合并器块应在不消耗更多指令的情况下暂停若干时钟循环。

每一累加器负责不同GL,即,存储及更新数据的其部分,且因此含有存储LM

·d

·b:CPM值,告诉桶形移位器将数据移位多少,

·a:将读取及更新的数据的存储器中的地址,

·en:用以实现将经更新数据写入到存储器的信号,

·d

信息d

由核心接收的指令415控制数据被如何处理。给予指令结构的实例以下项:

·地址:发送到累加器的数据的γ个地址,

·移位:发送到累加器的桶形移位器的γ个CPM值,

·更新:用于写入在累加器存储器中的γ个启用信号,

·输出:指示数据是否应在流417上输出的位,

·再循环:指示累加器输出是否应被再循环的位,

·所选择:Mux B 408的地址,

·消耗:合并块402是应从Mux A401获得数据还是继续使用现存数据,

·暂停:由合并块402使用以了解何时暂停给定数目个时钟循环。

区域R

对应于区域R

此计算可从U的列j=1到列j=K

算法1:区域R

沿着编码过程的临时奇偶校验的值无需被存储,这是因为下一步骤仅需要最后几个值

在本发明的优选实施例中,PCM被组织于γ个交织广义层中,使得U的每一及每个列中的d

区域R

图5展示a)编码器的核心及b)累加器实施方案的细节的示意图。粗箭头指示在区域R

在此区域中,由累加器(503、504、505、506)处理的数据是临时奇偶校验c

区域R

在区域R

在R

区域R

在区域R

因为临时奇偶校验

在PCM的最后N

如从方程式(28)可见,此系统的最后一个方程式允许用十分简单的运算获得冗余位t

其中

仍使用T的上三角性质,可递归地从j=1前进到j=N

使用方程式(28)及(30),可推导出用于在区域R

算法2:区域R

沿着编码过程的临时奇偶校验的值无需被存储,这是因为第三步骤仅需要最后几个值

在本发明的优选实施例中,PCM被组织于γ个交织广义层中,使得U的每一及每个列中的d

区域R

为了简化用于区域R

因为临时奇偶校验c被存储于累加器存储器中,所以输出L个冗余位t

图6展示处理区域R

在阶段2a期间,第一指令含有用于第k累加器中的

在阶段2b期间,第二指令辨别核心输出617上的输出

阶段2a与阶段2b处理之间的时间取决于由粗实线给定的管线的长度。为了实现高吞吐量,不同列的第一指令与第二指令交织。表1展示在第一指令的管线采用了三个时钟循环的情况下指令可如何被交织的实例。

表1

为了允许此交织,可期望第一指令的管线采用奇数个时钟循环。

在区域R

针对对角线外的块,间隙约束更加宽松。如果τ

区域R

在区域R

方程式(31)中的系统的前N

其中

在本发明中,假设矩阵S具有满秩,且因此其是可逆的。令A=S

如在段落006中解释,A由可能的大权重循环块组成。用w

本发明描述如何通过依赖于如下描述的特殊技术利用矩阵A的稀疏表示。首先,A被展开成矩形矩阵E,其仅由CPM组成。回想一下,A由一般循环块组成,具有权重w

其中

使w

经展开矩阵E由从方程式(35)推导的列的串接组成:

且用E

针对N

冗余位s的编码可使用E(而非A)来进行,这是因为(33)可被写为:

其中

举例来说,在图7的矩阵E中,矩阵E

算法3:区域R

在本发明的优选实施例中,矩阵S的大小经选取为广义层γ的数目的倍数,N

区域R

存在在区域R

首先,用向量

在阶段3a期间,需要迭代地更新s的值且将其存储于累加器803到806中。原则上,将需要使用额外存储器来存储s,但此处将利用PCM(11)的特殊结构。实际上,在区域R

阶段3a的处理类似于区域R

图8展示在阶段3a的处理期间的指令及数据流。将读取指令的处理展示为粗实线箭头,且将更新指令的处理展示为粗虚线箭头。

如在区域R

表2

一旦s被计算且被存储于累加器存储器中,阶段3b就开始且s的值从累加器存储器读取且被输出到流917。针对s的N

表3

用大小为(N

在本发明的优选实施例中,矩阵S具有数个广义层的大小N

在此段落中描述的优选实施例中,CPM S

·矩阵S是满秩的,

·矩阵S具有给定围长g>4,

·逆矩阵A由低权重循环行列式组成。

针对γ=4的特殊情况,给出此类矩阵的两个不同结构的若干实例。对γ的其它值或S中的CPM的其它组织进行的一般化可容易地从这些实例导出。在优选实施例的这些实例中,矩阵S具有大小4×4个块,且因此最少3个全零块对使其满秩来说是必要的。

1.在标示为S3g的第一结构中,呈现当全零块的数目等于3且对应于S的Tanner图的围长等于g时选取S中的CPM的解决方案。在不失一般性的情况下,可假设S的第一块行及第一块列中的CPM等于单位矩阵,即,S

3个全零块的任何其它位置可通过执行块行/列置换获得。六个CPM(S

2.在标示为S4

六个CPM(S

针对目标围长g∈{6,8,10}的值及循环大小L=32,遵循结构S3

如可见,W中循环的权重相当低,尤其是对围长g=6或g=8来说。

用大小为(N

在此段落中呈现本发明的优选实施例,此时矩阵S的大小是GL的数目的l倍,其中l>1。为了便于呈现,仅呈现γ=4且l=2的情况。所属领域的技术人员可容易地将此实例扩展到l的更大值及γ的其它值。

尽管可适用于大小为(l

代替地,在本发明中提出对矩阵S强加特定结构,此允许递归地使用在段落0049中针对γ×γ矩阵呈现的编码器。所提出的结构在以下方程式中针对γ=4呈现:

其中S′及S″是遵循段落0049的约束的γ×γ矩阵,即,S′=S3

1.使用具有输入

2.累加临时奇偶校验位

3.使用具有输入

在这三个步骤结束时,最终获得了冗余位[s

仅编码两个区:R

存在PCM的维度不够大而不允许在方程式(11)中所描述的三个区域中的组织的情况。实际上,当N

且码字仅具有两个部分,即,x=[u;s]。

在此情况中,本发明中呈现的本发明仅由两个循序步骤组成:

·步骤1:第一步骤使用区域R

·步骤2:第二步骤使用R

与区域R

- 确定准循环低密度奇偶校验码的方法和基于准循环低密度奇偶校验码进行数据编码的系统

- 用于编码准循环低密度奇偶校验码的方法及设备