半导体装置与存储器单元

文献发布时间:2023-06-19 10:38:35

技术领域

本发明是关于一种半导体装置与存储器单元。

背景技术

为了满足高密度交叉点(cross-point)的存储器需求,相变动态随机存取存储器(phase change random access memory,PCRAM)以及电阻式随机存取存储器(resistiverandom access memory,RRAM)的尺寸越来越小,小接点尺寸的选择器(selector)的发展越显重要。举例而言,晶体管(transistor)由于具有较大的接点尺寸因而限制高密度存储器的实现。双端点(two-terminal)存取装置(access device)会是应用于微缩尺寸技术的选择器的一个选择。

交叉点存储器阵列通常需要大量的选择器。选择器的阈值电压(thresholdvoltage)可以通过调节选择层(selector layer)的厚度调整。然而,选择层的厚度若是减少过多,则会导致装置的漏电流(IOFF)增加,因而造成存储器阵列的电力浪费。

发明内容

根据本发明的一些实施方式,一种半导体装置,包含第一电极、第二电极、以及设置于第一电极与第二电极之间的铟掺杂硫基选择层(In-doped chalcogenide-basedselector layer),其中铟掺杂硫基选择层的铟含量为约2at.%至约10at.%。

根据本发明的另一些实施方式,一种存储器单元,包含存取装置以及设置于存取装置上的相变材料。存取装置包含第一电极、第二电极,以及设置于第一电极与第二电极之间的铟掺杂硫基选择层,其中铟掺杂硫基选择层的铟含量为约2at.%至约10at.%。

铟掺杂硫基选择层有助于改善材料的稳定度、黏着性以及工艺中的变异性。因此,使用铟掺杂硫基选择层的半导体装置具有提升产量以及降低周期性衰减的特性。

附图说明

为让本发明的上述和其他目的、特征、优点与实施例能更明显易懂,所附附图的详细说明如下:

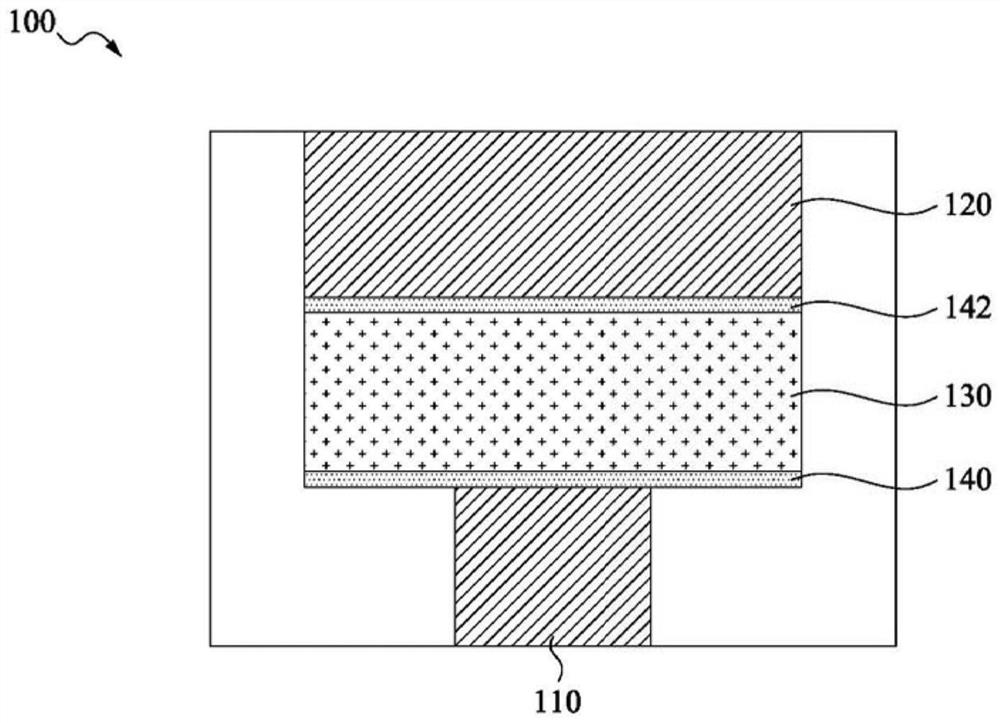

图1其为本发明的一实施方式的选择器的剖面示意图。

图2A至图2E分别为根据本发明的一实施方式中,制造如图1的选择器的方法于不同阶段的示意图。

图3为根据本发明的一些实施方式的装置的立体叠层视图。

图4A为根据一些实施方式中的第一群存储器单元叠层在一平面上的剖面图。

图4B为根据一些实施方式中的第二群存储器单元叠层在另一平面上的剖面图。

【符号说明】

100:选择器

102、104、106:介电层

110、412:第一电极

120、416:第二电极

130、414:铟掺杂硫基选择层

130':铟掺杂硫基材料层

140、142、320、420:刻蚀终止层

200:装置

210:衬底

300、400:存储器单元

310、410:存取装置

350、450:存储器

454:相变材料

456:顶电极

O1、O2:开口

BL:位线

WL:字线

具体实施方式

为使本发明的目的、技术方案和优点更加清楚明白,以下结合具体实施例,并参照附图,对本发明进一步详细说明。本领域技术人员在了解本发明的优选实施例后,当可由本发明所公开的技术,加以改变及修饰,其并不脱离本发明的精神与范围。

关于本文中所使用的『约』、『大约』或『大致约』一般通常系指数值的误差或范围约百分之二十以内,较好地是约百分之十以内,而更佳地则是约百分五之以内。文中若无明确说明,其所提及的数值皆视作为近似值,即如『约』、『大约』或『大致约』所表示的误差或范围。

此外,相对词汇,如『下』或『底部』与『上』或『顶部』,用来描述文中在附图中所示的一元件与另一元件的关系。相对词汇是用来描述装置在附图中所描述之外的不同方位是可以被理解的。例如,如果一附图中的装置被翻转,元件将会被描述原为位于其它元件的『下』侧将被定向为位于其他元件的『上』侧。例示性的词汇『下』,根据附图的特定方位可以包含『下』和『上』两种方位。同样地,如果一附图中的装置被翻转,元件将会被描述原为位于其它元件的『下方』或『之下』将被定向为位于其他元件上的『上方』。例示性的词汇『下方』或『之下』,可以包含『上方』和『上方』两种方位。

参照图1,其为本发明的一实施方式的选择器的剖面示意图。选择器100包含有第一电极110以及设置于第一电极110上的第二电极120。在一些实施例中,第一电极110的材料可以相同或是不同于第二电极120的材料。第一电极110的材料举例而言可以为钨(Tungsten)或是氮化钛(TiN)。第二电极120的材料举例而言可以为钨或是氮化钛。

第一电极110包含有铟掺杂硫基选择层130,铟掺杂硫基选择层130为设置在第一电极110以及第二电极120之间。铟掺杂硫基选择层130中包含有硫族化合物,示例性的硫族化合物可以包含有砷(As)、锗(Ge)、硒(Se)以及铟(In)。换句话说,铟掺杂硫基选择层130可以为铟掺杂的砷锗硒(In-doped AsGeSe)层。在一些实施例中,铟掺杂硫基选择层130的铟含量为约2at.%(原子百分比)至约10at.%。若是铟含量高于10at.%,则漏电流(IOFF)的情况会变得更严重,且元件的阈值电压会下降得过多。

在一些实施例中,铟掺杂硫基选择层130的铟含量为约2at.%至约10at.%,砷含量为约25at.%至约38at.%,锗含量为约8at.%至约20at.%,硒含量为约30at.%至约60at.%。

在一些实施例中,选择器100更包含有两刻蚀终止层140、142,分别设置于第一电极110与铟掺杂硫基选择层130之间以及设置于第二电极120与铟掺杂硫基选择层130之间。在一些实施例中,刻蚀终止层140、142可以为含碳的层或是硅掺杂碳(Si:C)层。

铟掺杂硫基选择层130有助于改善材料的稳定度、黏着性以及工艺中的变异性。因此,使用铟掺杂硫基选择层130的选择器100具有提升产量以及降低周期性衰减(cyclingdegradation)的特性。如前所述,铟掺杂硫基选择层130的铟含量为约2at.%至约10at.%,若是铟含量过低,则改善的情况不明显。在一些实施例中,铟掺杂硫基选择层130的厚度为约15纳米至约45纳米。使用铟掺杂硫基选择层130的选择器100,即便在如此薄的厚度下,仍可提供足够高的阈值电压以及足够低的漏电流,有利于应用于立体的交叉点阵列技术。

举例而言,于一示例性的使用铟掺杂硫基选择层130的选择器100中,在铟掺杂硫基选择层130的厚度约为30纳米的情况下,选择器100的阈值电压约为3.7伏特,在两伏特的操作电压时其漏电流为约700pA。此示例性的选择器100可在10纳秒(ns)完成开启,具有非常快的响应速度。

接着请参照图2A至图2E,其中图2A至图2E分别为根据本发明的一实施方式中,制造如图1的选择器100的方法在不同阶段的示意图。

如图2A所示,第一电极110被制作于介电层102中。第一电极110可以沿伸贯穿介电层102并连接至下层的存取电路(图中未绘示)。存取电路中的元件配置取决于阵列配置。举例而言,存取电路可包含有晶体管与二极管、字线与源极线、导电栓塞,以及半导体衬底中的掺杂区域等。

在一些实施例中,介电层102可以形成在存取电路的顶表面上。接着,沉积并图案化一光刻胶层于介电层102上,其中图案化光刻胶层的步骤包含使用光刻技术,以形成图案化光刻胶层重叠于第一电极110的位置上。而后,以图案化光刻胶层作为掩模,刻蚀介电层102,以形成介层窗于介电层102中。在图案化光刻胶层被移除之后,以导体材料,如钨或氮化钛,填充介层窗。接着执行平坦化工艺,以移除导体材料超出介电层102的部分,进而得到埋设在介电层102中的第一电极110。

参照图2B,刻蚀终止层140与另一介电层104形成于介电层102上。在一些实施例中,刻蚀终止层140的材料不同于介电层104的材料组成。举例而言,刻蚀终止层140可以为含碳的层或是硅掺杂碳(Si:C)层。介电层102、介电层104包含氧化物,如二氧化硅等材料。刻蚀终止层140可以通过任何适当的沉积工艺形成。

介电层104被图案化,以形成开口O1于第一电极110上。图案化介电层104的步骤包含形成图案化光刻胶层于介电层104上,接着以图案化光刻胶层作为掩模刻蚀介电层104,此刻蚀步骤可在抵达刻蚀终止层140时停止。在一些实施例中,未被图案化光刻胶层所覆盖的该部分刻蚀终止层140可以被完全地消耗以露出下方的第一电极110。在一些实施例中,未被图案化光刻胶层所覆盖的该部分刻蚀终止层140可以仍保留在介电层102上。图案化光刻胶层接着被移除。

参照图2C与图2D,铟掺杂硫基材料层130'沉积在开口O1上并填满开口O1。在一些实施例中,铟掺杂硫基材料层130'是通过射频溅射(RFsputter)的工艺制作。靶材设置于邻近于衬底,如设置在第一电极110、介电层104以及刻蚀终止层140上方。在溅射工艺中,靶材的材料会沉积在衬底上。

在溅射工艺中,靶材相对于反应腔的接地区具有一偏压,此偏压可来自于射频源以及直流电源所提供的电力。在溅射工艺中,一气体通过导管由气体源被供应至反应腔中。气体源可包含有不参与反应的气体,如氩、氪、氦、氙等气体,其可用以打击靶材使材料自靶材脱离以沉积于衬底上。由气体所形成的等离子体形成于靶材与衬底之间。等离子体中的离子以加速度朝向靶材移动,致使靶材上的材料脱离靶材。从靶材脱离的材料沉积在衬底上,以形成铟掺杂硫基材料层130'。

在一些实施例中,靶材的材料可以相同或是相似于铟掺杂硫基材料层130'的材料。在一些实施例中,靶材的材料包含砷、锗、硒、铟。在一些实施例中,靶材的铟含量为约2at.%至约10at.%,砷含量为约25at.%至约38at.%,锗含量为约8at.%至约20at.%,硒含量为约30at.%至约60at.%。

当铟掺杂硫基材料层130'沉积并填满开口O1之后,执行平坦化工艺,以移除铟掺杂硫基材料层130'超出于介电层104的部分,进而得到埋设于介电层104的铟掺杂硫基选择层130。在一些实施例中,铟掺杂硫基选择层130的厚度约为15纳米至45纳米之间。

参照图2E,第二电极120形成于铟掺杂硫基选择层130上。在一些实施例中,刻蚀终止层142形成于铟掺杂硫基选择层130以及介电层104上,且另一介电层106形成于刻蚀终止层142上,介电层106被图案化以形成开口O2于其中。图案化介电层106的步骤包含形成图案化光刻胶层于介电层106上。而后,以图案化光刻胶层作为掩模,刻蚀介电层106,刻蚀步骤在抵达刻蚀终止层142时停止。在一些实施例中,未被图案化光刻胶层所覆盖的该部分刻蚀终止层142可以被完全地消耗或是仍保留在介电层104上。图案化光刻胶层接着被移除。

当图案化光刻胶层被移除之后,导体材料,如钨或是氮化钛接着沉积并填满开口O2。接着执行平坦化工艺,以移除导体材料超出介电层106的部分,进而得到埋设在介电层106中并位于铟掺杂硫基选择层130上的第二电极120。

在一些实施例中,铟掺杂硫基选择层130与第二电极120的宽度大致相同,而第一电极110的宽度为小于铟掺杂硫基选择层130与其上的第二电极120的宽度。于另一些实施例中,第一电极110、铟掺杂硫基选择层130以及第二电极120三者的宽度可以大致相同。

接着请参照图3,其为根据本发明的一些实施方式的装置200的立体叠层视图。装置200包含有设置在衬底210上的存储器单元300的阵列。衬底210包含半导体衬底,或是具有电路的半导体衬底。在一些实施例中,衬底210可以为后端工艺(back end of line,BEOL)或是前端工艺(front end of line,FEOL)衬底。阵列中的每一存储器单元300包含有存取装置310以及存储器350,其中存取装置310与存储器350为半导体柱的形式。位线BL,其为导线,连接第一群的存储器单元300,而字线WL,其同样为导线且垂直于位线BL,则是连接第二群的存储器单元300。存取装置310中包含有铟掺杂硫基选择层,在一些实施例中,铟掺杂硫基选择层的铟含量为约2at.%至约10at.%。若是铟掺杂硫基选择层的铟含量高于10at.%,则漏电流的情况会变得更严重,且元件的阈值电压会下降得过多。在一些实施例中,铟掺杂硫基选择层的铟含量为约2at.%至约10at.%,砷含量为约25at.%至约38at.%,锗含量为约8at.%至约20at.%,硒含量为约30at.%至约60at.%。在一些实施例中,存储器单元300进一步垂直叠层成立体存储器阵列。介电层被形成且围绕存储器单元300。在一些实施例中,一个存储器单元300可以叠层于另一个存储器单元300上,并通过介电层相互隔离。在一些实施例中,存取装置310、存储器350以及导线(如字线WL、位线BL)之间更设置有刻蚀终止层320,刻蚀终止层320可以为含碳的层或是硅掺杂碳(Si:C)层。

参照图4A与图4B,其中图4A与图4B分别为根据一些实施方式中的第一群存储器单元400叠层于不同平面的剖面图,其中图4A的剖面位置可参考图3中的线段A-A,图4B其剖面位置可参考图3中的线段B-B。

每一字线WL沿第一方向延伸,并且并联第二群存储器单元400。字线WL同时作为每一存取装置410中的第一电极412。铟掺杂硫基选择层414形成于存取装置410的第一电极412上。铟掺杂硫基选择层414包含硫族化合物,如包含有砷、锗、硒以及铟。换句话说,铟掺杂硫基选择层414可以为铟掺杂的砷锗硒层。在一些实施例中,铟掺杂硫基选择层414的铟含量为约2at.%至约10at.%。若是铟掺杂硫基选择层414的铟含量高于10at.%,则漏电流的情况会变得更严重,且元件的阈值电压会下降得过多。

在一些实施例中,铟掺杂硫基选择层414的铟含量为约2at.%至约10at.%,砷含量为约25at.%至约38at.%,锗含量为约8at.%至约20at.%,硒含量为约30at.%至约60at.%。在一些实施例中,铟掺杂硫基选择层414的厚度为约15纳米至约45纳米。

第二电极416形成于铟掺杂硫基选择层414上。第一电极412以及第二电极416包含导体材料,如钨或是氮化钛。在一些实施例中,铟掺杂硫基选择层414为直接接触且电性连接于第一电极412与第二电极416。于另一些实施例中,额外的层,如刻蚀终止层、导热层、功函数层或是其他适合的层等,皆可设置在第一电极412、铟掺杂硫基选择层414、第二电极416之间。制作存取装置410的步骤可相似于如图2A至图2E所述的步骤。

第二电极416亦作为存储器450的底电极。存储器450电性连接至存取装置410且可被编程以提供两电阻态。在一些实施例中,存储器450可以包含有设置在第二电极416上的相变材料454。相变材料454电性连接至第二电极416。相变材料454的材料特性为可被编程,以提供具有第一电阻的第一相以及具有第二电阻的第二相,其中第一电阻大于第二电阻。

在一些实施例中,相变材料454可以为锗-鍗-碲化合物(Germanium-Antimony-Tellurium compound,GST compound,)如Ge

每一位线BL沿第二方向延伸且并联地连接第一群存储器单元400。存储器450的顶电极456设置在相变材料454上,且连接至位线BL。

在一些实施例中,在导体层以及半导体层之间,如在字线WL(第一电极412)、铟掺杂硫基选择层414、第二电极416,相变材料454以及顶电极456之间进一步设置有刻蚀终止层420,刻蚀终止层420可以为含碳的层或是硅掺杂碳(Si:C)层。

至此,公开了一种存储器单元400,其中每一存储器单元400包含有一选择器一电阻器(1S1R)的半导体结构。此1S1R的存储器单元400容许高密度的立体叠层整合。更进一步地说,通过引入铟掺杂硫基选择层414于存储器单元400中,存储器单元400可以在高密度的交叉点应用中,具有更高的阈值电压,更低的漏电流,以及更好的耐受表现。举例而言,在一使用铟掺杂硫基选择层414的存储器单元400中,在铟掺杂硫基选择层414的厚度约为30纳米的情况下,存储器单元400的阈值电压可大于3伏特,在两伏特的操作电压时其漏电流可小于1nA,其耐受表现可大于1E10个循环。铟掺杂硫基选择层414有助于改善材料的稳定度、黏着性以及工艺中的变异性,因此,元件与元件之间的变化变得更小,进而提升产量以及降低周期性衰减。

以上所述的具体实施例,对本发明的目的、技术方案和有益效果进行了进一步详细说明,所应理解的是,以上所述仅为本发明的具体实施例而已,并不用于限制本发明,凡在本发明的精神和原则之内,所做的任何修改、等同替换、改进等,均应包含在本发明的保护范围之内。

- 形成存储器单元材料的方法及形成半导体装置结构的相关方法、存储器单元材料以及半导体装置结构

- 半导体存储器单元阵列以及半导体只读存储器单元阵列