发光元件

文献发布时间:2023-06-19 10:40:10

技术领域

本发明涉及一种发光元件,尤其涉及一种层叠有多个发光层的发光元件。

背景技术

发光二极管作为无机光源,被广泛用于显示装置、车辆用灯具、一般照明等多种领域。发光二极管具有寿命长、功耗低且响应速度快的优点,因此正快速地替代现有光源。

尤其,显示装置通常利用蓝色、绿色及红色的混合色实现多样的颜色。显示装置的各个像素配备蓝色、绿色及红色的子像素,并且通过这些子像素的颜色来确定特定像素的颜色,并且通过这些像素的组合来实现图像。

发光二极管在显示装置中主要被用作背光源。然而,最近正在开发作为利用发光二极管直接实现图像的下一代显示器的微型LED(micro LED)。

发明内容

技术问题

本发明要解决的课题在于提供一种改善了光效率及光提取的发光元件。

本发明要解决的技术问题并不局限于以上提到的技术问题,未提到的其他技术问题能够通过下文的记载而被本领域技术人员明确地理解。

技术方案

为了达成要解决的一个课题,根据本发明的实施例的发光元件包括:第一发光部,包括第1-1型半导体层、第一活性层、第1-2型半导体层和第一欧姆层;第二发光部,布置于所述第一发光部上,包括第2-1型半导体层、第二活性层、第2-2型半导体层和第二欧姆层;第三发光部,布置于所述第二发光部上,包括第3-1型半导体层、第三活性层、第3-2型半导体层、一面与所述第3-2型半导体层电接触的第一金属图案和一面与所述第3-1型半导体层电接触的第二金属图案;第一垫,与所述第一欧姆层电连接;第二垫,与所述第二欧姆层电连接;第三垫,与所述第一金属图案电连接;公共垫,与所述第1-1型半导体层、所述第2-1型半导体层、所述第二金属图案共同电连接;以及第一过孔结构物,在所述第二金属图案与所述公共垫之间将所述第二金属图案与所述公共垫电连接,其中,所述第二金属图案的一面包括与所述第一过孔结构物相接的第一部分以及与所述第3-1型半导体层相接的第二部分。

根据一实施例,所述第二金属图案的第二部分可以具有所述第一部分的1~5倍的面积。

根据一实施例,所述第二部分可以具有包围所述第一部分的结构。

根据一实施例,所述第一金属图案及所述第二金属图案各自的导电率可以大于所述第一欧姆层及所述第二欧姆层各自的导电率。

根据一实施例,所述第一金属图案可以相接于所述第3-2型半导体层并具有第一厚度,所述第二金属图案贯通所述第3-1型半导体层及所述第三活性层,并且具有大于所述第一厚度的第二厚度。

根据一实施例,所述第一金属图案的与一面对向的另一面的高度可以与所述第二金属图案的与一面对向的另一面相同或者更高。

根据一实施例,所述第二金属图案还可以具有和所述一面对向的另一面,所述一面的宽度大于另一面的宽度,所述另一面的宽度大于所述第一过孔结构物的宽度。

根据一实施例,所述第二金属图案可以具有与所述第一过孔结构物邻近的部分的外侧壁凸出的结构。

根据一实施例,所述发光元件还可以包括:第二过孔结构物,在所述第一金属图案与所述第三垫之间将所述第一金属图案与所述第三垫电连接,其中,所述第一金属图案的一面包括与所述第二过孔结构物相接的第一部分以及与所述第3-2型半导体层相接的第二部分。

根据一实施例,所述第一金属图案的第二部分可以具有所述第一部分的1~5倍的面积。

根据一实施例,所述第二部分可以具有包围所述第一部分的结构。

根据一实施例,所述第一金属图案可以具有大于所述第二过孔结构物的宽度。

根据一实施例,所述发光元件还可以包括:第二过孔结构物,将所述第一欧姆层与所述第一垫之间电连接;第三过孔结构物,将所述第二欧姆层与所述第二垫之间电连接;第四过孔结构物,将所述第一金属图案与所述第三垫之间电连接;以及第一钝化膜,将所述第一过孔结构物至所述第四过孔结构物分别与所述第一发光部至所述第三发光部电绝缘,其中,所述第一钝化膜具有包围所述第一过孔结构物至所述第四过孔结构物各自的外侧壁的第一部分以及布置于所述第3-1型半导体层与所述第一垫至所述第三垫及所述公共垫之间的第二部分,所述第一钝化膜的所述第二部分具有大于或等于所述第一部分的厚度。

根据一实施例,所述发光元件还可以包括:第五过孔结构物,将所述公共垫与所述第1-1型半导体层之间电连接;以及第六过孔结构物,将所述公共垫与所述第2-1型半导体层之间电连接其中,所述第一钝化膜的第一部分包围所述第五过孔结构物及第六过孔结构物各自的外侧壁。

根据一实施例,所述第一过孔结构物至所述第六过孔结构物可以分别包括布线膜以及包围布线膜外侧壁的种子膜。

根据一实施例,所述第二金属图案可以具有与所述第一过孔结构物相接的一面和与该一面对向的另一面,所述发光元件还包括第五过孔结构物,所述第五过孔结构物包括:第一图案,与所述第二金属图案的另一面及所述第2-1型半导体层电接触;以及第二图案,将所述第一金属图案与所述第1-1型半导体层之间电连接。

根据一实施例,所述第一过孔结构物至所述第五过孔结构物可以分别包括布线膜以及包围布线膜外侧壁的种子膜。

根据一实施例,所述发光元件还可以包括:钝化膜,包围所述第一发光部至所述第三发光部各自的外侧壁;以及外侧种子膜,包围所述钝化膜的外侧壁。

根据一实施例,所述发光元件还可以包括:第一外侧种子膜,包围所述第一发光部至所述第三发光部中的一个或两个的外侧壁;第一钝化膜,布置于所述第一发光部至所述第三发光部中的至少一个与所述第一外侧种子膜之间;第二外侧种子膜,包围所述第一发光部至所述第三发光部中的剩余的发光部的外侧壁;以及第二钝化膜,布置于所述第一发光部至所述第三发光部中的剩余的发光部与所述第二外侧种子膜之间。

根据一实施例,与所述第1-1型半导体层、所述第2-1型半导体层及所述第3-1型半导体层各自的一面对向的另一面可以具有多个凸起。

根据一实施例,所述第1-1型半导体层、所述第2-1型半导体层及所述第3-1型半导体层可以分别包括n型半导体,所述第1-2型半导体层、所述第2-2型半导体层及所述第3-2型半导体层分别包括p型半导体。

根据一实施例,所述第1-1型半导体层、所述第2-1型半导体层及所述第3-1型半导体层可以分别包括p型半导体,所述第1-2型半导体层、所述第2-2型半导体层及所述第3-2型半导体层分别包括n型半导体。

其他实施例的具体事项包含在具体实施方式以及附图中。

有益效果

对于根据本发明的一示例的发光元件而言,在发出红色光的发光部中,在n型半导体层及p型半导体层形成有金属图案,从而能够提高欧姆特性。

并且,通过将第1-1型半导体层、第2-1型半导体层及第3-1型半导体层共同电连接于公共垫,从而相比于将第1-2型半导体层、第2-2型半导体层及第3-2型半导体层共同连接的情形能够更稳定地接收电流。

并且,在发光元件的外侧壁形成种子膜,从而能够反射从发光元件发出的光而提高发光元件的光效率。

附图说明

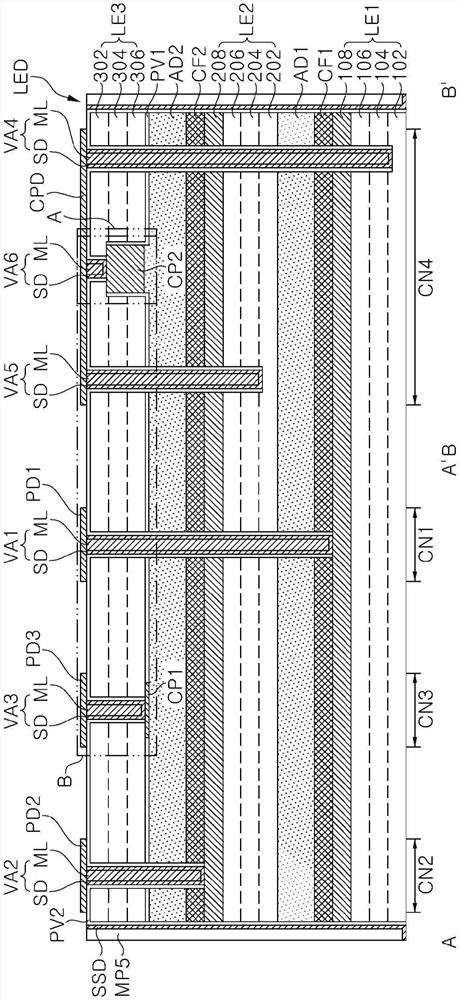

图1a是用于说明根据本发明的一实施例的发光元件的平面图。

图1b是将图1a的发光元件沿A-A'及B-B'截取的剖视图。

图1c是放大图1b的A的放大图。

图1d是放大图1b的B的放大图。

图1e是图示于图1b的发光元件的第一导电图案的平面图。

图1f是图示于图1b的发光元件的第二导电图案的平面图。

图1g是用于说明根据本发明的一实施例的另一发光元件的平面图。

图1h是将图1g的发光元件沿A-A'及B-B'截取的剖视图。

图1i是示出根据本发明的一实施例的发光元件的第一发光部至第三发光部各自的,关于每单位面积的电流密度的标准外量子效率的曲线图。

图2a是用于说明根据本发明的另一实施例的发光元件的平面图。

图2b是沿C-C'截取图2a的发光元件的剖视图。

图3至图28是用于说明根据一实施例的用于制造发光元件的方法的剖视图。

图29至图46是用于说明根据本发明的另一实施例的制造发光元件的方法的剖视图。

具体实施方式

为了充分理解本发明的构成及效果,参照附图对本发明的优选实施例进行说明。然而,本发明并不局限于以下公开的实施例,可以实现为多种形态,并且能够进行多样的变更。

并且,在本发明的实施例中使用的术语除非被另外定义,否则可以被解释为对相应技术领域中具有通常知识的人员通常已知的含义。

以下,参照附图对根据本发明的实施例的发光元件进行详细说明。

图1a是用于说明根据本发明的一实施例的发光元件的平面图,图1b是将图1a的发光元件沿A-A'及B-B'截取的剖视图,图1c是放大图1b的A的放大图,图1d是放大图1b的B的放大图,图1e是图示于图1b的发光元件的第一导电图案的平面图,图1f是图示于图1b的发光元件的第二导电图案的平面图。图1g是用于说明根据本发明的一实施例的另一发光元件的平面图,图1h是将图1g的发光元件沿A-A'及B-B'截取的剖视图。图1i是示出根据本发明的一实施例的发光元件的第一发光部至第三发光部各自的关于每单位面积的电流密度的标准外量子效率的曲线图。

参照图1a至图1h,发光元件可以包括第一发光部LE1、第二发光部LE2及第三发光部LE3。

从平面上观察,第一发光部LE1、第二发光部LE2及第三发光部LE3可以是具有位于同一平面的外侧壁的四边形结构。从平面上观察,发光元件可以包括第一边角CN1、第二边角CN2、第三边角CN3及第四边角CN4。

根据一示例,当第二发光部LE2偏向一方向而布置于第一发光部LE1上,并且第三发光部LE3偏向一方向而布置于第二发光部LE2上时,在第一发光部LE1发出的光中既存在经过第二发光部LE2及第三发光部LE3的光,也存在未经过第二发光部LE2及第三发光部LE3的光,从而存在发生混色的情况。根据本实施例,第一发光部LE1、第二发光部LE2及第三发光部LE3为具有同一个外侧壁的四边形结构,从而能够预先防止在偏向一方向的情况下发生的混色。

当第一发光部LE1的一面与第二发光部LE2相向时,第一发光部LE1的另一面可以是发光元件的光提取面。在第一发光部LE1的另一面是发光元件的光提取面的情况下,第一发光部LE1的波长可以最短,并且第二发光部LE2的波长大于第一发光部LE1的波长并小于第三发光部LE3的波长,而且第三发光部LE3的波长最长。例如,第一发光部LE1可以发出蓝色光,第二发光部LE2发出绿色光,第三发光部LE3发出红色光。

第一发光部LE1可以包括垂直层叠的第一n型半导体层102、第一活性层104、第一p型半导体层106及第一欧姆层108。第二发光部LE2可以包括垂直层叠的第二n型半导体层202、第二活性层204、第二p型半导体层206及第二欧姆层208。第三发光部LE3可以包括垂直层叠的第三p型半导体层306、第三活性层304、第三n型半导体层302、与第三p型半导体层306电连接的第一导电图案CP1以及与第三n型半导体层302电连接的第二导电图案CP2。

第一n型半导体层102、第二n型半导体层202及第三n型半导体层302分别可以是掺杂Si的氮化镓系半导体层。第一p型半导体层106、第二p型半导体层206及第三p型半导体层306分别可以是掺杂Mg的氮化镓系半导体层。第一活性层104、第二活性层204及第三活性层304分别可以包括多量子阱结构(Multi Quantum Well:MQW),并且调节其组成比以发出所期望的峰值波长的光。第一欧姆层108及第二欧姆层208分别可以利用氧化锡(SnO

参照图1b及图1d,第一导电图案CP1可以与位于发光元件的四个边角中的一个(例如,第三边角CN3)的第三p型半导体层306电接触。在第二发光部LE2与第三p型半导体层306之间,第一导电图案CP1的一面可以相接于第三p型半导体层306的一面而布置。作为一例,第一导电图案CP1可以具有第一厚度TH1。例如,第一厚度TH1可以是0.3~0.4μm。

第二导电图案CP2可以与位于发光元件的四个边角中的另一个(例如,第四边角CN4)的第三n型半导体层302电接触。第二导电图案CP2可以向第三发光部LE3内部延伸,并且具有贯通第三p型半导体层306及第三活性层304的柱状结构。通过包围第二导电图案CP2的外侧壁的第一钝化膜PV1,第二导电图案CP2可以与第三p型半导体层306及第三活性层304绝缘。第一钝化膜PV1可以包括选自由SiN

第二导电图案CP2的一面可以与第三n型半导体层302的一面相接,与第二导电图案CP2的一面对向的另一面可以位于比邻近于第二发光部的第三p型半导体层306的表面低或者相同的高度。作为一例,第二导电图案CP2可以具有大于第一导电图案CP1的第二厚度TH2,例如,可以具有3~4μm的厚度。如上所述,向第三发光部LE3内部延伸的第二导电图案CP2的第二厚度TH2形成为大于第一导电图案CP1的第一厚度TH1,从而能够减小第一导电图案CP1的另一面与第二导电图案CP2的另一面的高度差异。

根据如图1b及图1c所示的本发明的一实施例,在第二导电图案CP2中邻近于第六过孔结构物VA6的上部UP的第一宽度WT1可以大于贯通第三p型半导体层306及第三活性层304的下部LP的第二宽度WT2。第二导电图案CP2的下部LP可以具有预定的第二宽度WT2,第二导电图案CP2的上部UP可以具有越向上宽度越宽的结构。第一宽度WT1可以是第二导电图案CP2的最大宽度。并且,邻近于第六过孔结构物VA6的第二导电图案CP2的上部外侧壁可以凸出而具有尖锐的边缘部位SP。

根据一实施例,第二发光部LE2的第二n型半导体层202可以包括相接于第二活性层204的一面以及与一面对向的另一面。在第二n型半导体层202的另一面可以形成有多个微小凸起(参照图6)。微小凸起可以彼此均匀,也可以不均匀。虽然未图示,在第一发光部LE1的第一n型半导体层102的一面以及第三发光部LE3的第三n型半导体层302的一面也分别可以形成有多个微小凸起。

参照图1a至图1h,第一发光部LE1、第二发光部LE2及第三发光部LE3各自的外侧壁可以是同一平面。以下,发光元件的外侧壁表示第一发光部LE1、第二发光部LE2及第三发光部LE3各自的外侧壁。

发光元件还可以包括:第一粘结部AD1及第一滤色器CF1,布置于第一发光部LE1与第二发光部LE2之间;第二粘结部AD2及第二滤色器CF2,布置于第二发光部LE2与第三发光部LE3之间。

第一粘结部AD1及第二粘结部AD2分别具有粘结特性,并且包括诸如SOG(SiliconOn Glass)、SiO

根据一实施例,第二导电图案CP2贯通第三p型半导体层、第三活性层而布置,第一导电图案CP1布置于第三p型半导体层上,从而为了减小第一导电图案CP1与第二导电图案CP2之间的阶梯差,第二导电图案CP2可以形成为大于第一导电图案CP1的厚度。当布置于第一导电图案CP1及第二导电图案CP2的一面的第二粘结部AD2与第二滤色器CF2粘合时,不会由于第一导电图案CP1与第二导电图案CP2的减小后的阶梯差而产生第二粘结部AD2凹陷或凸出的部分,从而能够实质上均匀地形成。在第二粘结部AD2凹陷或凸出的情况下,当在凹陷的部分或凸出的部分形成气隙(air gap)并通过热压粘合第二粘结部AD2时,气隙内的空气膨胀,从而可能使得第二粘结部AD2与第二导电图案CP2之间发生剥离。根据本发明的一实施例,形成第一导电图案CP1与第二导电图案CP2之间的厚度差而减小与第二粘结部AD2相接的第一导电图案CP1和第二导电图案CP2的阶梯差,从而能够防止第二粘结部AD2形成凹陷的部分或凸出的部分,并且能够防止由于气隙造成的剥离。

在第三发光部LE3上,可以设置有:第一垫PD1,布置于第一边角CN1并与第一欧姆层108电连接;第二垫PD2,布置于第二边角CN2并与第二欧姆层208电连接;第三垫PD3,布置于第三边角CN3并与第一导电图案CP1电连接;以及公共垫CPD,布置于第四边角CN4并将第一n型半导体层至第三n型半导体层302共同电连接。

作为一例,第一垫PD1、第二垫PD2、第三垫PD3及公共垫CPD分别可以包括选自由Au、Ag、Ni、Al、Rh、Pd、Ir、Ru、Mg、Zn、Pt、Hf、Cr、Ti及Cu构成的组中的至少一种。并且,可以包括上述列举的物质的合金。

作为一例,第一垫PD1、第二垫PD2、第三垫PD3及公共垫CPD在平面上分别可以具有相同的宽度WT及形状。例如,在发光元件为10×10μm的情况下,第一垫PD1、第二垫PD2、第三垫PD3及公共垫CPD可以分别具有3~4μm的宽度,并且第一垫PD1、第二垫PD2、第三垫PD3及公共垫CPD之间分别具有2~4μm的宽度。

发光元件还可以包括:第一过孔结构物VA1,布置于第一边角CN1并将第一欧姆层108与第一垫PD1电连接;第二过孔结构物VA2,布置于第二边角CN2并将第二欧姆层208与第二垫PD2电连接;以及第三过孔结构物VA3,布置于第三边角CN3并将第一导电图案CP1与第三垫PD3电连接。并且,发光元件还可以包括:第四过孔结构物VA4,布置于第四边角CN4并将第一n型半导体层102与公共垫CPD电连接;第五过孔结构物VA5,将第二n型半导体层202与公共垫CPD电连接;第六过孔结构物VA6,将第二导电图案CP2与公共垫CPD电连接。

第一过孔结构物VA1可以贯通第三发光部LE3、第二粘结部AD2、第二滤色器CF2、第二发光部LE2、第一粘结部AD1及第一滤色器CF1。第二过孔结构物VA2可以贯通第三发光部LE3、第二粘结部AD2及第二滤色器CF2。第三过孔结构物VA3可以贯通第三发光部LE3。第四过孔结构物VA4可以贯通第三发光部LE3、第二粘结部AD2、第二滤色器CF2、第二发光部LE2、第一粘结部AD1、第一滤色器CF1、第一欧姆层108、第一p型半导体层106及第一活性层104。第五过孔结构物VA5可以贯通第三发光部LE3、第二粘结部AD2、第二滤色器CF2、第二欧姆层208、第二p型半导体层206及第二活性层204。第六过孔结构物VA6可以贯通第三n型半导体层302。参照图1a及图1b,第一过孔结构物VA1、第二过孔结构物VA2、第三过孔结构物VA3、第四过孔结构物VA4、第五过孔结构物VA5及第六过孔结构物VA6可以分别具有相同的第三宽度WT3。第三宽度WT3可以是1μm以下。

参照图1g至图1h,第一过孔结构物VA1、第二过孔结构物VA2、第三过孔结构物VA3、第四过孔结构物VA4、第五过孔结构物VA5及第六过孔结构物VA6可以分别具有互不相同的宽度。作为一例,第一过孔结构物VA1、第二过孔结构物VA2、第三过孔结构物VA3、第四过孔结构物VA4及第五过孔结构物VA5可以分别具有相同的第三宽度WT3,但是第六过孔结构物VA6具有大于第三宽度WT3的第四宽度WT4。例如,当第一发光部LE1发出蓝色光,第二发光部LE2发出绿色光,第三发光部LE3发出红色光时,在第一发光部、第二发光部及第三发光部中,根据每单位面积的电流密度的最大外量子效率(External Quantum Efficiency:EQE)可以不同。在图1i中,x轴表示发光单元的每单位面积的电流密度,y轴表示标准外量子效率(normalized EQE)。参照图1i,为了实现100%最大外量子效率,第一发光部LE1及第二发光部LE2要求每单位面积约2A/cm

另外,虽然未图示,但是出于相同的理由,与第三发光部的第三p型半导体层306电连接的第三过孔结构物VA3可以具有大于第一过孔结构物VA1、第二过孔结构物VA2、第四过孔结构物VA4、第五过孔结构物VA5及第六过孔结构物VA6各自的第三宽度WT3的第四宽度WT4。

根据如图1b及图1e所示的本发明的一实施例,第三过孔结构物VA3的一面可以与第一导电图案CP1的一面相接。第一导电图案CP1可以具有大于第三宽度WT3的宽度。第一导电图案CP1的一面可以同时与第三过孔结构物VA3及第三p型半导体层306的一面相接。第一导电图案CP1可以包括与第三过孔结构物VA3相接的第一部分PT1以及与第三p型半导体层306相接的第二部分PT2。第二部分PT2可以具有包围第一部分PT1的结构。第二部分PT2的面积可以是第一部分PT1的面积的1~5倍。

根据如图1b及图1f所示的本发明的一实施例,第六过孔结构物VA6的一面可以与第二导电图案CP2的一面相接。第二导电图案CP2可以具有大于第三宽度WT3的宽度。参照图1c,第二导电图案可以具有第一宽度WT1及第二宽度WT2,第六过孔结构物VA6的第三宽度WT3可以小于第一宽度WT1,并且小于第二宽度WT2。第二宽度WT2可以小于第一宽度WT1,并且大于第三宽度WT3。第二导电图案CP2的一面可以同时与第六过孔结构物VA6及第三n型半导体层302相接。第二导电图案CP2可以包括与第六过孔结构物VA6相接的第一部分PT1以及与第三n型半导体层302相接的第二部分PT2。第二部分PT2可以具有包围第一部分PT1的结构。第二部分PT2的面积可以是第一部分PT1的面积的1~5倍。

参照图1a及图1h,第一过孔结构物VA1、第二过孔结构物VA2、第三过孔结构物V43、第四过孔结构物VA4、第五过孔结构物VA5及第六过孔结构物VA6可以分别包括种子膜(seedlayer)SD及布线膜(plating layer)ML,并且种子膜SD可以具有包围布线膜ML的外侧壁的结构。作为一例,种子膜SD及布线膜ML可以包括铜,并且种子膜SD内的铜密度高于布线膜ML内的铜密度。

发光元件还可以包括包围第一过孔结构物VA1、第二过孔结构物VA2、第三过孔结构物V43、第四过孔结构物VA4、第五过孔结构物VA5及第六过孔结构物VA6各自的外侧壁并向第三n型半导体层302的表面延伸的第二钝化膜PV2。第二钝化膜PV2向第三n型半导体层302的表面延伸,从而能够将第三n型半导体层302与第一垫PD1、第二垫PD2、第三垫PD3及公共垫CPD之间电绝缘。第二钝化膜PV2可以包括选自由SiN

根据一实施例,对于第二钝化膜PV2而言,向第三n型半导体层302的表面延伸的部分的厚度可以大于或等于包围第一过孔结构物VA1、第二过孔结构物VA2、第四过孔结构物VA4、第五过孔结构物VA5及第六过孔结构物VA6各自的外侧壁的部分的厚度。

由于布置于第三n型半导体层302表面的第二钝化膜PV2的厚度大于或等于包围第一过孔结构物VA1、第二过孔结构物VA2、第四过孔结构物VA4、第五过孔结构物VA5及第六过孔结构物VA6各自的外侧壁的部分的厚度,因此当从基板分离发光元件时基板弯曲,此时布置于第三n型半导体层302表面的第二钝化膜PV2能够防止第一垫PD1、第二垫PD2、第三垫PD3及公共垫CPD从发光元件剥离。

还可以包括包围发光元件的外侧壁而布置的外侧种子膜SSD。根据一实施例,第二钝化膜PV2可以延伸至外侧种子膜SSD与发光元件之间而布置。外侧种子膜SSD的两端面与第四过孔结构物VA4的两端面实质上可以为同一平面。根据本发明的一实施例,在分别从第一发光部LE1、第二发光部LE2及第三发光部LE3发出的光中,向侧面方向发出的光可以被外侧种子膜SSD反射,从而能够提高发光元件的光效率。

选择性地,根据一实施例,还可以包括包围外侧种子膜SSD的外侧壁的掩模图案MP5。通过掩模图案MP5,发光元件可以和外部电绝缘。掩模图案MP5可以包括诸如光致抗蚀剂或聚酰亚胺、环氧等不透明且具有绝缘特性的物质。

根据一实施例,在完成发光元件后被去除的基板(未图示)在第一发光部LE1的第一p型半导体层106之间出现弯曲(bowing)现象,由于弯曲现象,当在基板上对多个发光元件之间进行元件分离的工序中,可能在发光元件发生裂痕(crack)。通过包围发光元件的外侧壁的掩模图案MP5能够防止裂痕。

在图1a至图1h中所述的发光元件中,以第一n型半导体层102、第二n型半导体层202及第三n型半导体层302分别电连接于公共垫CPD的情形进行说明,然而第一p型半导体层106、第二p型半导体层206及第三p型半导体层306分别也可以电连接于公共垫CPD。

图2a是用于说明根据本发明的另一实施例的发光元件的平面图。图2b是沿C-C'截取图2a的发光元件的剖视图。

参照图2a及图2b,发光元件可以包括第一发光部LE1、第二发光部LE2及第三发光部LE3。

第一发光部LE1可以包括垂直层叠的第一n型半导体层102、第一活性层104、第一p型半导体层106及第一欧姆层108。第二发光部LE2可以包括垂直层叠的第二欧姆层208、第二p型半导体层206、第二活性层204及第二n型半导体层202。第三发光部LE3可以包括垂直层叠的第三p型半导体层306、第三活性层304及第三n型半导体层302。第三发光部LE3还可以包括与第三p型半导体层306电连接的第一导电图案CP1和与第三n型半导体层302电连接的第二导电图案CP2。

发光元件还可以包括:第一粘结部AD1及第一滤色器CF1,布置于第一发光部LE1与第二发光部LE2之间;第二粘结部AD2、第二滤色器CF2及第三粘结部AD3,布置于第二发光部LE2与第三发光部LE3之间。第一滤色器CF1可以布置于第一欧姆层108与第一粘结部AD1之间。选择性地,第二滤色器CF2可以布置于第三p型半导体层306与第三粘结部AD3之间。第一粘结部AD1布置于第一滤色器CF1与第二欧姆层208之间而将第一发光部LE1与第二发光部LE2之间粘合。根据一实施例,第一粘结部AD1可以向贯通第一滤色器CF1、第一欧姆层108、第一p型半导体层106及第一活性层104的槽的内侧壁延伸而布置。第二粘结部AD2可以布置于第二n型半导体层202与第三粘结部AD3之间。第三粘结部AD3可以布置于第二粘结部AD2与第二滤色器CF2之间,并且向贯通第二滤色器CF2、第二p型半导体层206及第二活性层204的槽的内侧壁延伸而布置。

根据一实施例,第一导电图案CP1可以电接触于第三p型半导体层306上。第一导电图案CP1可以在第二发光部LE2与第三p型半导体层306之间布置为一面相接于第三p型半导体层306一面。作为一例,第一导电图案CP1可以具有贯通第二滤色器CF2及第三粘结部AD3的柱状结构。

第二导电图案CP2可以与第三n型半导体层302电接触。第二导电图案CP2可以向第三发光部LE3内部延伸,并且具有贯通第三p型半导体层306及第三活性层304的柱状结构。第二导电图案CP2可以具有大于第一导电图案CP1的厚度。作为一例,第二导电图案CP2可以具有贯通第三粘结部AD3、第二滤色器CF2、第三p型半导体层306及第三活性层304的柱状结构。

第二导电图案CP2的另一面可以位于比第一导电图案CP1高的高度,但是第二导电图案CP2的一面和第一导电图案CP1的一面可以布置于同一个平面。第一导电图案CP1的一面和第二导电图案CP2的一面作为当将第三发光部LE3粘结于第二发光部LE2时相接的面,通过使第一导电图案CP1的一面与第二导电图案CP2的一面作为同一个平面,从而能够提高粘结台性。

发光元件在平面上可以具有四边形结构,并且包括第一边角CN1、第二边角CN2、第三边角CN3及第四边角CN4。在第三发光部LE3上,可以设置有:第一垫PD1,布置于第一边角CN1并与第一欧姆层108电连接;第二垫PD2,布置于第二边角CN2并与第二欧姆层208电连接;第三垫PD3,布置于第三边角CN3并与第一导电图案CP1电连接;以及公共垫CPD,布置于第四边角CN4并将电连接第一n型半导体层102、第二n型半导体层202及第三n型半导体层302分别共同电连接。

根据一实施例,发光元件还可以包括:第一过孔结构物VA1,将第一垫PD1与第一欧姆层108电连接;第二过孔结构物VA2,将第二垫PD2与第二欧姆层208电连接;第三过孔结构物VA3,将第三垫PD3与第一导电图案CP1电连接;以及第四过孔结构物VA4,将公共垫CPD与第一n型半导体层102、第二n型半导体层202及第三n型半导体层302电连接。

第一过孔结构物VA1可以包括:第一图案PT1_1,与第一p型半导体层106电接触,并且贯通第一粘结部AD1及第二发光部LE2;第二图案PT2_1,与第一图案PT1_1电接触,并且布置于第二发光部LE2与第三发光部LE3之间;第三图案PT3_1,在第二图案PT2_1与第一垫PD1之间贯通第三发光部LE3而将第二图案PT2_1与第一垫PD1之间电连接。作为一例,第一图案PT1_1可以包括第一布线膜ML1和包围第一布线膜ML1的外侧壁的第一种子膜SD1。在这种情况下,第一图案PT1_1可以包括铜等金属。并且,第一图案PT1_1的外侧壁可以被第一钝化膜PV1包围而与第二发光部LE2电绝缘。第一钝化膜PV1可以具有包围第一图案PT1_1的外侧壁并向第二n型半导体层202表面延伸的结构。第一钝化膜PV1可以包括SiO

第二钝化膜PV2可以包括:第一图案PT1_2,贯通第二n型半导体层202、第二活性层204及第二p型半导体层206而与第二欧姆层208电接触;第二图案PT2_2,布置于第二发光部LE2与第三发光部LE3之间并与第一图案PT1_2电接触;第三图案PT3_2,贯通第二粘结部AD2及第三发光部LE3并将第二图案PT2_2与第二垫PD2电连接。作为一例,第一图案PT1_2可以包括第一布线膜ML1和包围第一布线膜ML1的外侧壁的第一种子膜SD1。在这种情况下,第一图案PT1_2可以包括铜等金属。并且,第一图案PT1_2的外侧壁可以被第一钝化膜PV1包围而与第二发光部LE2电绝缘。第一钝化膜PV1可以具有分别包围第一过孔结构物VA1的第一图案PT1_1的外侧壁和第二过孔结构物VA2的第一图案PT1_2的外侧壁并向第二n型半导体层202表面延伸的结构。第二图案PT2_2可以被第二粘结部AD2包围其外侧壁,并且第二图案PT2_2的一面与第一图案PT1_2接触,与一面对向的另一面与第三图案PT3_2接触。第一过孔结构物VA1的第二图案PT2_1与第二过孔结构物VA2的第二图案PT2_2可以位于同一高度。第二图案PT2_2的厚度和第二粘结部AD2的厚度可以实质上相同。第二图案PT2_2可以包括Au等金属。第三图案PT3_2可以包括第二布线膜ML2和包围第二布线膜ML2的外侧壁的第二种子膜SD2。在这种情况下,第三图案PT3_2可以包括铜等金属。第二过孔结构物VA2的第三图案PT3_2与第一过孔结构物VA1的第三图案PT3_1可以具有实质上相同的结构。另外,第三图案PT3_2可以被第二钝化膜PV2包围而与第三发光部LE3电绝缘。第二钝化膜PV2可以具有分别包围第一过孔结构物VA1的第三图案PT3_1的外侧壁和第二过孔结构物VA2的第三图案PT3_2的外侧壁并向第三n型半导体层302表面延伸的结构。

第三过孔结构物VA3可以贯通第三n型半导体层302、第三活性层304及第三p型半导体层306而将第一导电图案CP1与第三垫PD3之间电连接。第三过孔结构物VA3可以包括第二布线膜ML2和包围第二布线膜ML2的外侧壁的第二种子膜SD2。在这种情况下,第三过孔结构物VA3可以包括铜等金属。

根据一实施例,第三过孔结构物VA3的一面可以与第一导电图案CP1的一面相接。第一导电图案CP1可以具有大于第三过孔结构物VA3的宽度的宽度。第一导电图案CP1的一面可以同时与第三过孔结构物VA3及第三p型半导体层306的一面相接。第一导电图案CP1可以包括与第三过孔结构物VA3相接的第一部分PT1以及与第三p型半导体层306相接的第二部分PT2。第二部分PT2可以具有包围第一部分PT1的结构。第二部分PT2的面积可以是第一部分PT1的面积的1~5倍。

第四过孔结构物VA4可以包括:第一图案PT1_4,与第一n型半导体层102电接触并贯通第一活性层104、第一p型半导体层106、第一欧姆层108、第一滤色器CF1及第二发光部LE2;第二图案PT2_4,一面与第一图案PT1_4及第二n型半导体层202电接触,另一面与第二导电图案CP2电接触,并且布置于第二粘结部AD2内;第三图案PT3_4,将第二导电图案CP2与公共垫CPD之间电连接。第一图案PT1_4可以包括第一布线膜ML1和包围第一布线膜ML1的外侧壁的第一种子膜SD1。第一钝化膜PV1可以包围第一图案PT1_4的外侧壁。并且,第一粘结部AD1可以具有包围被第一钝化膜PV1包裹的第一图案PT1_4的外侧壁的一部分并向第一滤色器CF1表面延伸的结构。第二图案PT2_4的外侧壁可以具有被第一粘结部AD1包裹的结构。第三图案PT3_4可以包括第二布线膜ML2和包围第二布线膜ML2的外侧壁的第二种子膜SD2,并且具有外侧壁被第二钝化膜PV2包围的结构。第二钝化膜PV2可以具有向第三n型半导体层302表面延伸并且包围第一过孔结构物VA1的第三图案PT3_1、第二过孔结构物VA2的第三图案PT3_2和第四过孔结构物VA4的第三图案PT3_4各自的外侧壁的结构。

根据一实施例,第四过孔结构物VA4的一面可以与第二导电图案CP2的一面相接。第二导电图案CP2可以具有大于第四过孔结构物VA4的宽度的宽度。第二导电图案CP2的一面可以包括与第四过孔结构物VA4相接的第一部分PT1以及与第三n型半导体层302相接的第二部分PT2。第二部分PT2可以具有包围第一部分PT1的结构。第二部分PT2的面积可以是第一部分PT1的面积的1~5倍。

第一发光部LE1及第二发光部LE2各自的外侧壁可以是同一平面。沿第一发光部LE1及第二发光部LE2各自的外侧壁可以设置有第一外侧种子膜SSD1。第一钝化膜PV1可以在第一外侧种子膜SSD1与第一发光部LE1及第二发光部LE2各自的外侧壁之间延伸,从而第一发光部LE1及第二发光部LE2通过第一钝化膜PV1而与第一外侧种子膜SSD1绝缘。并且,在第一外侧种子膜SSD1外侧壁还可以配备有掩模图案MP3。

第二粘结部AD2的外侧壁可以具有从第一发光部LE1、第二发光部LE2及第三发光部LE3各自的外侧壁凸出的结构。还可以设置有:第二外侧种子膜SSD2,布置于第三发光部LE3的外侧壁上,并且向第二粘结部AD2的暴露的边缘部位上表面延伸。第二钝化膜PV2在第二外侧种子膜SSD2与第三发光部LE3外侧壁之间延伸,从而第三发光部LE3通过第二钝化膜PV2与第二外侧种子膜SSD2绝缘。并且,在第二外侧种子膜SSD2外侧壁还可以配备有掩模图案MP4。

在图2a及图2b所述的发光元件中,以第一n型半导体层102、第二n型半导体层202及第三n型半导体层302分别电连接于公共垫CPD的情形为例进行说明,第一p型半导体层106、第二p型半导体层206及第三p型半导体层306也可以分别电连接于公共垫CPD。

以下,对制造图1a至图1f的发光元件的方法进行说明。

图3至图28是用于说明根据一实施例的用于制造发光元件的方法的剖视图。

参照图3,可以在第一基板100上形成包括第一n型半导体层102、第一活性层104、第一p型半导体层106及第一欧姆层108的第一发光部LE1。可以在第一发光部LE1上形成第一滤色器CF1。第一滤色器CF1可以选择性地省略。

第一基板100在平面上可以具有四边形结构,并且包括第一边角CN1、第二边角CN2、第三边角CN3及第四边角CN4。第一发光部LE1及第一滤色器CF1可以具有与第一基板100对应的四边形结构,第一基板100的外侧壁与第一发光部LE1及第一滤色器CF1各自的外侧壁可以是同一平面。

参照图4,可以在第二基板200上形成包括第二n型半导体层202、第二活性层204、第二p型半导体层206及第二欧姆层208的第二发光部LE2。

根据一实施例,在将第二n型半导体层202生长在第二基板200上之前,可以使未掺杂掺杂剂的氮化镓层生长。

第二基板200在平面上可以具有四边形结构,第二发光部LE2可以具有与第二基板200对应的四边形结构,第二基板200的外侧壁与第二发光部LE2的各个外侧壁可以是同一平面。另外,第二基板200可以具有与第一基板100对应的结构及尺寸。

参照图5,可以翻转第二发光部LE2而在第二欧姆层208上利用可去除的粘合剂粘结支撑基板SS。在此,可以利用激光剥离(laser lift off)方法将第二基板200从第二发光部LE2去除。在去除了第二基板200的部分可以暴露有第二n型半导体层202或者暴露有未掺杂掺杂剂的氮化镓层。

参照图6,可以利用蚀刻工序蚀刻暴露的氮化镓层并进行化学处理,从而在表面形成多个凸起。多个凸起可以形成于未掺杂掺杂剂的氮化镓层,或者形成于第二n型半导体层202。

通过在第二n型半导体层202或者未掺杂掺杂剂的氮化镓层形成多个凸起,从第一活性层104或第二活性层204发出的光在多个凸起散射,从而能够提高光提取效率。

另外,可以选择性地执行如图6所示的工序。并且,虽然未详细图示,但是在第一n型半导体层102或第二n型半导体层202也可以形成有多个凸起。

以下,对省略了图6的工序的情形进行图示及说明。

参照图7,可以在第一基板100的第一滤色器CF1上沉积第一粘结部AD1,然后再次翻转粘结于支撑基板的第二发光部LE2,使得第二发光部LE2的第二欧姆层208布置为与第一粘结部AD1粘结,之后加热以粘结第一发光部LE1及第二发光部LE2。接着,可以将支撑基板SS从第二发光部LE2去除,并且去除可去除的粘结剂RA,从而暴露第二欧姆层208。

据此,可以在第一基板100上依次层叠第一n型半导体层102、第一活性层104、第一p型半导体层106、第一欧姆层108、第一滤色器CF1、第一粘结部AD1、第二n型半导体层202、第二活性层204、第二p型半导体层206及第二欧姆层208。

参照图8,可以在暴露的第二欧姆层208上形成第二导电图案CP2。第二滤色器CF2可以选择性地被省略。

参照图9,可以在第三基板300上形成包括第三n型半导体层302、第三活性层304、第三p型半导体层306的第三发光部LE3。第三发光部LE3在平面上可以具有四边形结构,第三发光部LE3可以具有与第三基板300对应的四边形结构,第三基板300的外侧壁与第三发光部LE3的外侧壁可以是同一平面。另外,第三基板300可以具有与第一基板100及第二基板200分别对应的结构及尺寸。

参照图10,可以对第三p型半导体层306及第三活性层304进行蚀刻,进而形成暴露第三n型半导体层302的第一孔H1。第一孔H1可以形成于第四边角CN4。作为一例,第一孔H1可以具有3~3.5μm的深度。

根据一实施例,第一孔H1可以包括具有预定宽度的上部和宽度逐渐增加的下部。第一孔H1的下部可以具有尖锐的边缘部位(参照图1c)。

参照图11,可以在形成有第一孔H1的第三n型半导体层302上方正地形成第一钝化膜PV1,以不填充第一孔H1。第一钝化膜PV1可以包括选自由SiN、TiN、TiO

对位于第二边角CN2的第一钝化膜PV1局部蚀刻,从而可以形成暴露第三p型半导体层306的第二孔H2。第二孔H2的深度小于第一孔H1,可以为0.3μm。

在形成第二孔H2的期间,形成于第一孔H1底面的第一钝化膜PV1可以一同被蚀刻,从而使第三n型半导体层302暴露。

可以选择性地省略第一钝化膜PV1。但是,在省略第一钝化膜PV1的情况下,后续形成的第二导电图案CP2可以在第一孔H1内侧壁隔开形成。

参照图12,可以形成填充第一孔H1的第二导电图案CP2,并且形成填充第二孔H2的第一导电图案CP1。

第一导电图案CP1可以包括Au/Be,第二导电图案CP2可以包括Au/Ge。第一导电图案CP1可以等于或大于第二孔H2的深度。第二导电图案CP2可以等于或大于第一孔H1的深度。例如,第二导电图案CP2可以具有3~4μm的厚度。

参照图13,可以翻转形成有第一导电图案CP1、第二导电图案CP2及第三发光部LE3的第三基板300,进而可以使第一导电图案CP1及第二导电图案CP2布置为与第二滤色器CF2相向。可以利用第二粘结部AD2粘结第二发光部LE2及第三发光部LE3。

据此,在第一基板100上可以依次层叠第一n型半导体层102、第一活性层104、第一p型半导体层106、第一欧姆层108、第一滤色器CF1、第一粘结部AD1、第二n型半导体层202、第二活性层204、第二p型半导体层206、第二欧姆层208、第二滤色器CF2、第二粘结部AD2、第三p型半导体层306、第三活性层304及第三n型半导体层302。并且,第一导电图案CP1及第二导电图案CP2可以布置于第二粘结部AD2与第三发光部LE3之间。

在粘结第三发光部LE3之后,第三基板300可以通过激光剥离工序去除。

选择性地,若在图11中未形成第一钝化膜PV1,第二导电图案CP2在第一孔H1内侧壁隔开形成,则第二粘结部AD2可以填补第一孔H1与第二导电图案CP2之间的空间而形成。

参照图14,可以对布置于第一边角CN1、第二边角CN2、第四边角CN4的第三发光部LE3、第二粘结部AD2及第二滤色器CF2进行蚀刻而分别形成暴露第二欧姆层208的第三孔H3、第四孔H4、第五孔H5及第六孔H6。第三孔H3可以布置于第二边角CN2,第四孔H4布置于第一边角CN1,第五孔H5及第六孔H6可以布置于第四边角CN4。

第三孔H3、第四孔H4、第五孔H5及第六孔H6分别可以具有实质上相同的第一宽度。

在形成第三孔H3、第四孔H4、第五孔H5及第六孔H6的期间,可以对第三发光部LE3、第二粘结部AD2及第二滤色器CF2各自的边缘部位进行蚀刻,从而暴露第二欧姆层208的一部分。从平面上观察,暴露的第二欧姆层208可以具有包围第二滤色器CF2的外侧壁的结构。

根据一实施例,通过对第三发光部LE3、第二粘结部AD2及第二滤色器CF2各自的边缘部位进行蚀刻,能够缓和在第一基板100与第一发光部LE1的第一p型半导体层106之间产生的应力。

参照图15,可以在第三孔H3内部形成第一掩模图案MP1。第一掩模图案MP1可以包括针对后续的蚀刻工序中使用的蚀刻剂具有蚀刻选择比而实质上不被蚀刻的物质。例如,第一掩模图案MP1可以包括光刻胶。

参照图16,可以对布置于第四孔H4、第五孔H5及第六孔H6各自底面的第二欧姆层208、第二p型半导体层206及第二活性层204进行蚀刻,从而局部暴露第二n型半导体层202。第四孔H4、第五孔H5及第六孔H6可以分别通过蚀刻工序具有向下扩展的结构。

在将第四孔H4、第五孔H5及第六孔H6分别向下扩展的期间,可以对第二欧姆层208、第二p型半导体层206及第二活性层204各自的边缘部位进行蚀刻,从而暴露第二n型半导体层202的一部分。从平面上观察,暴露的第二n型半导体层202可以具有包围第二活性层204的外侧壁的结构。

根据一实施例,通过对第二欧姆层208、第二p型半导体层206及第二活性层204各自的边缘部位进行蚀刻,能够缓和在第一基板100与第一发光部LE1的第一p型半导体层106之间产生的应力。

接着,可以在第五孔H5内部形成第二掩模图案。第二掩模图案MP2可以包括针对后续的蚀刻工序中使用的蚀刻剂具有蚀刻选择比而实质上不被蚀刻的物质,例如光刻胶。

参照图17,可以对布置于第四孔H4及第六孔H6各自的底面的第二n型半导体层202、第一粘结部AD1及第一滤色器CF1进行蚀刻,从而暴露第一欧姆层108的一部分。通过蚀刻工序,第四孔H4和第六孔H6分别可以具有向下扩展的结构。

在使第四孔H4和第六孔H6分别向下扩展的期间内,第二n型半导体层202、第一粘合部AD1和第一滤色器CF1各自的边缘部位被蚀刻,从而可以暴露第一欧姆层108的一部分。从平面上观察,暴露的第一欧姆层108可以具有包围第一滤色器CF1的外侧壁的结构。

根据一实施例,通过对第二n型半导体层202、第一粘结部AD1及第一滤色器CF1各自的边缘部位进行蚀刻,能够缓和在第一基板100与第一发光部LE1的第一p型半导体层106之间产生的应力。

接着,可以在第四孔H4内部形成第三掩模图案MP3。第三掩模图案MP3可以包括针对后续的蚀刻工序中使用的蚀刻剂具有蚀刻选择比而实质上不被蚀刻的物质,例如光刻胶。

参照图18,可以对布置于第六孔H6底面的第一欧姆层108、第一p型半导体层106及第一活性层104进行蚀刻,从而局部地暴露第一n型半导体层102。第六孔H6可以具有通过蚀刻工序进一步向下扩展的结构。

在将第六孔H6向下扩展的期间,可以对第一欧姆层108、第一p型半导体层106及第一活性层104各自的边缘部位进行蚀刻,从而暴露第一n型半导体层102的一部分。从平面上观察,暴露的第一n型半导体层102可以具有包围第一活性层104的外侧壁的结构。

根据一实施例,通过对第一欧姆层108、第一p型半导体层106及第一活性层104的边缘部位进行蚀刻,能够缓和在第一基板100与第一发光部LE1的第一p型半导体层106之间产生的应力。

接着,可以在第六孔H6内部形成第四掩模图案MP4。第四掩模图案MP4可以包括针对后续的蚀刻工序中使用的蚀刻剂具有蚀刻选择比而实质上不被蚀刻的物质,例如光刻胶。

参照图19,可以在第三边角CN3形成第七孔H7,在第四边角CN4形成第八孔H8,使得第一导电图案CP1及第二导电图案CP2暴露。第七孔H7可以通过蚀刻第三n型半导体层302、第三活性层304及第三p型半导体层306而使第一导电图案CP1暴露。

在形成第七孔H7及第八孔H8的蚀刻工序期间,或者形成第七孔H7及第八孔H8之后,可以执行在第一基板100上蚀刻第一n型半导体层102而分离为多个发光元件的工序。在图22的工序中对发光元件进行元件分离,从而能够缓和第一基板100与第一发光部LE1(尤其,第一p型半导体层106)之间由于弯曲(bowing)现象而产生的应力。

在形成第七孔H7及第八孔H8,并将发光元件元件分离之后,可以去除第一掩模图案MP1、第二掩模图案MP2、第三掩模图案MP3及第四掩模图案MP4。

参照图20,可以在第三n型半导体层302上以不填充第三孔H3、第四孔H4、第五孔H5、第六孔H6、第七孔H7及第八孔H8的方式方正地形成第二钝化膜PV2。并且,第二钝化膜PV2可以覆盖边缘部位被蚀刻的外侧壁。

根据一实施例,在第二钝化膜PV2中,形成于第三n型半导体层302上部的第二钝化膜PV2的厚度TH1可以大于形成于第三孔H3、第四孔H4、第五孔H5、第六孔H6、第七孔H7、第八孔H8各自的底面及侧壁的第二钝化膜PV2的厚度TH2。形成于第三n型半导体层302上部的第二钝化膜PV2的厚度TH1可以比第三孔H3、第四孔H4、第五孔H5、第六孔H6、第七孔H7、第八孔H8各自的底面及侧壁的第二钝化膜PV2的厚度TH2大2~4倍。

根据一实施例,第二钝化膜PV2可以包括透光率优良且具有绝缘特性的SiO

参照图21,针对第三n型半导体层302表面沿竖直方向进行蚀刻而选择性地去除形成于第三孔H3、第四孔H4、第五孔H5、第六孔H6、第七孔H7、第八孔H8各自的底面的第二钝化膜PV2。

由于形成于第三n型半导体层302上部的第二钝化膜PV2的厚度TH1大于形成于第三孔H3、第四孔H4、第五孔H5、第六孔H6、第七孔H7、第八孔H8各自的底面及侧壁的第二钝化膜PV2的厚度TH2,因此在蚀刻形成于第三孔H3、第四孔H4、第五孔H5、第六孔H6、第七孔H7、第八孔H8各自的底面的第二钝化膜PV2的期间内,形成于第三n型半导体层302上部的第二钝化膜PV2可以残留。并且,通过竖直蚀刻第二钝化膜PV2,形成于第三孔H3、第四孔H4、第五孔H5、第六孔H6、第七孔H7、第八孔H8各自的侧壁的第二钝化膜PV2可以不被蚀刻而残留。

根据一实施例,在蚀刻工序之后,残留于第三n型半导体层302上部的第二钝化膜PV2的厚度可以大于或等于残留于第三孔H3、第四孔H4、第五孔H5、第六孔H6、第七孔H7、第八孔H8各自的第二钝化膜PV2的厚度。

由于残留于第三n型半导体层302上部的第二钝化膜PV2的厚度大于或等于分别残留于第三孔H3、第四孔H4、第五孔H5、第六孔H6、第七孔H7、第八孔H8的第二钝化膜PV2的厚度,当后述工序时,即,从第一基板100分离完成的发光元件时,第一基板弯曲,此时,布置于第三n型半导体层302表面的第二钝化膜PV2能够防止第一垫PD1(参照图26)、第二垫PD2(参照图26)、第三垫PD3(参照图26)及公共垫CPD(参照图26)从发光元件剥离。

根据一实施例,第二欧姆层208可以暴露于第三孔H3的底面,第一欧姆层108可以暴露于第四孔H4的底面,第二n型半导体层202可以暴露于第五孔H5的底面,第一n型半导体层102可以暴露于第六孔H6的底面,第一导电图案CP1可以暴露于第七孔H7的底面,并且第二导电图案CP2可以暴露于第八孔H8的底面。

参照图22,可以在形成有第三孔H3、第四孔H4、第五孔H5、第六孔H6、第七孔H7及第八孔H8的第三n型半导体层302上以不填充形成有第二钝化膜PV2的第三孔H3、第四孔H4、第五孔H5、第六孔H6、第七孔H7、第八孔H8的方式方正地形成种子膜SD。种子膜SD可以包括铜等金属。作为一例,种子膜SD可以形成为20~30nm的厚度。

并且,种子膜SD可以包围形成有第二钝化膜PV2的发光元件的外侧壁而形成。以下,将形成于发光元件的外侧壁的种子膜SD称为外侧种子膜SSD。

参照图23,可以在形成有外侧种子膜SSD的发光元件的外侧壁形成第五掩模图案MP5。第五掩模图案MP5可以包括透光率低且具有绝缘特性的光刻胶。

参照图24,可以通过种子膜SD形成填充第三孔H3、第四孔H4、第五孔H5、第六孔H6、第七孔H7、第八孔H8的布线膜ML。布线膜ML可以利用电解镀覆而形成。布线膜ML可以包括铜等金属。

在形成布线膜ML的期间,由于形成于发光元件的外侧壁的第五掩模图案MP5,在发光元件的外侧壁可以不形成布线膜ML。因此,能够防止与邻近的其他发光元件或外部电连接。

根据一实施例,虽然通过将元件在第一基板100上进行元件分离,从而缓和了第一基板100与发光元件之间的应力,但是在第一基板100上的发光元件之间可能仍残留应力。由于这样的应力,可能在发光元件产生裂痕,而第五掩模图案MP5能够起到缓和的作用。

参照图25,可以蚀刻布线膜ML及种子膜SD,从而暴露形成于第三n型半导体层302上的第二钝化膜PV2的上部面。第二钝化膜PV2可以起到布线膜ML及种子膜SD蚀刻工序的蚀刻停止膜的作用。作为布线膜ML及种子膜SD的蚀刻工序,可以使用化学机械研磨(ChemicalMechanical Polishing:CMP)工序。

据此,可以分别形成填充第三孔H3的第二过孔结构物VA2、填充第七孔H7的第三过孔结构物VA3、填充第四孔H4的第一过孔结构物VA1、填充第五孔H5的第五过孔结构物VA5、填充第八孔H8的第六过孔结构物VA6及填充第六孔H6的第四过孔结构物VA4。

第一过孔结构物VA1可以形成于第一边角CN1,第二过孔结构物VA2可以形成于第二边角CN2、第三过孔结构物VA3可以形成于第三边角CN3。第四过孔结构物VA4、第五过孔结构物VA5及第六过孔结构物VA6可以形成于第四边角CN4。

参照图26,在第二钝化膜PV2上可以分别形成与第一过孔结构物VA1电接触的第一垫PD1、与第二过孔结构物VA2电接触的第二垫PD2、与第三过孔结构物VA3电接触的第三垫PD3、与第四过孔结构物VA4、第五过孔结构物VA5及第六过孔结构物VA6共同电接触的公共垫CPD。

可以向第一垫PD1、第二垫PD2及第三垫PD3分别施加正电压,并向公共垫CPD施加负电压。

参照图27,可以将通过图3至图26形成的多个发光元件LED贴装于目标贴装基板MB上。

在贴装基板MB可以形成有分别与第一垫PD1、第二垫PD2、第三垫PD3及公共垫CPD电粘结的键合垫BPD。在键合垫上可以分别形成粘结球BL。粘结球BL分别可以包括In、Sn、AuSn、InAu等。

键合垫BPD及粘结球BL可以以与贴装发光元件的位置对应的方式形成。

可以翻转形成有多个发光元件LED的第一基板100,进而将发光元件LED以与形成有键合垫BPD的贴装基板MB相向的方式进行布置。

可以在翻转后的第一基板100上形成使欲从第一基板分离的发光元件暴露的掩模图案MSK。

参照图28,利用掩模图案MSK在第一基板100执行选择性的激光剥离(selectiveLLO)工序,从而能够将布置于贴装基板MB的目标贴装位置的发光元件LED从第一基板100分离。分离后的发光元件LED之间的间隔距离可以根据贴装基板MB而不同。

分离后的发光元件LED各自的第一垫PD1、第二垫PD2、第三垫PD3及公共垫CPD可以分别与形成于键合垫BPD的上的粘结球BL粘结。据此,发光元件LED可以贴装于贴装基板MB。

若发光元件LED全部贴装于目标位置,则无需单独执行去除第一基板100的工序而可以将第一基板100从发光元件LED分离。

以下,对制造图2a及图2b所示的发光元件的方法进行说明。

图29至图46是用于说明根据本发明的另一实施例的制造发光元件的方法的剖视图。

参照图29,可以第一基板100上形成第一n型半导体层102、第一活性层104、第一p型半导体层106及第一欧姆层108,进而形成第一发光部LE1。接着,可以在第一发光部LE1上形成第一滤色器CF1。第一滤色器CF1可以选择性地省略。

第一基板100在平面上可以具有四边形结构,并且包括第一边角CN1、第二边角CN2、第三边角CN3及第四边角CN4。

可以对第一滤色器CF1、第一欧姆层108、第一p型半导体层106及第一活性层104进行蚀刻而在第四边角CN4形成暴露第一n型半导体层102的第一孔H1。

蚀刻工序期间,可以将多个第一发光部LE1在第一基板100上进行元件分离。即,可以对第一n型半导体层102、第一活性层104、第一p型半导体层106、第一欧姆层108、第一滤色器CF1的边缘部位进行蚀刻而将邻近的第一发光部LE1之间进行元件分离。

将第一发光部LE1元件分离,从而能够缓和在第一基板100与第一发光部LE1之间由于弯曲(bowing)现象而产生的应力。

参照图30,可以以填充第一孔H1的方式在第一滤色器CF1上形成第一粘结部AD1。第一粘结部AD1可以覆盖通过元件分离暴露的基板的上部面,进而覆盖元件分离后的第一发光元件的外侧壁。

参照图31,可以在第二基板200上形成第二n型半导体层202、第二活性层204、第二p型半导体层206及第二欧姆层208,进而形成第二发光部LE2。

参照图32,可以翻转第二发光部LE2而以与第一粘结部AD1相向的方式布置第二欧姆层208。通过进行热处理,可以利用第一粘结部AD1粘结第一发光部LE1及第二发光部LE2。接着,可以利用激光剥离(laser lift off)工序将第二基板200从第二发光部LE2去除。

结果,在第一基板100上可以依次层叠第一n型半导体层102、第一活性层104、第一p型半导体层106、第一欧姆层108、第一滤色器CF1、第一粘结部AD1、第二欧姆层208、第二p型半导体层206、第二活性层204及第二n型半导体层202。

参照图33,可以对第二n型半导体层202、第二活性层204及第二p型半导体层206进行蚀刻,从而形成使第一边角CN1的第一欧姆层108暴露的第三孔H3、使第二边角CN2的第二欧姆层208暴露的第二孔H2、使第四边角CN4的第二欧姆层208暴露的第四孔H4。作为一例,第二孔H2及第三孔H3可以具有相同的宽度,但是第四孔H4可以具有大于第二孔H2或第三孔H3的宽度。

在形成第二孔H2、第三孔H3及第四孔H4的期间内,可以对第二n型半导体层202、第二活性层204及第二p型半导体层206各自的边缘部位进行蚀刻,从而暴露第二欧姆层208的边缘部位。暴露的第二欧姆层208可以具有包围第二p型半导体层206的结构。通过蚀刻第二n型半导体层202、第二活性层204及第二p型半导体层206各自的边缘部位能够缓和施加于第一基板的应力。

接着,可以在第二孔H2内部形成第一掩模图案MP1。第一掩模图案MP1可以包括针对后续的蚀刻工序中使用的蚀刻剂具有蚀刻选择比而实质上不被蚀刻的物质。例如,第一掩模图案可以包括光刻胶。

参照图34,可以对位于第三孔H3及第四孔H4底面的第二欧姆层208、第一粘结部AD1及第一滤色器CF1进行蚀刻,从而使第一欧姆层108暴露。

在通过第二掩模图案MP2填充第三孔H3内部之后,可以对位于第四孔H4底面的第一欧姆层108、第一p型半导体层106及第一活性层104进行蚀刻而使第一n型半导体层102暴露。在第四孔H4下部内侧壁可以残留有第一粘结部AD1。

通过蚀刻工序,第三孔H3及第四孔H4可以具有向下扩展的结构。在将第三孔H3及第四孔H4向下扩展的期间,可以对第二欧姆层208、第一粘结部AD1、第一滤色器CF1、第一欧姆层108、第一p型半导体层106、第一活性层104及第一n型半导体层102进行蚀刻,从而将层叠的第一发光部LE1及第二发光部LE2元件分离。

通过元件分离第一发光部LE1及第二发光部LE2,能够缓和施加于第一基板的应力。

参照图35,在去除第一掩模图案MP1及第二掩模图案MP2之后,可以在形成有第二孔H2、第三孔H3及第四孔H4的第二n型半导体层202上以不填充第二孔H2、第三孔H3及第四孔H4的方式方正地形成第一钝化膜PV1。第一钝化膜PV1可以覆盖被蚀刻的第一发光部LE1及第二发光部LE2各自的外侧壁。第一钝化膜PV1可以包括SiO

根据一实施例,在第一钝化膜PV1中,形成于第二n型半导体层202上部面的第一钝化膜PV1的厚度可以大于形成于第二孔H2、第三孔H3及第四孔H4各自的侧壁及底面的第一钝化膜PV1的厚度。形成于第二n型半导体层202上部面的第一钝化膜PV1的厚度可以比形成于第二孔H2、第三孔H3及第四孔H4各自的侧壁及底面的第一钝化膜PV1的厚度大2~4倍。

接着,可以去除形成于第二孔H2、第三孔H3及第四孔H4各自的底面的第一钝化膜PV1。可以沿相对于第二n型半导体层202的表面垂直的方向蚀刻第一钝化膜PV1。

由于形成于第二n型半导体层202上部面的第一钝化膜PV1的厚度大于形成于第二孔H2、第三孔H3及第四孔H4各自的侧壁及底面的第一钝化膜PV1的厚度,因此当沿相对于第二n型半导体层202表面垂直的方向蚀刻第一钝化膜PV1时,在形成于第二孔H2、第三孔H3及第四孔H4各自的底面的第一钝化膜PV1被去除的期间内,形成于第二n型半导体层202上部的第一钝化膜PV1可以残留。并且,由于沿竖直方向蚀刻第一钝化膜PV1,因此形成于第二孔H2、第三孔H3及第四孔H4各自的侧壁的第一钝化膜PV1可以残留而不被蚀刻。

并且,在第一发光部LE1及第二发光部LE2各自的外侧壁可以残留有第一钝化膜PV1。

根据一实施例,残留于第二n型半导体层202上部面的第一钝化膜PV1的厚度可以大于或等于残留于第二孔H2、第三孔H3及第四孔H4各自的侧壁的第一钝化膜PV1的厚度。

参照图36,在形成有第一钝化膜PV1的第二n型半导体层202上可以以不填充第二孔H2、第三孔H3及第四孔H4各自的方式方正地形成第一种子膜SD1。并且覆盖第一发光部LE1及第二发光部LE2外侧壁的第一外侧种子膜SSD1可以一同形成。

接着,还可以形成覆盖第一外侧种子膜SSD1的第三掩模图案MP3。第三掩模图案MP3可以包括透光率低且具有绝缘特性的光刻胶。

根据一实施例,在后续工序中,在去除第一基板的期间内能够通过包围发光元件外侧壁的第三掩模图案MP3防止发光元件的裂痕。

参照图37,可以以填充形成有第一种子膜SD1的第二孔H2、第三孔H3及第四孔H4的方式在第一种子膜SD1上形成第一布线膜ML1。由于第三掩模图案MP3,在第一外侧种子膜SSD1上可以不形成第一布线膜ML1。

接着,对第一布线膜ML1及第一种子膜SD1进行蚀刻,使得第一钝化膜PV1的上部面暴露。第一钝化膜PV1可以起到第一布线膜ML1及第一种子膜SD1的蚀刻工序中的蚀刻停止膜的作用。第一布线膜ML1及第一种子膜SD1的蚀刻工序可以使用化学机械研磨工序。

据此,可以分别形成填充第二孔H2的第二过孔结构物VA2的第一图案PT1_2、填充第三孔H3的第一过孔结构物VA1的第一图案PT1_1以及填充第四孔H4的第四过孔结构物VA4的第一图案PT1_4。

对于第一过孔结构物VA1的第一图案PT1_1、第二过孔结构物VA2的第一图案PT1_2及第四过孔结构物VA4的第一图案PT1_4分别可以具有第一种子膜SD1包围第一布线膜ML1的结构,并且可以包括铜。

作为一例,第一种子膜SD1的铜晶体的密度可以比第一布线膜ML1的铜晶体的密度高。

参照图38,可以在第一过孔结构物VA1的第一图案PT1_1、第二过孔结构物VA2的第一图案PT1_2及第四过孔结构物VA4的第一图案PT1_4上分别形成第一过孔结构物VA1的第二图案PT2_1、第二过孔结构物VA2的第二图案PT2_2及第四过孔结构物VA4的第二图案PT2_4。第一过孔结构物VA1的第二图案PT2_1、第二过孔结构物VA2的第二图案PT2_2及第四过孔结构物VA4的第二图案PT2_4可以分别包括Au。

在第一过孔结构物VA1中,第二图案PT2_1可以具有大于第一图案PT1_1的宽度,并且第一图案PT1_1的一面与第一欧姆层108电接触,与一面对向的另一面与第二图案PT2_1的一面电接触。第二钝化膜PV2可以包围第一图案PT1_1的外侧壁并使第二图案PT2_1与第二n型半导体层202之间绝缘。并且,形成有第一钝化膜PV1的第一图案PT1_1的至少一部分可以具有被第一粘结部AD1包围的结构。作为一例,第一粘结部AD1可以包围形成有第一钝化膜PV1的第一图案PT1_1的中间部分。

在第二过孔结构物VA2中,第二图案PT2_2可以具有大于第一图案PT1_2的宽度,并且第一图案PT1_2的一面与第二欧姆层208电接触,与一面对向的另一面与第二图案PT2_2的一面电接触。第二钝化膜PV2可以包围第一图案PT1_2的外侧壁并使第二图案PT2_2与第二n型半导体层202之间绝缘。

在第四过孔结构物VA4中,第二图案PT2_4可以具有大于第一图案PT1_4的宽度,并且第一图案的一面与第一n型半导体层102电接触,与一面对向的另一面与第二图案PT2_4的一面电接触。根据一实施例,第四过孔结构物VA4的第二图案PT2_4的一面可以包括与第一图案PT1_4相接的第一部分PT1和与第二n型半导体层202相接的第二部分PT2,第二部分PT2可以是第一部分PT1的1~5倍。另外,第一钝化膜PV1可以包围第二图案PT2_4的外侧壁,并且在第二图案PT2_4与第二n型半导体层202之间被去除,从而使第二图案PT2_4与第二n型半导体层202之间电接触。并且,由于第四过孔结构物VA4的第一图案PT1_4具有向第一粘结部AD1内部延伸的结构,第一粘结部AD1可以具有包围第四过孔结构物VA4的第一图案PT1_4的下部的外侧壁的结构。

参照图39,可以在形成有第一过孔结构物VA1的第二图案PT2_1、第二过孔结构物VA2的第二图案PT2_2及第四过孔结构物VA4的第二图案PT2_4的第一钝化膜PV1上形成第二粘结部AD2。第二粘结部AD2的上部面可以是与第一过孔结构物VA1的第二图案PT2_1、第二过孔结构物VA2的第二图案PT2_2及第四过孔结构物VA4的第二图案PT2_4各自的上部面相同的平面。

作为一例,第一过孔结构物VA1的第二图案PT2_1、第二过孔结构物VA2的第二图案PT2_2及第四过孔结构物VA4的第二图案PT2_4分别可以包括Au等金属,第二钝化膜PV2可以包括SiO

参照图40,可以在第三基板300上形成包括第三n型半导体层302、第三活性层304及第三p型半导体层306的第三发光部LE3。可以在第三p型半导体层306上形成第二滤色器CF2。

在第三边角CN3,可以对第二滤色器CF2进行蚀刻而使第三p型半导体层306暴露,并且形成第五孔H5,在第四边角CN4,可以对第二滤色器CF2、第三p型半导体层306、第三活性层304进行蚀刻而形成暴露第三n型半导体层302的第六孔H6。

接着,可以在第二滤色器CF2上形成填充第五孔H5及第六孔H6的第三粘结部AD3。第三粘结部AD3可以覆盖第二滤色器CF2上部。

参照图41,可以对第五孔H5及第六孔H6内部的第三粘结部AD3进行蚀刻,从而再次打开第五孔H5而暴露第三p型半导体层306,并且将第三n型半导体层302的一部分暴露并形成宽度小于第六孔H6的第七孔H7。在第七孔H7的内侧壁可以残留有第三粘结部AD3。

参照图42,可以分别形成填充第五孔H5的第一导电图案CP1及填充第七孔H7的第二导电图案CP2。第一导电图案CP1可以与第三p型半导体层306电接触,包括Au/Be合金并起到第三p型半导体层306的欧姆层的功能。第一导电图案CP1的外侧壁可以具有被第三粘结部AD3包裹的结构。第二导电图案CP2可以与第三n型半导体层302电接触,包括Au/Ge合金并起到第三n型半导体层302的欧姆层的功能。第二导电图案CP2的外侧壁可以通过残留于第七孔H7内的第三粘结部AD3而与第三p型半导体层306及第三活性层304相绝缘。如上所述,第三p型半导体层306及第三n型半导体层302分别将包括金属的第一导电图案CP1及第二导电图案CP2使用为欧姆层,从而能够提高第三发光部LE3的欧姆特性。

可以针对第一导电图案CP1、第二导电图案CP2及第三粘结部AD3各自的上部面执行研磨工序,从而使其成为同一平面。在这种情况下,第一导电图案CP1及第二导电图案CP2可以包括金属,第三粘结部AD3可以包括SiO

参照图43,可以翻转第三基板300,进而使得第一导电图案CP1及第二导电图案CP2与布置于第二发光部LE2上的第一过孔结构物VA1的第二图案PT2_1、第二过孔结构物VA2的第二图案PT2_2及第四过孔结构物VA4的第二图案PT2_4相向。

根据一实施例,第一过孔结构物VA1的第二图案PT2_1、第二过孔结构物VA2的第二图案PT2_2、第四过孔结构物VA4的第二图案PT2_4及第二粘结部AD2与第一导电图案CP1、第二导电图案CP2及第三粘结部AD3可以彼此相向,并且通过热处理工序相互粘结。尤其,第四过孔结构物VA4的第二图案PT2_4可以与第二导电图案CP2粘结,第二粘结部AD2与第三粘结部AD3粘结,第一过孔结构物VA1的第二图案PT2_1及第二过孔结构物VA2的第二图案PT2_2分别与第二粘结部AD2粘结。

第二粘结部AD2与第三粘结部AD3之间(即,绝缘物之间)的粘结和第四过孔结构物VA4的第二图案与第二导电图案CP2之间(即,金属之间)的粘结可以同时执行,从而能够简化工序。

接着,执行激光剥离工序而从第三发光部LE3去除第三基板300。通过去除第三基板300能够使第三n型半导体层302暴露。

参照图44,可以蚀刻第三n型半导体层302、第三活性层304、第三p型半导体层306、第二滤色器CF2及第三粘结部AD3而形成使第二过孔结构物的第二图案PT2_2暴露的第八孔H8,蚀刻第三n型半导体层302、第三活性层304、第三p型半导体层306而形成使第一导电图案CP1暴露的第九孔H9,蚀刻第三n型半导体层302、第三活性层304、第三p型半导体层306、第二滤色器CF2及第三粘结部AD3而形成使第一过孔结构物VA1的第二图案PT2_1暴露的第十孔H10,蚀刻第三n型半导体层302而形成使第二导电图案CP2暴露的第十一孔H11。

在形成第八孔H8、第九孔H9、第十孔H10及第十一孔H11的期间,可以蚀刻第三n型半导体层302、第三活性层304、第三p型半导体层306、第二滤色器CF2及第三粘结部AD3的边缘部位而使第二粘结部AD2的边缘部位暴露。暴露于边缘部位的第二粘结部AD2可以具有包围第三粘结部AD3的外侧壁的结构。

接着,可以以不填充第八孔H8、第九孔H9、第十孔H10及第十一孔H11的方式在第三n型半导体层302上方正地形成第二钝化膜PV2。根据一实施例,在第二钝化膜PV2中,形成于第三n型半导体层302上部面的第二钝化膜PV2的厚度可以大于形成于第八孔H8、第九孔H9、第十孔H10及第十一孔H11各自的侧壁及底面的第二钝化膜的厚度。作为一例,形成于第三n型半导体层302上部面的第二钝化膜PV2的厚度可以比形成于第八孔H8、第九孔H9、第十孔H10及第十一孔H11各自的侧壁及底面的第二钝化膜PV2的厚度大2~4倍。

沿垂直于第三n型半导体层302表面的方向蚀刻第二钝化膜PV2,从而去除形成于第八孔H8、第九孔H9、第十孔H10及第十一孔H11各自的底面的第二钝化膜PV2。

由于形成于第三n型半导体层302上部面的第二钝化膜PV2的厚度大于形成于第八孔H8、第九孔H9、第十孔H10及第十一孔H11各自的侧壁及底面的第二钝化膜PV2的厚度,因此在去除第八孔H8、第九孔H9、第十孔H10及第十一孔H11各自的底面的第二钝化膜PV2期间,第三n型半导体层302上部面的第二钝化膜PV2及第八孔H8、第九孔H9、第十孔H10及第十一孔H11各自的侧壁的第二钝化膜PV2可以残留。

残留于第三n型半导体层302上部面的第二钝化膜PV2的厚度大于或等于残留于第八孔H8、第九孔H9、第十孔H10及第十一孔H11各自的侧壁的第二钝化膜PV2的厚度,当进行后述工序时,即,从第一基板100分离完成的发光元件时,第一基板100弯曲,此时,形成于第三n型半导体层302表面的第二钝化膜PV2能够防止第一垫PD1(参照图2b)、第二垫PD2(参照图2b)、第三垫PD3(参照图2b)及公共垫CPD(参照图2b)从发光元件剥离。

并且,形成于使第二粘结部AD2边缘部位暴露的第三粘结部AD3、第二滤色器CF2、第二p型半导体层206、第二活性层204及第二n型半导体层202外侧壁的第二钝化膜PV2可以残留。

参照图45,可以以不填充形成有第二钝化膜PV2的第八孔H8、第九孔H9、第十孔H10及第十一孔H11各自的方式在第三n型半导体层302上方正地形成第二种子膜SD2。

并且,第二外侧种子膜SSD2可以向使第二粘结部AD2边缘部位暴露且形成有第二钝化膜PV2的第三粘结部AD3、第二滤色器CF2、第二p型半导体层206、第二活性层204及第二n型半导体层202外侧壁延伸。

接着,可以形成覆盖第二外侧种子膜SSD2的第四掩模图案MP4。第四掩模图案MP4可以包括透光率低且具有绝缘特性的光刻胶。

根据一实施例,通过包围发光元件外侧壁的第四掩模图案MP4能够防止在后续工序中可能发生的发光元件的裂痕。

参照图46,可以利用第二种子膜SD2填充第八孔H8、第九孔H9、第十孔H10及第十一孔H11中的每一个,并在第二种子膜SD2上形成第二布线膜ML2。

接着,对第二布线膜ML2及第二种子膜SD2进行蚀刻,使得第二钝化膜PV2的上部面暴露,从而分别形成填充第八孔H8的第二过孔结构物VA2的第三图案PT3_2、填充第九孔H9的第三过孔结构物VA3、填充第十孔H10的第一过孔结构物VA1的第三图案PT3_1以及填充第十一孔H11的第四过孔结构物VA4的第三图案PT3_4。

第一过孔结构物VA1的第三图案PT3_1、第二过孔结构物VA2的第三图案PT3_2、第三过孔结构物VA3及第四过孔结构物VA4的第三图案PT3_4各自的上部面可以与第二钝化膜PV2的上部面实质上相同。

另外,通过在第二外侧种子膜SSD2上布置第四掩模图案MP4,在第二外侧种子膜SSD2上可以不形成第二布线膜ML2。

根据一实施例,第二外侧种子膜SSD2及第二布线膜ML2可以包括铜。作为一例,第二外侧种子膜SSD2的铜晶体可以具有比第二布线膜ML2的铜晶体更高的密度。

再次参照图2b,在第二钝化膜PV2上可以分别形成有与第一过孔结构物VA1的第三图案PT3_1电接触的第一垫PD1、与第二过孔结构物VA2的第三图案PT3_2电接触的第二垫PD2、与第三过孔结构物VA3电接触的第三垫PD3以及与第四过孔结构物VA4的第三图案PT3_4电接触的公共垫CPD。

以上,虽然参照附图对本发明的实施例进行了说明,但是在本发明所属技术领域中具有通常知识的人员可以理解本发明能够在不改变其技术思想或必要特征的情况下实施为其他具体的形态。因此,应该理解以上所述的实施例在所有方面均为示意性而并非限定性的。

- 发光元件用组合物、发光元件用组合物的制造方法、发光元件用组合物的评价方法、发光元件和发光元件的制造方法

- 发光材料和使用其的有机发光元件、波长变换发光元件、光变换发光元件、有机激光二极管发光元件、色素激光器、显示装置以及照明装置