半导体器件及其制备方法

文献发布时间:2023-06-19 10:40:10

技术领域

本发明涉及集成电路领域,具体涉及一种半导体器件及其制备方法。

背景技术

随着集成电路的发展,器件尺寸越来越小,集成度越来越高,随着半导体器件特征尺寸的不断减小,传统的平面半导体制造技术已经无法使用,非平面技术的半导体器件应运而生,例如绝缘体上硅,双栅,多栅等新工艺的应用。为了克服器件的短沟道效应,抑制漏电流,现有技术提出了鳍式场效应晶体管(Fin FET),鳍式场效应晶体管是一种常见的多栅器件,鳍式场效应晶体管的结构包括:位于半导体衬底表面的鳍部和阻挡层,所述阻挡层覆盖部分所述鳍部的侧壁,且阻挡层表面低于鳍部顶部;位于阻挡层表面,以及鳍部的顶部和侧壁表面的栅极结构;位于所述栅极结构两侧的鳍部内的源区和漏区。

目前鳍式场效应管在小尺寸领域被广发使用,目前急需一种制造多沟道全包围栅极鳍形半导体器件的方法。

发明内容

本发明要解决的技术问题是,提供一种制造多沟道全包围栅极鳍形半导体器件的方法,有效抑制短沟道效应,有效抑制了器件的漏电及穿通等问题。

为了解决上述技术问题,本发明提供了一种半导体器件的形成方法,其特征在于,包括以下步骤:

步骤一、提供一半导体衬底,所述衬底上依次形成有第一氧化物层和第一掩膜层;

步骤二、图案化蚀刻氧化物层至基底露出,形成凹陷;

步骤三、所述凹陷内形成有复合鳍型结构,所述复合鳍型结构为交替生长的第一鳍型层和第二鳍型层;

步骤四、在衬底表面形成有垂直于所述复合鳍型结构的伪栅极结构,在伪栅极上方覆盖有第二掩膜层,在伪栅极结构两侧形成有侧墙;

步骤五、刻蚀侧墙两侧的复合鳍型结构及第一氧化物层形成凹陷;

步骤六、对伪栅极底部的复合鳍型结构以及第一氧化物层进行部分刻蚀;

步骤七、在伪栅极底部的复合鳍型结构及第一氧化物层两侧形成阻挡层;

步骤八、在伪栅极底部的复合鳍型结构两侧的凹陷内外延生长源漏极;

步骤九、在步骤八之后的器件上覆盖一层第二氧化物层及第三掩膜层并平坦化处理至伪栅极顶部露出;

步骤十、蚀刻去除伪栅极;

步骤十一、蚀刻去除复合鳍型结构两侧的第一氧化物层;

步骤十二、选择性蚀刻去除复合鳍型结构中的第一鳍型层,形成悬空于基体上方的多层沟道结构;

步骤十三、依次在沟道外周沉积一高介电常数层和金属材料层。

优选地,第一鳍型层的材料为硅或锗硅,第二鳍型层的材料相对应的为锗硅或硅。

优选地,所述步骤二中刻蚀至底部基体露出。

优选地,所述步骤七中通过原子层沉积及蚀刻工艺在伪栅极底部的复合鳍型结构及第一氧化物层两侧形成阻挡层。

优选地,所述步骤一中半导体衬底为单晶硅。

优选地,所述第一掩膜层为氮化硅,也可是氮化硅和氧化硅复合构成。

优选地,所述第一氧化物层为氧化硅。

优选地,所述伪栅极为多晶硅。

优选地,所述伪栅极侧墙为氮化硅。

本发明还公开了一种半导体器件,包括:半导体衬底和依次形成于半导体衬底上的源漏掺杂层、氧化层和掩膜层;所述源漏掺杂层、氧化层和掩膜层沿垂直于半导体衬底表面方向形成有凹陷结构;所述凹陷结构终止至半导体衬底表面;悬浮于半导体衬底上的鳍型结构,所述鳍型结构包括若干层沿垂直于半导体衬底表面方向重叠的第二鳍型层;所述第二鳍型层横跨所述凹陷结构形成沟道;在所述沟道外周还依次形成有高介电常数材料层和金属材料层;侧墙,形成于所述鳍型结构上;阻挡层,位于凹陷结构两侧,同时所述阻挡层位于所述若干层第二鳍型层之间,以及第二鳍型层与侧墙之间。

附图说明

图1为本发明步骤一后形成的器件示意图。

图2为本发明步骤二后形成的器件示意图。

图3为本发明步骤三后形成的器件示意图。

图4为本发明步骤三后形成的器件的平行于复合鳍型结构的示意图。

图5为本发明步骤四、步骤五后形成的器件示意图。

图6为本发明步骤六后形成的器件示意图。

图7为本发明步骤七后形成的器件示意图。

图8为本发明步骤八后形成的器件示意图。

图9为本发明步骤九后形成的器件示意图。

图10为本发明步骤十后形成的器件示意图。

图11为本发明步骤十后形成的器件沿着去除伪栅极结构后凹陷方向的剖面图示意图。

图12为本发明步骤十一后形成的器件示意图。

图13为本发明步骤十二后形成的器件示意图。

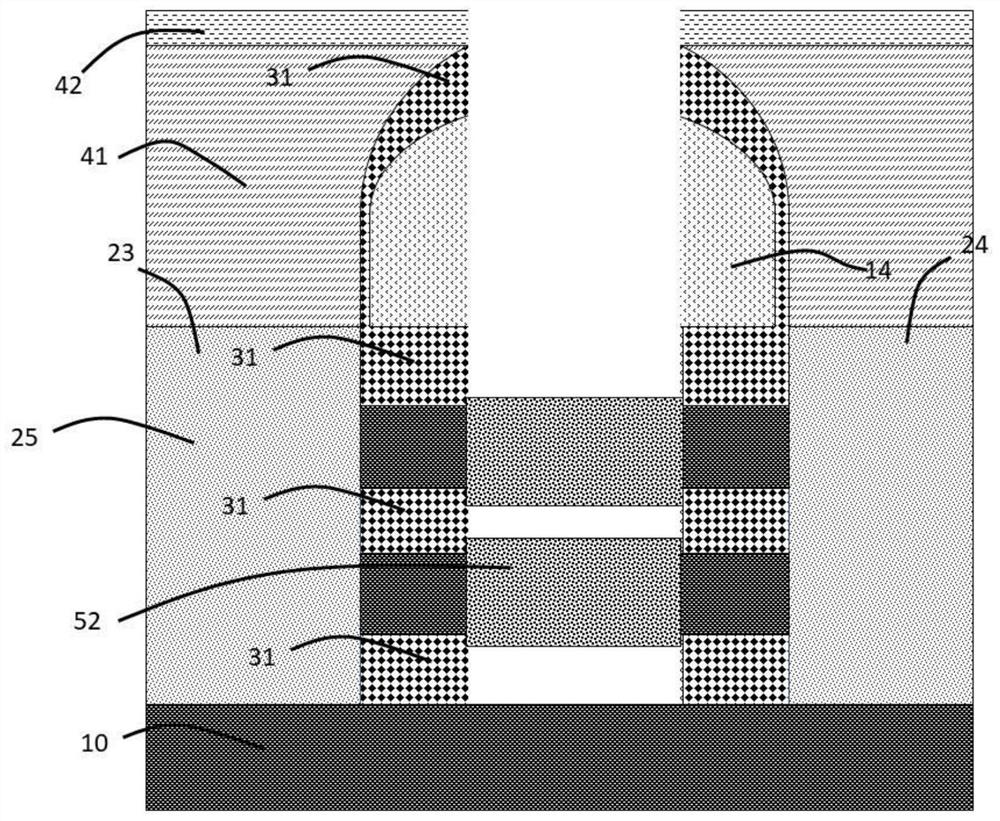

图14为本发明步骤十二后形成的器件平行于鳍型结构的示意图。

图15为本发明步骤十三后形成的器件示意图。

图16为本发明步骤十三后形成的器件平行于鳍型结构的示意图。

附图标记说明

10 半导体衬底 11 第一氧化物层

12 第一掩膜层 20 复合鳍型结构

21 第一鳍型层 22 第二鳍型层

13 伪栅极结构 14 侧墙

15 第二掩膜层 31 阻挡层

23 源极 24 漏极

25 源漏掺杂层 41 第二氧化物层

42 第三掩膜层 51 高介电常数层

52 金属材料层

具体实施方式

下面结合附图对本发明做详细说明。需要理解的是,本发明并不局限于上述特定实施方式,其中未尽详细描述的设备和结构应该理解为用本领域中的普通方式予以实施;任何熟悉本领域的技术人员,在不脱离本发明技术方案范围情况下,都可利用上述揭示的方法和技术内容对本发明技术方案作出许多可能的变动和修饰,或修改为等同变化的等效实施例,这并不影响本发明的实质内容。

半导体器件的形成方法,其特征在于,包括以下步骤:

步骤一,参阅图1所示,提供一半导体衬底10,所述半导体衬底10上依次形成有第一氧化物层11和第一掩膜层12。所述半导体衬底10可以是单晶硅,多晶硅或非晶硅;也可以是硅、锗、锗化硅、砷化镓等半导体材料;本实施例中,所述半导体衬底10的材料为单晶硅。

所述第一掩膜层12材料为氮化硅,也可是氮化硅和氧化硅复合构成。

所述第一氧化物层11材料为氧化硅。

步骤二,参阅图2,图案化蚀刻氧化物层至半导体衬底10露出,形成凹陷。较佳地,刻蚀至底部基体露出。

步骤三、参阅图3-图4,所述凹陷内形成有复合鳍型结构20,所述复合鳍型结构为交替生长的第一鳍型层21和第二鳍型层22。第一鳍型层21的材料与第二鳍型层22的材料不同。第一鳍型层21的材料为硅,第二鳍型层的材料相对应的为锗硅。此外,第一鳍型层21的材料也可以为锗硅,第二鳍型层22的材料则相对应的为硅。图4为平行于复合鳍型结构20的示意图。

步骤四,参阅图5,在衬底表面形成有垂直于所述复合鳍型结构的伪栅极结构13,在伪栅极结构上方覆盖有第二掩膜层15,在伪栅极结构两侧形成有侧墙14;较佳地,所述伪栅极结构13为多晶硅。所述伪栅极侧墙14为氮化硅。所述第二掩膜层15的材料为氮化硅,也可是氮化硅和氧化硅复合构成。

步骤五,参阅图5,刻蚀侧墙两侧的复合鳍型结构20及第一氧化物层11形成凹陷,较佳地,刻蚀至底部半导体衬底10露出。

步骤六,参阅图6,对伪栅极底部的复合鳍型结构20以及第一氧化物层11进行部分刻蚀。

步骤七,参阅图7,在伪栅极底部的复合鳍型结构20及第一氧化物层11两侧形成阻挡层31;较佳地,可以采用原子层沉积及蚀刻工艺在伪栅极底部的复合鳍型结构20及第一氧化物层11两侧形成阻挡层31。

步骤八,参阅图8,在伪栅极底部的复合鳍型结构两侧的凹陷内外延生长源极23和漏极24。

步骤九,参阅图9,在步骤八之后的器件上覆盖一层第二氧化物层41及第三掩膜层42并平坦化处理至伪栅极顶部露出;

步骤十,参阅图10-图11,蚀刻去除伪栅极结构13。图11为沿着去除伪栅极结构13后凹陷方向的剖面图。第二氧化物层41的材料为氧化硅。

步骤十一,参阅图12,蚀刻去除复合鳍型结构20两侧的第一氧化物层11。

步骤十二,参阅图13-14,选择性蚀刻去除复合鳍型结构中的第一鳍型层,形成悬空于基体上方的多层沟道结构。图14为平行于鳍型结构的示意图。

步骤十三,参阅图15-16,依次在沟道外周沉积一高介电常数层和金属材料层。图16为平行于鳍型结构的示意图。

本发明的器件性能及能有效抑制短沟道效应(short channel effect)的特殊性能,由于器件沟道被栅极包围,所以器件漏场的影响也被消除,有效抑制了器件的漏电及穿通问题。

实施例二

参见图16所示,本实施例中,使用实施例一的方法制造了下述半导体器件,包括半导体衬底10,依次形成于半导体衬底10上的源漏掺杂层25、第二氧化物层41和第三掩膜层42,悬浮于半导体衬底上的鳍型结构,侧墙14,阻挡层31。

所述源漏掺杂层25、第二氧化物层41和第三掩膜层42沿垂直于半导体衬底表面方向形成有凹陷结构;所述凹陷结构终止至半导体衬底10表面。

所述鳍型结构包括若干层沿垂直于半导体衬底表面方向重叠的第二鳍型层22;所述第二鳍型层22横跨所述凹陷结构;在所述凹陷结构内的第二鳍型层的外周还依次形成有高介电常数材料层51和金属材料层52。

所述侧墙14形成于所述鳍型结构上。

所述阻挡层31位于凹陷结构两侧,同时所述阻挡层31位于所述若干层第二鳍型层22之间,以及第二鳍型层22与侧墙14之间。

本发明的器件性能及能有效抑制短沟道效应(short channel effect)的特殊性能,由于器件沟道被栅极包围,所以器件漏场的影响也被消除,有效抑制了器件的漏电及穿通问题。

以上仅为本发明的优选实施例,并不用于限定本发明。对于本领域的技术人员来说,本发明可以有各种更改和变化。凡在本发明的精神和原则之内,所作的任何修改、等同替换、改进等,均应包含在本发明的保护范围之内。

- 半导体器件中孔、半导体器件的制备方法及半导体器件

- 半导体器件用部材、以及半导体器件用部材形成液和半导体器件用部材的制造方法、以及使用该方法制造的半导体器件用部材形成液、荧光体组合物、半导体发光器件、照明装置和图像显示装置