集成电路及动态引脚控制方法

文献发布时间:2023-06-19 10:43:23

技术领域

本发明是有关于一种引脚控制方法,尤指使用于集成电路的动态引脚控制方法。

背景技术

随着半导体制程技术的进步,由早期的微米制程进化到目前的纳米制程,集成电路的功能不断提高,以一般的微处理器为例,其接脚数已经高达数百支。由于集成电路制程技术的提高,单位面积内的电子组件数量倍数成长,但是集成电路(IC)接脚所连接的焊垫却无法随其制程技术的提升而等量缩小,这是受限于焊接技术、导线尺寸与封装技术并没有大幅提升的关系。因此,在集成电路中,接脚的面积成本可能是相当高的。由于集成电路面积成本相当昂贵,接脚数目的增加意味着成本的增加,且单位面积内的电路增加表示相同的封装内需要有更多的接脚数目,接脚数目的多寡也会直接影响芯片封装良率。

传统的集成电路经由封装后,都会有明确的引脚定义,因此封装完毕后,就不能更改集成电路内部的引脚定义。这对于系统厂商在电路板布局上会有很多的限制。若要达到可变换引脚,要先确认集成电路的输入引脚的位置与输出引脚的位置,根据引脚配置表使用多级多任务器(MUX)将输入引脚串接至对应的输出引脚,亦即除了封装后的引脚配置,还要参考引脚配置表去设定多级多任务器(MUX)才可提供另一新的引脚配置。因此,若欲使集成电路的某一输入引脚能够弹性地连接到相异的输出引脚,则需要使用较复杂的多级多任务器,使得多级多任务器需要占用更大的面积,再者,用户利用参考引脚配置表去做设定的过程也会越趋复杂。

发明内容

本发明实施例提供一种集成电路,包括多个周边输入输出引脚,多个通用型输入输出引脚,一链接网络,连接至这些周边输入输出引脚及这些通用型输入输出引脚,及一网络控制电路,耦接于该链接网络,用以根据这些周边输入输出引脚与这些通用型输入输出引脚的对应关系控制这些周边输入输出引脚经由该链接网络连接至这些通用型输入输出引脚。

本发明实施例提供一种动态引脚控制方法,使用于一集成电路,该集成电路包括多个周边输入输出引脚,多个通用型输入输出引脚,一链接网络,连接于这些周边输入输出引脚及这些通用型输入输出引脚,及一网络控制电路,耦接于该链接网络,该方法包括该网络控制电路根据这些周边输入输出引脚与这些通用型输入输出引脚的对应关系产生一控制信号,及根据该控制信号将这些周边输入输出引脚经由该链接网络连接至这些通用型输入输出引脚。

附图说明

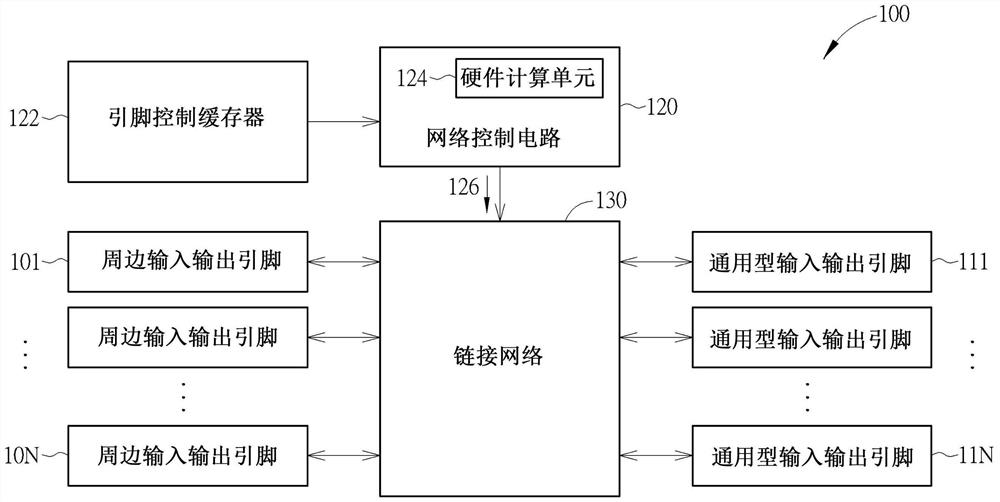

图1为实施例集成电路的示意图。

图2为实施例汴尼兹网络(Benes network)的示意图。

图3A和图3B为图1集成电路与其他多个集成电路拉线的示意图。

图4为实施例集成电路使用软件应用程序连接周边输入输出引脚以及通用型输入输出引脚的示意图。

图5为实施例的动态引脚控制方法的流程图。

图6为实施例动态引脚对应关系储存于引脚控制缓存器的示意图。

图7为实施例集成电路示意图。

图8为汴尼兹网络产生控制信号实施例的示意图。

图9为汴尼兹网络使用完整残余分树控制算法实施例的示意图。

图10为汴尼兹网络第一区块使用完整残余分树控制控制算法实施例的流程图。

图11A以及图11B为开关控制方式的示意图。

图12为汴尼兹网络第一区块使用完整残余分树控制算法实施例的示意图。

图13为汴尼兹网络第二区块使用位控制算法实施例的流程图。

图14为汴尼兹网络使用位控制算法实施例的示意图。

具体实施方式

图1为实施例集成电路100的示意图。集成电路100包括周边输入输出引脚101-10N、通用型输入输出引脚111-11N、引脚控制缓存器122、链接网络130及网络控制电路120。链接网络130连接周边输入输出引脚101-10N以及通用型输入输出引脚111-11N。网络控制电路120耦接于链接网络130,且根据周边输入输出引脚101-10N以及通用型输入输出引脚111-11N的对应关系控制周边输入输出引脚101-10N经由链接网络130连接至通用型输入输出引脚111-11N。

引脚控制缓存器122储存周边输入输出引脚101-10N与通用型输入输出引脚111-11N的对应关系。当要动态调整引脚对应关系,如将周边输入输出引脚101连接至通用型输入输出引脚118,周边输入输出引脚102连接至通用型输入输出引脚116,则将引脚对应关系更新至引脚控制缓存器122。引脚控制缓存器122传送引脚对应关系至网络控制电路120的硬件计算单元124以产生控制信号126。链接网络130再依据控制信号126来做开关控制以完成引脚连接。在本发明的一个实施例中,引脚控制缓存器122亦可独立在集成电路100外,而系耦接于集成电路100的网络控制电路120。

在本发明的一个实施例中,周边输入输出引脚101-10N可为集成电路的功能引脚。集成电路的功能引脚包含读取控制(RD)引脚、中断要求(INT)引脚、写入控制(WR)引脚、内存访问控制引脚、系统重置(RESET)引脚等,但不限于此。硬件计算单元124计算出控制信号126后,网络控制电路120便可依不同的需要改变集成电路100的功能引脚和通用型输入输出引脚111-11N的连接。

图2为实施例汴尼兹网络(Benes network)的示意图。在本发明的一个实施例中,链接网络130可为汴尼兹网络(Benes network)。在汴尼兹网络(Benes network)中,由于每个输入端点到输出端点之间通过的门(gate)数量是相同的,因此不会有选择不同路径而造成不同门延迟(gate delay)的问题。如图2所示,由左侧000连接至右侧000的门数量为5。同样地,由左侧100连接至右侧100的门(gate)数量也为5。使用传统多任务器多级串接(MUX)或纵横式交换开关(crossbar switch)的方式,随着想要连接引脚的位置越多,MUX串接起来的复杂度与面积都会变大,导致经过的门数量增加,且使用者查表去做设定的过程也会越复杂。此外,因MUX串接方式不同,在某些情形下,不同输入端点到输出端点通过的门数量会有很大差异,例如一个输入到输出通过的门数量为1,但另一个输入到输出通过的门数量可能为19。因此在应用上,汴尼兹网络(Benes network)不会有一般使用多任务器多级串接(MUX)与纵横式交换开关,由于通过的门数量不同而造成各个路径的不同延迟问题。

在本发明的一个实施例中,可以改善电路板因集成电路摆放位置造成的拉线问题。图3A和图3B为集成电路100与其他多个集成电路204、206、208拉线的示意图,如图3A所示,集成电路100摆放位置已经固定,在先前技术中,由于集成电路100的输出引脚是固定不可变的,以致于集成电路206以及集成电路204并不容易与集成电路100拉线。然而通过本发明实施例的网络控制电路120,即可以改变集成电路100输出引脚的位置,如图3B所示,将可以使集成电路206以及集成电路204的拉线容易,也可以减少因不良布线所造成的电流或电磁干扰。

图4为集成电路100使用软件应用程序402控制周边输入输出引脚101-10N以及通用型输入输出引脚111-11N的连接的示意图。集成电路100包括周边输入输出引脚101-10N、通用型输入输出引脚111-11N、链接网络130及网络控制电路120。网络控制电路120可包含软件应用程序402,网络控制电路120可耦接于链接网络130。链接网络130亦可使用汴尼兹网络(Benes network)连接周边输入输出引脚101-10N以及数个通用型输入输出引脚111-11N。当需要动态调整周边输入输出引脚101-10N以及通用型输入输出引脚111-11N的对应关系,则将引脚对应关系更新至软件应用程序402。当软件应用程序402产生控制信号406,控制信号406会使网络控制电路120控制链接网络130。链接网络130再依据控制信号406来做开关控制以连接周边输入输出引脚101-10N以及数个通用型输入输出引脚111-11N。在本发明的一个实施例中,软件应用程序402亦可独立在集成电路100外,而将控制信号406由外部输入网络控制电路120。

图5为实施例的动态引脚控制方法的流程图。

步骤S502:将集成电路的周边输入输出引脚101-10N与通用型输入输出引脚111-11N的引脚对应关系储存至引脚控制缓存器122;

步骤S504:网络控制电路120根据周边输入输出引脚101-10N与通用型输入输出引脚111-11N的引脚对应关系产生控制信号126、406;

步骤S506:网络控制电路120传送控制信号126、406用以控制链接网络130,依据控制信号126、406将周边输入输出引脚101-10N经由链接网络130连接通用型输入输出引脚111-11N。

在步骤S502中,周边输入输出引脚101-10N与通用型输入输出引脚111-11N的对应关系储存至引脚控制缓存器122,若因需求要动态调整引脚,仅需更改引脚控制缓存器122。如图6所示,想要把I2C的位置从GPIOA[2]与GPIOA[3]修改到GPIOA[14]与GPIOA[15],直接修改引脚控制缓存器122内容即可,也不需要查表。动态调整引脚修改设定后,若要得知目前引脚分配,也是直接读出此引脚控制缓存器122内容即可。根据引脚控制缓存器122的引脚对应关系,网络控制电路120的硬件计算单元124会产生控制信号126来控制汴尼兹网络(Benes network)的连接。传统使用多任务器多级串接(MUX)或纵横式交换开关(crossbarswitch)的方式,随着想要连接引脚的位置越多,多任务器多级串接起来的复杂度与面积都会变大,使用者查表去做设定的过程也会越复杂。本发明实施例提供一简易的方式提供动态引脚设定。

在步骤S504中,网络控制电路120根据周边输入输出引脚101-10N与通用型输入输出引脚111-11N的对应关系,使用完整残余分树控制(complete residue partition treecontrol)及位控制(bit control)产生控制信号126。根据实施例的不同,可以由硬件计算单元124产生控制信号126或软件应用程序402产生控制信号406。链接网络130是使用汴尼兹网络(Benes network)。控制信号126、406主要是用来控制汴尼兹网络(Benes network)中的每一个门(gate)开关控制,以达成周边输入输出引脚101-10N以及数个通用型输入输出引脚111-11N的连接控制。

图7为实施例集成电路示意图。图7右边的通用型输入输出引脚721-728数量,相对于左边的周边输入输出引脚701-716数量,引脚数量是较少的,若使用传统的集成电路封装方式,则无法使用全部的周边输入输出引脚701-716,而必须有所取舍。使用本实施例的动态引脚控制方法,通用型输入输出引脚721-728可依需求,通过网络控制电路130控制与周边输入输出引脚701-716的耦接,所以可以有效使用全部的周边输入输出引脚701-716。且链接网络可使用汴尼兹网络(Benes network),通过的门(gate)数量相同,而不会有引脚延迟时间相异的问题。

图8为汴尼兹网络(Benes network)产生控制信号实施例的示意图。将具有N个输入的汴尼兹网络分两个区块。第一区块801是使用完整残余分树控制(Complete ResiduePartition Tree Control,CRPT Control)算法,第一区块801的阶段数量为K,K=log

图10为汴尼兹网络(Benes network)第一区块801使用完整残余分树(CRPTControl)控制算法实施例的流程图。其中,第一区块801含有K个阶段,K=(log

步骤S1001:将输入的数列转换为两层数列,数列中的奇数组成为上位序列(Uppersequence),数列中的偶数组成为下位序列(Lower sequence);

步骤S1002:将上位序列(Upper sequence)执行除2

步骤S1003:依先标记第一矩阵Up2K再标记第二矩阵Low2K的顺序,将0到(N/2-1)的数字标记在第一矩阵Up2K以及第二矩阵Low2K中,若标记过程发生搜寻冲突,即数字应标记在第一矩阵Up2K的第i项,但第二矩阵Low2K的第i项已被标记,或数字应标记在第二矩阵Low2K的第i项,但第一矩阵Up2K的第i项已被标记,则执行步骤S1004,否则持续执行步骤S1003,直到完成标记数字=(N/2-1)的位置,则跳至步骤S1005;

步骤S1004:将应标记数字标记在第一矩阵Up2K或第二矩阵Low2K的第i项,清除另一矩阵的第i项,并将另一矩阵的第i项的值储存为冲突数字,再依第一矩阵Up2K至第二矩阵Low2K的顺序重新找出并标记冲突数字不为原先位置的新位置,若再发生搜寻冲突则回到步骤S1004,否则执行步骤S1003;

步骤S1005:将标记第一矩阵Up2K以及第二矩阵Low2K的结果转换为开关的控制,若被标记的数字在第一矩阵Up2K的第i项,则第i开关控制即是0,若被标记的数字在第二矩阵Low2K的第i项,则第i开关控制即是1。

在第1阶段,当K=1时,依照步骤S1001-S1005,可得到第1阶段的开关控制结果。在第2阶段,当K=2时,依照步骤S1001-S1005,可得到第2阶段的开关控制结果。依序将K从1至(log

如图12所示,实施例具有16个输入,即N=16,16个输入的数列为[0,1,2,3,4,6,5,8,7,10,12,11,14,13,15,9],代表将周边输入输出引脚0欲耦接至通用型输入输出引脚0,周边输入输出引脚1欲耦接至通用型输入输出引脚1,周边输入输出引脚2欲耦接至通用型输入输出引脚2,周边输入输出引脚3欲耦接至通用型输入输出引脚3,周边输入输出引脚4欲耦接至通用型输入输出引脚4,周边输入输出引脚5欲耦接至通用型输入输出引脚6,周边输入输出引脚6欲耦接至通用型输入输出引脚5,周边输入输出引脚7欲耦接至通用型输入输出引脚8,周边输入输出引脚8欲耦接至通用型输入输出引脚7,周边输入输出引脚9欲耦接至通用型输入输出引脚10,周边输入输出引脚10欲耦接至通用型输入输出引脚12,周边输入输出引脚11欲耦接至通用型输入输出引脚11,周边输入输出引脚12欲耦接至通用型输入输出引脚14,周边输入输出引脚13欲耦接至通用型输入输出引脚13,周边输入输出引脚14欲耦接至通用型输入输出引脚15,周边输入输出引脚15欲耦接至通用型输入输出引脚9。在第1阶段,当K=1时,执行步骤S1001,获取数列中的奇数组以得到上位序列:[0,2,4,5,7,12,14,15],及获取数列中的偶数组以得到下位序列:[1,3,6,8,10,11,13,9]。执行步骤S1002,进行除2

表1

接下来执行步骤S1003,将0做标记,如表2所示,0位在第一矩阵Up2K的第0个位置及第二矩阵Low2K的第0个位置,但第一矩阵Up2K比第二矩阵Low2K具有较高的优先次序,因此将0标记在第一矩阵Up2K的第0个位置:

表2

接着标记1,如表3所示,1位在第一矩阵Up2K的第1个位置及第二矩阵Low2K的第1个位置,但第一矩阵Up2K比第二矩阵Low2K具有较高的优先次序,因此将1标记在第一矩阵Up2K的第1个位置:

表3

接着标记2,如表4所示,2位在第一矩阵Up2K的第2个位置及第一矩阵Up2K的第3个位置,但第一矩阵Up2K的第2个位置在第一矩阵Up2K的第3个位置前面,因此将2标记在第一矩阵Up2K的第2个位置:

表4

接着标记3,如表5所示,3位在第一矩阵Up2K的第4个位置及第二矩阵Low2K的第2个位置,但第一矩阵Up2K比第二矩阵Low2K具有较高的优先次序,因此将3标记在第一矩阵Up2K的第4个位置:

表5

接着标记4,如表5所示,4位在第二矩阵Low2K的第3个位置及第二矩阵Low2K的第7个位置,但第二矩阵Low2K的第3个位置在第二矩阵Low2K的第7个位置前面,因此将4标记在第二矩阵Low2K的第3个位置:

表5

接着标记5,如表6所示,5位在第二矩阵Low2K的第4个位置及第二矩阵Low2K的第5个位置,但第二矩阵Low2K的第4个位置在第二矩阵Low2K的第5个位置前面,因此将5标记在第二矩阵Low2K的第4个位置,但此时因为第一矩阵Up2K第4个位置已被标记,发生搜寻冲突,得执行步骤S1004:

表6

接下来执行步骤S1004,保留标记5在第二矩阵Low2K的第4个位置,清除第一矩阵Up2K的第4个位置,并储存冲突数字=3,重新由第一矩阵Up2K至第二矩阵Low2K的顺序找出冲突数字=3的新位置,即第二矩阵Low2K的第2个位置,如表7所示,执行标记动作,但此时因为第一矩阵Up2K的第2个位置已被标记,发生搜寻冲突,得执行步骤S1004:

表7

接下来执行步骤S1004,保留标记3在第二矩阵Low2K的第2个位置,清除第一矩阵Up2K的第2个位置,并储存冲突数字=2,重新由第一矩阵Up2K至第二矩阵Low2K的顺序找出冲突数字=2的新位置,即第一矩阵Up2K的第3个位置,如表8所示,执行标记动作,但此时因为第二矩阵Low2K第3个位置已被标记,发生搜寻冲突,得执行步骤S1004:

表8

接下来执行步骤S1004,保留标记2在第一矩阵Up2K的第3个位置,清除第二矩阵Low2K的第3个位置,并储存冲突数字=4,重新由第一矩阵Up2K至第二矩阵Low2K的顺序找出冲突数字=4的新位置,即第二矩阵Low2K的第7个位置,如表9所示,执行标记动作:

表9

接下来执行步骤S1003,接着标记6,如表10所示,6位在第一矩阵Up2K的第5个位置及第二矩阵Low2K的第6个位置,但第一矩阵Up2K比第二矩阵Low2K具有较高的优先次序,因此将6标记在第一矩阵Up2K的第5个位置:

表10

接着标记7,如表11所示,7位在第一矩阵Up2K的第6个位置及第一矩阵Up2K的第7个位置,但第一矩阵Up2K的第6个位置在第一矩阵Up2K的第7个位置前面,因此将7标记在第一矩阵Up2K的第6个位置,此时完成标记数字7的位置,即完成所有标记(N/2-1),便可执行步骤S1005:

表11

接下来执行步骤S1005,若被标记的数字在第一矩阵Up2K的第i项,则第i开关控制即是0,若被标记的数字在第二矩阵Low2K的第i项,则第i开关控制即是1,如表12所示,可得到开关控制结果为[0,0,1,0,1,0,0,1]。

表12

如图12所示,当经过第1阶段,依步骤S1001-S1005,可得到第1个阶段的开关控制结果为[0,0,1,0,1,0,0,1],由于开关控制是0时代表平行输出,开关控制是1时代表交叉输出,因此原数列经由第1个阶段的开关会被分为新的两数列[0,2,6,5,10,12,14,9]及[1,3,4,8,7,11,13,15]。在第2阶段,对此两数列进行取商运算,此时N=8,K=2。先计算第一数列[0,2,6,5,10,12,14,9],执行步骤S1001,获取数列中的奇数组以得到上位序列:[0,6,10,14],及获取数列中的偶数组以得到下位序列:[2,5,12,9]。执行步骤S1002,进行除2

表13

接下来执行步骤S1003,将0做标记,如表14所示,0位在第一矩阵Up2K的第0个位置及第二矩阵Low2K的第0个位置,但第一矩阵Up2K比第二矩阵Low2K具有较高的优先次序,因此将0标记在第一矩阵Up2K的第0个位置:

表14

接着标记1,如表3所示,1位在第一矩阵Up2K的第1个位置及第二矩阵Low2K的第1个位置,但第一矩阵Up2K比第二矩阵Low2K具有较高的优先次序,因此将1标记在第一矩阵Up2K的第1个位置:

表15

接着标记2,如表16所示,2位在第一矩阵Up2K的第2个位置及第二矩阵Low2K的第3个位置,但第一矩阵Up2K比第二矩阵Low2K具有较高的优先次序,因此将2标记在第一矩阵Up2K的第2个位置:

表16

接着标记3,如表17所示,3位在第一矩阵Up2K的第3个位置及第二矩阵Low2K的第2个位置,但第一矩阵Up2K比第二矩阵Low2K具有较高的优先次序,因此将3标记在第一矩阵Up2K的第3个位置,此时完成标记数字3的位置,完成所有标记(N/2-1),即可执行步骤S1005:

表17

接下来执行步骤S1005,若被标记的数字在第一矩阵Up2K的第i项,则第i开关控制即是0,若被标记的数字在第二矩阵Low2K的第i项,则第i开关控制即是1,如表18所示,可得到开关控制结果为[0,0,0,0]。

表18

接下来计算第2阶段的第二数列[1,3,4,8,7,11,13,15],执行步骤S1001,获取数列中的奇数组以得到上位序列:[1,4,7,13],及获取数列中的偶数组以得到下位序列:[3,8,11,15]。执行步骤S1002,进行除2

表19

接下来执行步骤S1003,将0做标记,如表20所示,0位在第一矩阵Up2K的第0个位置及第二矩阵Low2K的第0个位置,但第一矩阵Up2K比第二矩阵Low2K具有较高的优先次序,因此将0标记在第一矩阵Up2K的第0个位置:

表20

接着标记1,如表21所示,1位在第一矩阵Up2K的第1个位置及第一矩阵Up2K的第2个位置,但第一矩阵Up2K的第1个位置在第一矩阵Up2K的第2个位置前面,因此将1标记在第一矩阵Up2K的第1个位置:

表21

接着标记2,如表22所示,2位在第二矩阵Low2K的第1个位置及第二矩阵Low2K的第2个位置,但第二矩阵Low2K的第1位置在第二矩阵Low2K的第2个位置前面,因此将2标记在第二矩阵Low2K的第1个位置,但此时因为第一矩阵Up2K第1个位置已被标记,发生搜寻冲突,得执行步骤S1004:

表22

接下来执行步骤S1004,保留标记2在第二矩阵Low2K的第1个位置,清除第一矩阵Up2K的第1个位置,并储存冲突数字=1,重新由第一矩阵Up2K至第二矩阵Low2K的顺序找出冲突数字=1的新位置,即第一矩阵Up2K的第2个位置,如表23所示,执行标记动作:

表23

接下来执行步骤S1003,接着标记3,如表24所示,3位在第一矩阵Up2K的第3个位置及第二矩阵Low2K的第3个位置,但第一矩阵Up2K比第二矩阵Low2K具有较高的优先次序,因此将3标记在第一矩阵Up2K的第3个位置,此时完成标记数字3的位置,完成所有标记(N/2-1),即可执行步骤S1005:

表24

接下来执行步骤S1005,若被标记的数字在第一矩阵Up2K的第i项,则第i开关控制即是0,若被标记的数字在第二矩阵Low2K的第i项,则第i开关控制即是1,如表25所示,可得到开关控制结果为[0,1,0,0]。

表25

在第2阶段,经由计算第一数列[0,2,6,5,10,12,14,9]得到开关控制结果如表18,经由计算第二数列[1,3,4,8,7,11,13,15]得到开关控制结果如表25,可以得到K=2阶段的所有开关控制结果[0,0,0,0,0,1,0,0],如图12所示。

如图12所示,经过第2阶段,原数列经过第1个阶段以及第2个阶段开关,被分为新的四个数列[0,6,10,14]、[2,5,12,9]、[1,8,7,13]、[3,4,11,15]。在第3阶段,对此四数列进行取商运算,此时N=4,K=3,计算此四个数列。先计算第一数列[0,6,10,14],执行步骤S1001,获取数列中的奇数组以得到上位序列:[0,10],及获取数列中的偶数组以得到下位序列:[6,14]。执行步骤S1002,进行除2

表26

接下来执行步骤S1003,将0做标记,如表27所示,0位在第一矩阵Up2K的第0个位置及第二矩阵Low2K的第0个位置,但第一矩阵Up2K比第二矩阵Low2K具有较高的优先次序,因此将0标记在第一矩阵Up2K的第0个位置:

表27

接着标记1,如表28所示,1位在第一矩阵Up2K的第1个位置及第二矩阵Low2K的第1个位置,但第一矩阵Up2K比第二矩阵Low2K具有较高的优先次序,因此将1标记在第一矩阵Up2K的第1个位置,此时完成标记数字1的位置,完成所有标记(N/2-1),即可执行步骤S1005:

表27

接下来执行步骤S1005,若被标记的数字在第一矩阵Up2K的第i项,则第i开关控制即是0,若被标记的数字在第二矩阵Low2K的第i项,则第i开关控制即是1,如表28所示,可得到开关控制结果为[0,0]。

表28

接下来计算第二数列[2,5,12,9],执行步骤S1001,获取数列中的奇数组以得到上位序列:[2,12],及获取数列中的偶数组以得到下位序列:[5,9]。执行步骤S1002,进行除2

表29

接下来执行步骤S1003,将0做标记,如表30所示,0位在第一矩阵Up2K的第0个位置及第二矩阵Low2K的第0个位置,但第一矩阵Up2K比第二矩阵Low2K具有较高的优先次序,因此将0标记在第一矩阵Up2K的第0个位置:

表30

接着标记1,如表31所示,1位在第一矩阵Up2K的第1个位置及第二矩阵Low2K的第1个位置,但第一矩阵Up2K比第二矩阵Low2K具有较高的优先次序,因此将1标记在第一矩阵Up2K的第1个位置,此时完成标记数字1的位置,完成所有标记(N/2-1),即可执行步骤S1005:

表31

接下来执行步骤S1005,若被标记的数字在第一矩阵Up2K的第i项,则第i开关控制即是0,若被标记的数字在第二矩阵Low2K的第i项,则第i开关控制即是1,如表32所示,可得到开关控制结果为[0,0]。

表32

接下来计算第三数列[1,8,7,13],执行步骤S1001,获取数列中的奇数组以得到上位序列:[1,7],及获取数列中的偶数组以得到下位序列:[8,13]。执行步骤S1002,进行除2

表33

接下来执行步骤S1003,将0做标记,如表34所示,0位在第一矩阵Up2K的第0个位置及第二矩阵Low2K的第0个位置,但第一矩阵Up2K比第二矩阵Low2K具有较高的优先次序,因此将0标记在第一矩阵Up2K的第0个位置:

表34

接着标记1,如表35所示,1位在第二矩阵Low2K的第0个位置及第二矩阵Low2K的第1个位置,但第二矩阵Low2K的第0位置在第二矩阵Low2K的第1个位置前面,因此将1标记在第一矩阵Low2K的第0个位置,但此时因为第一矩阵Up2K第0个位置已被标记,发生搜寻冲突,得执行步骤S1004:

表35

接下来执行步骤S1004,保留标记1在第二矩阵Low2K的第0个位置,清除第一矩阵Up2K第0个位置,并储存冲突数字=0,重新由第一矩阵Up2K至第二矩阵Low2K的顺序找出冲突数字=0的新位置,即第一矩阵Up2K的第1个位置,如表36所示,此时完成标记数字0的位置,完成所有标记(N/2-1),即可执行步骤S1005:

表36

接下来执行步骤S1005,若被标记的数字在第一矩阵Up2K的第i项,则第i开关控制即是0,若被标记的数字在第二矩阵Low2K的第i项,则第i开关控制即是1,如表37所示,可得到开关控制结果为[1,0]。

表37

接下来计算第四数列[3,4,11,15],执行步骤S1001,获取数列中的奇数组以得到上位序列:[3,11],及获取数列中的偶数组以得到下位序列:[4,15]。执行步骤S1002,进行除2

表38

接下来执行步骤S1003,将0做标记,如表39所示,0位在第一矩阵Up2K的第0个位置及第二矩阵Low2K的第0个位置,但第一矩阵Up2K比第二矩阵Low2K具有较高的优先次序,因此将0标记在第一矩阵Up2K的第0个位置:

表39

接着标记1,如表40所示,1位在第一矩阵Up2K的第1个位置及第二矩阵Low2K的第1个位置,但第一矩阵Up2K比第二矩阵Low2K具有较高的优先次序,因此将1标记在第一矩阵Up2K的第1个位置,此时完成标记数字1的位置,完成所有标记(N/2-1),即可执行步骤S1005:

表40

接下来执行步骤S1005,若被标记的数字在第一矩阵Up2K的第i项,则第i开关控制即是0,若被标记的数字在第二矩阵Low2K的第i项,则第i开关控制即是1,如表41所示,可得到开关控制结果为[0,0]。

表41

在第3阶段,经由计算四个数列[0,6,10,14]、[2,5,12,9]、[1,8,7,13]、[3,4,11,15]得到开关控制结果如表28、表32、表37及表41,结合此四组开关控制结果,即可得到如图12中所示之第3阶段的所有开关控制结果[0,0,0,0,1,0,0,0],其即为第一区块801使用CRPT控制算法的开关控制结果。

图13为汴尼兹网络(Benes network)第二区块802使用位控制算法实施例的流程图。其中,第二区块802含有P个阶段,P=log

步骤S1301:将输入的数列转为两层数列,数列中的奇数组成为上位序列(Uppersequence);

步骤S1302:将上位序列(Upper sequence)转为二进制存入第一矩阵UpBin;

步骤S1303:将UpBin内的值与2^(log

在第二区块802的第1个阶段,P=1,依照所述步骤S1301-S1303,可得到第1个阶段的开关控制结果。依序将P从1至log

如图14所示,延续图12的实施例数列,第二区块802中每一个阶段使用位控制算法进行运算。实施例的汴尼兹网络(Benes network)之第二区块802的输入数列为[0,10,6,14,2,12,5,9,8,7,1,13,3,11,4,15]。在第1个阶段,P=1,N=16,依照所述步骤S1301,将输入的数列转为两层数列,数列中的奇数组成为上位序列:[0,6,2,5,8,1,3,4]。执行步骤S1302,将上位序列(Upper sequence)转为二进制存入第一矩阵UpBin,如表42的第二列所示。接着执行步骤S1303,UpBin内的值与2^(log

表42

第二区块802的输入数列经由第1个阶段开关,得到数列[0,6,10,14,2,5,12,9,7,1,8,13,3,4,11,15]为第2个阶段的输入。在第2个阶段,P=2,N=16,依照所述步骤S1301,将输入的数列转为两层数列,数列中的奇数组成为上位序列:[0,10,2,12,7,8,3,11]。执行步骤S1302,将上位序列(Upper sequence)转为二进制存入第一矩阵UpBin,如表43的第二列所示。接着执行步骤S1303,UpBin内的值与2^(log

表43

第二区块802的输入数列经由第1个阶段开关以及第2个阶段开关,得到数列[0,2,6,5,10,9,14,12,1,3,7,4,8,11,13,15]为第3个阶段的输入。在第3个阶段,P=3,N=16,依照所述步骤S1301,将输入的数列转为两层数列,数列中的奇数组成为上位序列:[0,6,10,14,1,7,8,13]。执行步骤S1302,将上位序列(Upper sequence)转为二进制存入第一矩阵UpBin,如表44的第二列所示。接着执行步骤S1303,UpBin内的值与2^(log

表44

第二区块802的输入数列经由第1个阶段开关,第2个阶段开关以及第3个阶段开关,得到数列[0,1,2,3,5,4,6,7,9,8,10,11,12,13,14,15]为第4个阶段的输入。在第4个阶段,P=4,N=16,依照所述步骤S1301,将输入的数列转为两层数列,数列中的奇数组成为上位序列:[0,2,5,6,9,10,12,14]。执行步骤S1302,将上位序列(Upper sequence)转为二进制存入第一矩阵UpBin,如表45的第二列所示。接着执行步骤S1303,UpBin内的值与2^(log

表45

由表42、表43、表44、表45可得到4个阶段的开关控制结果。如图14所示,第二区块802中的开关控制结果。因此,结合完整残余分树控制(CRTC Control)算法以及位控制(bitcontrol)算法可得汴尼兹网络(Benes network)的所有开关控制结果。

本实施例使用完整残余分树控制(CRPT Control)算法以及位控制(bit control)算法,可以快速运算出汴尼兹网络(Benes network)中的每一个门(gate)开关控制,以达成动态调整周边输入输出引脚101-10N以及数个通用型输入输出引脚111-11N的连接控制。使用本发明实施例,甚至可以达成在不同时间提供变换不同引脚连接的功能。

本实施例提供一种集成电路以及动态引脚控制方法。网络控制电路耦接于链接网络,用以动态控制周边输入输出引脚经由链接网络连接至通用型输入输出引脚。周边输入输出引脚可以是集成电路的功能引脚。链接网络可采用汴尼兹网络(Benes network),以达到每个周边输入输出引脚到通用型输入输出引脚之间通过的门(gate)数量是相同的,因而不会有选择不同路径而造成有不同门延迟(gate delay)的问题。本实施例将引脚对应关系储存至引脚控制缓存器,修改设定后,若要参考目前引脚,可直接读出此引脚控制缓存器设定即可。本实施例可动态设定或调整引脚连接,因而可以解决电路板上部分集成电路(IC)因固定在某些位置造成与主要控制集成电路(control IC)之间不易拉线的问题,使拉线更容易也减少因布线所造成的电流干扰问题。当制作不同引脚数量与封装的集成电路(IC),如周边输入输出引脚远多于通用型输入输出引脚,使用本实施例的动态引脚控制方法,将可以有效使用全部的周边输入输出引脚。

以上所述仅为本发明之优选实施例,凡依本发明权利要求范围所做之均等变化与修饰,皆应属本发明之涵盖范围。

【符号说明】

100、202、204、206 集成电路

101至10N、701至716 周边输入输出引脚

111至11N、721至728 通用型输入输出引脚

120 网络控制电路

122 引脚控制缓存器

124 硬件计算单元

126 控制信号

130 链接网络

402 软件应用程序

406 控制信号

S502至S506、S1001至S1005、S1301至S1303 步骤

801 第一区块

802 第二区块。

- 集成电路及动态引脚控制方法

- 带复用引脚的集成电路及引脚复用方法