数据传输方法、处理器、芯片及电子设备

文献发布时间:2023-06-19 11:02:01

技术领域

本公开涉及信息处理技术领域,尤其涉及一种数据传输方法、处理器、芯片及电子设备。

背景技术

深度神经网络(DNNs)为有很多隐藏层的神经网络,一个芯片的计算资源不可以满足大规模的深度神经网络的需求,如果将大规模的网络切分映射在单个计算核上计算的时间将非常大。在有限的众核簇情况下,每个计算核的内存资源有限,需要对神经网络的输入图像数据进行切分,将一个大规模的DNNs切分映射到芯片群上。整个切分过程中,计算核簇内、簇间存在的大量数据交换,如交叠数据,如部分和数据,如图形整合等等。

发明内容

有鉴于此,本公开提出了一种数据传输方法、处理器、芯片及电子设备。

根据本公开的一方面,提供了一种数据传输方法,所述方法用于处理器的计算核之间的数据传输,每个处理器包括多个计算核,每个处理器内部的计算核之间、以及不同处理器的计算核之间能够进行数据传输;其中,每个计算核包括存储部件,所述存储部件用于存储与其他计算核进行传输的数据;所述方法包括:分多次进行所述计算核之间的数据传输,其中,在m个计算核之间进行数据传输的情况下,在每次发送中,将m个计算核中的每个计算核的数据分别发送给m个计算核中一个目标计算核,其中,每个计算核对应的目标计算核各不相同;或者,在m个计算核与n个计算核之间进行数据传输的情况下,根据m个计算核和n个计算核的存储部件的容量,调整m个计算核每次发送的数据量大小,其中m个计算核与n个计算核存在重叠或不存在重叠。

在一种可能的实现方式中,在m个计算核之间进行数据传输的情况下,任意m-1个计算核组成的各计算核组的数据需要传输至作为目标计算核的其余的一个计算核,在每次发送中,将m个计算核中的每个计算核的数据分别发送给m个计算核中一个目标计算核,包括:在每次发送中,从各计算核组中,分别选取一个不同的计算核,将该计算核的数据发送至对应的目标计算核,共发送m-1次。

在一种可能的实现方式中,根据m个计算核和n个计算核的存储部件的容量,调整m个计算核每次发送的数据量大小,包括:根据m个计算核和n个计算核的存储部件的容量,调整m个计算核每次发送的数据量大小,使得每次发送中,m个计算核发送的数据总量最大,且m个计算核中的每一个发送的数据总量小于该计算核的存储部件的容量,n个计算核中的每一个接收的数据总量小于该计算核的存储部件的容量。

在一种可能的实现方式中,根据m个计算核和n个计算核的存储部件的容量,调整m个计算核每次发送的数据量大小,包括:确定约束条件,所述约束条件包括每次发送中,m个计算核中的每一个发送的数据总量小于该计算核的存储部件的容量,n个计算核中的每一个接收的数据总量小于该计算核的存储部件的容量;建立目标函数,所述目标函数使得每次发送中,m个计算核发送的数据总量最大;在满足所述约束条件的情况下,求解所述目标函数,获得传输方案,所述传输方案包括m个计算核中的每一个在每次传输中向n个计算核中的各计算核发送的数据量。

根据本公开的另一方面,提供了一种处理器,每个处理器包括多个计算核,每个处理器内部的计算核之间、以及不同处理器的计算核之间能够进行数据传输;其中,每个计算核包括存储部件,所述存储部件用于存储与其他计算核进行传输的数据;所述处理器分多次进行所述计算核之间的数据传输,其中,在m个计算核之间进行数据传输的情况下,在每次发送中,将m个计算核中的每个计算核的数据分别发送给m个计算核中一个目标计算核,其中,每个计算核对应的目标计算核各不相同;或者,在m个计算核与n个计算核之间进行数据传输的情况下,根据m个计算核和n个计算核的存储部件的容量,调整m个计算核每次发送的数据量大小,其中m个计算核与n个计算核存在重叠或不存在重叠。

在一种可能的实现方式中,在m个计算核之间进行数据传输的情况下,任意m-1个计算核组成的各计算核组的数据需要传输至作为目标计算核的其余的一个计算核,在每次发送中,将m个计算核中的每个计算核的数据分别发送给m个计算核中一个目标计算核,包括:在每次发送中,从各计算核组中,分别选取一个不同的计算核,将该计算核的数据发送至对应的目标计算核,共发送m-1次。

在一种可能的实现方式中,所述处理器用于根据m个计算核和n个计算核的存储部件的容量,调整m个计算核每次发送的数据量大小,包括:所述处理器根据m个计算核和n个计算核的存储部件的容量,调整m个计算核每次发送的数据量大小,使得每次发送中,m个计算核发送的数据总量最大,且m个计算核中的每一个发送的数据总量小于该计算核的存储部件的容量,n个计算核中的每一个接收的数据总量小于该计算核的存储部件的容量。

在一种可能的实现方式中,根据m个计算核和n个计算核的存储部件的容量,调整m个计算核每次发送的数据量大小,包括:确定约束条件,所述约束条件包括每次发送中,m个计算核中的每一个发送的数据总量小于该计算核的存储部件的容量,n个计算核中的每一个接收的数据总量小于该计算核的存储部件的容量;建立目标函数,所述目标函数使得每次发送中,m个计算核发送的数据总量最大;在满足所述约束条件的情况下,求解所述目标函数,获得传输方案,所述传输方案包括m个计算核中的每一个在每次传输中向n个计算核中的各计算核发送的数据量。

根据本公开的另一方面,提供了一种人工智能芯片,所述芯片包括如上所述的处理器。

根据本公开的另一方面,提供了一种电子设备,所述电子设备包括如上所述人工智能芯片。

通过本公开的实施例的数据传输方法,可分多次进行所述计算核之间的数据传输,在m个计算核之间进行数据传输的情况下,通过将m个计算核中的每个计算核的数据分别发送给m个计算核中一个目标计算核,可以使每次数据传输的过程中,各发送数据的计算核只需发送给一个计算核,各接收数据的计算核也只需要接收一个计算核的数据,可以防止在数据传输过程中由于多个计算核发送给一个计算核引起的路由传输拥堵,从而提高芯片的计算效率。或者,在m个计算核与n个计算核之间进行数据传输的情况下,根据m个计算核和n个计算核的存储部件的容量,确定约束条件,调整m个计算核每次发送的数据量大小,可以使各计算核每次接收数据或发送数据的数据量满足存储部件的容量,支持收发计算核数量相同或不同的多个计算核对多个计算核的数据传输,还支持发送数据总量大于接收数据总量的传输,可以克服传输过程中因发送数据量过多造成的拥堵及发送数据量过少造成资源浪费,提高芯片的计算效率。

根据下面参考附图对示例性实施例的详细说明,本公开的其它特征及方面将变得清楚。

附图说明

包含在说明书中并且构成说明书的一部分的附图与说明书一起示出了本公开的示例性实施例、特征和方面,并且用于解释本公开的原理。

图1示出根据本公开的实施例的处理器的示意图;

图2示出根据本公开的实施例的存储部件的示意图;

图3示出相关技术中数据传输方法的示意图;

图4示出根据本公开的实施例的数据传输方法的流程图;

图5示出根据本公开的实施例的数据传输方法的示意图;

图6示出根据本公开的实施例的数据传输方法的流程图;

图7示出根据本公开的实施例的数据传输方法的示意图;

图8示出根据本公开的实施例的数据传输方案的示意图;

图9是示出根据本公开实施例的电子装置的框图;

图10是示出根据本公开实施例的电子装置的框图。

具体实施方式

以下将参考附图详细说明本公开的各种示例性实施例、特征和方面。附图中相同的附图标记表示功能相同或相似的元件。尽管在附图中示出了实施例的各种方面,但是除非特别指出,不必按比例绘制附图。

在这里专用的词“示例性”意为“用作例子、实施例或说明性”。这里作为“示例性”所说明的任何实施例不必解释为优于或好于其它实施例。

另外,为了更好的说明本公开,在下文的具体实施方式中给出了众多的具体细节。本领域技术人员应当理解,没有某些具体细节,本公开同样可以实施。在一些实例中,对于本领域技术人员熟知的方法、手段、元件和电路未作详细描述,以便于凸显本公开的主旨。

图1示出根据本公开的实施例的处理器的示意图。根据本公开实施例的数据传输方法用于处理器的计算核之间的数据传输,每个处理器包括多个计算核,每个处理器内部的计算核之间、以及不同处理器的计算核之间能够进行数据传输;其中,每个计算核包括存储部件,所述存储部件用于存储与其他计算核进行传输的数据。

在一种可能的实现方式中,如图1所示,每个计算核包括处理部件及存储部件。所述处理部件可以包括树突单元、轴突单元、胞体单元、路由单元。所述存储部件可以包括多个存储单元。

在一种可能的实现方式中,多个处理器可以集成在一个类脑计算芯片中,类脑计算芯片即存算一体的神经形态电路,以大脑的处理模式为参考,通过模拟大脑中神经元对信息的传递与处理,提升处理效率并降低功耗。每个处理器可包括多个计算核,计算核之间可独立处理不同的任务,或并行处理同一任务,以提升处理效率。计算核之间可通过计算核内的路由单元进行核间信息传输。

在计算核之内,可以设置有处理部件和存储部件。处理部件可以包括树突单元、轴突单元、胞体单元和路由单元。处理部件可以模拟大脑的神经元对信息的处理模式,其中,树突单元用于接收信号,轴突单元用于发送尖峰信号,胞体单元用于信号的集成变换,路由单元用于同其它计算核进行信息传输。计算核内的处理部件可以对存储部件的多个存储单元进行读写访问,以与计算核内的存储部件进行数据交互,并可分别承担各自的数据处理任务和/或数据传输任务,以获得数据处理结果,或者与其他计算核进行通信。其中,与其他计算核进行通信包括与本处理器内的其他计算核进行通信,以及与其他处理器内的计算核通信。

在一种可能的实现方式中,图2示出根据本公开的实施例的存储部件的示意图。如图2所示,每个计算核的存储部件可以包括第一存储单元MEM0、第二存储单元MEM1和第三存储单元MEM2。例如,如图2所示,计算核Core_i包括第一存储单元MEM0、第二存储单元MEM1和第三存储单元MEM2,计算核Core_j包括第一存储单元MEM0、第二存储单元MEM1和第三存储单元MEM2。其中,计算核Core_i和计算核Core_j可以为相同处理器内的计算核,也可以为不同处理器内的计算核。

其中,第一存储单元MEM0、第二存储单元MEM1用于接收轴突单元的读写访问。轴突单元可以读取第一存储单元MEM0、第二存储单元MEM1内数据并进行数据处理,并将处理后的结果写入第一存储单元MEM0、第二存储单元MEM1。

第三存储单元MEM2用于接收路由单元的读写访问,以使路由单元将从第三存储单元MEM2读取的数据发送给外部计算核,或者将路由单元接收的来自外部计算核的数据送入第三存储单元MEM2存储。例如,如图2所示,计算核Core_i的第三存储单元MEM2可以接收该计算核Core_i的路由单元的读写访问,以使该计算核Core_i的路由单元将从该计算核Core_i的第三存储单元MEM2读取的数据发送给外部计算核Core_j,或者将计算核Core_i路由单元接收的来自外部计算核Core_j的数据送入计算核Core_i的第三存储单元MEM2存储。同样的,计算核Core_j的第三存储单元MEM2可以接收该计算核Core_j的路由单元的读写访问,以使该计算核Core_j的路由单元将从该计算核Core_j的第三存储单元MEM2读取的数据发送给外部计算核Core_i,或者将计算核Core_j路由单元接收的来自外部计算核Core_i的数据送入计算核Core_j的第三存储单元MEM2存储。

第一存储单元MEM0、第二存储单元MEM1和第三存储单元MEM2还可以用于接收胞体单元的读写访问。胞体单元可以读取第三存储单元MEM2中存储的数据,并可以进行处理,或传输至第一存储单元MEM0或第二存储单元MEM1。胞体单元还可以将从第一存储单元MEM0或第二存储单元MEM1读取的数据写入或经过处理后写入第三存储单元MEM2。

通过这种方式,第三存储单元MEM2可以存储用于同外部计算核进行通讯的数据,因此,计算核内部的数据可以与计算核外部的数据进行数据交换,便于相同处理器的计算核之间,以及不同处理器的计算核之间的数据通信。

在一种可能的实现方式中,第三存储单元MEM2可以为静态随机存取存储器(Static Random Access Memory,SRAM)。例如,可以包括读写宽度为16B,容量为12KB的SRAM。其中,第三存储单元MEM2可以接收胞体单元读取运算参数以进行非线性运算,或者可接收路由单元读取路由表,以进行数据通信。本公开对存储单元的读写宽度和容量不做限制。

在一种可能的实现方式中,所述方法包括分多次进行所述计算核之间的数据传输。

其中各计算核之间传输的数据可以是部分和数据,例如,在深度方向上切分引起的多个部分数据。

在将大规模的神经网络数据映射到众核簇(处理器中的多个计算核)的过程中,需要将处理数据在深度方向上进行切分,并将切分后的各个部分数据送入众核簇内各个计算核,众核簇内各个计算核对接收的部分数据进行运算获得部分数据的运算结果,称为部分和。在这种情况下,想要获取神经网络的运算结果还需要对部分数据的运算结果做进一步的相加运算,即对部分和数据做进一步数据处理。

由于计算核为存算一体神的经形态电路,计算核的存储空间比较小,受物理空间的限制,当多个计算核之间存在大量的缓存数据(例如交叠数据,部分和数据,图形整合等)进行交换时,缓存数据大于收发缓存空间需要多次传送。

相关技术中,采用单个计算核一次发送的数据量为该计算核的发送量上限,或者一次接收的数据量为该计算核的接收上限。在一个计算核对一个计算核发送的情况下,上述方案比较高效,在多个计算核对多个计算核发送的情况下,上述方案可能会存在路由发送延时长,容易造成拥堵以及资源的浪费。

举例来说,图3示出相关技术中数据传输方法的示意图。如图3所示,假设Sm=0、Sm=1、Sm=2、Sm=3分别对应四个计算核,可以表示为计算核Sm=0、计算核Sm=1、计算核Sm=2、以及计算核Sm=3。其中,计算核Sm=0存储了深度为0-31的部分和数据,计算核Sm=1存储了深度为32-63的部分和数据,计算核Sm=2存储了深度为64-95的部分和数据,计算核Sm=3存储了深度为96-127的部分和数据。其中,对应不同深度的各个部分和数据还包括了“0~13行”区域的数据、“14~27行”区域的数据、“28~41行”区域的数据、以及“42~55行”区域的数据。

其中,各区域数据可以是输入神经网络的按行切分的处理子数据,例如,假设所述神经网络对高度为56像素的图像数据做运算,“0~13行”区域的数据可以对应“0~13行”的子图数据。

其中,所述区域的数据大小为7KB,各个计算核内物理收发缓存空间容量大小的限制为12KB,即存储部件中第三存储单元MEM2的容量。

计算核Sm=0、计算核Sm=1、计算核Sm=2、以及计算核Sm=3需要分别发送21KB的数据,同时还需要分别接收21KB的数据。由于计算核内物理收发缓存空间容量大小的限制为12KB,每次发送和接收数据容量需要小于12KB,因此,各个计算核需要多次执行接收和发送操作才可以完成分别发送以及接收21KB数据的任务。

当计算核Sm=1、计算核Sm=2、以及计算核Sm=3同时发出7KB数据,即将自己“0~13行”区域数据发送给计算核Sm=0,计算核Sm=0共接收了21KB数据量,由于计算核Sm=0一次只能接收12KB,造成了传输拥堵。假如计算核Sm=1、计算核Sm=2、以及计算核Sm=3同时发出4KB(“0~13行”区域中的部分数据)给计算核Sm=0,则发送端的每个计算核所发送数据量小于12KB,造成很大的浪费,造成路由传输时间被延长。

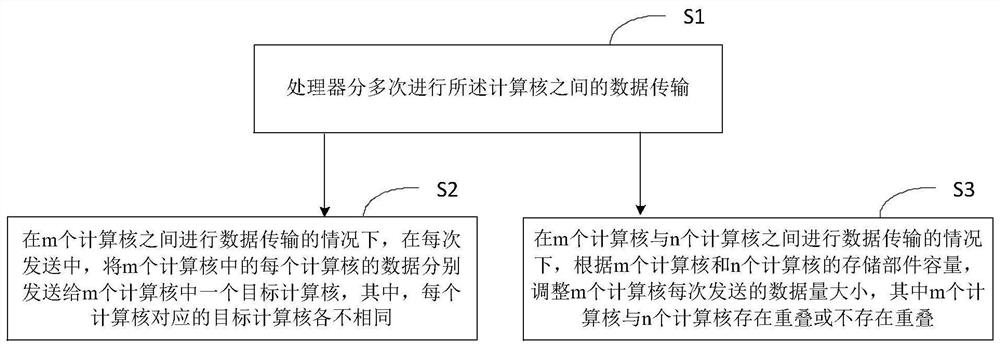

在一种可能的实现方式中,图4示出根据本公开的实施例的数据传输方法的流程图,如图4所示,在步骤S1中,处理器分多次进行所述计算核之间的数据传输,其中,在步骤S2中,在m个计算核之间进行数据传输的情况下,在每次发送中,将m个计算核中的每个计算核的数据分别发送给m个计算核中一个目标计算核,其中,每个计算核对应的目标计算核各不相同;或者,在步骤S3中,在m个计算核与n个计算核之间进行数据传输的情况下,根据m个计算核和n个计算核的存储部件的容量,调整m个计算核每次发送的数据量大小,其中m个计算核与n个计算核存在重叠或不存在重叠。

举例来说,在数据传输的过程中,需要通过各计算核的路由单元访问该计算核内存储部件的第三存储单元MEM2执行读写操作。在m个计算核之间或者在m个计算核与n个计算核之间进行数据传输,会受到计算核存储部件中第三存储单元MEM2容量的限制。

进一步,在多个计算核之间的数据传输,存在多个计算核发送数据至一个计算核或者一个计算核发送数据至多个计算核的情况,更容易使接收数据的计算核或者发送数据的计算核的第三存储单元MEM2发生数据溢出,即计算核接收数据或发送数据的数据量超过计算核第三存储单元MEM2容量。

在这种情况下,可以分多次进行所述计算核之间的数据传输。其中,在m个计算核之间进行数据传输的情况下,可以通过在每次数据传输的过程中,使各发送数据的计算核只需发送给一个计算核,各接收数据的计算核也只需要接收一个计算核的数据。

或者,在m个计算核与n个计算核之间进行数据传输的情况下,可以通过在每次数据传输的过程中,调整各计算核接收或发送数据量大小,在满足第三存储单元MEM2容量限制的情况下完成数据的传输。

其中m个计算核与n个计算核存在重叠或不存在重叠,即m个计算核与n个计算核中可以有部分相同的计算核,也可以m个计算核与n个计算核完全不同。并且,m个计算核与n个计算核的数量可以相同,也可以不同。

在一种可能的实现方式中,在m个计算核之间进行数据传输的情况下,任意m-1个计算核组成的各计算核组的数据需要传输至作为目标计算核的其余的一个计算核,在每次发送中,将m个计算核中的每个计算核的数据分别发送给m个计算核中一个目标计算核,包括:在每次发送中,从各计算核组中,分别选取一个不同的计算核,将该计算核的数据发送至对应的目标计算核,共发送m-1次。

举例来说,在m个计算核之间进行数据传输的情况下,任意m-1个计算核组成的各计算核组可以有m组,可以通过m-1次发送完成m个计算核之间进行数据传输。在每次发送中,从m个计算核组中分别选取一个不同的计算核,将该计算核的数据发送至对应的目标计算核。

例如,在4个计算核(m=4)之间进行数据传输,Sm=0、Sm=1、Sm=2、Sm=3分别对应4个计算核,任意3个计算核组成的各计算核组可以有4组:

第一组:Sm=0、Sm=1、Sm=2;

第二组:Sm=0、Sm=1、Sm=3;

第三组:Sm=0、Sm=2、Sm=3;

第四组:Sm=1、Sm=2、Sm=3;

其中,上述各计算核组内各计算核存储的数据需要传输至作为目标计算核的其余的一个计算核,例如,第一组的目标计算核是Sm=3,第二组的目标计算核是Sm=2,第三组的目标计算核是Sm=1,第三组的目标计算核是Sm=0。

在每次发送中,从各计算核组中,分别选取一个不同的计算核,即从各计算核组中选取出的计算核彼此不同,将该计算核的数据发送至对应的目标计算核,共发送3次。并且,在3次发送过程中需要遍历各组计算核。

例如,第一次可以从第一组选取计算核Sm=2、从第二组选取计算核Sm=3、从第三组选取计算核Sm=0、从第四组选取计算核Sm=1分别发送给对应的目标计算核Sm=3、Sm=2、Sm=1、Sm=0;

第一次还可以从第一组选取计算核Sm=0、从第二组选取计算核Sm=1、从第三组选取计算核Sm=2、从第四组选取计算核Sm=3分别发送给对应的目标计算核Sm=3、Sm=2、Sm=1、Sm=0。应当理解,对于每次计算核的选取,在满足每一次各组选取的计算核不相同的情况下,本公开对选取方式不做限定。

对于第二次,第三次选取计算核,需要在各组中之前未发送过数据的计算核中选取。例如,假如第一次从第一组选取计算核Sm=2、从第二组选取计算核Sm=3、从第三组选取计算核Sm=0、从第四组选取计算核Sm=1分别发送给对应的目标计算核Sm=3、Sm=2、Sm=1、Sm=0;第二次可从第一组选取计算核Sm=1、从第二组选取计算核Sm=0、从第三组选取计算核Sm=3、从第四组选取计算核Sm=2分别发送给对应的目标计算核Sm=3、Sm=2、Sm=1、Sm=0;或者,第二次也可以从第一组选取计算核Sm=0,从第二组选取计算核Sm=1,从第三组选取计算核Sm=2,从第四组选取计算核Sm=3。

通过上述在m个计算核之间进行数据传输的方法,可以防止在每次传输过程中由于多个计算核发送给一个计算核引起的路由传输拥堵。

在一种可能的实现方式中,在m个计算核之间进行数据传输的情况下,图5示出根据本公开的实施例的数据传输方法的示意图。

如图5所示,假设Sm=0、Sm=1、Sm=2、Sm=3分别对应4个计算核(m=4),可以表示为计算核Sm=0、计算核Sm=1、计算核Sm=2、以及计算核Sm=3。计算核Sm=0存储了深度为0-31的部分和数据,计算核Sm=1存储了深度为32-63的部分和数据,计算核Sm=2存储了深度为64-95的部分和数据,计算核Sm=3存储了深度为96-127的部分和数据。

其中,对应不同深度的各个部分和数据还包括了“0~13行”区域的数据、“14~27行”区域的数据、“28~41行”区域的数据、以及“42~55行”区域的数据。其中,所述区域的数据大小为7KB,各个计算核内物理收发缓存空间容量大小的限制为12KB,即存储部件中第三存储单元MEM2的容量。

如图5所示,所述循环遍历的数据传输方法包括三个计算周期,其中三个周期对应分多次进行所述计算核之间的数据传输的次数。

在T1计算周期,计算核Sm=0可以将“14~27行”区域的7KB数据送入计算核Sm=1,计算核Sm=1可以将“28~41行”区域的7KB数据送入计算核Sm=2,计算核Sm=2可以将“42~55行”区域的7KB数据送入计算核Sm=3,计算核Sm=3可以将“0~13行”区域的7KB数据送入计算核Sm=0。

其中,计算核Sm=0可以将“14~27行”区域的7KB数据送入计算核Sm=1,包括:

计算核Sm=0的胞体单元将第一存储单元MEM0(或第二存储单元MEM1)读取的“14~27行”区域的7KB数据按照计算核Sm=0设定的存储顺序(例如,从低地址到高地址的顺序,本公开不做限定)写入计算核Sm=0的第三存储单元MEM2。

计算核Sm=0的路由单元将第三存储单元MEM2中读取的“14~27行”区域的7KB数据发送给计算核Sm=1。

计算核Sm=1的路由单元将接收的计算核Sm=0发送的“14~27行”区域的7KB数据按照计算核Sm=1设定的存储顺序写入计算核Sm=1的第三存储单元MEM2。

计算核Sm=1的胞体单元读取计算核Sm=1的第三存储单元MEM2存储的“14~27行”区域的7KB数据按照计算核Sm=1设定的存储顺序写入计算核Sm=1的第一存储单元MEM0(或第二存储单元MEM1)。

应当理解,各计算核将待发送数据送入其它计算核的过程可以参考上述过程,不再赘叙。

在T2计算周期,计算核Sm=0可以将“28~41行”区域的7KB数据送入计算核Sm=2,计算核Sm=1可以将“42~55行”区域的7KB数据送入计算核Sm=3,计算核Sm=2可以将“0~13行”区域的7KB数据送入计算核Sm=0,计算核Sm=3可以将“14~27行”区域的7KB数据送入计算核Sm=1。

在T3计算周期,计算核Sm=0可以将“42~55行”区域的7KB数据送入计算核Sm=3,计算核Sm=1可以将“0~13行”区域的7KB数据送入计算核Sm=0,计算核Sm=2可以将“14~27行”区域的7KB数据送入计算核Sm=1,计算核Sm=3可以将“28~41行”区域的7KB数据送入计算核Sm=2。

这样,在上述过程中,在每个计算周期中,各个计算核发送的数据容量和接收的数据容量为7KB,可以满足各个计算核内物理收发缓存空间容量12KB大小的限制。

四个不同的计算核之间可以通过3个计算周期完成四个计算核的循环传输过程,并且在每个计算周期中,都可以遍历各个计算核,各个计算核发送和接收的数据量相同。

需要说明的是,尽管以计算核Sm=0、计算核Sm=1、计算核Sm=2、以及计算核Sm=3间的数据产生作为示例介绍了循环遍历的数据传输方法如上,但本领域技术人员能够理解,本公开应不限于此,对计算核的数量不做限制,m个不同计算核可以通过m-1次发送遍历至所有计算核。其中,m-1次代表数据传输的计算周期的次数。

通过上述多个计算核之间循环遍历的数据产生方法,可以解决数据路由传输的拥堵问题。

在一种可能的实现方式中,根据m个计算核和n个计算核的存储部件的容量,调整m个计算核每次发送的数据量大小,包括:

根据m个计算核和n个计算核的存储部件的容量,调整m个计算核每次发送的数据量大小,使得每次发送中,m个计算核发送的数据总量最大,且m个计算核中的每一个发送的数据总量小于该计算核的存储部件的容量,n个计算核中的每一个接收的数据总量小于该计算核的存储部件的容量。

举例来说,计算核之间进行数据传输,需要通过各计算核的路由单元访问该计算核内存储部件的第三存储单元MEM2执行读写操作。在m个计算核与n个计算核之间进行数据传输的情况下,会受到计算核存储部件中第三存储单元MEM2容量的限制,每个计算核一次发送的数据量为该计算核的发送量上限,或者一次接收的数据量为该计算核的接收上限,这两个上限均由第三存储单元MEM2容量的确定。

如果在m个计算核与n个计算核之间进行数据传输的过程中,如果不合理规划各计算核每次待发送数据的数据量和待接收数据的数据量,可能会出现有的计算核的待发送数据的数据量或待接收数据的数据量超过第三存储单元MEM2容量的限制,造成路由发送延时长,数据传输拥堵;而有的计算核的待发送数据的数据量或待接收数据的数据量很小或等于0,使计算核处于空闲状态,造成资源的浪费。

因此,如果在m个计算核与n个计算核之间进行数据传输的过程中,可根据各计算核第三存储单元MEM2容量的大小,满足在m个计算核中的每一个计算核每次需要发送至n个计算核的待发送数据总量小于每一个计算核的第三存储单元MEM2容量,并且n个计算核中的每一个计算核每次需要接收的m个计算核分别发送的待接收数据总量小于每一个计算核的第三存储单元MEM2容量的情况下,调整m个计算核中各个计算核每次发送的数据量大小,使得每次发送中,m个计算核发送的数据总量最大。

通过这种根据m个计算核和n个计算核的存储部件的容量,调整m个计算核每次发送的数据量大小的方式,克服传输过程中因发送数据量过多造成的拥堵及发送数据量过少造成资源浪费,提高芯片的计算效率。

在一种可能的实现方式中,图6示出根据本公开的实施例的数据传输方法的流程图。如图6所示,根据m个计算核和n个计算核的存储部件的容量,调整m个计算核每次发送的数据量大小,包括步骤如下:

步骤S31,确定约束条件,所述约束条件包括每次发送中,m个计算核中的每一个发送的数据总量小于该计算核的存储部件的容量,n个计算核中的每一个接收的数据总量小于该计算核的存储部件的容量。

步骤S32,建立目标函数,所述目标函数使得每次发送中,m个计算核发送的数据总量最大。

步骤S33,在满足所述约束条件的情况下,求解所述目标函数,获得传输方案,所述传输方案包括m个计算核中的每一个在每次传输中向n个计算核中的各计算核发送的数据量。

在步骤S31中,图7示出根据本公开的实施例的数据传输方法的示意图。如图7所示,所述处理器选取决策变量,包括需要执行发送数据操作的计算核、需要执行接收数据操作的计算核、以及各计算核需要发送和接收的数据量。如图7所示,需要执行发送数据操作的计算核有m个(m>0),可以表示为C

计算核C

所述处理器确定约束条件,即在每次发送中,各个计算核发送数据总量及接收数据总量满足计算核内物理收发缓存空间容量大小的限制。

在需要执行接收数据操作的n个计算核C′

在需要执行发送数据操作的m个计算核C

在如图7所示的各个计算核执行发送数据操作或执行接收操作的过程中,各个计算核发送数据总量及接收数据总量会受到计算核内物理收发缓存空间容量大小的限制。其中,计算核内物理收发缓存空间容量大小可以是计算核内存储部件中第三存储单元MEM2的容量大小,例如第三存储单元MEM2的容量大小为12KB。

因此,可以确定约束条件如下式:

在公式(1)中,

其中,m个计算核与n个计算核存在重叠或不存在重叠,如果存在重叠的情况,可能会出现发送数据的计算核C

在步骤S32中,所述处理器建立传输模型的目标函数,所述目标函数使得每次发送中,m个计算核发送的数据总量最大。

由于在数据收发的传输过程中,各计算核执行接收数据操作以及执行发送数据操作过程中接收和发送的数据量呈线性关系,可以采用线性规划方法建立传输模型。模型的目标函数为各个计算核执行接收数据操作以及执行发送数据操作的最少次数,可以等效为各个计算核每次执行接收数据操作以及执行发送数据操作过程中接收和发送的数据量最大,因此,可以确定传输模型的目标函数如下式:

在公式(2)中,

在步骤S33,所述处理器在满足约束条件的情况下,求解传输模型的目标函数,获得数据传输方案,所述传输方案包括m个计算核中的每一个计算核在每次传输中向n个计算核中的各计算核发送的数据量,计算核按照传输方案进行数据传输。

在满足约束条件的情况下对所建立传输模型的目标函数进行数学求解,可以获得数据传输方案,即各个计算核执行接收数据操作以及执行发送数据操作的次数最少的方案。需要执行发送数据操作的各计算核和需要执行接收数据操作的各计算核可以按照获得的传输方案执行相应指令完成计算核之间的数据传输。

举例来说,图8示出根据本公开的实施例的数据传输方案的示意图。如图8所示,在满足公式(1)中约束条件的情况下,对所建立如公式(2)所示的传输模型的目标函数进行数学求解,可以得到如图8所示的数据传输方案,即得到计算核C

在公式(3)中,Y

因此,如图8所示,需要执行发送数据操作的各计算核C

这样,通过寻找约束条件,建立接收和发送的数据总量最大的目标函数,采用数学线性规划模型进行建模求解,可以获得最优化的数据传输方案。其中,所述处理器可以实时发送数据,即在每次数据传输的过程中,根据m个计算核和n个计算核的存储部件的容量,确定约束条件,调整m个计算核每次发送的数据量大小。该方案可以支持收发计算核数量相同或不同的多个计算核对多个计算核的数据传输,并且可以支持发送数据总量大于接收数据总量的传输,克服传输过程中因发送数据量过多造成的拥堵及发送数据量过少造成资源浪费,提高芯片的计算效率。

根据本公开的另一方面,提供了一种处理器,每个处理器包括多个计算核,每个处理器内部的计算核之间、以及不同处理器的计算核之间能够进行数据传输;其中,每个计算核包括存储部件,所述存储部件用于存储与其他计算核进行传输的数据;所述处理器分多次进行所述计算核之间的数据传输,其中,在m个计算核之间进行数据传输的情况下,在每次发送中,将m个计算核中的每个计算核的数据分别发送给m个计算核中一个目标计算核,其中,每个计算核对应的目标计算核各不相同;或者,在m个计算核与n个计算核之间进行数据传输的情况下,根据m个计算核和n个计算核的存储部件的容量,调整m个计算核每次发送的数据量大小,其中m个计算核与n个计算核存在重叠或不存在重叠。

在一种可能的实现方式中,在m个计算核之间进行数据传输的情况下,任意m-1个计算核组成的各计算核组的数据需要传输至作为目标计算核的其余的一个计算核,在每次发送中,将m个计算核中的每个计算核的数据分别发送给m个计算核中一个目标计算核,包括:在每次发送中,从各计算核组中,分别选取一个不同的计算核,将该计算核的数据发送至对应的目标计算核,共发送m-1次。

在一种可能的实现方式中,所述处理器用于根据m个计算核和n个计算核的存储部件的容量,调整m个计算核每次发送的数据量大小,包括:所述处理器根据m个计算核和n个计算核的存储部件的容量,调整m个计算核每次发送的数据量大小,使得每次发送中,m个计算核发送的数据总量最大,且m个计算核中的每一个发送的数据总量小于该计算核的存储部件的容量,n个计算核中的每一个接收的数据总量小于该计算核的存储部件的容量。

在一种可能的实现方式中,根据m个计算核和n个计算核的存储部件的容量,调整m个计算核每次发送的数据量大小,包括:确定约束条件,所述约束条件包括每次发送中,m个计算核中的每一个发送的数据总量小于该计算核的存储部件的容量,n个计算核中的每一个接收的数据总量小于该计算核的存储部件的容量;建立目标函数,所述目标函数使得每次发送中,m个计算核发送的数据总量最大;在满足所述约束条件的情况下,求解所述目标函数,获得传输方案,所述传输方案包括m个计算核中的每一个在每次传输中向n个计算核中的各计算核发送的数据量。

在一种可能的实现方式中,本公开实施例还提出一种人工智能芯片,所述芯片包括如上所述的处理器。如图1所示,所述芯片可以包括一个或多个处理器,所述处理器可以包括多个计算核,本公开对芯片内计算核的数量不做限制。

在一种可能的实现方式中,本公开实施例提出了一种电子设备,所述电子设备包括如上所述的人工智能芯片。

图9是示出根据本公开实施例的一种组合处理装置1200的结构图。如图9中所示,该组合处理装置1200包括计算处理装置1202(例如,上述包括多个计算核的人工智能处理器)、接口装置1204、其他处理装置1206和存储装置1208。根据不同的应用场景,计算处理装置中可以包括一个或多个计算装置1210(例如,计算核)。

在一种可能的实现方式中,本公开的计算处理装置可以配置成执行用户指定的操作。在示例性的应用中,该计算处理装置可以实现为单核人工智能处理器或者多核人工智能处理器。类似地,包括在计算处理装置内的一个或多个计算装置可以实现为人工智能处理器核或者人工智能处理器核的部分硬件结构。当多个计算装置实现为人工智能处理器核或人工智能处理器核的部分硬件结构时,就本公开的计算处理装置而言,其可以视为具有单核结构或者同构多核结构。

在示例性的操作中,本公开的计算处理装置可以通过接口装置与其他处理装置进行交互,以共同完成用户指定的操作。根据实现方式的不同,本公开的其他处理装置可以包括中央处理器(Central Processing Unit,CPU)、图形处理器(Graphics ProcessingUnit,GPU)、人工智能处理器等通用和/或专用处理器中的一种或多种类型的处理器。这些处理器可以包括但不限于数字信号处理器(Digital Signal Processor,DSP)、专用集成电路(Application Specific Integrated Circuit,ASIC)、现场可编程门阵列(Field-Programmable Gate Array,FPGA)或者其他可编程逻辑器件、分立门或者晶体管逻辑器件、分立硬件组件等,并且其数目可以根据实际需要来确定。如前所述,仅就本公开的计算处理装置而言,其可以视为具有单核结构或者同构多核结构。然而,当将计算处理装置和其他处理装置共同考虑时,二者可以视为形成异构多核结构。

在一个或多个实施例中,该其他处理装置可以作为本公开的计算处理装置(其可以具体化为人工智能例如神经网络运算的相关运算装置)与外部数据和控制的接口,执行包括但不限于数据搬运、对计算装置的开启和/或停止等基本控制。在另外的实施例中,其他处理装置也可以和该计算处理装置协作以共同完成运算任务。

在一个或多个实施例中,该接口装置可以用于在计算处理装置与其他处理装置间传输数据和控制指令。例如,该计算处理装置可以经由所述接口装置从其他处理装置中获取输入数据,写入该计算处理装置片上的存储装置(或称存储器)。进一步,该计算处理装置可以经由所述接口装置从其他处理装置中获取控制指令,写入计算处理装置片上的控制缓存中。替代地或可选地,接口装置也可以读取计算处理装置的存储装置中的数据并传输给其他处理装置。

附加地或可选地,本公开的组合处理装置还可以包括存储装置。如图中所示,该存储装置分别与所述计算处理装置和所述其他处理装置连接。在一个或多个实施例中,存储装置可以用于保存所述计算处理装置和/或所述其他处理装置的数据。例如,该数据可以是在计算处理装置或其他处理装置的内部或片上存储装置中无法全部保存的数据。

根据不同的应用场景,本公开的人工智能芯片可用于服务器、云端服务器、服务器集群、数据处理装置、机器人、电脑、打印机、扫描仪、平板电脑、智能终端、PC设备、物联网终端、移动终端、手机、行车记录仪、导航仪、传感器、摄像头、相机、摄像机、投影仪、手表、耳机、移动存储、可穿戴设备、视觉终端、自动驾驶终端、交通工具、家用电器、和/或医疗设备。所述交通工具包括飞机、轮船和/或车辆;所述家用电器包括电视、空调、微波炉、冰箱、电饭煲、加湿器、洗衣机、电灯、燃气灶、油烟机;所述医疗设备包括核磁共振仪、B超仪和/或心电图仪。

图10示出根据本公开实施例的一种电子设备1900的框图。例如,电子设备1900可以被提供为一服务器。参照图10,电子设备1900包括处理组件1922(例如,包括多个计算核心的人工智能处理器),其进一步包括一个或多个计算核心,以及由存储器1932所代表的存储器资源,用于存储可由处理组件1922的执行的指令,例如应用程序。存储器1932中存储的应用程序可以包括一个或一个以上的每一个对应于一组指令的模块。此外,处理组件1922被配置为执行指令,以执行上述方法。

电子设备1900还可以包括一个电源组件1926被配置为执行电子设备1900的电源管理,一个有线或无线网络接口1950被配置为将电子设备1900连接到网络,和一个输入输出(I/O)接口1958。电子设备1900可以操作基于存储在存储器1932的操作系统,例如Windows ServerTM,Mac OS XTM,UnixTM,LinuxTM,FreeBSDTM或类似。

在本公开中,作为分离部件说明的单元可以是或者也可以不是物理上分开的,作为单元示出的部件可以是或者也可以不是物理单元。前述部件或单元可以位于同一位置或者分布到多个网络单元上。另外,根据实际的需要,可以选择其中的部分或者全部单元来实现本公开实施例所述方案的目的。另外,在一些场景中,本公开实施例中的多个单元可以集成于一个单元中或者各个单元物理上单独存在。

在上述实施例中,对各个实施例的描述都各有侧重,某个实施例中没有详述的部分,可以参见其他实施例的相关描述。上述实施例的各技术特征可以进行任意的组合,为使描述简洁,未对上述实施例中的各个技术特征所有可能的组合都进行描述,然而,只要这些技术特征的组合不存在矛盾,都应当认为是本说明书记载的范围。

本公开的电子设备或处理器还可以被应用于互联网、物联网、数据中心、能源、交通、公共管理、制造、教育、电网、电信、金融、零售、工地、医疗等领域。进一步,本公开的电子设备或处理器还可以用于云端、边缘端、终端等与人工智能、大数据和/或云计算相关的应用场景中。在一个或多个实施例中,根据本公开方案的算力高的电子设备或处理器可以应用于云端设备(例如云端服务器),而功耗小的电子设备或处理器可以应用于终端设备和/或边缘端设备(例如智能手机或摄像头)。在一个或多个实施例中,云端设备的硬件信息和终端设备和/或边缘端设备的硬件信息相互兼容,从而可以根据终端设备和/或边缘端设备的硬件信息,从云端设备的硬件资源中匹配出合适的硬件资源来模拟终端设备和/或边缘端设备的硬件资源,以便完成端云一体或云边端一体的统一管理、调度和协同工作。

以上已经描述了本公开的各实施例,上述说明是示例性的,并非穷尽性的,并且也不限于所披露的各实施例。在不偏离所说明的各实施例的范围和精神的情况下,对于本技术领域的普通技术人员来说许多修改和变更都是显而易见的。本文中所用术语的选择,旨在最好地解释各实施例的原理、实际应用或对市场中的技术的改进,或者使本技术领域的其它普通技术人员能理解本文披露的各实施例。

- 数据传输方法、处理器、芯片及电子设备

- 数据传输方法、装置、芯片、芯片模组及电子设备