内存装置和在内存装置中辅助读取操作的方法

文献发布时间:2023-06-19 11:05:16

技术领域

本发明涉及一种内存装置,且具体来说涉及一种内存装置和可改进读取操作的性能的内存装置的方法。

背景技术

近年来,内存装置用于在广泛范围的电子装置中储存信息。出于低功耗的目的,已引入具有低功耗的内存装置。举例来说,低功耗内存装置可具有低于1V上电复位(power-on-reset;POR)跳脱点,且在低功耗内存装置的上电过程期间需要用于读取操作(例如,熔丝读取、寄存器读取)的低电源。然而,低电源可导致读取操作的速度和准确度下降。

随着近年来内存装置的普及,用于改进内存装置的性能的更具创新性的方法和设计的需求已增长。

发明内容

本发明引入一种内存装置和其方法,所述方法可在读取操作中产生升压电压且将升压电压供应到感测电源线,进而改进读取操作的性能。

在一些实施例中,内存装置包含逻辑电路、电荷泵、开关以及感测放大器。逻辑电路配置成接收至少一个输入信号且对至少一个输入信号执行逻辑操作以输出使能信号。电荷泵耦接到逻辑电路,且配置成根据使能信号产生升压电压。开关耦接于电荷泵与感测电源线之间,且配置成根据使能信号控制电荷泵与感测电源线之间的电连接,以将升压电压供应到感测电源线。感测放大器配置成使用来自感测电源线的升压电压执行读取操作。

在一些实施例中,内存装置包含逻辑电路、多级电荷泵、第一开关、第二开关以及感测放大器。逻辑电路配置成接收至少一个输入信号且对至少一个输入信号执行逻辑操作以输出使能信号。多级电荷泵可包括第一级和第二级,且配置成根据使能信号通过第一级产生第一升压电压且通过第二级产生第二升压电压。第一开关耦接于多级电荷泵的第一级与感测电源线之间,且配置成根据使能信号将第一升压电压供应到感测电源线。第二开关耦接于多级电荷泵的第二级与感测电源线之间,且配置成根据使能信号将第二升压电压供应到感测电源线。感测放大器配置成使用来自感测电源线的第一升压电压和第二升压电压执行读取操作。

在一些实施例中,方法包含以下步骤:对至少一个输入信号执行逻辑操作以产生使能信号;根据使能信号通过电荷泵产生升压电压;根据使能信号控制电荷泵与感测电源线之间的电连接以将升压电压供应到感测电源线;以及使用来自感测电源线的升压电压执行读取操作。

附图说明

包含附图以提供对本发明的进一步理解,并且附图并入本说明书中且构成本说明书的一部分。附图说明本发明的实施例,且与描述一起用于解释本发明的原理。

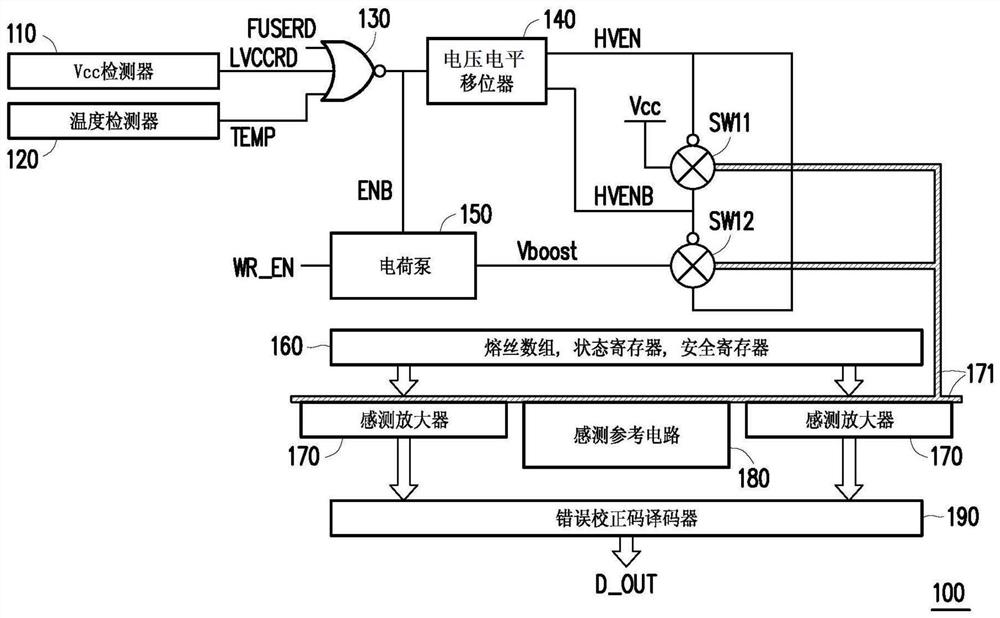

图1是示出根据本发明的一些实施例的内存装置的示意图;

图2是示出根据本发明的一些替代性实施例的内存装置的示意图;

图3是示出根据本发明的一些实施例的辅助内存装置中的读取操作的方法的流程图。

具体实施方式

现将详细地参考本发明的示范性实施例,示范性实施例的实例说明于附图中。只要有可能,相同元件符号在附图和描述中用来表示相同或相似部分。

应理解,在不脱离本发明的范围的情况下,可利用其它实施例且可作出结构性改变。此外,应理解,本文中所使用的措词和术语是出于描述的目的且不应视为是限制性的。本文中使用“包含”、“包括”或“具有”以及其变化形式意在涵盖其后列出的项目和其等效物以及额外项目。除非另有限制,否则术语“连接(connected)”以及“耦接(coupled)”及其在本文中的变体是广义上使用的并且涵盖直接和间接连接以及耦接。

参看图1,内存装置100可包含电源检测器110(或Vcc检测器110)、温度检测器120、逻辑电路130、电压电平移位器140、开关SW1和开关SW2、电荷泵150、电路160、感测放大器170、感测参考电路180以及译码器190。电源检测器110可检测电源电压Vcc的电压电平(level)以产生电源检测信号LVCCRD。在一些实施例中,电源检测信号LVCCRD可指示电源电压Vcc的电压电平是否小于预定阈值电压。举例来说,当电源电压Vcc的电压电平小于预定阈值电压时,电源检测信号LVCCRD可指示高电压电平(例如,逻辑电平“1”)。当电源电压Vcc的电压电平不小于预定阈值电压时,电源检测信号LVCCRD可指示低电压电平(例如,逻辑电平“0”)。电源电压Vcc的电压电平可影响读取操作的性能。举例来说,当电源电压Vcc低时,可降低读取操作的速度和准确度。因此,在电源电压Vcc低于预定阈值电压时,升压电压用于改进读取操作的性能是必需的。在一些实施例中,预定阈值电压可为用于成功地执行读取操作所需的最小电压。在本发明中不限制电源检测器110的类型和结构。

在一些实施例中,温度检测器120配置成检测内存装置100的温度以产生温度信号TEMP。温度信号TEMP可指示内存装置的温度是否大于预定阈值温度。举例来说,当内存装置100的温度大于预定阈值温度时,温度信号TEMP可指示高逻辑电平。当内存装置100的温度不大于预定阈值温度时,温度信号TEMP可指示低逻辑电平。由于当内存装置100的温度增加时内存装置100上读取操作的速度可能降低,因此当内存装置的温度高时,用于读取操作的升压电压是必需的,以提高读取操作的速度。在本发明中不限制温度检测器120的类型和结构。

在一些实施例中,在内存装置100的上电过程期间执行若干读取操作。举例来说,在内存装置100的上电过程期间,执行读取操作以读取储存于内存装置100的熔丝数组、状态寄存器以及安全寄存器中的信息。上电读取信号FUSERD可用于指示在内存装置100的上电过程期间是否执行至少一个读取操作。举例来说,当在上电过程期间执行读取操作时,上电读取信号FUSERD可具有高逻辑电平;且上电读取信号FUSERD可另外具有低逻辑电平。在一些实施例中,当在上电过程期间执行至少一个读取操作时,可产生升压电压且为至少一个读取操作供应升压电压。

在图1中,熔丝数组、状态寄存器以及安全寄存器由电路160表示,但熔丝数组、状态寄存器以及安全寄存器的位置不限于图1中所示的位置。在一些实施例中,内存装置100的熔丝数组可储存与内存装置100的身份有关的信息、内存装置100的冗余地址或适合储存于熔丝数组中的任何其它信息。内存装置100的状态寄存器可储存与内存装置100中的内存单元/块的状态相关的信息。内存单元/块的状态可包含忙碌状态、空闲状态或其它合适的状态。内存装置100的安全寄存器可储存安全信息,诸如内存装置100的受保护的单元/块、不受保护的单元/块。

在一些实施例中,内存装置100可配置成执行低电源写入操作,所述操作随后为低电源读取验证操作。验证信号(未示出)可用于指示是否执行低电源读取验证操作。当对内存装置100执行低电源读取验证操作时,可产生升压电压且为低电源读取验证操作供应升压电压,以提高低电源读取验证操作的速度和准确度。

逻辑电路130可接收电源检测信号LVCCRD、温度信号TEMP以及上电读取信号FUSERD中的至少一个,且对所接收信号执行逻辑操作以产生信号ENB。在一些实施例中,逻辑电路130可以是或可包含或非逻辑门,所述逻辑门配置成对输入到逻辑电路130的电源检测信号LVCCRD、温度信号TEMP以及上电读取信号FUSERD执行或非操作。因此,当所有上电读取信号FUSERD、温度检测信号TEMP以及电源检测信号LVCCRD处于低逻辑电平(例如,逻辑电平“0”)时,信号ENB具有高逻辑电平(例如,逻辑电平“1”)。当上电读取信号FUSERD、温度检测信号TEMP以及电源检测信号LVCCRD中的至少一个处于高逻辑电平(例如,逻辑电平“1”)时,信号ENB具有低逻辑电平(例如,逻辑电平“0”)。信号ENB可指示出现以下事件中的至少一个:在上电过程期间通过上电读取信号FUSERD的读取操作、通过温度检测信号TEMP的过高温度以及通过电源检测信号LVCCRD的过低电源电压Vcc。应注意,逻辑电路130的结构不限于图1中所示的结构,具有基于至少一个输入信号执行逻辑操作以产生信号ENB的功能的任何逻辑电路属本发明的范围。

在一些实施例中,将电荷泵150耦接到逻辑电路130以从逻辑电路130接收信号ENB。电荷泵150配置成产生升压电压Vboost,所述升压电压可在电源升压模式中大于电源电压Vcc。基于信号ENB(或信号EN,所述信号是ENB的反相信号)确定启动电源升压模式。在一些实施例中,当信号ENB处于低逻辑电平时(当电源检测信号LVCCRD、温度信号TEMP以及上电读取信号FUSERD中的至少一个处于高逻辑电平时),启动电源升压模式以产生升压电压Vboost。或者,当信号ENB处于高逻辑电平时(例如,当所有电源检测信号LVCCRD、温度信号TEMP以及上电读取信号FUSERD处于低逻辑电平时),禁用电源升压模式。

在一些实施例中,电荷泵150可进一步接收写入使能信号WR_EN,所述写入使能信号是用于写入操作的使能信号。在接收写入使能信号WR_EN之后,电荷泵150可产生用于写入操作的升压电压Vboost。换句话说,电荷泵150可在电源升压模式中共享写入操作和读取操作。

在一些实施例中,将电压电平移位器140耦接到逻辑电路130以接收信号ENB,且配置成转换信号ENB以产生信号HVEN和信号HVENB。信号HVEN是信号HVENB的反相信号;且信号HVEN和信号HVENB的电压电平不同于信号ENB的电压电平。举例来说,信号HVEN和信号HVENB的电压电平的绝对值可大于信号ENB的电压电平。

将开关SW11和开关SW12耦接到电压电平移位器140以接收信号HVEN和信号HVENB作为用于开关SW11和开关SW12的控制信号。在一些实施例中,当启动电源升压模式时,信号HVENB处于低逻辑电平且信号HVEN处于高逻辑电平。因此,关闭开关SW11且打开开关SW2以将电荷泵150电连接到感测电源线171,以在电源升压模式期间将升压电压Vboost供应到感测电源线171。或者,当禁用电源升压模式时,信号HVENB处于高逻辑电平且信号HVEN处于低逻辑电平。因此,关闭开关SW12且打开开关SW11以将电源电压Vcc供应到感测电源线171。换句话说,开关SW11和开关SW12可基于信号HVEN和信号HVENB控制电荷泵150与感测电源线171之间的电连接。

在一些实施例中,将感测放大器170耦接到感测电源线171,且配置成基于从感测电源线171接收的电源执行读取操作。当禁用电源升压模式(例如,打开开关SW11且关闭开关SW12)时,感测放大器170可基于电源电压Vcc执行读取操作。当启动电源升压模式(例如,关闭开关SW11且打开开关SW12)时,感测放大器170可基于升压电压Vboost执行读取操作。在一些实施例中,感测参考电路180配置成产生参考电压且将参考电压输出到感测放大器170。感测放大器170可基于从感测参考电路180输出的参考电压执行读取操作。

译码器190耦接到感测放大器170,且配置成译码通过感测放大器170输出的数据以产生读取操作的输出数据D_OUT。在一些实施例中,译码器190可为错误校正码(errorcorrection code;ECC)译码器,但译码器190的类型和结构在本申请案中不受限制。

参看图2,内存装置200可包含电源检测器210、温度检测器220、逻辑电路230、电压电平移位器240、多级电荷泵250、开关SW21和开关SW22、箝位电路260、感测放大器270、感测参考电路280以及译码器290。在一些实施例中,如图2所示的电源检测器210、逻辑电路230、感测放大器270、感测参考电路280以及译码器290与如图1所示的电源检测器110、逻辑电路130、感测放大器170、感测参考电路180以及译码器190相似,因此在下文省略关于这些元件的详细描述。

电压电平移位器240可通过反相器INV耦接到逻辑电路230。反相器INV配置成反相由逻辑电路230输出的信号ENB以产生信号EN。电压电平移位器240配置成转换信号EN以产生信号BoostEN,其中信号BoostEN的电压电平可高于信号EN的电压电平。

在一些实施例中,多级电荷泵250可包含第一级250a和第二级250b,所述第一级和第二级耦接到逻辑电路230以接收信号ENB。多级电荷泵250的第一级250a和第二级250b可分别在电源升压模式中产生升压电压V1和升压电压V2,其中基于信号ENB确定电源升压模式的启动。举例来说,当信号ENB处于低逻辑电平时,启动电源升压模式以分别产生升压电压V1和升压电压V2。当信号ENB处于高逻辑电平时,禁用电源升压模式。

在一些实施例中,多级电荷泵250可进一步接收写入使能信号WR_EN,所述写入使能信号为对内存装置200的写入操作的使能信号。在接收写入使能信号WR_EN之后,多级电荷泵250配置成产生用于写入操作的升压电压V1和升压电压V2。在一些实施例中,连接电路251配置成在写入操作期间将第一级250a和第二级250b串联电性耦接。因此,可产生具有不同升压电平的升压电压V1和升压电压V2,并将所述升压电压供应到写入操作。

在一些实施例中,连接电路251可包含晶体管M1和晶体管M2,其中晶体管M1耦接于第一级250a与第二级250b之间,且晶体管M2耦接于接收电源电压Vcc的参考节点与晶体管M1与第二级250b之间的连接节点之间。晶体管M1和晶体管M2的控制端配置成从电压电平移位器240接收信号BoostEN。因此,连接电路251可控制多级电荷泵250的第一级250a与第二级250b之间的电连接。在一些实施例中,连接电路251配置成在电源升压模式中将第一级250a与第二级250b电绝缘以用于读取操作。在一些替代实施例中,连接电路251可在写入操作中将第一级250a和第二级250b串联电性耦接到内存装置200。

在一些实施例中,开关SW21耦接于第一级250a与感测电源线271之间,且配置成基于信号BoostEN控制第一级250a与感测电源线271之间的电连接。开关SW22耦接于第二级250b与感测电源线271之间,以基于信号BoostEN控制第二级250b与感测电源线271之间的电连接。在一些实施例中,信号BoostEN配置成在启动电源升压模式时打开开关SW21和开关SW22。具体地说,当启动电源升压模式时,启动多级电荷泵250的第一级250a和第二级250b以产生升压电压V1和升压电压V2,并打开开关SW21和开关SW22以将升压电压V1和升压电压V2供应到感测电源线271。同时,连接电路251配置成将第一级250a与第二级250b电绝缘。因此,第一级250a和第二级250b可充当平行运行的两个独立电荷泵,以将升压电压V1和升压电压V2供应到感测电源线271。以这种方式,提高使感测电源线271的电压升压的效率。

在一些实施例中,箝位电路260耦接到感测电源线,且配置成将在感测电源线271处的电压箝制到预定电压电平。以这种方式,箝位电路260可防止电源升压模式期间的电压过冲。箝位电路260可包含晶体管M3,所述晶体管设计为耦接于接收电源电压Vcc的参考节点与感测电源线271之间的二极管。在一些实施例中,根据电源电压Vcc和晶体管M3的偏压电压的电压电平确定预定电压电平。应注意,箝位电路260的结构不限于图2中所示的结构,具有钳制感测电源线271的电压的功能的任何电路在本发明的范围内。

参看图3,示出在读取操作中使感测电源线的电源升压的方法的流程图。在步骤S510中,对至少一个输入信号执行逻辑操作以产生使能信号。在一些实施例中,至少一个输入信号可包含上电读取信号、电源检测信号以及温度信号中的至少一个。逻辑操作可为或非操作,但本发明不限于此。

在步骤S520中,根据使能信号由电荷泵产生升压电压。举例来说,当使能信号处于第一逻辑电平中时,电荷泵产生升压电压;且当使能信号处于第二逻辑电平中时,电荷泵不产生升压电压。

在步骤S530中,根据使能信号控制电荷泵与感测电源线之间的电连接,以将升压电压供应到感测电源线。在实例中,当使能信号处于第一逻辑电平中时,将电荷泵电性耦接到感测电源线,以使得将升压电压供应到感测电源线。当使能信号处于第二逻辑电平中时,电荷泵与感测电源线电绝缘,以使得升压电压不供应到感测电源线。

在步骤S540中,使用来自感测电源线的升压电压执行读取操作。在一些实施例中,读取操作可以是或可包含在上电过程期间的读取操作(诸如熔丝读取操作、状态寄存器读取操作、安全寄存器读取操作)、低电源读取操作以及在执行写入操作之后执行的验证读取操作。

概括地说,本发明的实施例引入一种内存装置和其方法,所述方法可在电源升压模式中使感测电源线升压,进而改进读取操作的性能。电荷泵用于基于通过对至少一个输入信号执行逻辑操作产生的使能信号来产生升压电压。电荷泵与感测电源线之间的电连接通过开关由使能信号控制。因此,在读取操作期间将升压电压供应到感测电源线。以这种方式,提高在内存装置中读取操作(尤其为低电源读取操作)的速度和准确度。另外,在一些实施例中,针对内存装置的写入操作而设计的电荷泵可用于在读取操作中升压电压。因此,减少本发明的内存装置的制造成本。

最后应说明的是:以上各实施例仅用以说明本发明的技术方案,而非对其限制;尽管参照前述各实施例对本发明进行了详细的说明,本领域的普通技术人员应当理解:其依然可以对前述各实施例所记载的技术方案进行修改,或者对其中部分或者全部技术特征进行等同替换;而这些修改或者替换,并不使相应技术方案的本质脱离本发明各实施例技术方案的范围。

- 内存装置和在内存装置中辅助读取操作的方法

- 内存集群的存储方法及装置、内存集群的读取方法及装置