多通路数据处理电路及系统

文献发布时间:2023-06-19 11:08:20

相关申请的交叉引用

本申请要求于2019年11月27日提交的申请号为16/698,349的美国专利申请的优先权,其通过引用整体并入本文。

技术领域

各个实施例总体涉及一种数据处理电路和系统,并且更特别地,涉及一种多通路数据处理电路和系统。

背景技术

为了满足相对较大的传输频率带宽的数据接口的需求,大多数电子产品采用串行器/解串器(SerDes)和多个通路来实现电子产品内部或外部的数据接口和相关电路。对于SerDes和多个通路,电子产品应用相应的数据处理电路以对数据接口意图发送或接收的数据执行必要的处理。

例如,对于多通路数据处理电路或通信装置,由于产品标准或产品开发,设计者需要设计具有不同传输频率带宽的数据接口的多个版本的电子产品。当采用多通路技术时,设计者可以基于传输频率带宽相对较小的某个版本的电子装置的数据接口电路,来布置相对较多数量的通路,从而容易地获得传输频率带宽相对较高的版本的电子产品的数据接口电路。

然而,从相应的数据处理电路的角度来看,通路的总数已经增加。因此,设计者需要重新考虑如何设置传输频率带宽较小版本的电子产品的数据处理电路的更新,或者是否校正数据处理电路以便将数据处理电路应用到传输频率带宽较大版本的电子产品。由于这种设置或校正可能涉及诸如相关芯片的集成电路内的电路布置的编程,因此这种设置或校正可能会增加电路的复杂性。在最坏的情况下,设计者可能不得不重新设计合适的数据处理电路。在这种最坏的情况下,当开发电子产品的相关版本时,可能会影响开发效率,并且可能会增加开发成本。

因此,当应用多通路技术时,就可扩展性而言,仍需要改善电子产品中使用的相应数据处理电路。

发明内容

各个实施例针对一种多通路数据处理电路及系统,该多通路数据处理电路及系统可以应用于采用多通路技术的电子装置,并实现具有相对低复杂度的电路结构的数据处理电路,从而满足具有数据接口的传输频率带宽彼此不同的多个版本的电子产品的需求。

在实施例中,提供了一种多通路数据处理电路,包括:多个通路电路模块,联接到数据接口的多个通路,并且包括第一通路电路模块和第二通路电路模块,其中,每一个通路电路模块包括第一处理电路和第二处理电路,第一通路电路模块的第一处理电路具有联接到第二通路电路模块的第一处理电路的输出端子,并且第一通路电路模块的第二处理电路具有联接到第二通路电路模块的第二处理电路的输出端子;以及多个寄存器,包括第一信息寄存器和第二信息寄存器,其中,第一信息寄存器具有联接到第二通路电路模块的第一处理电路的输入端子,以及联接到第一通路电路模块的第一处理电路的输出端子,并且第二信息寄存器具有联接到第二通路电路模块的第二处理电路的输入端子,以及联接到第一通路电路模块的第二处理电路的输出端子。

多个通路电路模块进一步包括第三通路电路模块,其中,第二通路电路模块的第一处理电路具有电联接到第三通路电路模块的第一处理电路的输出端子,并且第二通路电路模块的第二处理电路具有电联接到第三通路电路模块的第二处理电路的输出端子。第一信息寄存器的输入端子通过第三通路电路模块的第一处理电路电联接到第二通路电路模块的第一处理电路;并且第二信息寄存器的输入端子通过第三通路电路模块的第二处理电路电联接到第二通路电路模块的第二处理电路。

多个通路电路模块进一步包括第四通路电路模块,其中,第三通路电路模块的第一处理电路具有电联接到第四通路电路模块的第一处理电路的输出端子,并且第三通路电路模块的第二处理电路具有电联接到第四通路电路模块的第二处理电路的输出端子。第一信息寄存器的输入端子通过第三通路电路模块的第一处理电路以及第四通路电路模块的第一处理电路电联接到第二通路电路模块的第一处理电路;并且第二信息寄存器的输入端子通过第三通路电路模块的第二处理电路以及第四通路电路模块的第二处理电路电联接到第二通路电路模块的第二处理电路。

多个通路电路模块中的每一个进一步包括:控制电路,联接到与通路电路模块相对应的第一处理电路和第二处理电路。与通路电路模块相对应的控制电路根据通路控制信号,选择性地启用与通路电路模块相对应的第一处理电路和第二处理电路中的一个或多个。

当通路控制信号指示执行第一处理时,多个通路电路模块的控制电路启用多个通路电路模块的第一处理电路,将多个通路电路模块的第一处理电路分别联接到多个通路,并且以并行方式处理多个通路的不同数据集。

在实施例中,提供了一种多通路数据处理系统,包括:多个物理层电路模块,以并行方式联接到数据接口的多个通路;以及多通路数据处理电路,其中,多通路数据处理电路包括:多个通路电路模块,通过多个物理层电路模块分别联接到多个通路,并且包括第一通路电路模块和第二通路电路模块,其中每一个通路电路模块包括第一处理电路和第二处理电路,第一通路电路模块的第一处理电路具有联接到第二通路电路模块的第一处理电路的输出端子,并且第一通路电路模块的第二处理电路具有联接到第二通路电路模块的第二处理电路的输出端子;以及多个寄存器,包括第一信息寄存器和第二信息寄存器,其中,第一信息寄存器具有联接到第二通路电路模块的第一处理电路的输入端子,以及联接到第一通路电路模块的第一处理电路的输出端子,并且第二信息寄存器具有联接到第二通路电路模块的第二处理电路的输入端子,以及联接到第二通路电路模块的第一处理电路的输出端子。

当通路控制信号指示执行第一处理时,多个通路电路模块的控制电路启用多个通路电路模块的第一处理电路,并且将多个通路电路模块的第一处理电路通过多个物理层电路模块分别联接到多个通路,并且以并行方式处理多个通路的不同数据集。

多个物理层电路模块为传送器物理层电路。

多个物理层电路模块为接收器物理层电路。

在实施例中,提供了一种多通路数据处理系统,包括:N数量的通路电路模块,每一个通路电路模块包括M数量的处理电路并分别被配置为从通路接收数据,N和M中的每一个为2或大于2;以及M数量的寄存器,其中,寄存器之中的第P寄存器与通路电路模块的每一个内的处理电路之中的第P处理电路被联接以配置级联结构,使得第P寄存器将数据输出到通路电路模块之中的第一通路电路模块的第P处理电路中,并且通路电路模块之中的最后通路电路模块的第P处理电路将数据输出到第P寄存器,其中,处理电路中的每一个被配置为处理从前一级提供的数据,并将经处理的数据输出到后一级,并且其中,处理电路中的每一个进一步被配置为接收来自通路之中的相应通路的数据,并被配置为将经处理的数据输出到外部。

附图说明

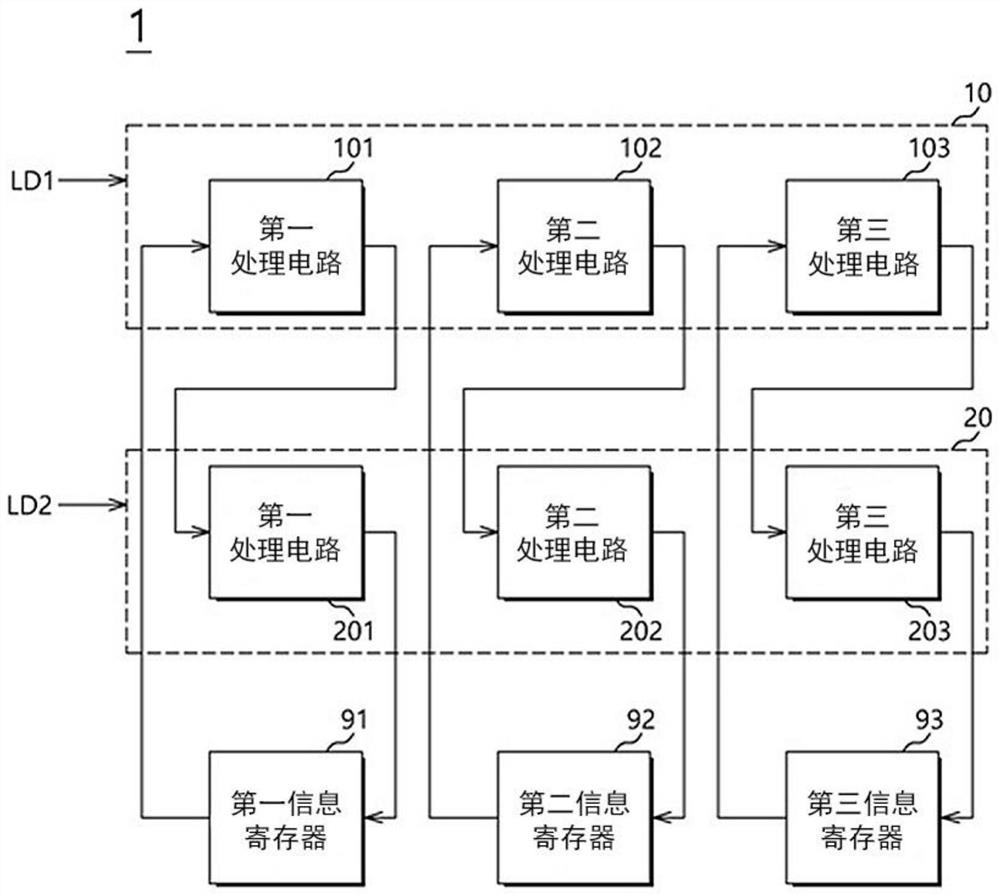

图1为示出多通路数据处理电路的实施例的框图。

图2为用于描述通过图1的多通路数据处理电路并行处理数据的实施例的示图。

图3为示出图1的多通路数据处理电路的另一实施例的框图。

图4为用于描述通过图3的多通路数据处理电路并行处理数据的实施例的示图。

图5为示出图1的多通路数据处理电路的另一实施例的框图。

图6为用于描述通过图5的多通路数据处理电路并行处理数据的实施例的示图。

图7为示出用于通过图1的多通路数据处理电路实现各种数据处理方法的实施例的框图。

图8为用于描述通过图7的多通路数据处理电路处理的协议数据单元的实施例的示图。

图9为示出使用图7的多通路数据处理电路实现CRC(循环冗余校验)的实施例的信号图

图10为示出包括多通路数据处理系统的电子装置的实施例的框图。

具体实施方式

为了充分理解本公开的目的、特征和效果,将参照附图通过特定实施例详细描述本公开。

以下参照附图更详细地描述本发明的各个实施例。然而,注意的是,本发明可以以不同的形式和变型来实施,并且不应被解释为限于本文阐述的实施例。相反,提供所描述的实施例是为了使本公开将是透彻且完整的,并且将本发明充分传达给本发明所属领域的技术人员。在整个公开中,在本发明的各个附图和实施例中,相同的附图标记指代相同的部件。

在下文中,各个实施例提供了一种多通路数据处理电路,该电路可以应用于采用多通路技术的电子装置。

根据实施例,多通路数据处理电路包括多个通路电路模块和多个寄存器。

多个通路电路模块联接到数据接口的多个通路,例如,第一至第N通路,其中N为2、3、4或更大。多个通路电路模块可以包括用于第一至第N通路的第一至第N通路电路模块。第一至第N通路电路模块中的每一个可以包括第一至第M处理电路,其中M是大于或等于2的整数。第一至第M处理电路可以具有不同的处理功能。

多个寄存器可以包括第一至第M寄存器。当执行特定的数据处理时,第P寄存器可以使用第一至第N通路电路模块的每一个内的第P处理电路进行操作,其中P是从1到M的整数。

在电路布置中,可以将用于第一至第N通路的第一至第N通路电路模块的每一个内的第一处理电路级联。在第一至第N通路电路模块的第一处理电路之中的两个相邻的第一处理电路之间,一个处理电路的输出端子联接到另一处理电路的输入端子。在第一至第N通路电路模块的级联的第一处理电路之中,第一个和最后一个联接到第一至第M寄存器之中的第一寄存器。类似地,还可以级联用于第一至第N通路的第一至第N通路电路模块的第P处理电路,以实现类似于第一至第N通路电路模块的第一处理电路的电路布置。

上述实施例可以应用于采用多通路技术的电子装置,并实现具有相对低复杂度的电路结构的数据处理电路,从而满足数据接口的传输频率带宽彼此不同的多个版本的电子装置的需求。当采用多通路技术时,设计者可以根据传输频率带宽相对较小版本的电子产品的数据接口电路,来布置相对较多数量的通路,从而获取传输频率带宽相对较大版本的电子产品的数据接口电路。多通路数据处理电路的结构可以应用于与电子产品内的数据接口电路相对应的数据处理电路。多通路数据处理电路的结构可以在电子产品内的两个或更多个元件或模块之间或之中实现数据接口电路的数据处理电路。

例如,由于用作数据存储装置的电子产品根据从数据接口传送或接收的数据来执行必要的处理,因此可以布置用于多通路数据处理电路中的各个第一至第N通路的第一至第N通路电路模块所需的第一至第M处理电路。例如,电子产品通过硬件电路执行处理,例如在OSI(开放系统互连)模型中的物理层、数据链路层、网络层或其它层次的数据处理,或其它随机必要的数据处理,并且本实施例不限于此。

可以布置与数据接口中的第一至第N通路相对应的第一至第N通路电路模块,并且可以对用于第一至第N通路的各个第一至第N通路电路模块内的第P处理电路进行级联,其中P是从1到M的整数。各个第一至第N通路电路模块内的级联的第P处理电路之中的第一个和最后一个被布置为使得联接到第一至第M寄存器之中的第P寄存器。

因此,多通路数据处理电路可以在电子产品中实现。以这种方式,多通路数据处理电路的结构可以满足对具有数据接口的传输频率带宽的大小彼此不同的多个版本的电子产品的电路布置的需求。根据本实施例的多通路数据处理电路不仅可以具有相对较低的复杂度,而且还可以具有优异的扩展性,从而有助于提高电子产品的开发效率,并降低电子产品的开发成本。

在下文中,将参照如下多个实施例描述多通路数据处理电路。

图1为示出多通路数据处理电路的实施例的框图。如图1所示,多通路数据处理电路1包括多个通路电路模块(例如,10和20)以及多个寄存器(例如,91、92和93)。多个通路电路模块联接到数据接口的多个通路,例如,两个通路LD1和LD2,并且包括通路电路模块10和通路电路模块20。

通路电路模块中的每一个包括第一处理电路(例如,101或201)以及第二处理电路(例如,102或202)。在实施例中,通路电路模块中的每一个可以进一步包括第三处理电路(例如,103或203)。

通路电路模块的每一个内的每个处理电路具有输入端子和输出端子,并且本实施例不限于输入端子和输出端子的数量和布置。例如,根据数据处理的必要性,处理电路可以具有一个或多个输入端子,该一个或多个输入端子被设置为接收相应通路的数据或从另一处理电路接收输出,并且具有一个或多个输出端子,该一个或多个输出端子被设置为将数据输出到第一至第M寄存器之中的相应寄存器,或者将数据输出到另一处理电路的输入端子,或者用作第P处理电路的相应通路的输出端子。这里,P是从1到M的整数。如图1所示,通路电路模块10的第一处理电路101具有联接到通路电路模块20的第一处理电路201的输出端子,通路电路模块10的第二处理电路102具有联接到通路电路模块20的第二处理电路202的输出端子,并且通路电路模块10的第三处理电路103具有联接到通路电路模块20的第三处理电路203的输出端子。

第一至第M寄存器包括第一信息寄存器91和第二信息寄存器92。第一信息寄存器91具有联接到通路电路模块20的第一处理电路201的输入端子,以及联接到通路电路模块10的第一处理电路101的输出端子。第二信息寄存器92具有联接到通路电路模块20的第二处理电路202的输入端子,以及联接到通路电路模块10的第二处理电路102的输出端子。在实施例中,多个寄存器可以进一步包括第三信息寄存器93,并且第三信息寄存器93具有联接到通路电路模块20的第三处理电路203的输入端子,以及联接到通路电路模块10第三处理电路103的输出端子。

图2是用于描述通过图1的多通路数据处理电路并行处理数据的实施例的示图。如图2所示,通过数据接口的两个通路LD1和LD2以并行方式将由PA_PDU0至PA_PDUQ-1表示的Q个数据集输入到图1的多通路数据处理电路1,从而并行处理数据。这里,Q是大于或等于2的整数。参照图1和图2,数据集PA_PDU0至PA_PDUQ-1中的数据集PA_PDU0和PA_PDU1以并行方式输入到通路电路模块10和20以处理数据。然后,数据集PA_PDU2和PA_PDU3以并行方式输入到通路电路模块10和20以处理数据。以这种方式,最后的数据集PA_PDUQ-2和PA_PDUQ-1也以并行方式输入到通路电路模块10和20以处理数据。通过这样的处理,可以提高数据处理效率。

图3为示出图1的多通路数据处理电路的另一实施例的框图。如图3所示,与包括通路电路模块10和20的图1的多通路数据处理电路1相比,图3的多通路数据处理电路1A可以进一步包括通路电路模块30。多通路数据处理电路1A可以应用于采用用于三个通路的数据接口的电子产品。

如图3所示,通路电路模块20的第一处理电路201具有联接到通路电路模块30的第一处理电路301的输出端子,通路电路模块20的第二处理电路202具有联接到通路电路模块30的第二处理电路302的输出端子。在实施例中,通路电路模块20的第三处理电路203具有联接到通路电路模块30的第三处理电路303的输出端子。

如图3所示,第一信息寄存器91的输入端子联接到通路电路模块30的第一处理电路301。当与图1相比时,第一信息寄存器91的输入端子通过通路电路模块30的第一处理电路301联接到通路电路模块20的第一处理电路201,并且第二信息寄存器92的输入端子联接到通路电路模块30的第二处理电路302。当与图1相比时,第二信息寄存器92的输入端子通过通路电路模块30的第二处理电路302联接到通路电路模块20的第二处理电路202。在实施例中,第三信息寄存器93的输入端子联接到通路电路模块30的第三处理电路303。当与图1相比时,第三信息寄存器93的输入端子通过通路电路模块30的第三处理电路303联接到通路电路模块20的第三处理电路203。

图4为用于描述通过图3的多通路数据处理电路并行处理数据的实施例的示图。参照图4,通过数据接口的三个通路LD1、LD2以及LD3以并行方式将由PA_PDU0至PA_PDUQ-1表示的Q个数据集输入到图3的多通路数据处理电路1A,从而并行处理数据。这里,Q是大于或等于3的整数。参照图3和图4,数据集PA_PDU0至PA_PDUQ-1之中的数据集PA_PDU0至PA_PDU2以并行方式输入到通路电路模块10、20和30以处理数据。然后,数据集PA_PDU3至PA_PDU5以并行方式输入到通路电路模块10、20和30以处理数据。以这种方式,最后的数据集PA_PDUQ-3和PA_PDUQ-1也以并行方式输入到通路电路模块10、20和30以处理数据。通过这样的处理,可以提高数据处理效率。

图5为示出图1的多通路数据处理电路的另一实施例的框图。如图5所示,与包括通路电路模块10、20和30的图3的多通路数据处理电路1A相比,图5的多通路数据处理电路1B可以进一步包括通路电路模块40。多通路数据处理电路1B可以应用于采用用于四个通路的数据接口的电子产品。

如图5所示,通路电路模块30的第一处理电路301具有联接到通路电路模块40的第一处理电路401的输出端子,通路电路模块30的第二处理电路302具有联接到通路电路模块40的第二处理电路402的输出端子。在实施例中,通路电路模块30的第三处理电路303具有电联接到通路电路模块40的第三处理电路403的输出端子。

如图5所示,第一信息寄存器91的输入端子联接到通路电路模块40的第一处理电路401。当与图1相比时,第一信息寄存器91的输入端子通过通路电路模块40的第一处理电路401以及通路电路模块30的第一处理电路301联接到通路电路模块20的第一处理电路201,并且第二信息寄存器92的输入端子联接到通路电路模块40的第二处理电路402。当与图1相比时,第二信息寄存器92的输入端子通过通路电路模块40的第二处理电路402以及通路电路模块30的第二处理电路302联接到通路电路模块20的第二处理电路202。在实施例中,第三信息寄存器93的输入端子联接到通路电路模块40的第三处理电路403。当与图1相比时,第三信息寄存器93的输入端子通过通路电路模块40的第三处理电路403以及通路电路模块30的第三处理电路303联接到通路电路模块20的第三处理电路203。

图6为用于描述通过图5的多通路数据处理电路并行处理数据的实施例的示图。参照图6,通过数据接口的四个通路LD1至LD4以并行方式将由PA_PDU0至PA_PDUQ-1表示的Q个数据集输入到图5的多通路数据处理电路1B,从而并行处理数据。这里,Q是大于或等于4的整数。参照图5和图6,数据集PA_PDU0至PA_PDUQ-1之中的数据集PA_PDU0至PA_PDU3以并行方式输入到通路电路模块10、20、30和40以处理数据。然后,数据集PA_PDU4至PA_PDU7以并行方式输入到通路电路模块10、20、30和40以处理数据。以这种方式,最后的数据集PA_PDUQ-4和PA_PDUQ-1也以并行方式输入到通路电路模块10、20、30和40以处理数据。通过这样的处理,可以提高数据处理效率。

图7为示出用于通过图1的多通路数据处理电路来实现各种数据处理方法的实施例的框图。如图7所示,多通路数据处理电路1C包括多个通路电路模块(例如,10C和20C)以及多个寄存器(例如,91C、92C和93C)。多个通路电路模块联接到数据接口的多个通路,例如,两个通路LD1和LD2,并且包括通路电路模块10C和通路电路模块20C。通路电路模块中的每一个包括第一处理电路(例如,101C或201C)以及第二处理电路(例如,102C或202C)。在实施例中,通路电路模块中的每一个可以进一步包括第三处理电路(例如,103C或203C)。

第一处理电路101C或102C包括两个或更多个输入端子。如图7所示,第一处理电路101C的一个输入端子用于从通路LD1接收数据,第一处理电路101C的另一输入端子用于从第一信息寄存器91C接收输出。第一处理电路201C的一个输入端子用于从通路LD2接收数据,第一处理电路201C的另一输入端子用于从第一处理电路101C接收经处理的数据。

第一处理电路101C或201C包括两个或更多个输出端子。如图7所示,第一处理电路101C的一个输出端子用于将第一处理电路101C的经处理的数据传送到第一处理电路201C,第一处理电路101C的另一输出端子用于输出第一处理电路101C的处理结果(例如,由PU1_LD1_R表示),使得电子产品的后续电路使用或处理该处理结果。

第一处理电路201C的一个输出端子用于将第一处理电路201C的经处理的数据输出到第一信息寄存器91C,第一处理电路201C的另一输出端子用于输出第一处理电路201C的处理结果(例如,由PU1_LD2_R表示),使得电子产品的后续电路使用或处理该处理结果。第二处理电路102C或202C或第三处理电路103C或203C也可以以类似的方式实现。

如图7所示,第二处理电路102C和202C的处理结果分别由PU2_LD1_R和PU2_LD2_R表示,第三处理电路103C和203C的处理结果分别由PU3_LD1_R和PU3_LD2_R表示。

图7所示的多通路数据处理电路1C的多个寄存器91C至93C由时钟信号CLK控制。

如图7所示,在实施例中,通路电路模块的每一个可以进一步包括控制电路(例如111C或211C),并且控制电路联接到与通路电路模块相对应的多个处理电路。例如,在图7中,控制电路111C联接到与通路电路模块10C相对应的第一处理电路101C、第二处理电路102C和第三处理电路103C,并且控制电路211C联接到与通路电路模块20C相对应的第一处理电路201C、第二处理电路202C和第三处理电路203C。与通路电路模块相对应的控制电路根据通路控制信号(例如,SCL1或SCL2),选择性地启用或禁用与通路电路模块相对应的多个处理电路中的一个或多个。例如,在图7中,控制电路111C根据通路控制信号SCL1选择性地启用或禁用与通路电路模块10C相对应的第一处理电路101C、第二处理电路102C和第三处理电路103C中的一个或多个。控制电路211C也可以类似地应用于通路电路模块20C。

在图7的实施例中,第一处理电路101C和102C使用CRC(循环冗余校验)电路实现。CRC是一种哈希函数,用于根据诸如网络数据帧、数据包或计算机文件的数据来生成具有少量固定位数的验证码。例如,CRC用于检测或检查可能在传输或存储数据之后发生的错误。当存在待传送或存储的数据时,第一处理电路可以通过CRC计算校验码,并将校验码附加到数据的后面。然后,接收器侧的第一处理电路可以执行相同的CRC操作,并且检查校验码是否彼此一致,以便检查数据中是否发生了改变。例如,第一处理电路101C和201C由符合国际标准CCITT CRC-16的CRC电路实现。

第二处理电路102C或202C可以实现另一种数据处理。例如,第二处理电路102C或202C可以计算数据接口中的数据流量,或包或帧的总数。第三处理电路103C或203C可以实现另一种数据处理。然而,本实施例不限于这样的示例。

返回图7,当通路控制信号SCL1或SCL2指示执行第一处理时,多个通路电路模块10C和20C的控制电路111C和211C启用多个通路电路模块的第一处理电路101C和201C,并将多个通路电路模块中的第一处理电路101C和201C联接到各个通路LD1和LD2,从而以并行方式处理多个通路的不同数据集。例如,通路控制信号可以指示启用第一处理电路,以及禁用第二和第三处理电路。

通路控制信号还可以指示不同的组合,以启用或禁用与同一通路对应的通路电路模块中的一个或多个处理电路。例如,当通路控制信号SCL1或SCL2指示执行第一处理和第二处理时,多个通路电路模块的第一和第二处理电路执行第一和第二处理。此外,CRC通过第一处理电路执行,并且其它数据处理,例如计算数据接口中包或帧的数据流量或总数的处理,通过第二处理电路同时执行。

图8为用于描述由图7的多通路数据处理电路处理的PDU(协议数据单元)的实施例的示图。如图8所示,框800表示包括数据字符1至9、A、B和C的帧或包。此外,框850表示表达为与该帧相对应的多个十六进制码的数据集,并且包括例如0x1017至0x1012A以及0x04A20的数据集。在数据集之中,最后一个数据集0x04A20是基于CCITT CRC-16通过CRC生成的校验码,该校验码是对0x1017至0x1012A的数据集执行的。

这里,假设用作表达为与该帧相对应的多个十六进制码的数据集的框850从传送器侧传送到接收器侧,并且图7的多通路数据处理电路1C在接收器侧验证数据的准确性。

图9为示出通过图7的多通路数据处理电路实现CRC的实施例的信号图。如图7、8和9所示,在由信号901表示的时钟信号CLK的情况下,框850表示的帧的多个数据集通过数据接口的两个通路LD1和LD2以并行方式输入到图7的多通路数据处理电路1C,以便并行处理数据。如信号904和信号907所示,框850表示的帧的两个数据集(例如,0x10107和0x08284)以并行方式输入到通路电路模块10C的第一处理电路101C以及通路电路模块20C的第一处理电路201C,以处理数据。然后,两个数据集(例如,0x03132和0x03334)以并行方式输入到第一处理电路101C和201C,以处理数据。以这种方式,最后的两个数据集(例如,0x1012A和0x04A20)也以并行方式输入到第一处理电路101C和201C,以处理数据。

如图9所示,控制电路111C和211C在由信号901表示的时钟信号CLK的情况下,根据通路控制信号SCL1和SCL2,将信号902和906输出到第一处理电路101C和201C,并选择性地启动第一处理电路101C和201C以处理数据。信号902和906的高电平表示启用,信号902和906的低电平表示禁用。

第一信息寄存器91C的输出端子和输入端子的数据分别由信号903和908表示,并且数据的0xFFFF表示第一信息寄存器91C的输出端子的初始值。

第一处理电路101C和201C的处理结果PU1_LD1_R和PU1_LD2_R分别由信号905和909表示。如图9所示,与第一处理电路201C的处理结果PU1_LD2_R相对应的信号909在计算的最后的输出中被表达为准确的脉冲波信号(例如,高电平),因为通过CRC获得了准确的结果。然而,本实施例不限于这样的示例。

例如,框800的帧可以由诸如传输层、网络层和/或数据链路层的各个层进行数据处理,但是本公开不限于此。如图8所示,作为示例,框800表示帧中包括的数据。例如,框800包括头部801、主体803和脚部805。头部801包括字段ESC_DL、SOF、TC和RSD。ESC_DL表示用于区分控制代码和数据代码的特定代码,而SOF表示指示这样的控制代码开始一个新帧的代码。TC定义信息流量或优先级,并被设置为多个不同的信息流量之一,例如TC0。RSD表示保留字段。头部801还可以包括网络层指示811和网络层信息813。例如,当将网络层指示811(例如,由L3S表示)设置为1时,其指示帧包括网络层L3的信息。网络层信息813(例如,由DestDeviceID_ENC表示)是目的地装置的识别码ID或地址,指示待将该协议数据单元传送到的装置。头部801还包括指示在协议数据单元中也存在传输层信息(即,L4)的传输层指示值815(例如,由L4S表示)。头部801包括端口标识值817(例如,由DestCPortID_ENC表示),该端口标识值817确定L4信息的数据对应于目的地装置的哪个端口,并且还包括L4信息的流量控制信标位(例如,由FCT表示)。可以基于DestCPortID_ENC和DestDeviceID_ENC识别端到端连接。头部801还可以包括指示该帧是否是传输层的最后消息的端位(例如,由EOM表示)。主体803包括待传送的用户或应用数据。脚部805可以包括基于CCITT CRC-16通过CRC生成的校验码,并且还包括字段ESC_DL、EOF_EVEN和FSN。EOF_EVEN表示帧的最后的控制代码,FSN表示帧序列号,该帧序列号为数据链路层正在传输时的序列号。然而,本实施例不限于这样的示例。

在一些实施例中,通过参照图3或图5的电路布置,图7的多通路数据处理电路1C可以额外扩展为适于三个通路、四个通路或其它数量的通路的多通路数据处理电路,以便增加数据频率带宽。因此,多通路数据处理电路可以满足对基于多通路数据处理电路实现的电子产品的数据频率带宽的要求。

图10为示出使用电子装置的多通路数据处理系统的实施例的框图。如图10所示,电子装置2和电子装置9执行通信或数据传输,并且电子装置2是基于多个通路(两个或更多通路)的数据接口,并且包括多通路数据处理系统(例如,1000或2000)。电子装置2是数据处理电路、通信装置、存储装置等,电子装置9是智能电话、可穿戴装置、平板计算机、笔记本计算机、台式计算机、服务器或其它随机计算装置,数据接口是USB、SATA或安装在计算机内部或外部的其它随机合适的数据接口。电子装置2和电子装置9可以实现为电子系统的一部分。如图10所示,电子装置2包括系统模块1300和系统存储器1400。例如,电子装置2可以实现为诸如存储卡的存储器装置,或诸如固态硬盘的存储装置,电子装置9可以实现为网络设备。在一些实施例中,电子装置2和电子装置9可以实现为电子产品内部的两个或更多个元件或模块。然而,本实施例不限于这样的示例。

多通路数据处理系统1000或2000包括多个物理层电路模块(例如,1101和1102或2101和2102)和多通路数据处理电路。多通路数据处理电路包括多个通路电路模块(例如,1201和1202或2201和2202)和多个寄存器。当多个通路电路模块1201和1202或2201和2202以及多个寄存器是对应于上述多通路数据处理电路或其组合的多个实施例(例如,图1、图3、图5和图7)中的至少一个的多个通路电路模块和多个寄存器时,多个通路电路模块通过多个物理层电路模块电联接到各个通路。例如,每个通路被配置为传送差分信号对。

在实施例中,当通路控制信号指示执行任意一个处理时,多个通路电路模块的控制电路启用与该处理相对应的多个通路电路模块和电路处理电路,将与该处理相对应的多个通路电路模块和处理电路分别通过多个物理层电路模块联接到多个通路,并且以并行方式处理多个通路的不同数据集,如图2、图4、图6或图9所示。

如图10所示,在实施例中,多个物理层电路模块(例如,1101和1102)是传送器物理层电路。在实施例中,多个物理层电路模块2101和2102是接收器物理层电路。在图10中,电子装置2中的传送器级和接收器级中的每一个都使用两个通路。然而,本实施例不限于这样的示例。在一些实施例中,可以以这样的方式配置电子装置2:使得传送器级和接收器级中的每一个使用第一数量的通路和第二数量的通路。第一数量和第二数量可以彼此相同或不同,并且第一数量和第二数量中的至少一个可以等于或大于2。根据图1、图3、图5和图7中的多通路数据处理电路的实施例,可以实现适于根据本实施例的电子装置的数据处理电路。

例如,参照图7至图9以及相关实施例,图10的物理层电路模块2101和2102可以被配置为处理来自两个或更多个通路(参见图8和图9)的数据集。然后,物理层电路模块2101和2102可以将经处理的数据集传送到根据图7的实施例实现的通路电路模块2201和2202,以便根据上述实施例执行CRC,或者并行执行CRC,以及数据流量和包或帧的总和的计算。类似地,图10的通路电路模块1201和1202可以被配置为处理从系统模块1300提供的两个或更多个通路的数据集。然后,通路电路模块1201和1202可以将通过CRC等处理的数据传送到物理层电路模块1101和1102,以便将数据传送到通路。

因此,可以实现能够应用于采用了多通路技术并且具有相对较低复杂度的电路结构的电子装置的数据处理电路,以提供多通路数据处理电路及系统的各种实施例,能够满足具有数据接口的传输频率带宽互不相同的多个版本的电子产品的需求。根据本实施例的多通路数据处理电路和系统不仅可以具有相对较低的复杂度,而且可以具有优异的可扩展性,从而有助于提高电子产品的开发效率并降低电子产品的开发成本。

在与多通路数据处理电路有关的实施例中,多通路数据处理电路、通路电路模块、处理电路、信息寄存器和控制电路中的一个或多个可以利用一个或多个逻辑门、逻辑电路、数字电路或其它电路来实现,利用诸如FPGA(现场可编程门阵列)的可编程集成电路或诸如ASIC(专用集成电路)的电路实现,或利用专用电路或模块实现。然而,本实施例不限于这样的示例。

因此,上述实施例可以应用于采用多通路技术的电子装置,并且可以实现具有相对低复杂度的电路结构的数据处理电路,以提供多通路数据处理电路和系统的各种实施例,能够满足具有数据接口的传输频率带宽互不相同的多个版本的电子产品的需求。根据本实施例的多通路数据处理电路和系统不仅可以具有相对较低的复杂度,而且还可以具有优异的可扩展性,从而有助于提高电子产品的开发效率并降低电子产品的开发成本。

尽管上文已经描述了各个实施例,但是本领域技术人员将理解,所描述的实施例仅是示例。因此,本文描述的多通路数据处理电路和系统不应基于描述的实施例来限制。

- 多通路数据处理电路及系统

- 上行数据通路的构建方法及数据处理系统