三维集成电路及其制造方法

文献发布时间:2023-06-19 11:14:36

技术领域

本发明涉及存储器领域。具体而言,本发明涉及三维集成电路及其制造方法。

背景技术

动态随机存储器(DRAM)的工艺一般提供三层金属层,使得电源布线在高速高容量设计中受到很大的局限。在高速工作时,DRAM的内部电路会消耗很大的电流,有限的电源布线使得内部电源线上的压降过大,恶化了时序电路功能和性能参数。

图1示出了现有技术中DRAM晶片的一个金属层的电源布线的示意图。如图1所示,DRAM晶片具有多个电源管脚(power pad)引入外部电源,并且DRAM晶片的金属层上布置有多个横向和纵向布置的宽窄不一的电源线。图1中的虚线框内的电源线向数百个并行高频信号电路供电,这部分电源线被设置为宽导线。然而,由于DRAM仅有三层金属层的布线限制,虚线框内的电源线往往不足(宽度有限),使得这些电源线上的电压与电源管脚引入的电源电压相比存在很大的压降,影响电路的时序功能和性能。

因此,亟需解决现有技术中的上述技术问题。

发明内容

本发明涉及三维集成电路及其制造方法及对应的电子设备。在所述三维集成电路中,利用逻辑工艺芯片上的电源网络来改进存储器阵列芯片上的电源网络的压降,解决了现有技术中存储器阵列芯片电源布线不足的技术问题,使得存储器阵列内的电路可以工作在更高的频率上,并行操作更多的模块,从而具有更好的性能。

根据本发明的第一方面,提供了一种三维集成电路,所述三维集成电路包括:

存储器晶片,所述存储器晶片的金属层设置有多个第一电源线,所述多个第一电源线用于为所述存储器晶片上的电路供电;

逻辑晶片,所述逻辑晶片的金属层设置有多个第二电源线,所述多个第二电源线用于为所述存储器晶片上的电路供电;

其中所述多个第一电源线中的每一个第一电源线与所述多个第二电源线中的一个相应的第二电源线并联连接。

根据本发明的第二方面,提供了一种电子设备,其中所述电子设备包括根据上述第一方面所述的三维集成电路。

根据本发明的第三方面,提供了一种制造三维集成电路的方法,其中所述方法包括:

获取存储器晶片,所述存储器晶片的金属层设置有多个第一电源线,所述多个第一电源线用于给所述存储器晶片上的电路供电;

获取逻辑晶片,所述逻辑晶片的金属层设置有多个第二电源线,所述多个第二电源线用于为所述存储器晶片上的电路供电;以及

将所述多个第一电源线中的每一个第一电源线与所述多个第二电源线中的一个相应的第二电源线并联连接。

根据本发明的第四方面,提供了一种电子设备,其中所述电子设备包括根据上述第三方面所述的方法制造的三维集成电路。

附图说明

为了更好地理解本发明且示出如何实施本发明,现在将参考附图,在附图中:

图1示出了现有技术中DRAM晶片的一个金属层的电源布线的示意图;

图2例示了根据本发明的一个实施方案的三维集成电路的电源网络的示意图;以及

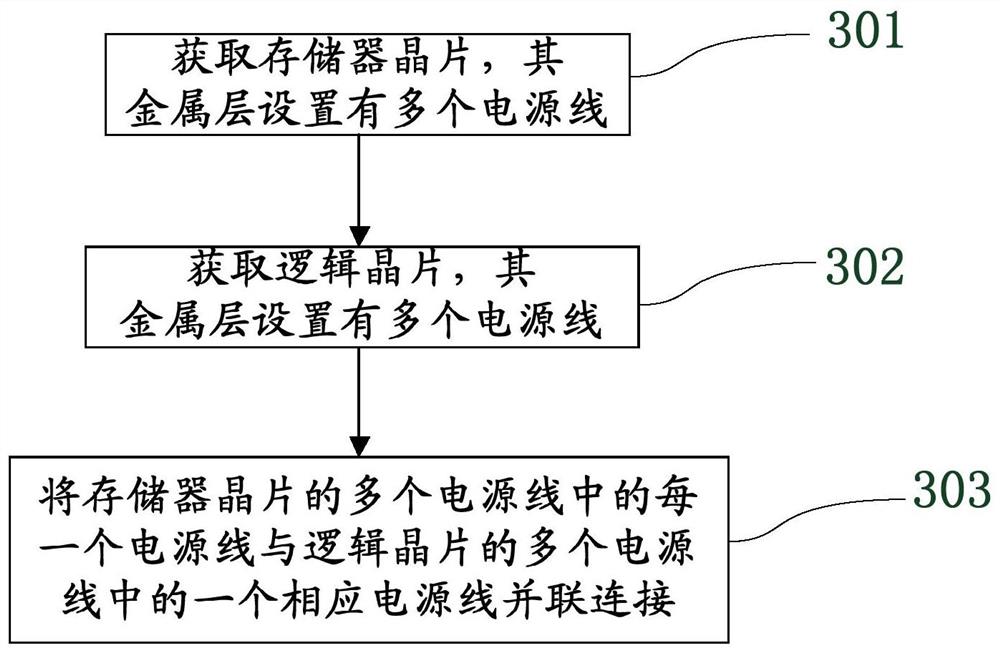

图3例示了根据本发明的制造三维集成电路的方法的一个实施方案的流程图。

具体实施方式

下面的描述阐述了根据本公开内容的示例实施方案。对于本领域普通技术人员而言,其他示例实施方案和实施方式将是显而易见的。此外,本领域普通技术人员将认识到,可以代替下面所讨论的实施方案或与下面讨论的实施方案相结合地应用多种等同技术,且所有这样的等同物应被认为是本公开内容所涵盖的。

根据本发明的第一方面,提供了一种三维集成电路,包括:

存储器晶片,所述存储器晶片的金属层设置有多个第一电源线,所述多个第一电源线用于为所述存储器晶片上的电路供电;

逻辑晶片,所述逻辑晶片的金属层设置有多个第二电源线,所述多个第二电源线用于为所述存储器晶片上的电路供电;

其中所述多个第一电源线中的每一个第一电源线与所述多个第二电源线中的一个相应的第二电源线并联连接。

根据本发明的第一方面的具体实施方案,其中所述存储晶片的顶部金属层的第一电源线与所述逻辑晶片的顶部金属层的第二电源线在一一对应的多个位置处混合键合。

根据本发明的第一方面的具体实施方案,其中所述存储器晶片是动态随机存储器晶片。

根据本发明的第一方面的实施方案,其中所述逻辑晶片设置有电源管脚,所述电源管脚与所述逻辑晶片的金属层的第二电源线连接。

根据本发明的第一方面的实施方案,其中所述多个第一电源线中的至少一个第一电源线被设置在所述存储器的顶部金属层中并且在位置上对应于与所述电源管脚都邻接的第二电源线。

根据本发明的第一方面的实施方案,其中所述混合键合的位置包括与所述电源管脚都邻接的第二电源线与所述电源管脚邻接的位置。

根据本发明的第一方面的优选实施方案,其中所述存储器晶片的第一电源线具有不小于10μm的等效宽度。在本发明的实施方案中,“等效宽度”指的是,由单个导线构成的电源线的宽度或者由多个导线并联构成的电源线的总宽度。

根据本发明的第一方面的实施方案,其中所述存储器晶片的多个第一电源线中的至少一个第一电源线由多个并联的导线构成。在本发明的一个实施例中,所述多个第一电源线中的至少一个第一电源线由4-5个2.5μm宽的导线并联组成。

根据本发明的第一方面的优选实施方案,其中所述存储器晶片的多个第一电源线具有的等效宽度不大于对应的第二电源线的等效宽度。更优选地,所述存储器晶片的多个第一电源线具有的等效宽度与对应的第二电源线的等效宽度相同。

根据本发明的第一方面的实施方案,其中所述多个第一电源线中的至少一个电源线设置在仅由所述存储器晶片的内部电源线作为所述存储器晶片的供电线路时电压降超过10%,优选地5%,电源电压的位置。

根据本发明的第二方面,提供了一种电子设备,其中所述电子设备包括根据上述第一方面所述的三维集成电路。

根据本发明的第三方面,提供了一种制造三维集成电路的方法,其中所述方法包括:

获取存储器晶片,所述存储器晶片的金属层设置有多个第一电源线,所述多个第一电源线用于给所述存储器晶片上的电路供电;

获取逻辑晶片,所述逻辑晶片的金属层设置有多个第二电源线,所述多个第二电源线用于为所述存储器晶片上的电路供电;以及

将所述多个第一电源线中的每一个第一电源线与所述多个第二电源线中的一个相应的第二电源线并联连接。

根据本发明的第三方面的具体实施方案,其中通过将所述存储晶片的顶部金属层的第一电源线与所述逻辑晶片的顶部金属层的第二电源线在一一对应的多个位置处混合键合,从而使所述存储晶片的顶部金属层与所述逻辑晶片的顶部金属层面对面地接合,以形成所述三维集成电路。

根据本发明的第三方面的实施方案,其中所述存储器晶片是动态随机存储器晶片。

根据本发明的第三方面的实施方案,其中所述逻辑晶片上设置有电源管脚,并且所述电源管脚与所述逻辑晶片的金属层的第二电源线连接。

根据本发明的第三方面的实施方案,其中所述多个第一电源线中的至少一个第一电源线被设置在所述存储器的顶部金属层中并且在位置上对应于与所述电源管脚都邻接的第二电源线。

根据本发明的第三方面的实施方案,其中所述混合键合的位置包括与所述电源管脚都邻接的第二电源线与所述电源管脚邻接的位置。

根据本发明的第三方面的实施方案,其中所述存储器晶片的第一电源线具有不小于10μm的等效宽度。

根据本发明的第三方面的实施方案,其中所述存储器晶片的多个第一电源线中的至少一个第一电源线由多个并联的导线构成。

根据本发明的第三方面的优选实施方案,其中所述存储器晶片的多个第一电源线具有的等效宽度不大于对应的第二电源线的等效宽度。更优选地,所述存储器晶片的多个第一电源线具有的等效宽度与对应的第二电源线的等效宽度相同。

根据本发明的第三方面的实施方案,其中所述多个第一电源线中的至少一个电源线设置在仅由所述存储器晶片的内部电源线作为所述存储器晶片的供电线路时电压降超过10%,优选地5%,电源电压的位置。

根据本发明的第四方面,提供了一种电子设备,其中所述电子设备包括根据上述第三方面所述的方法制造的三维集成电路。

下面将结合附图来对本发明的实施方案进行进一步详述。

图2例示了根据本发明的一个实施方案的三维集成电路的电源网络的示意图。图2中示出的三维集成电路包括存储器晶片210(诸如DRAM晶片)和逻辑晶片220。

在本文中,逻辑晶片指的是实现逻辑功能的晶片,存储器晶片是实现存储功能的晶片。

此外,为避免模糊本发明的主旨,图2中仅示出了存储器晶片210的顶部金属层和逻辑晶片220的顶部金属层,本领域技术人员应当知晓存储器晶片210和逻辑晶片220可以包括多层金属且还包括图2中未示出的一些构件。

在图2中,存储器晶片210的顶部金属层包括横向和纵向布置的多个电源线,其中虚线框214所在区域的电源线连接大量(诸如数百个并行信号)的高频(例如300-400MHz)电路。在如图1中示出的仅由存储器晶片的内部电源线作为存储器晶片的供电线路时,虚线框214内的两个纵向电源线与电源电压相比的电压降超过了电源电压的5%,甚至10%。因此,虚线框214内的两个纵向电源线被设置为较宽的导线,从而降低电源线的电阻来降低电压降。在本发明的实施方案中,单个宽电源线的等效宽度被设置为不小于10μm。应理解,这样的宽电源线可以由多个平行的导线构成,例如3-5个并联的2.5-5μm导线组成单个总宽度不小于10μm的宽电源线。

在图2中例示的实施例中,逻辑晶片220的顶部金属层具有与存储器晶片210的顶部金属层的宽电源线相同的宽电源线,在本文中,这指的是当逻辑晶片220的顶部金属层翻转且与存储器晶片210的顶部金属层扣合在一起时,逻辑晶片220的顶部金属层上具有的部分宽电源线与存储器晶片210的顶部金属层上的宽电源线完全重合,即,大小相等且位置相对应。应理解,在一些实施方案中,逻辑晶片220的顶部金属层上的至少一个宽电源线比存储器晶片210的顶部金属层上的对应宽电源线更宽。应理解,由于逻辑晶片220可以具有5-6层金属布线,除了与存储器晶片210的顶部金属层的宽电源线相同的宽电源线以外,逻辑晶片220的顶部金属层还可以设置多个横向和纵向的宽电源线。

在图2中,存储器晶片210和逻辑晶片220都在宽电源线的相对应的多个位置处设置有混合键合(Hybrid Bonding,HB)连接点212和222,当存储器晶片210的顶部金属层和逻辑晶片220的顶部金属层面对面扣合在一起时,两个晶片的金属层通过HB连接点的金属通孔垂直连接在一起。这将存储器晶片210的顶部金属层的电源线与逻辑晶片220的顶部金属层的电源线连接在一起,降低了存储器晶片210的顶部金属层的宽电源线的阻抗,改善了存储器晶片210在该处的电压降。另外,还应理解,存储器晶片210和逻辑晶片220都具有多层金属布线,其中存储器晶片210的非顶部金属层也可以包含电源线,该电源线可以通过通孔与存储器晶片210的顶部金属层并联,再通过混合键合与逻辑晶片220的顶部金属层的电源线并联。类似地,逻辑晶片220的非顶部金属层的电源线也可以通过通孔与逻辑晶片220的顶部金属层的电源线并联,再通过混合键合与存储器晶片210的顶部金属层并联。

与图1中示出的不同,图2中的存储器晶片210没有设置电源管脚,而逻辑晶片220设置有多个电源管脚221,电源管脚221与相邻的电源线223连接。由于供电电源通过电源线223引入到逻辑晶片220中,所以与多个电源管脚221都邻接的电源线223设置为宽导线。为了将供电电源最佳地引入到存储器晶片210,在电源线213和223与多个电源管脚221邻接的位置处设置混合键合连接点,使得电源从管脚221通过宽导线连接到存储器晶片210的电压降较大的位置。

图3例示了根据本发明的制造三维集成电路的方法的一个实施方案的流程图。

步骤301:获取存储器晶片210,存储器晶片210的金属层设置有用于给存储器晶片上的电路供电的多个电源线。

步骤302:获取逻辑晶片220,逻辑晶片220的金属层设置有用于为所述存储器晶片上的电路供电的多个电源线。

步骤303:将存储器晶片210的多个电源线中的每一个电源线与逻辑晶片220的多个电源线中的一个相应电源线并联连接。应理解,所述并联连接通过上面所描述的混合键合实现。

应注意,上述实施方案例示而非限制本发明,且本领域技术人员将能够在不背离所附权利要求的范围情况下设计许多替代实施方案。措辞“包括”或“包含”不排除权利要求中所列出的元件或步骤之外的元件或步骤的存在,“一”或“一个”不排除多个,且单个特征或其他单元可以实现权利要求中所记载的多个单元的功能。权利要求中的任何附图标记或标签均不应被解释为限制其范围。

- 三维集成电路、处理器、半导体芯片及三维集成电路的制造方法

- 三维集成电路、处理器、半导体芯片及三维集成电路的制造方法