全数字锁相环系统及全数字锁相环的频率校准方法

文献发布时间:2023-06-19 11:17:41

技术领域

本发明涉及电子信息技术领域,具体涉及一种全数字锁相环系统及全数字锁相环的频率校准方法。

背景技术

近十几年来,无线射频芯片市场火爆,加上CMOS制造工艺不断进步,数字技术在射频芯片中发挥着越来越大的作用。即越来越多的电路将由数字电路来实现。因为这样可以减小芯片的面积,缩小成本,还可以增强射频芯片的可配置性和工艺移植性。在整个射频芯片中,最早由数字电路代替原来的模拟电路的是收发机中的锁相环。通常,在射频应用中,对锁相环输出频率的精度,频率的范围要求比较高,这对由数字电路实现的锁相环是一个很大的挑战。

随着个人无线通信方式的不断拓展,新推出的移动电子终端,尤其是手机变得越来越强大,功能越来越丰富,其中Near-field-communication(以下简称NFC)功能的市场前景非常广泛。

NFC是一种近距离无线通信技术。使用了NFC技术的设备可以在彼此靠近的情况下进行数据交换,例如刷公交卡,给公交卡充值,商场的小额支付业务等,使人们的日常生活变得又安全又快捷。

NFC芯片工作时要求数字锁相环(Digital Phase-Locked Loop,简称DPLL)输出的频率信号与载波信号相位相同,频率相同,提供给收发机电路进行调制解调。所以数字锁相环工作时会跟踪载波频率信号,来输出一个系统要求的频率信号。但是在某些场合下,例如芯片发射大功率信号时,这个载波信号会被干扰,还有些场合下,会暂时无载波信号,这些情况都会导致数字锁相环不能很好的提供系统要求的频率信号。

因此,有必要提供改进的技术方案以克服现有技术中存在的以上技术问题。

发明内容

为了解决上述技术问题,本发明提供了一种全数字锁相环(All Digital Phase-Locked Loop,简称ADPLL)系统及全数字锁相环的频率校准方法,能够跟踪晶体频率,输出符合系统要求的频率信号,降低了在载波受干扰或者无载波时全数字锁相环输出的频率精度下降的风险,且成本较低,易实现。

根据本公开第一方面,提供了一种全数字锁相环系统,包括:全数字锁相环,包括数字振荡器,用于在校准阶段分别根据载波频率信号和晶体频率信号相应生成对应环路锁定时的第一控制码和第二控制码,以及在正常工作阶段根据晶体频率信号和第二频率放大倍数生成目标输出频率信号;校准单元,与全数字锁相环连接,用于根据第一控制码和第二控制码对第一频率放大倍数进行校准,生成第二频率放大倍数,其中,第一频率放大倍数为目标输出频率信号对应的频率值与载波频率信号对应的频率值的比值。

可选地,全数字锁相环系统还包括:第一分频器,与全数字锁相环连接,用于根据系统要求对目标输出频率信号进行分频,产生系统时钟信号。

可选地,全数字锁相环系统还包括:第一频率产生单元,用于提供载波频率信号;第二频率产生单元,用于提供晶体频率信号。

可选地,全数字锁相环系统还包括:选择单元,第一输入端与第一频率产生单元连接,第二输入端与第二频率产生单元连接,输出端与全数字锁相环连接,用于将载波频率信号和晶体频率信号分时的提供至全数字锁相环。

可选地,第二频率放大倍数的计算公式为:

可选地,目标输出频率信号对应的频率值等于晶体频率信号对应的频率值与第二频率放大倍数的乘积。

根据本公开第二方面,提供了一种全数字锁相环的频率校准方法,包括:基于载波频率信号获得第一控制码;基于晶体频率信号获得第二控制码;基于第一控制码和第二控制码对第一频率放大倍数进行校准,获得第二频率放大倍数;基于晶体频率信号和第二频率放大倍数获得目标输出频率信号,其中,第一频率放大倍数为目标输出频率信号对应的频率值与载波频率信号对应的频率值的比值。

可选地,基于晶体频率信号和第二频率放大倍数获得目标输出频率信号之后还包括:根据系统要求对目标输出频率信号进行分频,获得系统时钟信号。

可选地,目标输出频率信号对应的频率值等于晶体频率信号对应的频率值与第二频率放大倍数的乘积。

可选地,基于载波频率信号获得第一控制码包括:将载波频率信号输入至全数字锁相环,在全数字锁相环的环路锁定时获得第一控制码。

可选地,基于晶体频率信号获得第二控制码包括:将晶体频率信号输入至全数字锁相环,在全数字锁相环的环路锁定时获得第二控制码。

可选地,基于第一控制码和第二控制码对第一频率放大倍数进行校准,获得第二频率放大倍数包括:获得第一控制码和第二控制码的差值;基于差值获得全数字锁相环在接收晶体频率信号的情况下所产生的输出频率信号相对于目标输出频率信号的变化量;根据变化量对第一频率放大倍数进行校准,获得第二频率放大倍数。

本发明的有益效果是:本公开涉及一种全数字锁相环系统及全数字锁相环的频率校准方法,采用晶体频率信号代替载波频率信号作为全数字锁相环正常工作时的参考频率信号,由于晶体频率信号本身具有的高精度、高稳定性等的特征,因此能够降低在载波频率信号(简称载波)受干扰或者无载波频率信号时全数字锁相环输出的频率精度下降的风险,并增强全数字锁相环系统的抗干扰能力。同时,采用校准单元进行校准,可以提高在采用晶体频率信号作为参考频率信号时全数字锁相环产生的输出频率信号的准确性。

另一方面,本公开中涉及的全数字锁相环系统的结构简单,成本较低,且易实现。

应当说明的是,以上的一般描述和后文的细节描述仅是示例性和解释性的,并不能限制本发明。

附图说明

通过以下参照附图对本发明实施例的描述,本发明的上述以及其他目的、特征和优点将更为清楚。

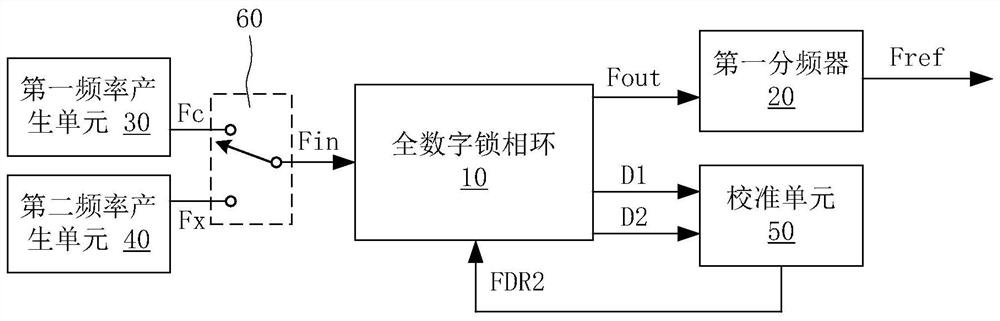

图1示出根据本公开实施例提供的全数字锁相环系统的结构框图;

图2示出根据本公开实施例提供的全数字锁相环系统的结构示意图;

图3示出根据本公开实施例提供的全数字锁相环的结构示意图;

图4示出根据本公开实施例提供的全数字锁相环的频率校准方法的流程框图。

具体实施方式

为了便于理解本发明,下面将参照相关附图对本发明进行更全面的描述。附图中给出了本发明的较佳实施例。但是,本发明可以通过不同的形式来实现,并不限于本文所描述的实施例。相反的,提供这些实施例的目的是使对本发明的公开内容的理解更加透彻全面。

除非另有定义,本文所使用的所有的技术和科学术语与属于本发明的技术领域的技术人员通常理解的含义相同。本文在本发明的说明书中所使用的术语只是为了描述具体的实施例的目的,不是旨在于限制本发明。

下面,参照附图对本发明进行详细说明。

参考图1,图1示出根据本公开实施例提供的全数字锁相环系统的结构框图。

如图1所示,本公开中,全数字锁相环系统包括有全数字锁相环10和第一分频器20。

其中,全数字锁相环10的输入端接收有参考频率信号Fin,该参考频率信号Fin经全数字锁相环10进行环路锁定之后,被放大可设定的放大倍数(本文中,记为FDR),即可得到一个具有较高频率的输出频率信号Fout,并于全数字锁相环10的输出端输出。此时,有fout=fin*FDR...................(1)。其中,fin为参考频率信号Fin的频率值,fout为输出频率信号Fout的频率值。

第一分频器20与全数字锁相环10的输出端连接,用于根据系统的要求,对全数字锁相环10输出的输出频率信号Fout进行分频,以对应产生系统时钟信号Fref。其中,在对输出频率信号Fout进行分频时,第一分频器20为根据不同的系统要求设置不同的第一分频因子(本文中,记为N,且N为正数),进而根据相应的第一分频因子N对输出频率信号Fout进行分频,以便于在同一输出频率信号Fout的基础上产生不同的系统时钟信号Fref。此时有fref=fout/N...............(2)。其中,fref为系统时钟信号Fref的频率值。

本公开中,可以在全数字锁相环系统中设置若干的第一分频器20,通过该若干的第一分频器20同时对输出频率信号Fout进行分频以同时产生若干的不同系统时钟信号Fref,进而可以支持不同需求的若干系统的同时运行。

应当理解的是,本公开中全数字锁相环10可采用现有的全数字锁相环结构进行构建,故其内部结构可看做是已知的,本文中也将不对全数字锁相环10的内部结构做详细介绍,仅为参考图3对全数字锁相环10的内部结构做一些大体说明,以方便对本公开技术方案的理解。

图3示出根据本公开实施例提供的全数字锁相环的结构示意图,如图3所示,本公开实施例中,全数字锁相环10包括:鉴相器11、时间数字转换器12、数字环路滤波器13、数字振荡器14和第二分频器15。

其中,鉴相器11的第一输入端接收参考频率信号Fin,鉴相器11的第二输入端接收反馈频率信号Fdiv,鉴相器11的输出端输出表征参考频率信号Fin与反馈频率信号Fdiv之间的相位差的指示信号。

时间数字转换器12与鉴相器11连接,用于根据鉴相器11输出的指示信号产生对应的数字信号。

数字环路滤波器13与时间数字转换器12连接,用于对时间数字转换器12输出的数字信号进行滤波,以得到控制数字振荡器14的控制码。

数字振荡器14与数字环路滤波器13连接,用于接收数字环路滤波器13输出的控制码,并在控制码的控制下生成振荡信号作为全数字锁相环的输出频率信号Fout。

第二分频器15分别与数字振荡器14和鉴相器11连接,用于根据第二分频因子(本文中,记为M,且M为正数)对数字振荡器14输出的输出频率信号Fout分频后产生反馈频率信号Fdiv。

可以理解的是,在全数字锁相环中,将输出频率信号Fout经M分频后反馈至鉴相器11的输入端作为反馈频率信号Fdiv,则此时全数字锁相环10的输出频率信号Fout就相当于是相对于输入的参考频率信号Fin的M倍的倍频输出。因此,全数字锁相环中对应第二分频因子M的倍频倍数即对应为本文中的频率放大倍数。相应的,通过调整第二分频器15的第二分频因子M,即可对应实现对全数字锁相环系统的频率放大倍数的调节。

进一步地,本公开中,全数字锁相环系统中的第一分频器20和第二分频器15均可为能够进行小数倍分频的小数分频器。

可以理解的是,现有的全数字锁相环系统为采用载波频率信号作为参考频率信号Fin来输出一个系统要求的频率信号,但由于载波频率信号在某些场合下容易受到干扰,进而会影响输出的系统时钟信号Fref的精度和准确性。因此,本公开的技术方案中,为采用具有高精度、高稳定性等特征的晶体频率信号代替载波频率信号作为参考频率信号Fin,来输出系统要求的频率信号。但是,由于晶体频率信号和载波频率信号的频率大小不同,故需要一种频率校准方法,来让全数字锁相环系统在采用具有固定频率的晶体频率信号作为参考频率信号Fin时得到的系统时钟信号的频率和相位,能够与采用载波频率信号作为参考频率信号Fin时得到的系统时钟信号的频率和相位无限接近。

参考图2,图2进一步的示出了根据本公开实施例提供的全数字锁相环系统的结构示意图。如图2所示,在图1的基础上,本公开中的全数字锁相环系统还包括有校准单元50,该校准单元50能够配合全数字锁相环10以实现全数字锁相环10在校准阶段的校准功能。

相应的,在全数字锁相环10的校准阶段,全数字锁相环10为分别根据载波频率信号Fc和晶体频率信号Fx相应生成对应环路锁定时的第一控制码D1和第二控制码D2。具体的,结合图3,当全数字锁相环10接收载波频率信号Fc作为参考频率信号Fin进行环路的锁定时,锁定之后数字振荡器14所接收的控制码即为第一控制码D1;而当全数字锁相环10接收晶体频率信号Fx作为参考频率信号Fin进行环路的锁定时,锁定之后数字振荡器14所接收的控制码即为第二控制码D2。

校准单元50与全数字锁相环10连接,用于根据第一控制码D1和第二控制码D2对第一频率放大倍数(本文中,即为FDR1)进行校准,生成第二频率放大倍数(本文中,即为FDR2)。

进一步地,在全数字锁相环10的正常工作阶段,全数字锁相环10为根据晶体频率信号Fx和第二频率放大倍数FDR2生成输出频率信号Fout,此时的输出频率信号Fout即为目标输出频率信号。基于公式(1),此时的第一频率放大倍数FDR1为目标输出频率信号对应的频率值与载波频率信号Fc对应的频率值的比值,即FDR1=fout/fc,转换后可得:fout=fc*FDR1..............(3)。其中,fc表为载波频率信号Fc对应的频率值。

可以理解的是,结合图3,前述第一频率放大倍数FDR1和第二频率放大倍数FDR2均对应为全数字锁相环10中第二分频器15的第二分频因子M,因此,校准单元50也可理解为根据第一控制码D1和第二控制码D2调整全数字锁相环10中第二分频器15的第二分频因子M,进而使得全数字锁相环10能够基于调整后的第二分频因子M对全数字锁相环10接收的晶体频率信号Fx进行倍频输出,之后经第一分频器20分频后获得系统所需的系统时钟信号Fref,最终可将该系统时钟信号Fref发送给相应的收发机做调制解调使用。

本公开中,频率校准的具体原理如下:

全数字锁相环10的基本原理为输入频率(对应前述的参考频率信号Fin的频率)乘以放大倍数FDR等于输出频率(对应前述的输出频率信号Fout的频率),即公式(1),进而当放大倍数不变时输入频率与输出频率成正比。进而可轻易得出的是,若想保证在校准前后全数字锁相环10输出的输出频率信号Fout的频率无限接近,只要让输入频率与放大倍数FDR成反比即可。所以在进行频率校准时,首先应获得不同的输入频率下输出频率变化的百分比(本文中,记为ΔFout),然后把所获得的百分比修正到放大倍数FDR上即可。

其中,该输出频率变化的百分比ΔFout的计算公式为:

其中,FDR1为第一频率放大倍数(校准前的放大倍数FDR),D1为第一控制码,D2为第二控制码,K

且进一步地,基于该输出频率变化的百分比ΔFout获得第二频率放大倍数FDR2的计算公式为:FDR2=FDR1*(1+ΔFout)..............(5)。而联立公式(4)和(5)即可得:

基于校准后所获得的第二频率放大倍数FDR2,可以使得全数字锁相环10一直选择晶体频率信号Fx作为输入的参考频率信号Fin,并在整个的通信期间均能够处在跟踪晶体频率信号Fx的闭环工作状态下,不易受外界的干扰,避免了跟踪载波频率信号Fc时存在的潜在风险。

示例性的,结合公式(4)、公式(5)和公式(6)可知,当第一控制码D1大于第二控制码D2时,输出频率变化的百分比ΔFout为正数,(1+ΔFout)大于1,使得第二频率放大倍数FDR2大于第一频率放大倍数FDR1;当第一控制码D1小于第二控制码D2时,输出频率变化的百分比ΔFout为负数,(1+ΔFout)小于1,使得第二频率放大倍数FDR2小于第一频率放大倍数FDR1。最终均可使得全数字锁相环10输出的输出频率信号Fout在校准前与校准后能够近似相等。

进一步地,本公开实施例中,全数字锁相环系统还包括:第一频率产生单元30和第二频率产生单元40。其中,第一频率产生单元30用于提供载波频率信号Fc,第二频率产生单元40用于提供晶体频率信号Fx。

进一步地,本公开实施例中,全数字锁相环系统还包括:选择单元60。该选择单元60的第一输入端与第一频率产生单元30连接,选择单元60的第二输入端与第二频率产生单元40连接,选择单元60的输出端与全数字锁相环10连接。该选择单元60用于根据相应的控制信号将由第一频率产生单元30提供的载波频率信号Fc和由第二频率产生单元40提供的晶体频率信号Fx分时的提供至全数字锁相环10。

可选地,该选择单元60如为二选一选择开关。

进一步地,参考图4,图4示出根据本公开实施例提供的全数字锁相环的频率校准方法的流程框图。

如图4所示,本公开实施例中,全数字锁相环的频率校准方法包括执行步骤S1、步骤S2、步骤S3和步骤S4。

具体的,在步骤S1中,基于载波频率信号获得第一控制码。

本实施例中,基于载波频率信号获得第一控制码进一步包括:将载波频率信号输入至全数字锁相环,在全数字锁相环的环路锁定时获得第一控制码。

参考图2和图3,示例性的,控制选择单元60连通第一频率产生单元30的输出端和全数字锁相环10的输入端,将载波频率信号Fc作为参考频率信号Fin输入至全数字锁相环10。全数字锁相环10跟踪该载波频率信号Fc进行环路锁定,在环路锁定之后,记录此时数字振荡器14所接收的控制码,该控制码即为第一控制码D1。

在步骤S2中,基于晶体频率信号获得第二控制码。

本实施例中,基于晶体频率信号获得第二控制码进一步包括:将晶体频率信号输入至全数字锁相环,在全数字锁相环的环路锁定时获得第二控制码。

参考图2和图3,示例性的,控制选择单元60连通第二频率产生单元40的输出端和全数字锁相环10的输入端,将晶体频率信号Fx作为参考频率信号Fin输入至全数字锁相环10。全数字锁相环10跟踪该晶体频率信号Fx进行环路锁定,在环路锁定之后,记录此时数字振荡器14所接收的控制码,该控制码即为第二控制码D2。

在步骤S3中,基于第一控制码和第二控制码对第一频率放大倍数进行校准,获得第二频率放大倍数。

本实施例中,基于第一控制码和第二控制码对第一频率放大倍数进行校准,获得第二频率放大倍数包括:获得第一控制码和第二控制码的差值;基于差值获得全数字锁相环在接收晶体频率信号的情况下所产生的输出频率信号相对于目标输出频率信号的变化量;根据变化量对第一频率放大倍数进行校准,获得第二频率放大倍数。

参考图2,示例性的,在获得第一控制码D1和第二控制码D2后,将第一控制码D1和第二控制码D2送入至校准单元40,由校准单元40按照前述公式(4)、公式(5)和公式(6)进行计算,获得新的频率放大倍数即第二频率放大倍数FDR2。以及本实施例中,为将输出频率变化的百分比作为变化量进行的计算与分析。

进一步地,第一频率放大倍数FDR1为目标输出频率信号对应的频率值与载波频率信号Fc对应的频率值的比值,即FDR1=fout/fc。

在步骤S4中,基于晶体频率信号和第二频率放大倍数获得目标输出频率信号。

参考图2和图3,在获得第二频率放大倍数FDR2后,将该第二频率放大倍数FDR2写入至全数字锁相环10,以调整全数字锁相环10中第二分频器15的第二分频因子M。之后,仅将晶体频率信号Fx作为参考频率信号Fin输入至全数字锁相环10,由全数字锁相环10基于调整后的第二分频器15的第二分频因子M跟踪该晶体频率信号Fx并进行环路锁定。在环路锁定之后,全数字锁相环10中数字振荡器14所输出的输出频率信号Fout即为目标输出频率信号。

进一步地,在基于晶体频率信号和第二频率放大倍数获得目标输出频率信号之后还包括:根据系统要求对目标输出频率信号进行分频,获得系统时钟信号。也即将获得的目标输出频率信号输入至第一分频器20,由第一分频器20将目标输出频率信号按照预先设置的第一分频因子N进行分频,获得系统时钟信号Fref。

基于前述描述,本公开中的全数字锁相环系统及全数字锁相环的频率校准方法简单、易实现,可以使用于手机的NFC芯片应用中。同时,还可以应用于如CW雷达系统,以及可受益于能够跟踪可变频率参考信号的应用中,例如调谐器,该调谐器可应用在如卫星无线电系统、电视、车辆智能交通系统(ITS)、以太网收发器、蓝牙和蓝牙低功耗(LE)应用等更多应用中。

应当说明的是,在本文中,所含术语“包括”、“包含”或者其任何其他变体意在涵盖非排他性的包含,从而使得包括一系列要素的过程、方法、物品或者设备不仅包括那些要素,而且还包括没有明确列出的其他要素,或者是还包括为这种过程、方法、物品或者设备所固有的要素。在没有更多限制的情况下,由语句“包括一个……”限定的要素,并不排除在包括所述要素的过程、方法、物品或者设备中还存在另外的相同要素。

最后应说明的是:显然,上述实施例仅仅是为清楚地说明本发明所作的举例,而并非对实施方式的限定。对于所属领域的普通技术人员来说,在上述说明的基础上还可以做出其它不同形式的变化或变动。这里无需也无法对所有的实施方式予以穷举。而由此所引申出的显而易见的变化或变动仍处于本发明的保护范围之中。

- 全数字锁相环系统及全数字锁相环的频率校准方法

- 全数字锁相环、环路频宽校准方法与环路增益校准方法