静电保护结构和静电保护电路

文献发布时间:2023-06-19 11:21:00

技术领域

本发明实施例涉及半导体制造领域,尤其涉及一种静电保护结构和静电保护电路。

背景技术

在集成电路(integrated circuits,IC),静电放电(electrostatic discharge,ESD)对芯片的可靠性影响不容忽视,尤其在深亚微米、纳米技术普遍应用的当今,外部环境、人体、机械、辐射场等静电放电对IC破坏性的影响更加显著,业界在IC的设计与制造过程中对ESD的防护做了大量的研究与实践。

在集成电路芯片的制作和应用中,随着超大规模集成电路工艺技术的不断提高,目前的CMOS集成电路制作技术已经进入深亚微米、纳米阶段,MOS器件的尺寸不断缩小,栅氧化层的厚度越来越薄,MOS器件耐压能力不断下降,静电放电对集成电路的危害变得越来越显著。因此,对集成电路进行ESD保护也变得尤为重要。

在系统级芯片(System on Chip,SOC)的设计中,通常有输入信号电压高于电源(VDD)电压的情况,此时需要采用耐压容忍电路进行信号的传输。

然而,设计有耐压容忍电路的芯片,接收耐压容忍电路所传输信号的内部功能性电路存在被ESD而损毁的问题。

发明内容

本发明实施例解决的问题是提供一种静电保护结构和静电保护电路,优化静电保护效果。

为解决上述问题,本发明提供一种静电保护结构,用于对耐压容忍电路提供静电保护,所述耐压容忍电路包括:电源电压端,用于加载电源电压;外接输入端,用于接收外部电压信号;所述电源电压端和外接输入端之间连接有第一晶体管和第二晶体管,所述第一晶体管和第二晶体管的掺杂区形成在衬底的同一阱区中;所述静电保护结构包括:第一静电释放响应电路,连接于电源电压端和阱区之间,用于在电源电压端向外接输入端释放静电时,触发电源电压和阱区之间的静电释放通路;第二静电释放响应电路,连接于外接输入端和阱区之间,用于在外接输入端向电源电压端释放静电时,触发外接输入端和阱区之间的静电释放通路。

可选地,所述第一晶体管为第一P型晶体管,所述第二晶体管为第二P型晶体管,所述第一P型晶体管和第二P型晶体管共漏极连接;所述第一P晶体管的源极为所述电源电压端,所述第二P型晶体管的源极为所述外接输入端;所述阱区为N型阱区。

可选地,所述第一静电释放响应电路包括:电容器,与电源电压端相连,用于在电源电压端向外接输入端释放静电时进行充电;导通开关,与所述电容器相连,包括控制端、第一连接端和第二连接端,用于在控制端被触发时实现第一连接端和第二连接端的电连接,所述控制端与所述电容器相连,所述第一连接端连接地端,所述第二连接端与所述阱区相连。

可选地,所述导通开关为第一N型晶体管,所述第一N型晶体管的栅极与所述电容器相连,第一N型晶体管的源极与所述N型阱区相连,第一N型晶体管的漏极与所述地端相连。

可选地,所述第一N型晶体管的栅极与所述漏极之间还连接有一电阻器。

可选地,所述第二静电释放响应电路包括:多个串联的单向开关。

可选地,所述单向开关为二极管。

可选地,所述耐压容忍电路还包括:选择电路,用于选择电源电压端和外接输入端的高电压加载至所述阱区,所述选择电路包括:与所述电源电压端相连的第一输入端,与所述外接输入端相连的第二输入端,以及与所述阱区相连的输出端。

可选地,所述选择电路包括:第三P型晶体管,所述第三P型晶体管的栅极与所述电源电压端相连,所述第三P型晶体管的源极与所述外接输入端相连,所述第三P型晶体管的漏极与所述N型阱区相连;以及第四P型晶体管,所述第四P型晶体管的栅极与所述外接输入端相连,所述第四P型晶体管的源极与电源电压端相连,所述第四P型晶体管的漏极与N型阱区相连。

可选地,所述耐压容忍电路还包括:地端静电释放电路,连接于所述外接输入端和地端之间。

可选地,所述地端静电释放电路包括:串联连接的第二N型晶体管和第三N型晶体管。

相应地,本发明还提供一种静电保护电路,包括:耐压容忍电路,用于实现外部电压信号的传输,包括:电源电压单元,用于提供电源电压;外接输入焊垫,用于接收外部电压信号;所述电源电压单元与外接输入焊垫之间连接有第一晶体管和第二晶体管,所述第一晶体管和第二晶体管的掺杂区形成在衬底的阱区中;所述耐压容忍电路还包括:本发明提供的所述静电保护结构;功能电路,连接于所述电源电压单元和地端之间。

可选地,还包括:电源箝位电路,连接于所述电源电压单元和地端之间。

与现有技术相比,本发明实施例的技术方案具有以下优点:

本发明实施例中的静电保护结构包括:第一静电释放响应电路和第二静电释放响应电路,第一静电释放响应电路连接于电源电压端和阱区之间,在电源电压端积累有静电电荷时,能触发使电源电压和阱区之间形成电流通路,用于进行静电释放;类似的,所述第二静电释放响应电路连接于外接输入端和阱区之间,在外接输入端积累有静电电荷时,能触发外接输入端和阱区之间形成电流通路,用于进行静电释放。因此,本发明实施例的静电保护结构能够及时释放静电荷,避免衬底中寄生PNP因积累较多电荷而造成电压过大而开启,从而可以避免PMOS泄放ESD电流的问题,进而优化了静电保护效果、保护了其他电路的安全性。

附图说明

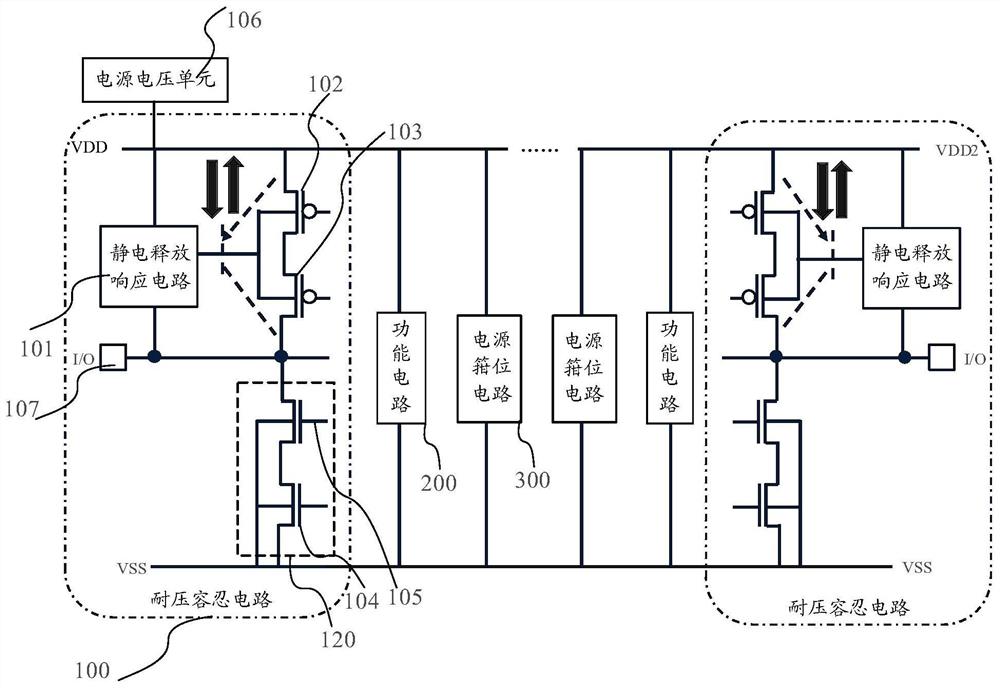

图1为一种静电保护电路的示意图;

图2为图1所示静电保护电路的半导体结构侧视图;

图3为本发明实施例静电保护电路的电路示意图;

图4为本发明实施例静电保护结构的侧面示意图;

图5为本发明静电保护电路的电流-电压测试曲线图。

具体实施方式

由背景技术可知,现有技术设计有耐压容忍电路的芯片中,内部电路存在被ESD而损毁的问题,下面结合常规设计对产生ESD的原因进行分析。

参考图1和图2,分别示意除了现有技术电路示意图和半导体结构示意图。现有技术中系统级芯片包括:所述耐压容忍电路10,内部电路20和电源箝位电路,其中,所述耐压容忍电路10用于实现外接信号的传输,所述耐压容忍电路10中包括两个串联的PMOS12、13,所述PMOS的掺杂区形成在衬底的N型阱区中。

由于外接信号的电压有存在超过电源电压的可能,所述耐压容忍电路10还设置了选择电路11,连接于所述电源电压单元VDD1和外接信号输入焊盘I/O之间。所述选择电路11为一高电平选择电路,用于选择电源电压和外接信号电压中比较高的加载至所述N型阱区中,以避免外接信号的电压超过电源电压时产生电流向电源总线倒灌的问题。

这种结构避免了外接信号输入焊盘I/O向电源电压单元VDD1的电流倒灌,相应地,在产生静电积累要进行静电释放时,也阻断了外接信号输入焊盘I/O向电源电压单元VDD1的静电释放通路。

继续参考图2,为图1所示椭圆虚线框对应的半导体结构的侧面剖视图。本实施例中,位于电源电压单元VDD1和外接信号输入焊盘I/O之间的两个相连的PMOS管掺杂区形成于N型阱区中,并产生了寄生的横向PNP三极管,寄生横向pnp三极管因为外接信号输入焊盘I/O积累大量静电荷而造成电压过大而开启,导致PMOS泄放ESD电流。

在这个过程中,如果PMOS鲁棒性不够容易造成损毁,或者,容易造成电源电压单元VDD1和外接信号输入焊盘I/O之间其他电路(例如内部电路20或者电源箝位电路30)的雪崩击穿。

为了解决所述技术问题,本发明提供一种静电保护结构,用于对耐压容忍电路提供静电保护,所述耐压容忍电路包括:电源电压端,用于加载电源电压;外接输入端,用于接收外部电压信号;所述电源电压端和外接输入端之间连接有第一晶体管和第二晶体管,所述第一晶体管和第二晶体管的掺杂区形成在衬底的同一阱区中;所述静电保护结构包括:第一静电释放响应电路,连接于电源电压端和阱区之间,用于在电源电压端向外接输入端释放静电时,触发电源电压和阱区之间的静电释放通路;第二静电释放响应电路,连接于外接输入端和阱区之间,用于在外接输入端向电源电压端释放静电时,触发外接输入端和阱区之间的静电释放通路。

本发明实施例中的静电保护结构包括:第一静电释放响应电路和第二静电释放响应电路,第一静电释放响应电路连接于电源电压端和阱区之间,在电源电压端积累有静电电荷时,能触发使电源电压和阱区之间形成电流通路,用于进行静电释放;类似的,所述第二静电释放响应电路连接于外接输入端和阱区之间,在外接输入端积累有静电电荷时,能触发外接输入端和阱区之间形成电流通路,用于进行静电释放。因此,本发明实施例的静电保护结构能够及时释放静电荷,避免衬底中寄生PNP因积累较多电荷而造成电压过大而开启,从而可以避免PMOS泄放ESD电流的问题,进而优化了静电保护效果、保护了其他电路的安全性。

参考图3,示出了本发明实施例静电保护电路的示意图。所述静电保护电路包括:耐压容忍电路100、功能电路200和电源箝位电路300。

功能电路200,为用于实现特定功能的内部电路。比如,所述功能电路200为存储器电路等。所述功能电路200一端与耐压容忍电路100相连,另一端与地端相连。

耐压容忍电路100,用于实现外部电压信号的传输。

具体地,所述耐压容忍电路100包括:外接输入焊垫107,用于接收外部电压信号。外接输入焊垫107为一金属连接端子,用于在静电保护电路工作时,提供静电保护电路与外接电路的连接端。

电源电压单元106,用于提供电源电压VDD。更具体地说,所述电源电压单元106向所述功能电路200提供电源电压VDD。

所述电源电压单元106与外接输入焊垫107之间还连接有第一晶体管102和第二晶体管103。

结合参考图4所示晶体管的侧面示意图,所述第一晶体管102和第二晶体管103的掺杂区形成在衬底110的同一阱区111中。

具体地,在本实施例中,所述第一晶体管102为第一P型晶体管,所述第二晶体管103为第二P型晶体管,所述第一P型晶体管和第二P型晶体管为耐压容忍电路中P型晶体管的部分。

本实施例中,所述第一P型晶体管102和第二P型晶体管103共漏极连接;所述第一P晶体管102的源极为所述电源电压端,所述第二P型晶体管的源极为所述外接输入端。在其他实施例中,所述第一P型晶体管102和第二P型晶体管103还可以有单独的漏极,且单独的漏极通过外部连接结构实现电连接。

本实施例中,所述衬底110为P型衬底,所述阱区111为N型阱区。所述第一P型晶体管和第二P型晶体管的共漏极掺杂区形成于所述N型阱区中,从而在所述衬底110中形成寄生的PNP三极管,且所述N型阱区具有寄生电容R-NW。

本发明实施例在所述电源电压端VDD和所述外接输入端107之间设置静电释放响应电路107,在所述电源电压端VDD和所述外接输入端107之间形成静电释放通路。

相应的地,本发明实施例还提供一种静电保护结构,结合参考图4所示本发明一实施例静电保护结构的半导体结构图,所述静电释放响应电路107包括:

第一静电释放响应电路1011,接于电源电压端和阱区111之间,用于在电源电压端向外接输入端释放静电时,触发电源电压和阱区之间的静电释放通路。

具体地,所述第一静电释放响应电路1011包括:

电容器1021,与电源电压端VDD相连,用于在电源电压端VDD向外接输入端I/O释放静电时进行充电。

导通开关1023,与所述电容器1021相连,包括控制端、第一连接端和第二连接端,用于在控制端被触发时实现第一连接端和第二连接端的电连接,所述控制端与所述电容器1021相连,所述第一连接端连接地端,所述第二连接端与所述阱区相连。

具体地,本实施例中,所述导通开关1023为第一N型晶体管,所述第一N型晶体管的栅极为所述控制端,与所述电容器1021相连;所述第一N型晶体管的漏极为所述第一连接端,与所述地端相连;所述第一N型晶体管的源极为所述第二连接端,与所述N型阱区相连。

在实际应用中,当电源电压端VDD需要进行静电释放时,向所述电容器1021进行充电,当充电至所述第一N型晶体管的开启电压时,使所述第一N型晶体管的源极和漏极相连,进而使所述N型阱区连接至地端VSS。在所述衬底中形成的寄生pnp(虚线所示)可以实现导通,从而实现静电释放。

如图4所示,所述第一N型晶体管的栅极与所述漏极之间还连接有一电阻器102,可以起到分压的作用,避免第一N型晶体管的栅极直接与地端VSS相连。

所述静电释放响应电路107还包括:第二静电释放响应电路1012,连接于外接输入端I/O和阱区111之间,用于在外接输入端I/O向电源电压端释放静电时,触发外接输入端I/O和阱区111之间的静电释放通路。

具体地,所述第二静电释放响应电路1012包括:多个串联的单向开关1024。所述多个串联的单向开关1024连接于所述外接输入端I/O和阱区111之间,用于在外接输入端I/O积累较多静电电荷需要进行释放时,触发所述单向开关导通,使静电释放在所述外接输入端I/O和阱区111之间形成释放通路。

本实施例中,所述单向开关1024为二极管,为常用的单向导通开关。实际工艺中可以根据设计要求选择二极管的数量。

结合参考图3,本实施例的静电保护结构中,所述耐压容忍电路还包括:地端静电释放电路105,连接于所述外接输入端I/O和地端VSS之间,用于在外接输入端I/O和地端VSS之间实现静电释放通路。

本实施例中,所述外接输入端I/O和电源电压端VDD之间,所述外接输入端I/O地端VSS之间,均可形成静电释放通路,为静电释放提供了多个选择,从而保证了ESD防护效果,进而减小内部的功能电路200被ESD损毁的几率,提高了功能电路200的安全性。

具体地,在本实施例中,所述地端静电释放电路105包括:串联连接的第二N型晶体管104和第三N型晶体管105。

如图3所示,本发明实施例中,所述耐压容忍电路还包括:选择电路1013,为高电平选择电路,用于选择电源电压端VDD和外接输入端107的高电压加载至所述阱区,所述选择电路包括:与所述电源电压端相连的第一输入端,与所述外接输入端相连的第二输入端,以及与所述阱区相连的输出端。

本实施例通过所述高电平选择电路,选择电源电压端VDD和外接输入端107中电平较高的输出至所述阱区。

具体地,本实施例中,所述选择电路1013包括:第三P型晶体管1032,所述第三P型晶体管1032的栅极与所述电源电压端VDD相连,所述第三P型晶体管1032的源极与所述外接输入端I/O相连,所述第三P型晶体管1032的漏极与所述N型阱区111相连。

所述选择电路1013还包括:第四P型晶体管1031,所述第四P型晶体管1031的栅极与所述外接输入端I/O相连,所述第四P型晶体管1031的源极与电源电压端VDD相连,所述第四P型晶体管1031的漏极与N型阱区111相连。

在其他实施例中,还可以采用其他的结构的高电平选择电路。

本实施例静电保护电路还包括:电源箝位电路300,连接于所述电源电压单元106和地端VSS之间,用于使加载在功能电路200上的为一较为稳定的预设电平。

在其他实施例中,所述静电保护电路还可以不设置所述电源箝位电路。

参考图5,示意出了本发明实施例静电保护电路的电流-电压测试曲线图。其中横坐标为电压,单位为伏特,纵坐标为电流,单位为安培。图中实线为第一静电释放响应电路的电压-电流曲线图,可以看出在电源电压端VDD向外接输入端I/O方向的ESD电流释放能力,虚线为第二静电释放响应电路的电压-电流曲线图,可以看出在外接输入端I/O向电源电压端VDD方向的ESD电流释放能力。

通过虚线可以看出,当达到第二静电释放响应电路中单向开关的阈值电压2V时,第二静电释放响应电路的电流快速增加,从而实现静电释放。

相应地,通过实线可以看出,当达到第一静电释放响应电路中第一N型晶体管的开启电压时,第一静电释放电路的电流快速增加,具有较好的静电释放效果。

实际应用中,可以通过对第一N型晶体管和单向开关的设置,来减小静电释放的开启电压,进一步优化静电保护的效果。

本发明实施例披露如上,但本发明实施例并非限定于此。任何本领域技术人员,在不脱离本发明实施例的精神和范围内,均可作各种更动与修改,因此本发明实施例的保护范围应当以权利要求所限定的范围为准。