堆叠式封装结构及封装方法

文献发布时间:2023-06-19 11:21:00

技术领域

本发明涉及封装技术领域,尤其涉及一种堆叠式封装结构及封装方法。

背景技术

作为目前封装高密集成的主要方式,堆叠封装得到越来越多的重视,芯片的堆叠是提高电子封装高密化的主要途径之一,堆叠封装技术已经在业界得到比较广泛的开发和应用。

现有技术的堆叠封装结构中,重布线层等金属层设于两层有机介电钝化层之间,即重布线层覆盖在第一介电层上方,第二介电层覆盖在重布线层上方,形成三层堆叠封装结构。

在热循环制程和可靠性过程中,重布线层与两层介电层受到温差影响后,易受热膨胀遇冷收缩;而介电层与重布线层两种结构材料的热膨胀系数不同,重布线层与两层介电层两种结构材料的膨胀或收缩的程度不同,在两种结构材料的交界处会受到应力拉扯,因而三层堆叠封装结构的交界处容易产生分层或者裂纹的情况,即在重布线层、第一介电层和第二介电层三者交界处易发生分层或裂纹的情况。

发明内容

本发明的目的在于提供一种堆叠式封装结构及封装方法,以解决目前堆叠式封装结构在热循环制程和可靠性过程中重布线层与两层介电层由于结构材料的膨胀或收缩的程度不同导致的三层堆叠结构交界处易产生分层或者裂纹的问题。

为了实现上述发明目的之一,本发明一实施方式提供一种堆叠式封装结构,包括芯片,第一介电层设于所述芯片的主动表面上;重布线层设于所述第一介电层上,所述重布线层开设有第一金属层开口,所述第一金属层开口裸露至少部分所述第一介电层;第二介电层设于所述重布线层上;所述第一介电层的表面还开设有第一凹槽,所述第一凹槽与所述第一金属层开口相互连通,所述第二介电层经由所述第一金属层开口及所述第一凹槽与所述第一介电层连接。

作为本发明一实施方式的进一步改进,所述第一凹槽的宽度不小于所述第一金属层开口的宽度,且所述第一凹槽的深度超过0.3um。

作为本发明一实施方式的进一步改进,所述第一凹槽的宽度等于所述第一金属层开口的宽度。

作为本发明一实施方式的进一步改进,所述第二介电层还开设有第二介电层开口,所述第二介电层开口裸露至少部分所述重布线层;所述封装结构还包括锡球,所述锡球通过所述第二介电层开口与所述重布线层电性连接。

作为本发明一实施方式的进一步改进,所述封装结构还包括设于所述锡球与所述重布线层两者之间的球下金属层,所述球下金属层经由所述第二介电层开口将所述锡球与所述重布线层电性连接,所述球下金属层的部分侧面与所述重布线层的表面围设形成有第二金属层开口;所述第二介电层的表面还开设有第二凹槽。

作为本发明一实施方式的进一步改进,所述第二凹槽的底面与所述第二金属层开口的上侧面高度相差超过0.3um。

作为本发明一实施方式的进一步改进,所述第二凹槽与所述第二金属层开口连通或至少部分重叠。

作为本发明一实施方式的进一步改进,所述封装结构还包括设于所述第二介电层上方的第三介电层,所述第三介电层包封所述球下金属层。

本发明一实施方式还提供一种堆叠式封装方法,包括步骤:将第一介电层设置于晶圆或芯片的主动表面上;将重布线层设置于所述第一介电层上,并在所述重布线层上开设第一金属层开口,使得所述第一金属层开口裸露至少部分所述第一介电层;在所述第一介电层的表面开设第一凹槽,使得所述第一凹槽与所述第一金属层开口相互连通;将第二介电层设置于所述重布线层上,使得所述第二介电层经由所述第一金属层开口及所述第一凹槽与所述第一介电层连接。

作为本发明一实施方式的进一步改进,所述方法还包括:所述第一凹槽的宽度不小于所述第一金属层开口的宽度,且所述第一凹槽的深度超过0.3um。

作为本发明一实施方式的进一步改进,所述方法还包括:在所述第二介电层上开设第二介电层开口,使得所述第二介电层开口裸露至少部分所述重布线层;在所述第二介电层开口处植入锡球,使得所述锡球与所述重布线层电性连接。

作为本发明一实施方式的进一步改进,所述方法还包括:在所述锡球与所述重布线层两者之间设置球下金属层,使得所述球下金属层经由所述第二介电层开口将所述锡球与所述重布线层电性连接,所述球下金属层的部分侧面与所述重布线层的表面围设形成第二金属层开口。

作为本发明一实施方式的进一步改进,所述方法还包括:在所述第二介电层的表面开设第二凹槽,使得所述第二凹槽的底面与所述第二金属层开口的上侧面高度相差超过0.3um,且所述第二凹槽与所述第二金属层开口连通或至少部分重叠。

与现有技术相比,本发明的有益效果在于:通过在第一介电层的表面开设凹槽,将第二介电层嵌入第一介电层中,增大两层介电层之间的的接触面积、增加介电层之间的粘合力,从而抵抗与重布线层之间的应力,防止重布线层与两层介电层三者交界处分层或者裂纹的产生。

附图说明

图1是本发明第一实施例中封装结构的截面示意图;

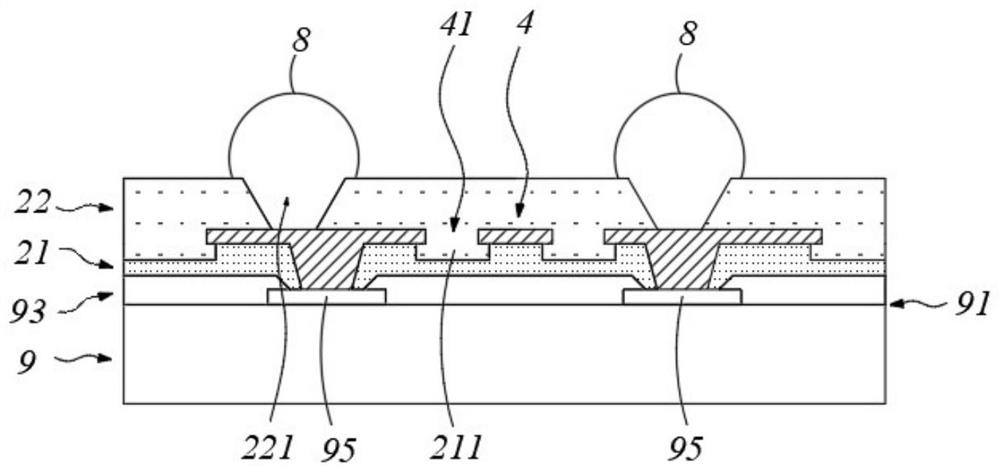

图2是本发明第二实施例中封装结构的截面示意图;

图3是本发明第三实施例中封装结构的截面示意图;

图4是本发明第四实施例中封装结构的截面示意图;

图5是本发明第一实施例中封装方法的流程图;

图6是本发明第一实施例中各步骤对应的结构示意图。

具体实施方式

为使本申请的目的、技术方案和优点更加清楚,下面将结合本申请具体实施方式及相应的附图对本申请技术方案进行清楚、完整地描述。显然,所描述的实施方式仅是本申请一部分实施方式,而不是全部的实施方式。基于本申请中的实施方式,本领域普通技术人员在没有做出创造性劳动前提下所获得的所有其他实施方式,都属于本申请保护的范围。

下面详细描述本发明的实施方式,实施方式的示例在附图中示出,其中自始至终相同或类似的标号表示相同或类似的元件或具有相同或类似功能的元件。下面通过参考附图描述的实施方式是示例性的,仅用于解释本发明,而不能理解为对本发明的限制。

如图1至图3所示,本发明一实施例提供了一种堆叠式封装结构,包括芯片9,芯片9可以是硅芯片,或者是扇出型重布线基板,如eWLB(嵌入式晶圆级球栅阵列)塑封料与硅组成的异构芯片。第一介电层21设于所述芯片9的主动表面91上;重布线层4设于所述第一介电层21上,所述重布线层4开设有第一金属层开口41,所述第一金属层开口41裸露至少部分所述第一介电层21;第二介电层22设于所述重布线层4上;所述第一介电层21的表面还开设有第一凹槽211,所述第一凹槽211与所述第一金属层开口41相互连通,所述第二介电层22经由所述第一金属层开口41及所述第一凹槽211与所述第一介电层21连接。

本发明实施例中,堆叠式封装结构为芯片级封装,封装结构包括设有主动表面91的芯片9,三层堆叠式结构通过一层层平铺堆叠的形式设置于芯片9的主动表面91上,即第一介电层21设置于芯片9的主动表面91上方,重布线层4设置于第一介电层21的上方,第二介电层22则设置于重布线层4的上方,形成三层结构。

重布线层4为金属层,为实现线路走线,重布线层4开设有第一金属层开口41,第一金属层开口41沿着材料厚度方向贯穿重布线层4,将第一介电层21的至少部分表面露出;第二介电层22则可经过或穿过第一金属层开口41后,与下方的第一介电层21相互连接。

由于介电层与重布线层4两种材料的热膨胀系数不同,且第一介电层21与第二介电层22可能是不同的材料,或者两层介电层厚度及面积也不尽相同,在热循环制程中三层结构易受热膨胀遇冷收缩,在第一金属层开口41边界三层结构的交界处,易受到应力拉扯作用而出现三层结构分层或者产生裂纹的现象。为此,在第一介电层21的表面开设第一凹槽211,第二介电层22经过第一金属层开口41后可继续向下经过第一凹槽211,最终与第一介电层21相互连接;即第二介电层22至少部分进入或嵌入第一介电层21中。由此,两层介电层之间的接触面积增大,两者之间的粘合力提升,可抵抗与重布线层4之间的应力作用,从而防止分层或者产生裂纹、提高可靠性。

同时,为实现功能性系统互联,芯片9的主动表面91上还可设有金属焊垫95与一层保护层93,金属焊垫95暴露于保护层93之外;第一介电层21还设有开口,用于暴露出至少部分金属焊垫95;重布线层4则通过这个开口与金属焊垫95电性连接,从而重布线层4与芯片9相互电性连接。

其中,第一介电层21可通过涂覆等工艺设置于芯片9的主动表面91上,材料不限,可以是苯环丁烯(BCB)或聚亚酰胺(PI)等,或者是其它高分子介电材料以及带填料的高分子介电材料等。

重布线层4可以通过溅镀或者电镀等方式设置于第一介电层21的上方,重布线层4的材料可以为钛、TiW、铜、金和金属的合金,或者是钛、TiW、铜、镍和金的合金等金属的单层或多层结构,如200-1000A Ti与2-30um Cu。

第二介电层22也可通过涂覆等工艺加工,使其设于重布线层4以及暴露的第一介电层21表面上。

第一金属层开口41与第一凹槽211的加工形式不限,可通过微影蚀刻或者激光刻蚀等方式来除去部分重布线层4以及部分第一介电层21,以得到第一金属层开口41与第一凹槽211两者;两者的加工形式可以相同,也可以不相同。

此外,堆叠式封装结构为晶圆级或板级封装,如封装结构包括晶圆,晶圆设有主动表面91,三层堆叠式结构通过一层层平铺堆叠的形式设置于晶圆的主动表面91上。其中,芯片9可以是硅芯片,或者是扇出型重布线基板,如eWLB(嵌入式晶圆级球栅阵列)塑封料与硅组成的异构芯片。

进一步的,所述第一凹槽211的宽度不小于所述第一金属层开口41的宽度,且所述第一凹槽211的深度超过0.3um。

进一步的,所述第一凹槽211的宽度等于所述第一金属层开口41的宽度。

具体的,为增大两层介电层的接触面积,可将第一凹槽211的深度设置为超过0.3um,使得第一介电层21与第二介电层22两者之间的嵌套部分尽量大。其中,通过实际实验验证,将嵌入深度设置为超过0.3um可有效避免分层现象。

同时,第一凹槽211宽度加宽,使得第一凹槽211的边界可与第一金属层开口41对齐,或第一凹槽211的边界位于重布线层4的下方;如图2所示,较佳的,为方便加工,第一凹槽211的边界可与第一金属层开口41对齐,两者可同时通过激光或蚀刻来加工形成。

由此,两层介电层相互嵌套,接触面积极大增加、粘合力提升,可抵抗与重布线层4之间的应力作用,防止分层或者产生裂纹。

进一步的,所述第二介电层22还开设有第二介电层开口221,所述第二介电层开口221裸露至少部分所述重布线层4;所述封装结构还包括锡球8,所述锡球8通过所述第二介电层开口221与所述重布线层4电性连接。

为电性连接其他外部电路,如电路板(PCB)、芯片9或其他半导体封装件等,在封装结构中,还可在第二介电层22上方设置锡球8,将锡球8与重布线层4电性连接。

具体的,第二介电层22上开设有第二介电层开口221,第二介电层开口221沿着材料厚度方向贯穿第二介电层22,将重布线层4的至少部分表面露出;锡球8则可经过或穿过第二介电层开口221后,与下方的重布线层4相互电性连接。其中,锡球8可植入第二介电层开口221中并与重布线层4直接接触,或者通过球下金属层6与重布线层4接触。

进一步的,所述封装结构还包括设于所述锡球8与所述重布线层4两者之间的球下金属层6,所述球下金属层6经由所述第二介电层开口221将所述锡球8与所述重布线层4电性连接,所述球下金属层6的部分侧面与所述重布线层4的表面围设形成有第二金属层开口62;所述第二介电层22的表面还开设有第二凹槽222。

进一步的,所述第二凹槽222的底面与所述第二金属层开口62的上侧面高度相差超过0.3um。

进一步的,所述第二凹槽222与所述第二金属层开口62连通或至少部分重叠。

如图3所述,为方便锡球8焊接,可在第二介电层开口221内形成球下金属层6,球下金属层6经过或穿过第二介电层开口221后,与下方的重布线层4电性连接,再在球下金属层6的上方形成锡球8等金属焊球,使得锡球8与球下金属层6电性连接。由此,重布线层4的金属线路露出面积增加,锡球8焊接方便且与重布线层4的电性连接牢靠。

当设置有球下金属层6时,第二介电层22位于球下金属层6下方且与球下金属层6镶嵌,球下金属层6与第二介电层22之间也存在热胀冷缩导致的应力作用。为改善此情况,还可在第二介电层22的表面开设第二凹槽222,以减少第二介电层22的材料份量。

较佳的,除去部分第二介电层22,在其表面形成深度超过0.3um的第二凹槽222,以减少第二介电层22的材料份量;同时,第二凹槽222的边界可以与球下金属层6的边界齐平,以方便加工;或者第二凹槽222进入球下金属层6下方,使得第二凹槽222在第二介电层22表面的挖空面积尽可能大,第二介电层22与球下金属层6两者之间的接触面积尽可能小,从而最大程度地缓解不同材料在热胀冷缩产生的应力作用和改变应力方向,防止分层或者产生裂纹、提高可靠性。

进一步的,所述封装结构还包括设于所述第二介电层22上方的第三介电层23,所述第三介电层23包封所述球下金属层。

为了进一步提升整体封装结构的可靠性,设置第三介电层23包封UBM球下金属层6,将裸露出的UBM球下金属层6包裹起来。第三介电层23可以为覆盖于UBM球下金属层6的岛状结构,并沿着UBM球下金属层6的侧边开口,如第三介电层23的截面形状可以是环形或带倒角的方形。

如此,整体封装结构的是耐用度和持久度提升,可靠性增强;独立的第三介电层23保护单个UBM球下金属层6,可以缓减UBM球下金属层6热胀冷缩的变形,防止晶圆和封装体的翘曲变化。

为方便理解,以下对示例进行具体描述:

实施例1

如图1所示,芯片9的主动表面91设有三层堆叠式结构,主动表面91上还设有金属焊垫95与一层保护层93,金属焊垫95暴露于保护层93之外。

第一介电层21设置于芯片9的主动表面91上方;第一介电层21还设有开口,以暴露出至少部分金属焊垫95。

重布线层4设置于第一介电层21的上方;重布线层4通过第一介电层21设置的开口与金属焊垫95的露出部分电性连接;重布线层4开设有第一金属层开口41,第一金属层开口41沿着材料厚度方向贯穿重布线层4,将第一介电层21的至少部分表面露出。

第一介电层21表面的表面还开设有第一凹槽211,第一凹槽211与第一金属层开口41连通,且第一凹槽211的宽度大于第一金属层的宽度,即第一凹槽211边界进入重布线层4下方。

第二介电层22则设置于重布线层4的上方;在第二介电层22上开设有第二介电层开口221,可将重布线层4的至少部分表面露出;在第二介电层开口221位置处设有锡球8,锡球8与重布线层4焊接固定以实现电性连接。

实施例2

如图2所示,同样的,芯片9的主动表面91设有三层堆叠式结构,主动表面91上还设有金属焊垫95与一层保护层93,金属焊垫95暴露于保护层93之外。

与第一实施例不同的是,本实施例中,第一凹槽211与第一金属层两者宽度等宽,即第一凹槽211边界与第一金属层边界齐平,两者可同时通过激光或蚀刻来加工形成,加工方便工艺简单。

实施例3

如图3所示,同样的,芯片9的主动表面91设有三层堆叠式结构,主动表面91上还设有金属焊垫95与一层保护层93,金属焊垫95暴露于保护层93之外。

与第一实施例不同的是,本实施例中,在第二介电层开口221内形成有球下金属层6,球下金属层6经过或穿过第二介电层开口221后,与下方的重布线层4电性连接。

球下金属层6的上方焊接形成锡球8等金属焊球,使得锡球8与球下金属层6电性连接。

实施例4

如图4所示,同样的,芯片9的主动表面91设有三层堆叠式结构,主动表面91上还设有金属焊垫95与一层保护层93,金属焊垫95暴露于保护层93之外。

与第三实施例不同的是,本实施例中,在第二介电层22上方设置包封UBM球下金属层6的第三介电层23,将裸露出的UBM球下金属层6包裹起来。第三介电层23为覆盖于UBM球下金属层6的岛状结构,并沿着UBM球下金属层6的侧边开口,如第三介电层23的截面形状是环形或带倒角的方形。

如图5所示,本发明实施例还提供了一种堆叠式封装方法,所述方法包括以下步骤,下面进行具体说明:

S2将第一介电层21设置于晶圆或芯片9的主动表面91上;

S4将重布线层4设置于所述第一介电层21上,并在所述重布线层4上开设第一金属层开口41,使得所述第一金属层开口41裸露至少部分所述第一介电层21;

S6在所述第一介电层21的表面开设第一凹槽211,使得所述第一凹槽211与所述第一金属层开口41相互连通;

S8将第二介电层22设置于所述重布线层4上,使得所述第二介电层22经由所述第一金属层开口41及所述第一凹槽211与所述第一介电层21连接。

本发明实施例中,封装结构为晶圆级封装或芯片级封装,晶圆或芯片9设有主动表面91。

首先,通过涂覆等工艺将第一介电层21设置于芯片9的主动表面91上方。接着,通过溅镀或者电镀等方式,将重布线层4设置于第一介电层21的上方;并在重布线层4上开设第一金属层开口41,第一金属层开口41沿着材料厚度方向贯穿重布线层4,将第一介电层21的至少部分表面露出;同时,也在第一介电层21的表面开设第一凹槽211,第一凹槽211可以与第一金属层开口41通过微影蚀刻或者激光刻蚀等方式一并加工;然后,再通过涂覆等工艺,将第二介电层22则设置于重布线层4的上方;第二介电层22可经过第一金属层开口41及第一凹槽211两者后,进入下方的第一介电层21,即第一介电层21与第二介电层22两者相互嵌套并连接。其中,第一介电层21与第二介电层22可能是不同的材料,或者两层介电层厚度及面积也不尽相同。

进一步的,对于步骤S6,所述方法具体包括:

所述第一凹槽211的宽度不小于所述第一金属层开口41的宽度,且所述第一凹槽211的深度超过0.3um。

为增大两层介电层的接触面积,将第一凹槽211的深度设置为超过0.3um,并加宽第一凹槽211宽度,使得第一凹槽211的边界与第一金属层开口41对齐,或第一凹槽211的边界位于重布线层4的下方。

进一步的,在步骤S8之后,所述方法还包括:

S91在所述第二介电层22上开设第二介电层开口221,使得所述第二介电层开口221裸露至少部分所述重布线层4;

S93在所述第二介电层开口221处植入锡球8,使得所述锡球8与所述重布线层4电性连接。

进一步的,对于步骤S93,所述方法具体包括:

S931在所述锡球8与所述重布线层4两者之间设置球下金属层6,使得所述球下金属层6经由所述第二介电层开口221将所述锡球8与所述重布线层4电性连接,所述球下金属层6的部分侧面与所述重布线层4的表面围设形成第二金属层开口62。

为电性连接其他外部电路,还可在第二介电层22上方设置锡球8。具体的,在第二介电层22上开设第二介电层开口221,第二介电层开口221沿着材料厚度方向贯穿第二介电层22,将重布线层4的至少部分表面露出;在第二介电层开口221内形成球下金属层6,球下金属层6经过或穿过第二介电层开口221后,与下方的重布线层4电性连接;在球下金属层6的上方形成锡球8等金属焊球,使得锡球8与球下金属层6电性连接。

进一步的,对于步骤S931,所述方法具体包括:

在所述第二介电层22的表面开设第二凹槽222,使得所述第二凹槽222的底面与所述第二金属层开口62的上侧面高度相差超过0.3um,且所述第二凹槽222与所述第二金属层开口62连通或至少部分重叠。

设置球下金属层6后,球下金属层6的部分侧面与重布线层4的表面围设形成第二金属层开口62,球下金属层6与第二介电层22之间也存在热胀冷缩导致的应力作用。

为改善此情况,还可在第二介电层22的表面开设第二凹槽222,第二凹槽222深度超过0.3um,且边界可以与球下金属层6的边界齐平,或者第二凹槽222进入球下金属层6下方,从而第二介电层22与球下金属层6两者之间的接触面积尽可能小,从而最大程度地缓解不同材料在热胀冷缩产生的应力作用。

下面整体描述堆叠式封装方法:

本发明实施例中,如图6所示,封装结构为晶圆级封装或芯片级封装,晶圆或芯片9设有主动表面91。主动表面91上还设有金属焊垫95与一层保护层93,金属焊垫95暴露于保护层93之外。

首先,通过涂覆等工艺将第一介电层21设置于主动表面91与金属焊垫95的上方,第一介电层21还设有开口,暴露出至少部分金属焊垫95。

再通过溅镀或者电镀等方式,将重布线层4设置于第一介电层21的上方;重布线层4通过第一介电层21设置的开口与金属焊垫95的露出部分电性连接,以与芯片9相互电性连接。

通过微影蚀刻或者激光刻蚀的方式除去部分重布线层4以及部分第一介电层21,以形成贯穿重布线层4的第一金属层开口41及位于第一介电层21表面的第一凹槽211;

再通过涂覆等工艺,将第二介电层22则设置于重布线层4的上方;在第二介电层22上开设第二介电层开口221,将重布线层4的至少部分表面露出;在第二介电层开口221位置处植入锡球8,使得锡球8与重布线层4电性连接。

综上,本发明提供的堆叠式封装结构,芯片9的主动表面91上方依次设有第一介电层21、重布线层4以及第二介电层22这三层堆叠式结构,通过在第一介电层21的表面增加第一凹槽211,使得第一介电层21可进入第二介电层22,嵌套的两层介电层之间的接触面积增大,两者之间的粘合力提升,可抵抗与重布线层4之间的应力作用,从而防止分层或者产生裂纹、提高可靠性。

应当理解,虽然本说明书按照实施方式加以描述,但并非每个实施方式仅包含一个独立的技术方案,说明书的这种叙述方式仅仅是为清楚起见,本领域技术人员应当将说明书作为一个整体,各实施方式中的技术方案也可以经适当组合,形成本领域技术人员可以理解的其他实施方式。

上文所列出的一系列的详细说明仅仅是针对本发明的可行性实施方式的具体说明,并非用以限制本发明的保护范围,凡未脱离本发明技艺精神所作的等效实施方式或变更均应包含在本发明的保护范围之内。