半导体装置

文献发布时间:2023-06-19 11:27:38

关联申请的相互参照

本申请基于2018年11月7日申请的日本专利申请第2018-209870号,这里通过参照而并入其记载内容。

技术领域

本发明涉及将结型FET(Field Effect Transistor:以下简记为JFET)与MOSFET(Metal Oxide Semiconductor Field Effect Transistor的简写)级联连接(cascodeconnected)而成的半导体装置。

背景技术

以往,提出了将设为常通型的JFET与设为常断型的MOSFET级联连接而成的半导体装置。另外,JFET例如使用碳化硅基板、氮化镓基板等而构成,MOSFET例如使用硅基板而构成。

这样的半导体装置中,在连接电源而施加了电压偏置时,在JFET及MOSFET中产生漏电流,在JFET的漏电流比MOSFET的漏电流大的情况下,未流尽的电荷被蓄积于MOSFET。而且,在MOSFET中,通过PN结的反偏压的大小增加并击穿,从而成为流通JFET的漏电流的状态。该情况下,在MOSFET中,击穿状态持续继续,因此有可能发生栅极寿命的降低、阈值电压的变动等。

因此,例如,在专利文献1中提出了与MOSFET并联地连接外接的旁路电阻。由此,JFET的漏电流也通过旁路电阻而排出,因此能够抑制MOSFET击穿。

现有技术文献

专利文献

专利文献1:日本特开2017―59697号公报

发明内容

但是,上述半导体装置由于设为具有旁路电阻的半导体装置,因此在安装了半导体装置后难以进行MOSFET的耐压等的特性检查。

本发明的目的在于,提供在级联连接有JFET和MOSFET的半导体装置中能够抑制MOSFET持续击穿、并且在安装后也能够抑制难以进行MOSFET的特性检查的情况的半导体装置。

根据本发明的1个方案,半导体装置具备具有源极电极、漏极电极、栅极电极的JFET以及具有源极电极、漏极电极、栅极电极的MOSFET,JFET和MOSFET通过将JFET的源极电极与MOSFET的漏极电极电连接而级联连接,JFET具有第1导电型的漂移层、配置在漂移层上的第1导电型的沟道层、形成在沟道层的表层部并与沟道层相比为高杂质浓度的第1导电型的源极层、在沟道层中形成得比源极层深且作为栅极电极的第2导电型的栅极层、在沟道层中形成得比源极层深且与栅极层分离的第2导电型的体层、隔着漂移层而配置在与源极层相反的一侧的漏极层、与源极层及体层电连接的源极电极、以及与漏极层电连接的漏极电极,栅极层与体层之间的耐压比MOSFET的耐压低。

由此,栅极层与体层之间的耐压被设为MOSFET的耐压以下。因此,在JFET中产生了漏电流时,在MOSFET击穿之前,漏电流容易经由栅极层被排出。从而,能够抑制MOSFET击穿,还能够抑制MOSFET成为持续击穿的状态。并且,由于也不需要与MOSFET并联地配置外接电阻等,因此还能够抑制在安装半导体装置后难以进行MOSFET的特性检查的情况。

并且,根据本发明的其他方案,半导体装置具备具有源极电极、漏极电极、栅极电极的JFET以及具有源极电极、漏极电极、栅极电极的MOSFET,JFET和MOSFET通过将JFET的源极电极与MOSFET的漏极电极电连接而级联连接,MOSFET具备第1导电型的漂移层、配置在漂移层上的第2导电型的沟道层、形成在沟道层的表层部且与漂移层相比为高杂质浓度的第1导电型的源极层、配置在夹在源极层与漂移层之间的沟道层的表面的栅极绝缘膜、配置在栅极绝缘膜上的栅极电极、隔着漂移层而配置在与沟道层相反的一侧的漏极层、与沟道层及源极层电连接的源极电极、以及与漏极层连接的漏极电极,在漂移层形成有结晶缺陷,以使MOSFET的漏电流比JFET的漏电流大。

由此,在MOSFET中形成有结晶缺陷,以使在MOSFET中产生的漏电流比在JFET中产生的漏电流大。因此,能够抑制MOSFET击穿,并且能够抑制MOSFET成为持续击穿的状态。并且,由于也不需要与MOSFET并联地配置外接电阻等,因此还能够抑制在安装半导体装置后难以进行MOSFET的特性检查的情况。

另外,各构成要素等所附加的带括弧的参照附图标记表示该构成要素等与后述的实施方式中记载的具体构成要素等之间的对应关系的一例。

附图说明

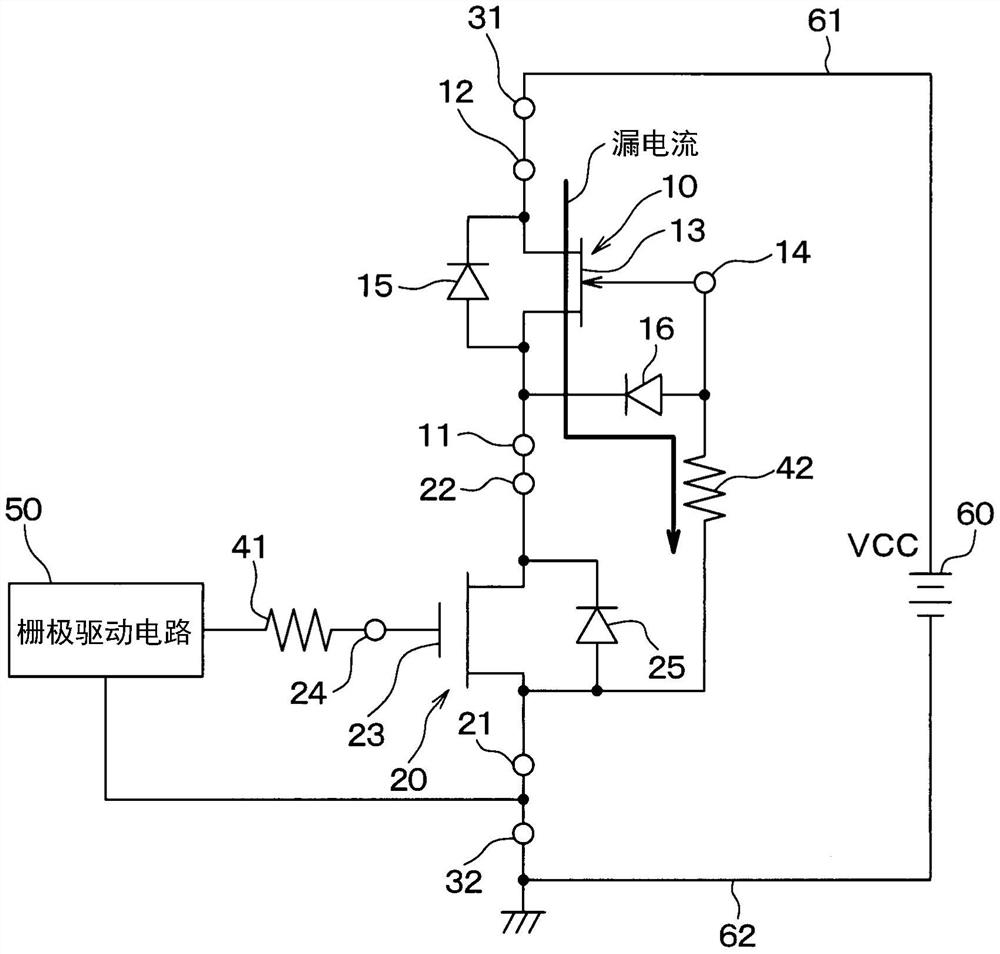

图1是表示第1实施方式中的半导体装置的电路图以及漏电流流通的路径的图。

图2是第1半导体芯片的平面图。

图3是沿着图2中的III-III线的截面图。

图4是表示JFET中的栅极层与体层之间的长度、和栅极层与体层之间的耐压的关系的图。

图5是第2半导体芯片的平面图。

图6是沿着图5中的VI-VI线的截面图。

图7是第2实施方式中的第2半导体芯片的截面图。

图8是表示照射线量与MOSFET的漏电流的关系的图。

图9是表示第2实施方式中的半导体装置的电路图以及漏电流流通的路径的图。

具体实施方式

以下,基于附图说明本发明的实施方式。另外,在以下的各实施方式中,对于彼此相同或等同的部分附加相同的附图标记而进行说明。

(第1实施方式)

说明第1实施方式。首先,说明本实施方式的半导体装置中的电路结构。如图1所示,本实施方式的半导体装置将常通型的JFET10与常断型的MOSFET20级联连接而构成。另外,本实施方式中,将JFET10及MOSFET20分别设为N沟道型。

JFET10具有源极电极11、漏极电极12、栅极层(即栅极电极)13,具体结构在后面叙述。MOSFET20具有源极电极21、漏极电极22以及栅极电极23,具体结构在后面叙述。

而且,JFET10及MOSFET20中,JFET10的源极电极11与MOSFET20的漏极电极22被电连接。并且,JFET10的漏极电极12与第1端子31连接,MOSFET20的源极电极21与第2端子32连接。

MOSFET20的栅极电极23经由栅极焊盘24及调整用电阻41而与栅极驱动电路50连接。JFET10的栅极层13经由调整用电阻42及栅极焊盘14而与MOSFET20的源极电极21电连接。

并且,本实施方式中,在JFET10的漏极电极12与源极电极11之间连接有二极管15。本实施方式中,在JFET10中,如图3所示,在N

进而,通过在JFET10中形成有体层116,从而在栅极焊盘14与源极电极11之间形成二极管16。该二极管成为阴极与源极电极11连接的状态,且成为阳极与栅极焊盘14连接的状态。

并且,在MOSFET20的漏极电极22与源极电极21之间连接有二极管25。该二极管25是在MOSFET20的结构上形成的寄生二极管,阴极与漏极电极22电连接,阳极与源极电极21电连接。

以上是本实施方式的半导体装置的电路结构。而且,这样的半导体装置中,第1端子31与被从电源60施加电压Vcc的电源线61连接,第2端子32与地线62连接。

接着,参照图2~图5说明JFET10及MOSFT20的具体结构。本实施方式中,JFET10形成于第1半导体芯片100,MOSFET20形成于第2半导体芯片200。而且,虽然没有特别图示,但半导体装置在将这些第1半导体芯片100及第2半导体芯片200级联连接而电连接的状态下被一体化。

第1半导体芯片100如图2所示设为平面矩形状,具有单元区域101以及包围该单元区域101的外周区域102。而且,在单元区域101形成有JFET10。

具体来说,第1半导体芯片100如图3所示具备半导体基板110,该半导体基板110具有由N

漂移层113上配置有N

进而,以将源极层115贯通的方式形成有与沟道层114相比设为高杂质浓度的P

本实施方式中,栅极层13及体层116沿着半导体基板110的面方向上的一个方向延伸设置,在该面方向且与延伸设置方向正交的方向上交替地配置。即,图3中,栅极层13及体层116在纸面垂直方向上延伸设置。并且,栅极层13及体层116在纸面左右方向上交替地配置,且相互分离地配置。

本实施方式中,关于栅极层13及体层116,杂质浓度相等,并且沿着排列方向的宽度相等。另外,本实施方式中,体层116一直形成到比栅极层13深的位置。即,体层116与栅极层13相比向漏极层111侧突出。

而且,本实施方式中,栅极层13及体层116构成为,栅极层13与体层116之间的耐压BVgb为JFET10的阈值电压以上且为MOSFET20的耐压以下。另外,所谓JFET10的阈值电压,是JFET10成为截止状态的电压。

在此,如图4所示,随着栅极层13与体层116之间的长度L变长,栅极层13与体层116之间的耐压BVgb变高。因此,本实施方式中,关于栅极层13及体层116,将长度L设定为,使栅极层13与体层116之间的耐压BVgb为JFET10的阈值电压以上且为MOSFET20的耐压以下。

如图3所示,在半导体基板110的一面110a上形成有层间绝缘膜117。而且,在层间绝缘膜117,形成有使源极层115及体层116露出的接触孔117a。在层间绝缘膜117上形成有经由接触孔117a而与源极层115及体层116电连接的源极电极11。

另外,源极电极11包含单元区域101的整个面而形成。即,源极电极11形成为所谓的实心状。因此,源极电极11与后述的栅极布线118相比,截面积足够大。换言之,源极电极11与后述的栅极布线118相比,电流容量足够大。

在半导体基板110的另一面110b侧,形成有与漏极层111电连接的漏极电极12。

如图2所示,在外周区域102形成有栅极焊盘14及栅极布线118。而且,栅极布线118与栅极焊盘14连接,并且在与图3不同的截面中与栅极层13电连接。另外,虽然没有特别图示,但在外周区域102中,为了能够实现耐压提高,在半导体基板110的表层部,以包围单元区域101的方式形成有环状的P型的阱区域、多个P型的保护环,作为多重环构造。

以上是本实施方式中的第1半导体芯片100的结构。另外,本实施方式的第1半导体芯片100中,N

接着,关于第2半导体芯片200的结构,参照图5及图6进行说明。

如图5所示,第2半导体芯片200被设为平面矩形状,具有单元区域201以及包围单元区域201的外周区域202。而且,在单元区域201形成有MOSFET20。

具体来说,如图6所示,第2半导体芯片200具备半导体基板210,该半导体基板210具有由N

并且,在半导体基板210中,以将沟道层213贯通而到达漂移层212的方式形成有多个沟槽214,由该沟槽214将沟道层213分离为多个。本实施方式中,多个沟槽214沿着半导体基板210的一面210a的面方向中的一个方向(图6中纸面进深方向)等间隔地形成为条状。另外,多个沟槽214也可以通过将前端部环绕而设为环状构造。

并且,各沟槽214内被以覆盖各沟槽214的壁面的方式形成的栅极绝缘膜215和形成在该栅极绝缘膜215之上的由多晶硅等构成的栅极电极23填埋。由此,构成了沟槽栅构造。另外,本实施方式中,各沟槽214的壁面相当于沟道层213的表面。

而且,在沟道层213,形成有N

更详细来说,源极层216被设为如下构造:在沟槽214间的区域中,以沿着沟槽214的长度方向而与沟槽214的侧面相接的方式棒状地延伸设置,在比沟槽214的顶端靠内侧的位置终止。并且,接触层217被2个源极层216夹着而沿沟槽214的长度方向(即源极层216)棒状地延伸设置。另外,本实施方式的接触层217以半导体基板210的一面210a为基准而形成得比源极层216深。

在沟道层213(即半导体基板210的一面210a)上形成有层间绝缘膜218。而且,在层间绝缘膜218中形成有使源极层216的一部分及接触层217露出的接触孔218a。在层间绝缘膜218上形成有经由接触孔218a而与源极层216及接触层217电连接的源极电极21。

在半导体基板210的另一面210b侧形成有与漏极层211电连接的漏极电极22。

并且,如图5所示,在外周区域202形成有栅极焊盘24及栅极布线219。而且,栅极布线219在与图6不同的截面中与栅极电极23电连接。另外,虽然没有特别图示,但在外周区域202,为了能够实现耐压提高,在半导体基板210的表层部,作为多重环构造而以包围单元区域201的方式形成有环状的P型的阱区域、多个P型的保护环。

以上为第2半导体芯片200的结构。另外,本实施方式的第2半导体芯片200中,N型、N

接着,关于本实施方式的半导体装置的动作进行说明。另外,本实施方式的半导体装置由于具有常断的MOSFET20,因此整体以常断的方式动作。

首先,为了使半导体装置进行开关导通动作而成为导通状态,从栅极驱动电路50对MOSFET20的栅极电极23施加规定的正的栅极电压。由此,常断型的MOSFET20成为导通状态。并且,JFET10的栅极层13与第2端子32连接。因此,常通型的JFET10的栅极层13与源极电极11的电位差几乎为零,JFET10成为导通状态。因而,在第1端子31与第2端子32之间流过电流,半导体装置最终成为导通状态。

接着,为了使半导体装置进行开关截止动作而成为截止状态,使对MOSFET20的栅极电极23施加的栅极电压变小(例如设为0V)。由此,常断型的MOSFET20成为截止状态。并且,由于MOSFET20成为截止状态,从而MOSFET20的漏极电极22和与其连接着的JFET10的源极电极11的电压上升,在该源极电极11与连接于第2端子32的JFET10的栅极层13之间产生电位差。而且,通过使源极电极11与栅极层13之间的电位差达到阈值,使得沟道消失而JFET10成为截止状态。由此,在第1端子31与第2端子32之间不再流过电流,半导体装置最终成为截止状态。

而且,本实施方式中,如上述那样,栅极层13与体层116之间的耐压BVgb被设为JFET10的阈值电压以上且MOSFET20的耐压以下。因此,在电源线61连接于第1端子31而地线62连接于第2端子32且在JFET10中产生了漏电流的情况下,能够抑制MOSFET20击穿。

即,本实施方式中,如上述那样,MOSFET20被设为与JFET10相比漏电流容易变少的结构。因此,半导体装置中,在JFET10中产生漏电流时,该漏电流流入MOSFET20从而MOSFET20中的PN结的反偏压增加。但是,本实施方式的半导体装置中,栅极层13与体层116之间的耐压BVgb比MOSFET20的耐压低。因而,半导体装置中,在MOSFET20击穿之前,在JFET10的栅极层13与体层116之间发生击穿,JFET10中的漏电流也通过栅极层13排出。由此,能够抑制MOSFET20击穿,还能够抑制MOSFET20持续击穿。

并且,栅极层13与体层116之间的耐压BVgb被设为JFET10成为截止状态的阈值电压以上。因此,在栅极层13与体层116之间发生击穿时,成为沟道没有形成于沟道层114的状态。因而,在栅极层13与体层116之间发生了击穿时,能够抑制漏电流经由沟道向MOSFET20流动。

另外,本实施方式中,如上述那样具备体层116,因此在发生了浪涌时,能够经由体层116流过浪涌电流。从而,与没有配置体层116的情况相比,对于浪涌电流的耐量也能够提高。

该情况下,本实施方式中,体层116形成得比栅极层13深。即,关于体层116,从半导体基板110的一面110a到底面的长度比从半导体基板110的一面110a到栅极层13的底面的长度长。即,体层116成为与栅极层13相比向漏极层111侧突出的状态。因此,关于电场强度,与栅极层13的底部侧相比,体层116的底部侧更容易变高。因而,在发生了浪涌时,在体层116的底部侧的区域容易发生击穿,浪涌电流容易向体层116流入。即,本实施方式中,采用浪涌电流能够流入栅极布线118及源极电极11的结构,但浪涌电流特别容易经由体层116流入电流容量大的源极电极11。因此,能够抑制栅极布线118因浪涌而熔断,能够抑制第1半导体芯片100被破坏。

如以上说明的那样,本实施方式中,栅极层13与体层116之间的耐压BVgb被设为JFET10的阈值电压以上且MOSFET20的耐压以下。因此,在JFET10中产生了漏电流时,在MOSFET20击穿之前,漏电流容易经由栅极层13而排出。因而,能够抑制MOSFET20击穿,还能够抑制MOSFET20成为持续击穿的状态。并且,由于也不需要与MOSFET20并联地配置外接电阻等,因此还能够抑制在安装半导体装置后难以进行MOSFET20的特性检查的情况。

(第2实施方式)

对第2实施方式进行说明。在本实施方式中,变更了MOSFET20的结构,其他与上述第1实施方式相同,因此在此省略说明。

本实施方式中,如图7所示,在MOSFET20中,多个结晶缺陷220形成于漂移层212。本实施方式中,结晶缺陷220例如通过照射氦(He)线而形成。但是,结晶缺陷220也可以通过其他方法形成。

而且,如图8所示,本实施方式中,调整了He线的照射线量,以使得在MOSFET20中产生的漏电流大于在JFET10中产生的漏电流。即,形成了结晶缺陷220,以使得在MOSFET20中产生的漏电流大于在JFET10中产生的漏电流。

另外,本实施方式中,虽然没有特别图示,但在JFET10中没有形成体层116,在JFET10中没有形成二极管15、16。

以上为本实施方式中的半导体装置的结构。接着,对上述半导体装置中的漏电流进行说明。

本实施方式中,在MOSFET20中形成有结晶缺陷220,以使得在MOSFET20中产生的漏电流大于在JFET10中产生的漏电流。因此,如图9所示,在该半导体装置中,能够将在JFET10中产生的全部漏电流从MOSFET20向地电位排出,因此能够抑制MOSFET20中的PN结的反偏压增加。因而,本实施方式的半导体装置中,能够抑制MOSFET20击穿,还能够抑制MOSFET20成为持续击穿的状态。

如以上说明的那样,本实施方式中,在MOSFET20中形成有结晶缺陷220,以使得在MOSFET20中产生的漏电流大于在JFET10中产生的漏电流。因此,能够抑制MOSFET20击穿,还能够抑制MOSFET20成为持续击穿的状态。并且,由于也不需要与MOSFET20并联地配置外接电阻等,因此还能够抑制在安装半导体装置后难以进行MOSFET20的特性检查的情况。

(其他实施方式)

本发明以实施方式为基准进行了记载,但可理解为本发明不限定于该实施方式和构造。本发明还包含各种变形例及等价范围内的变形。除此以外,各种组合和方式、进而在这些中包括仅一个要素、其以上或其以下的其他组合和方式也落入本发明的范畴和思想范围。

例如,在上述各实施方式中,也可以适当地将JFET10及MOSFET20设为P沟道型。

并且,在上述各实施方式中,作为MOSFET20而说明了沟槽栅型的结构,但MOSFET20也可以设为平面栅型。

进而,在上述各实施方式中,体层116也可以设为与栅极层13相同的深度。但是,在想要从体层116流过较多浪涌电流的情况下,优选采用体层116的底部侧与栅极层13的底部侧相比电场强度容易变高的结构。该情况下,可以是,通过使体层116的底部成为前端细的形状、或使体层116的宽度比栅极层13的宽度窄,从而设为体层116的底部侧与栅极层13的底部侧相比电场强度容易变高的结构。并且,可以是,通过将与体层116的底面相连的区域设为杂质浓度比与栅极层13的底面相连的区域高的N型区域,从而设为体层116的底部侧与栅极层13的底部侧相比电场强度容易变高的结构。

并且,在上述第1实施方式中,说明了通过调整栅极层13与体层116之间的长度L从而使栅极层13与体层116之间的耐压BVgb为JFET10的阈值电压以上且比MOSFET20的耐压低的例子。但是,栅极层13与体层116之间的耐压BVgb也可以如下那样调整。例如,栅极层13与体层116之间的耐压BVgb也可以通过调整栅极层13与体层116之间的沟道层114的杂质浓度从而被设为JFET10的阈值电压以上且比MOSFET20的耐压低。该情况下,栅极层13与体层116之间的耐压BVgb也可以通过栅极层13与体层116之间的长度L以及沟道层114的杂质浓度这两者来调整。

并且,也可以将上述各实施方式组合。即,在上述第2实施方式中,JFET10也可以设为如上述第1实施方式那样形成有体层116的结构。由此,能够进一步抑制MOSFET20击穿。

另外,在上述第2实施方式中,MOSFET20通过结晶缺陷220而抑制击穿。因此,在JFET10中形成体层116的情况下,可以将该体层116形成为,使得栅极层13与体层116之间的耐压比MOSFET20的耐压高。即,也可以使JFET10的体层116作为主要针对浪涌电流的应对而形成。

- 晶体、结晶性氧化物半导体、包含结晶性氧化物半导体的半导体膜、包含晶体和/或半导体膜的半导体装置以及包含半导体装置的系统

- 半导体光发射装置的制造方法、半导体光发射装置、半导体装置的制造方法、半导体装置、一种装置的制造方法、以及一种装置