图像感测装置

文献发布时间:2023-06-19 11:27:38

技术领域

本公开的各种实施方式涉及半导体设计技术,更具体地,涉及图像感测装置。

背景技术

图像感测装置利用半导体的光敏特性来捕获图像。通常,有两种类型的感测装置:电荷耦合器件(CCD)图像感测装置和互补金属氧化物半导体(CMOS)图像感测装置。近来,因为CMOS图像感测装置允许模拟和数字控制电路二者直接实现在单个集成电路(IC)上,所以CMOS图像感测装置得到广泛使用。

发明内容

本公开的各种实施方式涉及可以减少在读出电路之间发生的失配的图像感测装置。

根据一个实施方式,一种图像感测装置可以包括:第一列线至第四列线,其在列方向上延伸并且在行方向上依次设置;第一单位像素电路和第三单位像素电路,其布置在第一行中并联接至第一列线和第三列线;第二单位像素电路和第四单位像素电路,其布置在第二行中并联接至第二列线和第四列线;第一读出电路和第二读出电路,其对应于第一单位像素电路和第二单位像素电路;第三读出电路和第四读出电路,其对应于第三单位像素电路和第四单位像素电路;第一路径改变电路,其适于基于第一控制信号来改变第一列线和第二列线与第一读出电路和第二读出电路之间的第一路径和第二路径,使得第一单位像素电路和第二单位像素电路在第一单位时间期间根据第一关系联接至第一读出电路和第二读出电路;以及第二路径改变电路,其适于基于第二控制信号来改变第三列线和第四列线与第三读出电路和第四读出电路之间的第三路径和第四路径,使得第三单位像素电路和第四单位像素电路在第一单位时间期间根据与第一关系不同的第二关系联接至第三读出电路和第四读出电路。

根据一个实施方式,一种图像感测装置可以包括:第一列线至第四列线,其在列方向上延伸并且在行方向上依次设置;第一单位像素电路,其布置在第一行中并联接至第一列线;第二单位像素电路,其布置在第二行中并联接至第二列线;第三单位像素电路,其布置在第一行中并联接至第四列线;第四单位像素电路,其布置在第二行中并联接至第三列线;第一读出电路和第二读出电路,其分别对应于第一单位像素电路和第二单位像素电路;第三读出电路和第四读出电路,其分别对应于第三单位像素电路和第四单位像素电路;第一路径改变电路,其适于基于第一控制信号针对每个单位时间来改变第一列线和第二列线与第一读出电路和第二读出电路之间的第一路径和第二路径;以及第二路径改变电路,其适于基于第二控制信号针对每个单位时间来改变第三列线和第四列线与第三读出电路和第四读出电路之间的第三路径和第四路径。

根据一个实施方式,一种图像感测装置可以包括:第一列线至第四列线,其在列方向上延伸并且在行方向上依次设置;第一单位像素电路,其布置在第一行中并联接至第一列线;第二单位像素电路,其布置在第二行中并联接至第二列线;第三单位像素电路,其布置在第一行中并联接至第三列线;第四单位像素电路,其布置在第二行中并联接至第四列线;第一读出电路和第二读出电路,其分别对应于第一单位像素电路和第二单位像素电路;第三读出电路和第四读出电路,其分别对应于第三单位像素电路和第四单位像素电路;第一路径改变电路,其适于基于第一控制信号针对每个单位时间来改变第一列线和第二列线与第一读出电路和第二读出电路之间的第一路径和第二路径;以及第二路径改变电路,其与第一路径改变电路不同地、适于基于第二控制信号针对每个单位时间来改变第三列线和第四列线与第三读出电路和第四读出电路之间的第三路径和第四路径。

根据一个实施方式,一种图像感测装置可以包括:第一列线至第四列线,其在列方向上延伸并且在行方向上依次设置;第一单位像素电路和第三单位像素电路,其布置在第一行中并联接至第一列线和第三列线;第二单位像素电路和第四单位像素电路,其布置在所第二行中并联接至第二列线和第四列线;第一读出电路和第二读出电路,其分别对应于第一单位像素电路和第二单位像素电路;第三读出电路和第四读出电路,其分别对应于第三单位像素电路和第四单位像素电路;第一路径改变电路,其适于基于第一控制信号来改变第一列线和第二列线与第一读出电路和第二读出电路之间的第一路径和第二路径,使得第一单位像素电路和第二单位像素电路在第一单位时间期间根据第一关系联接至第一读出电路和第二读出电路;以及第二路径改变电路,其适于基于第二控制信号来改变第三列线和第四列线与第三读出电路和第四读出电路之间的第三路径和第四路径,使得第三单位像素电路和第四单位像素电路在第一单位时间期间根据第一关系和第二关系中的任何一个随机地联接至第三读出电路和第四读出电路。

根据一个实施方式,一种图像传感装置可以包括:两个线组,其在行方向上设置,并且每个线组具有在列方向上延伸的两条列线;两个像素组,其在行方向上设置并且每个像素组具有在列方向上设置的两个单位像素电路,各个像素组中的单位像素电路分别联接至各个线组中的列线;两个读出组,其在行方向上设置,并且每个读出组具有在列方向上设置的两个读出电路,各个读出组中的读出电路适于分别从各个像素组中的单位像素电路读出像素信号;以及路径控制电路,其适合于控制像素组和读出组之间的路径,以使从各个读出组中选择的一对读出电路能够在单位量时间期间输出像素信号。

附图说明

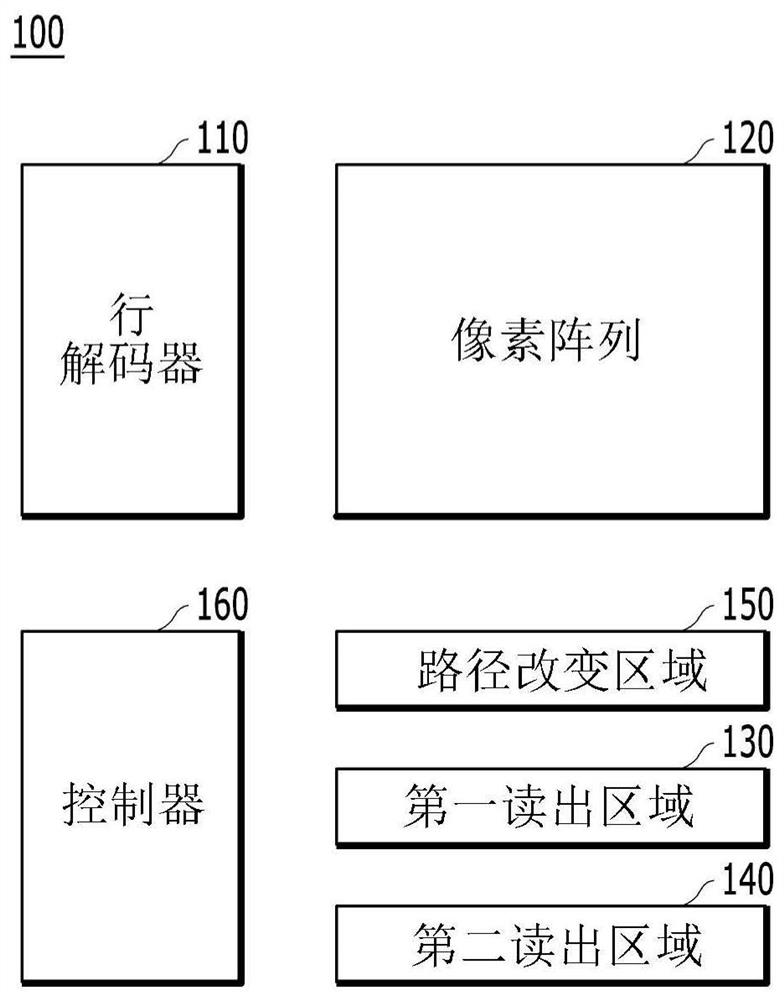

图1是示出根据本公开的第一实施方式的图像感测装置的框图。

图2是例示了图1所示的像素阵列、路径改变区域、第一读出区域和第二读出区域的内部结构的框图。

图3和图4是例示了图2中示出的第一路径改变电路和第二路径改变电路的框图。

图5和图6是用于描述图2中所示的第一像素电路至第四像素电路的像素信号通过哪个读出区域被读出的图。

图7是例示了根据本公开的第二实施方式的图像感测装置的框图。

图8是例示了图7所示的像素阵列、路径改变区域、第一读出区域和第二读出区域的内部结构的框图。

图9和图10是例示了图8中示出的第一路径改变电路和第二路径改变电路的框图。

图11和图12是用于描述图8所示的第一像素电路至第四像素电路的像素信号通过哪个读出区域被读出的图。

图13是例示了根据本公开的第三实施方式的图像感测装置的框图。

图14是例示了图13所示的像素阵列、第一读出区域、第二读出区域和路径改变区域的内部结构的框图。

图15是例示了图14所示的路径控制电路的电路图。

图16至图19是例示了图14中示出的第一路径改变电路和第二路径改变电路的框图。

具体实施方式

下面参照附图更详细地描述各种实施方式。提供这些实施方式以使得本公开是透彻的和完整的,并将本公开的范围充分地传达给本领域技术人员。在整个说明书中,对“实施方式”等的引用并不一定仅是一个实施方式,并且对任何这样的短语的不同引用也并一定是相同的实施方式。

将理解的是,当元件被称为“连接至”或“联接至”另一元件时,它可以直接在另一元件上,连接至或联接至另一元件,或者可以存在一个或更多个中间元件。另外,还将理解的是,当在本说明书中使用术语“包括”、“包含”及其衍生词时,其指定所提及元件的存在,并且不排除存在或添加一个或更多个其它元件。除非上下文另外明确指出,否则如本文所使用的,单数形式也可以包括复数形式,反之亦然。在本申请和所附权利要求书中使用的冠词“一”、“一个”通常应被解释为意指“一个或更多个”,除非另外说明或从上下文清楚地指向单数形式。

图1是例示了根据本公开的第一实施方式的图像感测装置100的框图。

参照图1,图像感测装置100可以包括行解码器110、像素阵列120、第一读出区域130、第二读出区域140、路径改变区域150和控制器160。

行解码器110可以控制像素阵列120的操作。例如,行解码器110可以以两行为单位控制像素阵列120。

像素阵列120可以包括布置在多个行和多个列的交叉处的多个像素电路。下面,具体参照图2来描述多个像素电路。像素阵列120可以在行解码器110的控制下生成像素信号。例如,像素阵列120可以在第一行线时间期间从布置在第一行和第二行中的像素电路生成像素信号,并在第n行线时间(其中,“n”是自然数)期间,从布置在第(2n-1)行和第2n行中的像素电路生成像素信号。短语“行线时间”表示特定行被激活的时间。

第一读出区域130可以读出从像素阵列120生成的像素信号的一半像素信号。例如,第一读出区域130可以在第一行线时间期间,读出从布置在第一行中的像素电路的一半像素电路生成的像素信号和从布置在第二行中的像素电路的一半像素电路生成的像素信号。

第二读出区域140可以读出从像素阵列120生成的像素信号的另一半像素信号。例如,第二读出区域140可以在第一行线时间期间,读出从布置在第一行中的像素电路的另一半像素电路生成的像素信号以及从布置在第二行中的像素电路的另一半像素电路生成的像素信号。

路径改变区域150可以将从像素阵列120生成的像素信号的一半像素信号传送到第一读出区域130,并且将从像素阵列120生成的像素信号的另一半像素信号传送到第二读出区域140。

第一读出区域130、第二读出区域140和路径改变区域150可以设置在像素阵列120的一侧上。具体地,路径改变区域150可以设置在像素阵列120与读出区域130和140之间。

控制器160可以控制行解码器110、第一读出区域130和第二读出区域140以及路径改变区域150的整体操作。例如,控制器160可以包括定时控制器。

图2是例示了图1所示的像素阵列120、第一读出区域130和第二读出区域140以及路径改变区域150中的每一个的一部分的框图。

参照图2,像素阵列120可以包括第一像素电路PX00、第二像素电路PX01、第三像素电路PX10和第四像素电路PX11。第一像素电路PX00和第二像素电路PX01可以布置在第一列中,并且第三像素电路PX10和第四像素电路PX11可以布置在第二列中。第一像素电路PX00和第三像素电路PX10可以布置在第一行中,第二像素电路PX01和第四像素电路PX11可以布置在第二行中。

第一像素电路PX00至第四像素电路PX11中的每一个可以包括至少一个像素。例如,第一像素电路PX00至第四像素电路PX11中的每一个可以包括单个像素或多个像素。多个像素可以具有共享每条列线的结构。

第一像素电路PX00可以联接至第一奇数编号列线CL00。第二像素电路PX01可以联接至第一偶数编号列线CL01。第三像素电路PX10可以联接至第二偶数编号列线CL11。第四像素电路PX11可以联接至第二奇数编号列线CL10。可以看出,第一像素电路PX00、第二像素电路PX01、第一奇数编号列线CL00和第一偶数编号列线CL01的联接结构与第三像素电路PX10、第四像素电路PX11、第二奇数编号列线CL10和第二偶数编号列线CL11的联接结构不同。例如,联接结构可以彼此相对(或镜像)。

第一像素电路PX00可以在第一行线时间期间向第一奇数编号列线CL00输出至少一个像素信号。第二像素电路PX01可以在第一行线时间期间向第一偶数编号列线CL01输出至少一个像素信号。第三像素电路PX10可以在第一行线时间期间向第二偶数编号列线CL11输出至少一个像素信号。第四像素电路PX11可以在第一行线时间期间向第二奇数编号列线CL10输出至少一个像素信号。

第一奇数编号列线CL00、第一偶数编号列线CL01、第二奇数编号列线CL10和第二偶数编号列线CL11可以在行方向上依次设置。每个单独的列线可以在列方向上延伸。

第一读出区域130可以包括第一读出电路ADC00和第三读出电路ADC01。第一读出电路ADC00可以读出从第一像素电路PX00生成的像素信号或从第二像素电路PX01生成的像素信号。例如,第一读出电路ADC00可以在第一帧时间期间读出从第一像素电路PX00生成的像素信号,并且在第二帧时间期间读出从第二像素电路PX01生成的像素信号。第三读出电路ADC01可以读出从第三像素电路PX10生成的像素信号或从第四像素电路PX11生成的像素信号。例如,第三读出电路ADC01可以在第一帧时间期间读出从第四像素电路PX11生成的像素信号,并且在第二帧时间期间读出从第三像素电路PX10生成的像素信号。

第二读出区域140可以包括第二读出电路ADC10和第四读出电路ADC11。第二读出电路ADC10可以读出从第一像素电路PX00生成的像素信号或从第二像素电路PX01生成的像素信号。例如,第二读出电路ADC10可以在第一帧时间期间读出从第二像素电路PX01生成的像素信号,并且在第二帧时间期间读出从第一像素电路PX00生成的像素信号。第四读出电路ADC11可以读出从第三像素电路PX10生成的像素信号或从第四像素电路PX11生成的像素信号。例如,第四读出电路ADC11可以在第一帧时间期间读出从第三像素电路PX10生成的像素信号,并且在第二帧时间期间读出从第四像素电路PX11生成的像素信号。

第一读出电路ADC00和第二读出电路ADC10可以对应于第一像素电路PX00和第二像素电路PX01,并且读出从第一像素电路PX00和第二像素电路PX01生成的像素信号。第三读出电路ADC01和第四读出电路ADC11可以对应于第三像素电路PX10和第四像素电路PX11,并且读出从第三像素电路PX10和第四像素电路PX11生成的像素信号。

路径改变区域150可以包括第一路径改变电路SW00和第二路径改变电路SW01。第一路径改变电路SW00可以基于第一控制信号SEL1来改变第一奇数编号列线CL00和第一偶数编号列线CL01与第一读出电路ADC00和第二读出电路ADC10之间的第一路径和第二路径。例如,第一路径改变电路SW00可以针对每个单位时间(即,在多个重复时间段中的每一个处或之内)改变第一路径和第二路径。第二路径改变电路SW01可以基于第二控制信号SEL2来改变第二奇数编号列线CL10和第二偶数编号列线CL11与第三读出电路ADC01和第四读出电路ADC11之间的第三路径和第四路径。例如,第二路径改变电路SW01可以针对每个单位时间改变第三路径和第四路径。

可以从控制器160生成第一控制信号SEL1和第二控制信号SEL2。在本实施方式中,可以针对每个单位时间以互相非反相的状态来生成第一控制信号SEL1和第二控制信号SEL2。例如,第一控制信号SEL1和第二控制信号SEL2可以是相同的信号。在一些实施方式中,第一控制信号SEL1和第二控制信号SEL2中的任何一个可以在每个单位时间转变,而另一个可以随机地生成。在一些实施方式中,第一控制信号SEL1和第二控制信号SEL2中的每一个可以随机地生成。单位时间可以是两个或更多个行线时间或者一个或更多个帧时间。

图3和图4是例示了图2所示的第一路径改变电路SW00和第二路径改变电路SW01的框图。

例如,图3和图4是例示了当第一控制信号SEL1和第二控制信号SEL2处于非反相状态时第一路径改变电路SW00和第二路径改变电路SW01的操作的框图。图3例示了当第一控制信号SEL1和第二控制信号SEL2各处于第一逻辑电平(例如,“0”)时,通过第一路径改变电路SW00和第二路径改变电路SW01形成的第一路径至第四路径的示例,并且图4例示了当第一控制信号SEL1和第二控制信号SEL2各处于第二逻辑电平(例如,“1”)时,通过第一路径改变电路SW00和第二路径改变电路SW01形成的第一路径至第四路径的示例。

如图3所示,当第一控制信号SEL1和第二控制信号SEL2各处于逻辑低电平(即,“0”)时,第一路径改变电路SW00可以改变第一路径和第二路径,使得第一奇数编号列线CL00联接至第一读出电路ADC00并且第一偶数编号列线CL01联接至第二读出电路ADC10,并且第二路径改变电路SW01可以改变第三路径和第四路径,使得第二奇数编号列线CL10联接至第三读出电路ADC01并且第二偶数编号列线CL11联接至第四读出电路ADC11。例如,第一路径和第二路径可以在列方向上平行地形成,并且第三路径和第四路径也可以在列方向上平行地形成。

如图4所示,当第一控制信号SEL1和第二控制信号SEL2各处于逻辑高电平(即,“1”)时,第一路径改变电路SW0可以改变第一路径和第二路径,使得第一奇数编号列线CL00联接至第二读出电路ADC10并且第一偶数编号列线CL01联接至第一读出电路ADC00,并且第二路径改变电路SW01可以改变第三路径和第四路径,使得第二奇数编号列线CL10联接至第四读出电路ADC11并且第二偶数编号列线CL11联接至第三读出电路ADC01。例如,第一路径和第二路径可以形成为彼此交叉,并且第三路径和第四路径也可以形成为彼此交叉。

在下文中,描述了根据第一实施方式的具有上述配置的图像感测装置100的操作。

在本实施方式中,作为示例描述了针对每个单个帧时间改变第一路径和第二路径以及第三路径和第四路径。

首先,下面描述在第一帧时间期间图像感测装置100的操作。

在第一帧时间期间,控制器160可以生成各自具有逻辑低电平(即,“0”)的第一控制信号SEL1和第二控制信号SEL2。第一路径改变电路SW00可以基于第一控制信号SEL1,改变列线(即,第一奇数编号列线CL00和第一偶数编号列线CL01)与读出电路(即,第一读出电路ADC00和第二读出电路ADC10)之间的第一路径和第二路径,使得第一像素电路PX00和第二像素电路PX01根据第一关系(即,第一对应关系)联接至第一读出电路ADC00和第二读出电路ADC10。例如,第一路径改变电路SW00可以改变第一路径和第二路径,使得第一奇数编号列线CL00联接至第一读出电路ADC00并且第一偶数编号列线CL01联接至第二读出电路ADC10(参照图3)。第二路径改变电路SW01可以基于第二控制信号SEL2,来改变列线(即,第二奇数编号列线CL10和第二偶数编号列线CL11)与读出电路(即,第三读出电路ADC01和第四读出电路ADC11)之间的第三路径和第四路径,使得第三像素电路PX10和第四像素电路PX11根据与第一关系不同的第二关系(即,第二对应关系)联接至第三读出电路ADC01和第四读出电路ADC11。例如,第二路径改变电路SW01可以改变第三路径和第四路径,使得第二奇数编号列线CL10联接至第三读出电路ADC01并且第二偶数编号列线CL11联接至第四读出电路ADC11(参照图3)。

在第一帧时间的第一行线时间期间,第一像素电路PX00可以通过第一奇数编号列线CL00输出至少一个像素信号,第二像素电路PX01可以通过第一偶数编号列线CL01输出至少一个像素信号,第三像素电路PX10可以通过第二偶数编号列线CL11输出至少一个像素信号,并且第四像素电路PX11可通过第二奇数编号列线CL10输出至少一个像素信号。

因此,第一读出电路ADC00可以读出第一像素电路PX00的像素信号,第二读出电路ADC10可以读出第二像素电路PX01的像素信号,第三读出电路ADC01可以读出第四像素电路PX11的像素信号,并且第四读出电路ADC11可以读出第三像素电路PX10的像素信号。

下面参照图5描述在第一帧时间期间图像感测装置100的操作。

图5是用于描述在第一读出区域130和第二读出区域140之间通过哪个读出区域读出从图2所示的第一像素电路PX00至第四像素电路PX11生成的像素信号的图。

参照图5,在第一帧时间的第一行线时间期间,可以通过第一读出区域130中所包括的第一读出电路ADC00读出从布置在第一行中的第一像素电路PX00和第三像素电路PX10生成的像素信号的一半像素信号,并且可以通过第二读出区域140中包括的第四读出电路ADC11读出像素信号的另一半像素信号。类似地,在第一帧时间的第一行线时间期间,可以通过第二读出区域140中包括的第二读出电路ADC10读出从布置在第二行中的第二像素电路PX01和第四像素电路PX11生成的像素信号的一半像素信号,并且可以通过第一读出区域130中包括的第三读出电路ADC01读出像素信号的另一半像素信号。

因此,可以以其中第一读出区域130中所包括的一些读出电路与第二读出区域140中所包括的一些读出电路基于相同行线而混合的形式读出像素信号。

接下来,下面描述在第二帧时间期间图像感测装置100的操作。

在第二帧时间期间,控制器160可以生成各自具有逻辑高电平(即,“1”)的第一控制信号SEL1和第二控制信号SEL2。第一路径改变电路SW00可以基于第一控制信号SEL1,来改变列线(即,第一奇数编号列线CL00和第一偶数编号列线CL01)与读出电路(即,第一读出电路ADC00和第二读出电路ADC10)之间的第一路径和第二路径,使得第一像素电路PX00和第二像素电路PX01根据第二关系联接至第一读出电路ADC00和第二读出电路ADC10。例如,第一路径改变电路SW00可以改变第一路径和第二路径,使得第一奇数编号列线CL00联接至第二读出电路ADC10,并且第一偶数编号列线CL01联接至第一读出电路ADC00(参照图4)。第二路径改变电路SW01可以基于第二控制信号SEL2,来改变列线(即,第二奇数编号列线CL10和第二偶数编号列线CL11)与读出电路(即,第三读出电路ADC01和第四读出电路ADC11)之间的第三路径和第四路径,使得第三像素电路PX10和第四像素电路PX11根据第一关系联接至第三读出电路ADC01和第四读出电路ADC11。例如,第二路径改变电路SW01可以改变第三路径和第四路径,使得第二奇数编号列线CL10联接至第四读出电路ADC11,并且第二偶数编号列线CL11联接至第三读出电路ADC01(参照图4)。

在第二帧时间的第一行线时间期间,第一像素电路PX00可以通过第一奇数编号列线CL00输出至少一个像素信号,第二像素电路PX01可以通过第一偶数编号列线CL01输出至少一个像素信号,第三像素电路PX10可以通过第二偶数编号列线CL11输出至少一个像素信号,并且第四像素电路PX11可以通过第二奇数编号列线CL10输出至少一个像素信号。

因此,第一读出电路ADC00可以读出第二像素电路PX01的像素信号,第二读出电路ADC10可以读出第一像素电路PX00的像素信号,第三读出电路ADC01可以读出第三像素电路PX10的像素信号,并且第四读出电路ADC11可以读出第四像素电路PX11的像素信号。

下面参照图6描述在第二帧时间期间图像感测装置100的操作。

图6是用于描述在第一读出区域130和第二读出区域140之间通过哪个读出区域读出从图2所示的第一像素电路PX00至第四像素电路PX11生成的像素信号的图。

参照图6,在第二帧时间的第一行线时间期间,可以通过第二读出区域140中包括的第二读出电路ADC10读出从布置在第一行中的第一像素电路PX00和第三像素电路PX10生成的像素信号的一半像素信号,并且可以通过第一读出区域130中包括的第三读出电路ADC01读出像素信号的另一半像素信号。类似地,在第二帧时间的第一行线时间期间,可以通过第一读出区域130中包括的第一读出电路ADC00读出从布置在第二行中的第二像素电路PX01和第四像素电路PX11生成的像素信号的一半像素信号,并且可以通过第二读出区域140中包括的第四读出电路ADC11读出像素信号的另一半像素信号。

因此,可以以其中第一读出区域130中包括的一些读出电路与第二读出区域140中包括的一些读出电路混合的形式的方式,从布置在每行中的像素电路读出像素信号。

另外,第一读出区域130中所包括的各个读出电路和第二读出区域140中所包括的各个读出电路可以在第一帧时间和第二帧时间期间交替地从相应的两个像素电路读出像素信号。

尽管在第一实施方式中作为示例描述了第一路径至第四路径针对每个单个帧时间改变,但是本公开不限于此。例如,在第一实施方式中,可以每两个或更多个行线时间或每两个或更多个帧时间,来改变第一路径至第四路径。另外,尽管在第一实施方式中作为示例描述了第一路径至第四路径在第一帧时间和第二帧时间期间连续地(即,规则地)改变,但是本公开不限于此。例如,在第一实施方式中,可以在第一帧时间和第二帧时间期间随机地改变第一路径至第四路径。

图7是例示了根据本公开的第二实施方式的图像感测装置200的框图。

参照图7,图像感测装置200可以包括行解码器210、像素阵列220、第一读出区域230、第二读出区域240、路径改变区域250和控制器260。

行解码器210可以控制像素阵列220的操作。例如,行解码器210可以以两行为单位控制像素阵列220。

像素阵列220可以包括布置在多个行和多个列的交叉处的多个像素电路。下面,具体参照图8描述多个像素电路。像素阵列220可以在行解码器210的控制下生成像素信号。例如,像素阵列220可以在第一行线时间期间从布置在第一行和第二行中的像素电路生成像素信号,并且在第n行线时间(其中,“n”是自然数)期间,从布置在第(2n-1)行和第2n行的像素电路生成像素信号。

第一读出区域230可以读出从像素阵列220生成的像素信号的一半像素信号。例如,第一读出区域230可以在第一行线时间期间读出从布置在第一行中的像素电路的一半像素电路生成的像素信号和从布置在第二行中的像素电路的一半像素电路生成的像素信号。

第二读出区域240可以读出从像素阵列220生成的像素信号的另一半像素信号。例如,第二读出区域240可以在第一行线时间期间读出从布置在第一行中的像素电路的另一半像素电路生成的像素信号以及从布置在第二行中的像素电路的另一半像素电路生成的像素信号。

路径改变区域250可以将从像素阵列220生成的像素信号的一半像素信号传送到第一读出区域230,并且可以将从像素阵列220生成的像素信号的另一半像素信号传送到第二读出区域240。

第一读出区域230、第二读出区域240和路径改变区域250可以设置在像素阵列220的一侧。具体地,路径改变区域250可以设置在像素阵列220与读出区域230和240之间。

控制器260可以控制行解码器210、第一读出区域230和第二读出区域240以及路径改变区域250的整体操作。例如,控制器260可以包括定时控制器。

图8是例示了图7所示的像素阵列220、第一读出区域230和第二读出区域240以及路径改变区域250中的每一个的一部分的框图。

参照图8,像素阵列220可以包括第一像素电路PX00、第一像素电路PX01、第三像素电路PX10和第四像素电路PX11。第一像素电路PX00和第二像素电路PX01可以布置在第一列中,并且第三像素电路PX10和第四像素电路PX11可以布置在第二列中。第一像素电路PX00和第三像素电路PX10可以布置在第一行中,并且第二像素电路PX01和第四像素电路PX11可以布置在第二行中。

第一像素电路PX00至第四像素电路PX11中的每一个可以包括至少一个像素。例如,第一像素电路PX00至第四像素电路PX11中的每一个可以包括单个像素或多个像素。多个像素可以具有共享每条列线的结构。

第一像素电路PX00可以联接至第一奇数编号列线CL00。第二像素电路PX01可以联接至第一偶数编号列线CL01。第三像素电路PX10可以联接至第二奇数编号列线CL10。第四像素电路PX11可以联接至第二偶数编号列线CL11。可以看出,第一像素电路PX00、第二像素电路PX01、第一奇数编号列线CL00和第一偶数编号列线CL01的联接结构与第三像素电路PX10、第四像素电路PX11、第二奇数编号列线CL10和第二偶数编号列线CL11的联接结构相同。

第一像素电路PX00可以在第一行线时间期间向第一奇数编号列线CL00输出至少一个像素信号。第二像素电路PX01可以在第一行线时间期间向第一偶数编号列线CL01输出至少一个像素信号。第三像素电路PX10可以在第一行线时间期间向第二奇数编号列线CL10输出至少一个像素信号。第四像素电路PX11可以在第一行线时间期间向第二偶数编号列线CL11输出至少一个像素信号。

第一奇数编号列线CL00、第一偶数编号列线CL01、第二奇数编号列线CL10和第二偶数编号列线CL11中的每一个可以在列方向上延伸,而列线在行方向上依次设置。

第一读出区域230可以包括第一读出电路ADC00和第三读出电路ADC01。第一读出电路ADC00可以读出从第一像素电路PX00生成的像素信号或从第二像素电路PX01生成的像素信号。例如,第一读出电路ADC00可以在第一帧时间期间读出从第一像素电路PX00生成的像素信号,并且在第二帧时间期间读出从第二像素电路PX01生成的像素信号。第三读出电路ADC01可以读出从第三像素电路PX10生成的像素信号或从第四像素电路PX11生成的像素信号。例如,第三读出电路ADC01可以在第一帧时间期间读出从第四像素电路PX11生成的像素信号,并且在第二帧时间期间读出从第三像素电路PX10生成的像素信号。

第二读出区域240可以包括第二读出电路ADC10和第四读出电路ADC11。第二读出电路ADC10可以读出从第一像素电路PX00生成的像素信号或从第二像素电路PX01生成的像素信号。例如,第二读出电路ADC10可以在第一帧时间期间读出从第二像素电路PX01生成的像素信号,并且在第二帧时间期间读出从第一像素电路PX00生成的像素信号。第四读出电路ADC11可以读出从第三像素电路PX10生成的像素信号或从第四像素电路PX11生成的像素信号。例如,第四读出电路ADC11可以在第一帧时间期间读出从第三像素电路PX10生成的像素信号,并且在第二帧时间期间读出从第四像素电路PX11生成的像素信号。

第一读出电路ADC00和第二读出电路ADC10可以对应于第一像素电路PX00和第二像素电路PX01,并且读出从第一像素电路PX00和第二像素电路PX01生成的像素信号。第三读出电路ADC01和第四读出电路ADC11可以对应于第三像素电路PX10和第四像素电路PX11,并且读出从第三像素电路PX10和第四像素电路PX11生成的像素信号。

路径改变区域250可以包括第一路径改变电路SW00和第二路径改变电路SW01。第一路径改变电路SW00可以基于第一控制信号SEL1来改变第一奇数编号列线CL00和第一偶数编号列线CL01与第一读出电路ADC00和第二读出电路ADC10之间的第一路径和第二路径。第一路径改变电路SW00可以针对每个单位时间改变第一路径和第二路径。第二路径改变电路SW01可以基于第二控制信号SEL2来改变第二奇数编号列线CL10和第二偶数编号列线CL11与第三读出电路ADC01和第四读出电路ADC11之间的第三路径和第四路径。第二路径改变电路SW01可以针对每个单位时间改变第三路径和第四路径。

可以从控制器160生成第一控制信号SEL1和第二控制信号SEL2。在本实施方式中,可以针对每个单位时间以互相反相的状态来生成第一控制信号SEL1和第二控制信号SEL2。在一些实施方式中,第一控制信号SEL1和第二控制信号SEL2中的任何一个可以针对每个单位时间转变,并且另一个可以随机地生成。在一些实施方式中,第一控制信号SEL1和第二控制信号SEL2中的每一个可以随机地生成。单位时间可以包括两个或更多个行线时间以及一个或更多个帧时间中的任何一个。

图9和图10是例示了图8所示的第一路径改变电路SW00和第二路径改变电路SW01的框图。

例如,图9和图10例示了当第一控制信号SEL1和第二控制信号SEL2处于反相状态时第一路径改变电路SW00和第二路径改变电路SW01的操作。图9例示了当第一控制信号SEL1处于第一逻辑电平(例如,“0”)并且第二控制信号SEL2处于第二逻辑电平(例如,“1”)时,通过第一路径改变电路SW00和第二路径改变电路SW01形成的第一路径至第四路径的示例,并且图10例示了当第一控制信号SEL1处于第二逻辑电平(例如,“1”)并且第二控制信号SEL2处于第一逻辑电平(例如,“0”)时,通过第一路径改变电路SW00和第二路径改变电路SW01形成的第一路径至第四路径的示例。

如图9所示,当第一控制信号SEL1处于逻辑低电平(即,“0”)并且第二控制信号SEL2处于逻辑高电平(即,“1”)时,第一路径改变电路SW00可以改变第一路径和第二路径,使得第一奇数编号列线CL00联接至第一读出电路ADC00并且第一偶数编号列线CL01联接至第二读出电路ADC10,并且第二路径改变电路SW01可以改变第三路径和第四路径,使得第二奇数编号列线CL10联接至第四读出电路ADC11并且第二偶数编号列线CL11联接至第三读出电路ADC01。例如,第一路径和第二路径可以在列方向上平行地形成,并且第三路径和第四路径可以形成为彼此交叉。

如图10所示,当第一控制信号SEL1处于逻辑高电平(即,“1”)并且第二控制信号SEL2处于逻辑低电平(即,“0”)时,第一路径改变电路SW0可以改变第一路径和第二路径,使得第一奇数编号列线CL00联接至第二读出电路ADC10并且第一偶数编号列线CL01联接至第一读出电路ADC00,并且第二路径改变电路SW01可以改变第三路径和第四路径,使得第二奇数编号列线CL10联接至第三读出电路ADC01并且第二偶数编号列线CL11联接至第四读出电路ADC11。例如,第一路径和第二路径可以形成为彼此交叉,并且第三路径和第四路径可以在列方向上平行地形成。

在下文中,描述了根据第二实施方式的具有上述配置的图像感测装置200的操作。

在本实施方式中,作为示例描述了针对每个单个帧时间改变第一路径和第二路径以及第三路径和第四路径。

首先,下面描述在第一帧时间期间图像感测装置200的操作。

在第一帧时间期间,控制器260可以生成具有逻辑低电平(即,“0”)的第一控制信号SEL1和具有逻辑高电平(即,“1”)的第二控制信号SEL2。第一路径改变电路SW00可以基于第一控制信号SEL1来改变列线(即,第一奇数编号列线CL00和第一偶数编号列线CL01)与读出电路(即,第一读出电路ADC00和第二读出电路ADC10)之间的第一路径和第二路径,使得第一像素电路PX00和第二像素电路PX01根据第一关系联接至第一读出电路ADC00和第二读出电路ADC10。例如,第一路径改变电路SW00可以改变第一路径和第二路径,使得第一奇数编号列线CL00联接至第一读出电路ADC00,并且第一偶数编号列线CL01联接至第二读出电路ADC10(参照图9)。第二路径改变电路SW01可以基于第二控制信号SEL2来改变列线(即,第二奇数编号列线CL10和第二偶数编号列线CL11)与读出电路(即,第三读出电路ADC01和第四读出电路ADC11)之间的第三路径和第四路径,使得第三像素电路PX10和第四像素电路PX11根据与第一关系不同的第二关系联接至第三读出电路ADC01和第四读出电路ADC11。例如,第二路径改变电路SW01可以改变第三路径和第四路径,使得第二奇数编号列线CL10联接至第四读出电路ADC11,并且第二偶数编号列线CL11联接至第三读出电路ADC01(参照图9)。

在第一帧时间的第一行线时间期间,第一像素电路PX00可以通过第一奇数编号列线CL00输出至少一个像素信号,第二像素电路PX01可以通过第一偶数编号列线CL01输出至少一个像素信号,第三像素电路PX10可以通过第二奇数编号列线CL10输出至少一个像素信号,并且第四像素电路PX11可以通过第二偶数编号列线CL11输出至少一个像素信号。

因此,第一读出电路ADC00可以读出第一像素电路PX00的像素信号,第二读出电路ADC10可以读出第二像素电路PX01的像素信号,第三读出电路ADC01可以读出第四像素电路PX11的像素信号,并且第四读出电路ADC11可以读出第三像素电路PX10的像素信号。

下面参照图11描述在第一帧时间期间图像感测装置200的操作。

图11是用于描述在第一读出区域230和第二读出区域240之间通过哪个读出区域读出从图8所示的第一像素电路PX00至第四像素电路PX11生成的像素信号的图。

参照图11,在第一帧时间的第一行线时间期间,可以通过第一读出区域230中包括的第一读出电路ADC00读出从布置在第一行中的第一像素电路PX00和第三像素电路PX10生成的像素信号的一半像素信号,可以通过第二读出区域240中包括的第四读出电路ADC11读出像素信号的另一半像素信号。类似地,在第一帧时间的第一行线时间期间,可以通过第二读出区域240中包括的第二读出电路ADC10读出从布置在第二行中的第二像素电路PX01和第四像素电路PX11生成的像素信号的一半像素信号,并且可以通过第一读出区域230中包括的第三读出电路ADC01读出像素信号的另一半像素信号。

因此,可以以其中第一读出区域230中所包括的一些读出电路和第二读出区域240中所包括的一些读出电路基于相同行线而混合的形式读出像素信号。

接下来,下面描述在第二帧时间期间图像感测装置200的操作。

在第二帧时间期间,控制器260可以生成具有逻辑高电平(即,“1”)的第一控制信号SEL1和具有逻辑低电平(即,“0”)的第二控制信号SEL2。第一路径改变电路SW00可以基于第一控制信号SEL1来改变列线(即,第一奇数编号列线CL00和第一偶数编号列线CL01)与读出电路(即,第一读出电路ADC00和第二读出电路ADC10)之间的第一路径和第二路径,使得第一像素电路PX00和第二像素电路PX01根据第二关系联接至第一读出电路ADC00和第二读出电路ADC10。例如,第一路径改变电路SW00可以改变第一路径和第二路径,使得第一奇数编号列线CL00联接至第二读出电路ADC10,并且第一偶数编号列线CL01联接至第一读出电路ADC00(参照图10)。第二路径改变电路SW01可以基于第二控制信号SEL2来改变列线(即,第二奇数编号列线CL10和第二偶数编号列线CL11)与读出电路(即,第三读出电路ADC01和第四读出电路ADC11)之间的第三路径和第四路径,使得第三像素电路PX10和第四像素电路PX11根据第一关系联接至第三读出电路ADC01和第四读出电路ADC11。例如,第二路径改变电路SW01可以改变第三路径和第四路径,使得第二奇数编号列线CL10联接至第三读出电路ADC01,并且第二偶数编号列线CL11联接至第四读出电路ADC11(参照图10)。

在第二帧时间的第一行线时间期间,第一像素电路PX00可以通过第一奇数编号列线CL00输出至少一个像素信号,第二像素电路PX01可以通过第一偶数编号列线CL01输出至少一个像素信号,第三像素电路PX10可以通过第二奇数编号列线CL10输出至少一个像素信号,并且第四像素电路PX11可以通过第二偶数编号列线CL11输出至少一个像素信号。

因此,第一读出电路ADC00可以读出第二像素电路PX01的像素信号,第二读出电路ADC10可以读出第一像素电路PX00的像素信号,第三读出电路ADC01可以读出第三像素电路PX10的像素信号,并且第四读出电路ADC11可以读出第四像素电路PX11的像素信号。

下面参照图12描述在第二帧时间期间图像感测装置200的操作。

图12是用于描述在第一读出区域230和第二读出区域240之间通过哪个读出区域读出从图8所示的第一像素电路PX00至第四像素电路PX11生成的像素信号的图。

参照图12,在第二帧时间的第一行线时间中,可以通过第二读出区域240中包括的第二读出电路ADC10读出从布置在第一行中的第一像素电路PX00和第三像素电路PX10生成的像素信号的一半像素信号,并且可以通过第一读出区域230中包括的第三读出电路ADC01读出像素信号的另一半像素信号。类似地,在第二帧时间的第一行线时间期间,可以通过第一读出区域230中包括的第一读出电路ADC00读出从布置在第二行中的第二像素电路PX01和第四像素电路PX11生成的像素信号的一半像素信号,并且可以通过第二读出区域240中包括的第四读出电路ADC11读出像素信号的另一半像素信号。

因此,可以以其中第一读出区域230中所包括的一些读出电路和第二读出区域240中所包括的一些读出电路混合的形式,从布置在每行中的像素电路读出像素信号。

另外,第一读出区域230中所包括的各个读出电路和第二读出区域240中所包括的各个读出电路可以在第一帧时间和第二帧时间期间交替地从对应的两个像素电路读出像素信号。

尽管在第二实施方式中作为示例描述了第一路径至第四路径针对每个单个帧时间改变,但是本公开不限于此。例如,在第二实施方式中,可以每两个或更多个行线时间或每两个或更多个帧时间,改变第一路径至第四路径。另外,尽管在第二实施方式中作为示例描述了第一路径至第四路径在第一帧时间和第二帧时间期间连续地(即,规则地)改变,但是本公开不限于此。例如,在第二实施方式中,可以在第一帧时间和第二帧时间期间随机地改变第一路径至第四路径。

图13是例示了根据本公开的第三实施方式的图像感测装置300的框图。

参照图13,图像感测装置300可以包括行解码器310、像素阵列320、第一读出区域330、第二读出区域340、路径改变区域350和控制器360。

行解码器310可以控制像素阵列320的操作。例如,行解码器310可以以两行为单位控制像素阵列320。

像素阵列320可以包括布置在多个行和多个列的交叉处的多个像素电路。下面,具体参照图14描述多个像素电路。像素阵列320可以在行解码器310的控制下生成像素信号。例如,像素阵列320可以在第一行线时间期间从布置在第一行和第二行中的像素电路生成像素信号,并且在第n行线时间(其中,“n”是自然数)期间,从布置在第(2n-1)行和第2n行的像素电路生成像素信号。

第一读出区域330可以读出从像素阵列320生成的像素信号的一半像素信号。例如,第一读出区域330可以在第一行线时间期间读出从布置在第一行中的像素电路的一半像素电路生成的像素信号和从布置在第二行中的像素电路的一半像素电路生成的像素信号。

第二读出区域340可以读出从像素阵列320生成的像素信号的另一半像素信号。例如,第二读出区域340可以在第一行线时间期间读出从布置在第一行中的像素电路的另一半像素电路生成的像素信号以及从布置在第二行中的像素电路的另一半像素电路生成的像素信号。

路径改变区域350可以将从像素阵列320生成的像素信号的一半像素信号传送到第一读出区域330,并且将从像素阵列320生成的像素信号的另一半像素信号传送到第二读出区域340。

第一读出区域330、第二读出区域340和路径改变区域350可以设置在像素阵列320的一侧。具体地,路径改变区域350可以设置在像素阵列320与读出区域330和340之间。

控制器360可以控制行解码器31、第一读出区域330和第二读出区域340以及路径改变区域350的整体操作。例如,控制器360可以包括定时控制器。

图14是例示了图13所示的像素阵列320、第一读出区域330和第二读出区域340以及路径改变区域350中的每一个的一部分的框图。

参照图14,像素阵列320可以包括第一像素电路PX00、第二像素电路PX01、第三像素电路PX10和第四像素电路PX11。第一像素电路PX00和第二像素电路PX01可以布置在第一列中,并且第三像素电路PX10和第四像素电路PX11可以布置在第二列中。第一像素电路PX00和第三像素电路PX10可以布置在第一行中,并且第二像素电路PX01和第四像素电路PX11可以布置在第二行中。

第一像素电路PX00至第四像素电路PX11中的每一个可以包括至少一个像素。例如,第一像素电路PX00至第四像素电路PX11中的每一个可以包括单个像素或多个像素。多个像素可以具有共享每条列线的结构。

第一像素电路PX00可以联接至第一奇数编号列线CL00。第二像素电路PX01可以联接至第一偶数编号列线CL01。第三像素电路PX10可以联接至第二奇数编号列线CL10。第四像素电路PX11可以联接至第二偶数编号列线CL11。可以看出,第一像素电路PX00、第二像素电路PX01、第一奇数编号列线CL00和第一偶数编号列线CL01的联接结构与第三像素电路PX10、第四像素电路PX11、第二奇数编号列线CL10和第二偶数编号列线CL11的联接结构相同。

第一像素电路PX00可以在第一行线时间期间向第一奇数编号列线CL00输出至少一个像素信号。第二像素电路PX01可以在第一行线时间期间向第一偶数编号列线CL01输出至少一个像素信号。第三像素电路PX10可以在第一行线时间期间向第二奇数编号列线CL10输出至少一个像素信号。第四像素电路PX11可以在第一行线时间期间向第二偶数编号列线CL11输出至少一个像素信号。

第一奇数编号列线CL00、第一偶数编号列线CL01、第二奇数编号列线CL10和第二偶数编号列线CL11可以在列方向上延伸,并且在行方向上依次设置。

第一读出区域330可以包括第一读出电路ADC00和第三读出电路ADC01。第一读出电路ADC00可以读出从第一像素电路PX00生成的像素信号或从第二像素电路PX01生成的像素信号。例如,第一读出电路ADC00可以在第一帧时间期间读出从第一像素电路PX00生成的像素信号,并且在第二帧时间期间读出从第二像素电路PX01生成的像素信号。第三读出电路ADC01可以读出从第三像素电路PX10生成的像素信号或从第四像素电路PX11生成的像素信号。例如,第三读出电路ADC01可以在第一帧时间期间读出从第四像素电路PX11生成的像素信号,并且在第二帧时间期间读出从第三像素电路PX10生成的像素信号。

第二读出区域340可以包括第二读出电路ADC10和第四读出电路ADC11。第二读出电路ADC10可以读出从第一像素电路PX00生成的像素信号或从第二像素电路PX01生成的像素信号。例如,第二读出电路ADC10可以在第一帧时间期间读出从第二像素电路PX01生成的像素信号,并且在第二帧时间期间读出从第一像素电路PX00生成的像素信号。第四读出电路ADC11可以读出从第三像素电路PX10生成的像素信号或从第四像素电路PX11生成的像素信号。例如,第四读出电路ADC11可以在第一帧时间期间读出从第三像素电路PX10生成的像素信号,并且在第二帧时间期间读出从第四像素电路PX11生成的像素信号。

第一读出电路ADC00和第二读出电路ADC10可以对应于第一像素电路PX00和第二像素电路PX01,并且读出从第一像素电路PX00和第二像素电路PX01生成的像素信号。第三读出电路ADC01和第四读出电路ADC11可以对应于第三像素电路PX10和第四像素电路PX11,并且读出从第三像素电路PX10和第四像素电路PX11生成的像素信号。

路径改变区域350可以包括路径控制电路PS以及第一路径改变电路SW00和第二路径改变电路SW01。路径控制电路PS可以基于第一控制信号SEL1和第二控制信号SEL2来生成第三控制信号SEL3。第一路径改变电路SW00可以基于第一控制信号SEL1来改变第一奇数编号列线CL00和第一偶数编号列线CL01与第一读出电路ADC00和第二读出电路ADC10之间的第一路径和第二路径。第一路径改变电路SW00可以针对每个单位时间改变第一路径和第二路径。第二路径改变电路SW01可以基于第二控制信号SEL2来改变第二奇数编号列线CL10和第二偶数编号列线CL11与第三读出电路ADC01和第四读出电路ADC11之间的第三路径和第四路径。第二路径改变电路SW01可以针对每个单位时间改变第三路径和第四路径。

可以从控制器360生成第一控制信号SEL1和第二控制信号SEL2。在本实施方式中,可以针对每个单位时间以互相反相的状态来生成第一控制信号SEL1和第二控制信号SEL2。在一些实施方式中,第一控制信号SEL1和第二控制信号SEL2中的任何一个可以在每个单位时间转变(即,规则地生成),并且另一个可以随机地生成。在一些实施方式中,第一控制信号SEL1和第二控制信号SEL2中的每一个可以随机地生成。单位时间可以包括两个或更多个行线时间以及一个或更多个帧时间中的任何一个。

图15是例示了图14所示的路径控制电路PS的电路图。

参照图15,路径控制电路PS可以包括第一开关元件SC0和第二开关元件SC1。

第一开关元件SC0可以基于第二控制信号SEL2输出第一反相控制信号/SEL1作为第三控制信号SEL3。第一反相控制信号/SEL1可以是通过将第一控制信号SEL反相而获得的信号。

第二开关元件SC1可以基于第二反相控制信号/SEL2,输出第一控制信号SEL1作为第三控制信号SEL3。第二反相控制信号/SEL2可以是通过将第二控制信号SEL2反相而获得的信号。

图16至图19是用于描述图14所示的第一路径改变电路SW00和第二路径改变电路SW01的框图。

如图16所示,第一路径改变电路SW00可以改变第一路径和第二路径,使得第一奇数编号列线CL00联接至第一读出电路ADC00,并且第一偶数编号列线CL01联接至第二读出电路ADC10,并且第二路径改变电路SW01可以改变第三路径和第四路径,使得第二奇数编号列线CL10联接至第四读出电路ADC11,并且第二偶数编号列线CL11联接至第三读出电路ADC01。例如,第一路径和第二路径可以在列方向上平行地形成,并且第三路径和第四路径可以形成为彼此交叉。

如图17所示,第一路径改变电路SW00可以改变第一路径和第二路径,使得第一奇数编号列线CL00联接至第一读出电路ADC00,并且第一偶数编号列线CL01联接至第二读出电路ADC10,并且第二路径改变电路SW01可以改变第三路径和第四路径,使得第二奇数编号列线CL10联接至第三读出电路ADC01,并且第二偶数编号列线CL11联接至第四读出电路ADC11。例如,第一路径和第二路径可以在列方向上平行地形成,并且第三路径和第四路径也可以在列方向上平行地形成。

如图18所示,第一路径改变电路SW00可以改变第一路径和第二路径,使得第一奇数编号列线CL00联接至第二读出电路ADC10,并且第一偶数编号列线CL01联接至第一读出电路ADC00,并且第二路径改变电路SW01可以改变第三路径和第四路径,使得第二奇数编号列线CL10联接至第三读出电路ADC01,并且第二偶数编号列线CL11联接至第四读出电路ADC11。例如,第一路径和第二路径可以形成为彼此交叉,并且第三路径和第四路径可以在列方向上平行地形成。

如图19所示,第一路径改变电路SW00可以改变第一路径和第二路径,使得第一奇数编号列线CL00联接至第二读出电路ADC10,并且第一偶数编号列线CL01联接至第一读出电路ADC00,并且第二路径改变电路SW01可以改变第三路径和第四路径,使得第二奇数编号列线CL10联接至第四读出电路ADC11,并且第二偶数编号列线CL11联接至第三读出电路ADC01。例如,第一路径和第二路径可以形成为彼此交叉,并且第三路径和第四路径也可以形成为彼此交叉。

在第三实施方式中,如图16至图19中的任何一个所示,可以针对每个单位时间形成第一路径至第四路径。换句话说,在第三实施方式中,第一路径至第四路径可以针对每个单位时间随机地改变。

根据本公开的实施方式,以其中第一读出区域中的一些读出电路和第二读出区域中的一些读出电路基于相同行线而混合的形式来读出像素信号,从而减少第一读出区域中的读出电路与第二读出区域中的读出电路之间的不匹配。另外,根据本公开的实施方式,当第一路径至第四路径随机地改变而不是规则地改变时,可以进一步减小第一读出区域中的读出电路与第二读出区域中的读出电路之间的不匹配。

从以上描述显而易见的是,在根据实施方式的图像感测装置中,减小了读出电路之间发生失配的可能性,从而减小了行固定图案噪声(RFPN)。

尽管已经参照特定实施方式例示和描述了本公开,但是所公开的实施方式并非旨在限制性的。此外,应注意,在不脱离本发明的精神和/或范围的情况下,如本领域技术人员根据本公开将认识到的,可以通过替代、改变和修改以各种方式来实现本发明。本发明旨在涵盖落入所附权利要求的范围内的所有这样的替代、改变和修改。

相关申请的交叉引用

本申请要求于2019年12月16日提交的韩国专利申请No.2019-0167890的优先权,该韩国专利申请的全部内容通过引用合并于本文中。

- 图像感测装置的镜头安装组件和图像感测装置及其制造方法

- 图像感测装置及图像感测装置的控制方法