借助于额外导线来进行电网优化的方法与设备

文献发布时间:2023-06-19 11:29:13

技术领域

本发明涉及电子电路,尤指一种借助于额外导线来进行电网优化(power meshoptimization)的方法以及相关设备(apparatus)诸如一生产工具。

背景技术

相关技术中的时钟树合成(clock tree synthesis,CTS)方法可以很容易地带来某些问题,诸如电压衰退(voltage drop;或IR压降(IR drop))、电磁干扰(electromagnetic interference,EMI)等。尤其,在设计时间的后期,当发现这些问题时,可以用来解决这些问题的侦错方法不多,并且侦错可耗费许多时间。此外,如果具有这些问题的区域的各自的布线(routing)已经很拥挤,这些问题可能无法被有效地解决。因此,需要一种新颖的方法及相关架构,以在没有副作用或较不可能带来副作用的状况下解决相关技术的问题。

发明内容

本发明的一目的在于提供一种借助于额外导线来进行电网优化的方法以及相关设备诸如一生产工具,以解决上述的问题。

本发明的至少一实施例提供一种借助于额外导线来进行电网优化的方法,其中该方法可应用于(applicable to)时钟树(clock tree)。该方法可包含:读取一时钟元件(clock cell)定义文件以取得于一电路设计中的多个时钟元件的各自的基本信息,其中该多个时钟元件中的一个时钟元件的基本信息至少指出该时钟元件的一类型以及一大小;以及依据该多个时钟元件的各自的基本信息,执行一电网优化程序以产生一电网优化结果。例如,该电网优化程序可包含:针对于该多个时钟元件当中的多个类型的时钟元件中的任一类型的时钟元件,依据任一类型的时钟元件的各自的大小将任一类型的时钟元件分类为(classify into)多个子类型;以及对该多个子类型中的一组子类型的各自的时钟元件进行电网增强,以于该组子类型中的任一子类型的每一时钟元件加上跨接于原本电网中的一组原本导线的一组额外导线作为一组优化电网,其中该组优化电网的一导线宽度对应于任一子类型,以及该电网优化结果包含该原本电网以及该组优化电网。

除了上述方法外,本发明亦提供一种依据上述的方法来操作的设备,其中该设备可包含一处理电路以及耦接至该处理电路的一储存装置。例如,该处理电路可用来执行对应于该方法的一程序代码以控制该生产工具的操作,以执行该电网优化程序。另外,该储存装置可用来储存该时钟元件定义文件,以供被该处理电路读取。

本发明所提出的方法以及相关设备能确保依据该电路设计生产的电子装置能在各种状况下妥善地操作。此外,依据本发明的相关实施例来实施并不会增加许多额外成本。因此,相关技术的问题可被妥善地解决。相较于相关技术,本发明能在没有副作用或较不可能带来副作用的状况下于电子装置中实现强健的电网。

附图说明

图1为依据本发明一实施例的一种借助于额外导线来进行电网优化的设备的示意图。

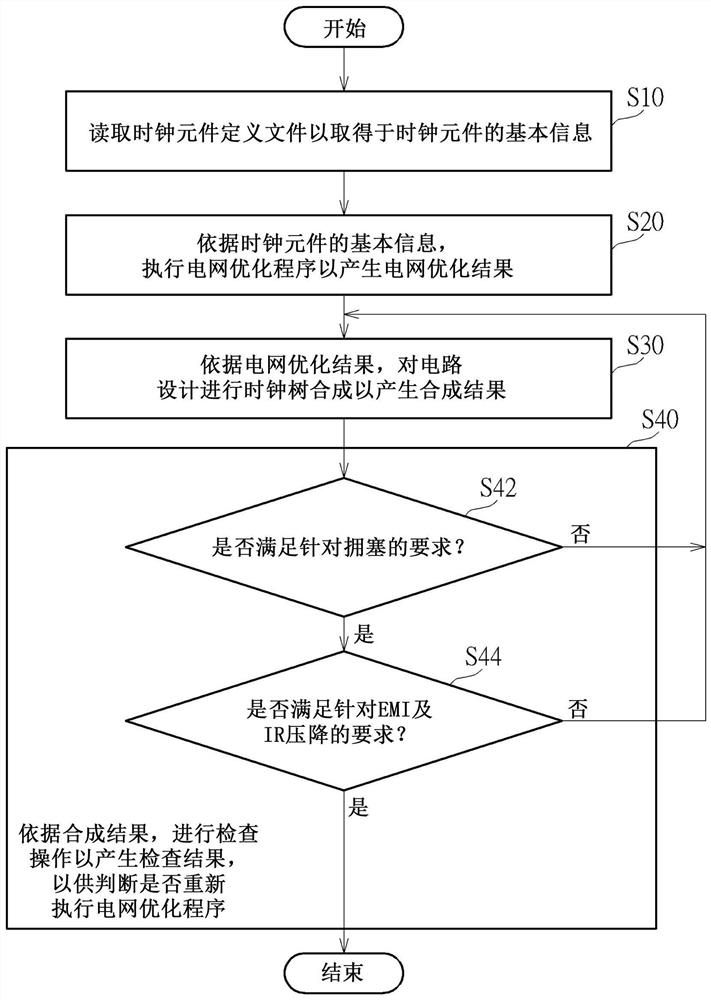

图2为依据本发明一实施例的一种借助于额外导线来进行电网优化的方法的流程图。

图3示出图2所示方法于本发明一实施例中的电网优化程序的一工作流程。

图4示出执行图3所示电网优化程序前的电路架构的例子。

图5示出图2所示方法于本发明一实施例中所产生的一电网优化结果。

图6示出图2所示方法于本发明一实施例中所产生的一组优化电网。

图7示出图2所示方法于本发明一实施例中的宽度控制方案。

图8示出图2所示方法于本发明一实施例中所涉及的多层架构。

具体实施方式

图1为依据本发明一实施例的一种借助于额外导线来进行电网优化的设备100的示意图,其中设备100可为用来进行电网优化的一生产工具。设备100可包含一处理电路110、至少一储存装置诸如储存装置120、一网络接口电路130等,而上列元件可通过一总线105彼此耦接,但本发明不限于此。于某些实施例中,图1所示架构可予以变化。如图1所示,处理电路110可执行至少一预定程序代码以控制设备100的操作,储存装置120可为设备100储存信息,而网络接口电路130可将设备100耦接到至少一网络以提供至少一网络服务给设备100。基于图1所示架构,在一电路设计时间的初期,设备100可为一用户诸如一电路设计者预先进行有效率的优化操作,以解决相关技术中的问题。

于上述实施例中,设备100可通过执行上述至少一预定程序代码的个人计算机等方式来实施;处理电路110可通过中央处理器(Central Processing Unit,CPU)、内存、芯片组等方式来实施。

图2为依据本发明一实施例的一种借助于额外导线来进行电网优化的方法的流程图。该方法可应用于(applicable to)时钟树(clock tree),尤其,时钟树合成(clock treesynthesis,CTS)。例如,处理电路110可用来执行对应于该方法的一程序代码112以控制设备100(诸如该生产工具)的操作,以执行一电网优化程序(procedure),其中程序代码112可作为上述至少一预定程序代码的例子。

于步骤S10中,处理电路110可读取一时钟元件(clock cell)定义文件122以取得于一电路设计中的多个时钟元件的各自的基本信息,其中该多个时钟元件中的一时钟元件的基本信息至少指出该时钟元件的类型、大小等,尤其,还指出该时钟元件的名字与位置。于是,处理电路110可从时钟元件定义文件122取得该多个时钟元件的各自的名字、位置、类型、大小等。依据本实施例,储存装置120可用来储存多个档案诸如时钟元件定义文件122,以被处理电路110读取。

于步骤S20中,处理电路110可依据该多个时钟元件的上述各自的基本信息,执行该电网优化程序以产生一电网优化结果。

于步骤S30中,处理电路110可依据该电网优化结果,对该电路设计进行上述时钟树合成以产生一合成结果,其中该合成结果可指出该电路设计中的至少一时钟树的布线。例如,处理电路110可读取一设计规范(design specification)文件124以取得该电路设计的设计规范(例如该电路设计的电路架构的大小、时钟树要求诸如时钟周期的目标范围等),以供进行上述时钟树合成,且可将该合成结果储存于一电网优化记录文件126。依据本实施例,时钟元件定义文件122与设计规范文件124优选由该用户诸如该电路设计者提供,但本发明不限于此。

于步骤S40中,处理电路110可依据该合成结果,进行至少一检查操作以产生至少一检查结果,以供判断是否重新执行该电网优化程序,其中上述至少一检查结果可指出上述至少一时钟树的上述布线是否满足针对至少一检查项目(例如拥塞(congestion)、IR压降、EMI等)的要求。依据本实施例,步骤S40可包含多个子步骤诸如步骤S42与S44。

于步骤S42中,处理电路110可判断该合成结果是否满足针对拥塞的要求。如果是,执行步骤S44;如果否,执行步骤S30。例如针对拥塞的要求可包含:不超过50个拥塞点。

于步骤S44中,处理电路110可判断该合成结果是否满足针对EMI及IR压降的要求。如果是,结束此工作流程,例如,进入下一阶段的操作;如果否,执行步骤S30。

基于图2所示的工作流程,因应上述至少一检查结果(例如该多个子步骤诸如步骤S42与S44的检查结果),处理电路110可依据该电网优化程序的至少一更新的参数来重新执行该电网优化程序以更新该电网优化结果。于是,在进入下一阶段的操作以前,设备100可为该用户诸如该电路设计者预先进行有效率的优化操作,而非如相关技术中在设计时间的后期尝试侦错,以彻底解决相关技术中的相当扰人的问题。

为了更好地理解,该方法可用图2所示的工作流程来说明,但本发明不限于此。依据某些实施例,一个或多个步骤可于图2所示的工作流程中增加、删除或修改。

图3示出图2所示方法于本发明一实施例中的该电网优化程序的一工作流程。

于步骤S21中,处理电路110可选择该多个时钟元件当中的多个类型的时钟元件中的一类型的时钟元件。该多个类型的时钟元件可包含:

(A)类型A的时钟元件,包含:缓冲器(buffer)与反向器(inverter);

(B)类型B的时钟元件,包含:多任务器(multiplexer,MUX);

(C)类型C的时钟元件,包含:或非门(NOR gate);

(D)类型D的时钟元件,包含:与门(AND gate);

但本发明不限于此。

于步骤S22中,处理电路110可依据(于步骤S21中刚刚选择的)该类型的时钟元件的各自的大小将该类型的时钟元件分类为(classify into)多个子类型,其中该多个子类型分别对应于不同大小范围。例如,当类型A被选择,其子类型可包含子类型A1、A2等;当类型B被选择,其子类型可包含子类型B1、B2等;当类型C被选择,其子类型可包含子类型C1、C2等;以及当类型D被选择,其子类型可包含子类型D1、D2等。

于步骤S23中,处理电路110可对(于步骤S22中刚刚分类的)该多个子类型中的一组子类型的各自的时钟元件进行电网增强,以于该组子类型中的任一子类型的每一时钟元件加上跨接于原本电网中的一组原本导线的一组额外导线作为一组优化电网,其中该组优化电网的一导线宽度对应于上述任一子类型,且该电网优化结果包含该原本电网以及该组优化电网。

于步骤S23A中,处理电路110可选择该组子类型中的一子类型。

于步骤S23B中,处理电路110可于(步骤S23A中刚刚选择的)该子类型的每一时钟元件加上跨接于该原本电网中的一组原本导线的一组额外导线作为一组优化电网。

于步骤S23C中,处理电路110可判断是否针对该组子类型中的全部子类型的时钟元件的处理已完成。如果是,执行步骤S24;如果否,执行步骤S23A,以针对该组子类型中的下一个子类型的时钟元件进行处理。

于步骤S24中,处理电路110可判断是否针对全部类型的时钟元件的处理已完成。如果是,结束此工作流程以执行步骤S30;如果否,执行步骤S21,以针对该多个类型的时钟元件中的下一个类型的时钟元件进行处理。

基于图3所示的工作流程,针对于该多个类型的时钟元件中的任一类型的时钟元件,处理电路110可依据上述任一类型的时钟元件的各自的大小将上述任一类型的时钟元件分类为其子类型,且可分别对这些子类型中的一部分子类型的时钟元件进行电网增强,以分别于该部分子类型的时钟元件加上跨接于(该原本电网中的)多组原本导线的多组额外导线作为多组优化电网,其中该多组优化电网的各自的导线宽度可分别对应于该部分子类型,且该电网优化结果可包含该原本电网以及该多组优化电网。

为了更好地理解,该方法(尤其,该电网优化程序)可用图3所示的工作流程来说明,但本发明不限于此。依据某些实施例,一个或多个步骤可于图3所示的工作流程中增加、删除或修改。

图4示出执行图3所示电网优化程序前的电路架构的例子。一般元件(normalcell)可用来进行一般操作,例如可实施成触发器(flip-flop),而时钟元件可用来传送时钟波形(clock waveform),例如可实施成该多个类型的时钟元件,诸如缓冲器、反向器等。另外,原本导线P_ME1(1)、P_ME1(2)、P_ME1(3)、P_ME1(4)、P_ME1(5)、P_ME1(6)、P_ME1(7)、P_ME1(8)等可用来耦接此电路架构至一电源电压,而原本导线G_ME1(1)、G_ME1(2)、G_ME1(3)、G_ME1(4)、G_ME1(5)、G_ME1(6)、G_ME1(7)、G_ME1(8)等可用来耦接此电路架构至一接地电压。上列原本导线{P_ME1(1),P_ME1(2),…}与{G_ME1(1),G_ME1(2),…}可交错排列以容许上述一般元件与时钟元件藉此耦接至该电源电压与该接地电压。

图5示出图2所示方法于本发明一实施例中所产生的该电网优化结果。相较于图4所示电路架构,除了该原本电网诸如上列原本导线{P_ME1(1),P_ME1(2),…}与{G_ME1(1),G_ME1(2),…},该电网优化结果可包含优化电网(例如:该多组优化电网,诸如跨接于该多组原本导线的该多组额外导线)。为了更好地理解,较大的时钟元件可具有较强的驱动能力,而较小的时钟元件可具有较弱的驱动能力,尤其,上述任一类型的时钟元件的上述各自的大小可对应于上述任一类型的时钟元件的各自的驱动能力,而某一时钟元件的驱动能力可描述为其可驱动的下一级时钟元件的最大数量,但本发明不限于此。在加上该优化电网以后,此电路架构中的原本可能易于烧毁的某些局部电路(诸如以虚线绘示圆圈所指示之处)可变得更为强健。

例如,于针对类型A的时钟元件进行处理的期间,处理电路110可对一组子类型A1、A2等的各自的时钟元件进行电网增强,以分别于该组子类型A1、A2等的各自的时钟元件加上分别具有导线宽度的宽度(A1)、宽度(A2)等的对应组优化电网,其中导线宽度的宽度(A1)、宽度(A2)等分别对应于该组子类型A1、A2等,以和其各自的驱动能力及对应的功耗、电流等吻合,且该电网优化结果包含这些组优化电网;于针对类型B的时钟元件进行处理的期间,处理电路110可对一组子类型B1、B2等的各自的时钟元件进行电网增强,以分别于该组子类型B1、B2等的各自的时钟元件加上分别具有导线宽度的宽度(B1)、宽度(B2)等的对应组优化电网,其中导线宽度的宽度(B1)、宽度(B2)等分别对应于该组子类型B1、B2等,以和其各自的驱动能力及对应的功耗、电流等吻合,且该电网优化结果包含这些组优化电网;依此类推。为了简明起见,本实施例与前述实施例相仿的内容在此不重复赘述。

表1

表1展示该组子类型A1、A2等及相关导线宽度的例子,其中n>i1>i2>i3>i4>i5>i6>i7>i8>0,符号「索引()」代表时钟元件索引,且符号「X」代表不予理会(Don’t care),其可指出不需要额外导线。该多个时钟元件可称为时钟元件{元件(1),元件(2),…,元件(n)}(例如符号「n」可代表正整数),且处理电路110可从时钟元件定义文件122取得时钟元件{元件(1),元件(2),…,元件(n)}的各自的名字{$num(1),$num(2),…,$num(n)},且将时钟元件{元件(1),元件(2),…,元件(n)}定义为分别具有名字{$num(1),$num(2),…,$num(n)}的时钟元件{元件(1):$num(1),元件(2):$num(2),…,元件(n):$num(n)}。于针对类型A的时钟元件进行处理的期间,处理电路110可产生如表1所示的分类结果,尤其,分别将时钟元件{{元件(索引(n)),…,元件(索引(i1))},{元件(索引(i1-1)),…,元件(索引(i2))},{元件(索引(i2-1)),…,元件(索引(i3))},{元件(索引(i3-1)),…,元件(索引(i4))},{元件(索引(i4-1)),…,元件(索引(i5))},{元件(索引(i5-1)),…,元件(索引(i6))},{元件(索引(i6-1)),…,元件(索引(i7))},{元件(索引(i7-1)),…,元件(索引(i8))}}分类为子类型{A1,A2,A3,A4,A5,A6,A7,A8}。另外,处理电路110可判断子类型{A1,A2,A3,A4}需要进行电网增强,且设定子类型{A1,A2,A3,A4}的各自的导线宽度{宽度(A1),宽度(A2),宽度(A3),宽度(A4)}。类似地,处理电路110可针对该多个类型中的剩余类型(诸如类型B、C与D)进行类似的操作。为了简明起见,本实施例与前述实施例相似的内容在此不重复赘述。

依据某些实施例,处理电路110可限制关于该优化电网的布线资源(例如于步骤S23中所选择的该组子类型(诸如子类型{A1,A2,A3,A4})的大小及对应的额外导线),尤其,使该优化电网的全部额外导线不占用金属层ME2(见图8)的布线资源的0.2%,作为权衡(trade-off)。

图6示出图2所示方法于本发明一实施例中所产生的一组优化电网,其中耦接至某一时钟元件的这组优化电网可作为步骤S23(尤其,步骤S23B)中的该组优化电网的例子。如图6所示,这组优化电网诸如分别跨接于原本导线P_ME1与原本导线P_ME1’以及原本导线G_ME1与G_ME1’的一组额外导线P_ME2与G_ME2可提供额外电流路径给这个时钟元件,而这些额外电流路径可包含位于金属层ME1(见图8)的原本导线P_ME1’与G_ME1’、通过两个接点分别耦接至原本导线P_ME1与P_ME1’且位于金属层ME2的额外导线P_ME2、以及通过两个接点分别耦接至原本导线G_ME1与G_ME1’且位于金属层ME2的额外导线G_ME2,其中上列接点可通过金属层ME1与ME2之间的连通柱(via)来实施,原本导线P_ME1与P_ME1’可代表原本导线{P_ME1(1),P_ME1(2),…}中的两个,诸如具有连续编号的两个电源导线,而原本导线G_ME1与G_ME1’可代表原本导线{G_ME1(1),G_ME1(2),…}中的两个,诸如具有连续编号的两个接地导线,但本发明不限于此。为了简明起见,本实施例与前述实施例相似的内容在此不重复赘述。

依据某些实施例,上述额外电流路径可包含位于金属层ME1的多个原本导线{P_ME1’}与多个原本导线{G_ME1’}、通过3个或更多个接点分别耦接至原本导线P_ME1与该多个原本导线{P_ME1’}且位于金属层ME2的额外导线P_ME2、以及通过3个或更多个接点分别耦接至原本导线G_ME1与该多个原本导线{G_ME1’}且位于金属层ME2的额外导线G_ME2,其中上列接点可通过金属层ME1与ME2之间的连通柱来实施,原本导线P_ME1与该多个原本导线{P_ME1’}可代表原本导线{P_ME1(1),P_ME1(2),…}中的3个或更多个,诸如具有连续编号的电源导线,而原本导线G_ME1与该多个原本导线{G_ME1’}可代表原本导线{G_ME1(1),G_ME1(2),…}中的3个或更多个,诸如具有连续编号的接地导线。为了简明起见,这些实施例与前述实施例相似的内容在此不重复赘述。

图7示出图2所示方法于本发明一实施例中的宽度控制方案。处理电路110可依据该电网优化程序的至少一更新的参数重新执行该电网优化程序以更新该电网优化结果。例如,上述至少一更新的参数可包含一更新的导线宽度,诸如导线宽度的宽度(x),但本发明不限于此。依据某些实施例,上述至少一更新的参数可予以变化。例如,上述至少一更新的参数可包含一更新的接点数(contact count),其中该更新的接点数代表该组额外导线中的一导线以及该组原本导线之间的接点(例如:连通柱)的数量。又例如,上述至少一更新的参数可包含该更新的导线宽度(诸如线宽度的宽度(x))与该更新的接点数。

图8示出图2所示方法于本发明一实施例中所涉及的多层架构,其中该多层架构包含一多晶硅(polycrystalline silicon,polysilicon)层以及其上的多个金属层ME1、ME2、ME3、…及多个绝缘层,而该多个绝缘层分别位于该多个金属层ME1、ME2、ME3、…之间。该多个时钟元件可位于该多晶硅层及其上的一第一金属层诸如金属层ME1,该原本电网可位于该第一金属层诸如金属层ME1,以及该组优化电网可位于该第一金属层上的一第二金属层,诸如金属层ME2。为了简明起见,于本实施例中类似的内容在此不重复赘述。

以上所述仅为本发明的优选实施例,凡依本发明权利要求范围所做的均等变化与修饰,皆应属本发明的涵盖范围。

【符号说明】

100 设备

105 总线

110 处理电路

112 程序代码

120 储存装置

122 时钟元件定义文件

124 设计规范文件

126 电网优化记录文件

130 网络接口电路

S10、S20、S21、S22、S23、

S23A、S23B、S23C、S24、

S30、S40、S42、S44 步骤

P_ME1(1)、P_ME1(2)、

P_ME1(3)、P_ME1(4)、

P_ME1(5)、P_ME1(6)、

P_ME1(7)、P_ME1(8)、…、

P_ME1、P_ME1’、

G_ME1(1)、G_ME1(2)、

G_ME1(3)、G_ME1(4)、

G_ME1(5)、G_ME1(6)、

G_ME1(7)、G_ME1(8)、…、

G_ME1、G_ME1’ 原本导线

P_ME2、G_ME2 额外导线

ME1、ME2、ME3、… 金属层。

- 借助于额外导线来进行电网优化的方法与设备

- 无需额外的代码分析来进行链接时代码优化的方法和系统