安全逻辑到物理高速缓存

文献发布时间:2023-06-19 11:32:36

本申请要求2018年6月29日提交的美国申请序号16/023,485的优先权权益,该申请以全文引用的方式并入本文中。

背景技术

存储器系统通常被提供为计算机或其它电子装置中的内部半导体集成电路。存在许多不同类型的存储器,包含易失性和非易失性存储器。

易失性存储器需要电力来维持其数据,且包含随机存取存储器(RAM)、动态随机存取存储器(DRAM)或同步动态随机存取存储器(SDRAM)等等。

非易失性存储器可在不被供电时保持所存储数据,且包含快闪存储器、只读存储器(ROM)、电可擦除可编程ROM(EEPROM)、可擦除可编程ROM(EPROM)、电阻可变存储器,例如相变随机存取存储器(PCRAM)、电阻式随机存取存储器(RRAM)、磁阻式随机存取存储器(MRAM)或3D XPoint

快闪存储器用作广泛范围的电子应用的非易失性存储器。快闪存储器系统通常包含允许高存储器密度、高可靠性和低功耗的单晶体管、浮动栅极或电荷阱存储器单元的一或多个群组。

两种常见类型的快闪存储器阵列架构包含NAND和NOR架构,所述架构以各自的基本存储器单元配置所布置的逻辑形式来命名。存储器阵列的存储器单元通常布置成矩阵。在一实例中,阵列的行中的每一浮动栅极存储器单元的栅极耦合到存取线(例如,字线)。在NOR架构中,阵列的列中的每一存储器单元的漏极耦合到数据线(例如,位线)。在NAND架构中,阵列的串中的每一存储器单元的漏极以源极到漏极方式一起串联耦合在源极线与位线之间。

NOR及NAND架构半导体存储器阵列均通过解码器来存取,所述解码器通过选择耦合到特定存储器单元的栅极的字线来激活特定存储器单元。在NOR架构半导体存储器阵列中,一旦被激活,选定存储器单元便使其数据值置于位线上,从而依据特定单元经编程的状态而使不同电流流动。在NAND架构半导体存储器阵列中,将高偏压电压施加于漏极侧选择栅极(SGD)线。以指定传递电压(例如,Vpass)驱动耦合到每一群组的未选定存储器单元的栅极的字线,以使每一群组的未选定存储器单元作为传递晶体管操作(例如,以不受其所存储数据值限制的方式传递电流)。电流随后从源极线穿过每个串联耦合的群组流动到位线,仅受每个群组中的所选择的存储器单元限制,从而将所选择的存储器单元的当前经编码数据值置于位线上。

NOR或NAND架构半导体存储器阵列中的每个快闪存储器单元可以个体地或共同地编程到一或数个经编程状态。举例来说,单层级单元(SLC)可以表示两个经编程状态(例如,1或0)中的一个,从而表示一个数据位。然而,快闪存储器单元还可表示两个以上经编程状态中的一个,从而允许制造较高密度存储器,而不增加存储器单元的数目,因为每一单元可表示一个以上二进制数位(例如,一个以上位)。此类单元可被称为多状态存储器单元、多数位单元或多层级单元(MLC)。在某些实例中,MLC可指代可存储每单元两个数据位(例如,四个经编程状态中的一个)的存储器单元,三层级单元(triple-level cell,TLC)可指代可存储每单元三个数据位(例如,八个经编程状态中的一个)的存储器单元,且四层级单元(quad-level cell,QLC)可存储每单元四个数据位。MLC在本文中在其较广义上下文中使用,其可指代可存储每单元一个以上数据位(即,可表示两个以上经编程状态)的任何存储器单元。

一些存储器阵列是布置于半导体衬底的表面上的二维(2D)结构。为了增加给定区域的存储器容量且降低成本,已减小个别存储器单元的大小。然而,个别存储器单元大小的减小存在技术限制,因此2D存储器阵列的存储器密度也存在技术限制。作为响应,正开发三维(3D)存储器结构,例如3D NAND架构半导体存储器系统,以进一步增大存储器密度且降低存储器成本。

此类3D NAND装置通常包含存储单元串,其串联(例如,以漏极到源极的方式)耦合于接近源极的一或多个源极侧选择栅极(SGS)与接近位线的一或多个漏极侧选择栅极(SGD)之间。在实例中,SGS或SGD可包含一或多个场效应晶体管(FET)或金属氧化物半导体(MOS)结构装置等。在一些实例中,所述串将竖直延伸通过含有相应字线的多个竖直间隔开的层。半导体结构(例如,多晶硅结构)可邻近于存储单元串而延伸以形成用于所述串的存储单元的通道。在竖直串的实例中,多晶硅结构可呈竖直延伸柱的形式。在一些实例中,串可以“折叠”,且因此相对于U形柱而布置。在其它实例中,多个竖直结构可堆叠于彼此上以形成存储单元串的堆叠阵列。

存储器阵列或装置可组合在一起以形成存储器系统的存储体,例如固态驱动器(SSD)、通用快闪存储(UFS

SSD可包含若干存储器系统,包含若干裸片或逻辑单元(例如,逻辑单元数字或LUN),且可包含执行操作存储器系统或与外部系统介接所需的逻辑函数的一或多个处理器或其它控制器。这种SSD可包含一或多个快闪存储器裸片,其上包含数个存储器阵列和外围电路系统。快闪存储器阵列可包含组织成数个物理页的数个存储器单元块。在许多实例中,SSD还会包含DRAM或SRAM(或其它形式的存储器裸片或其它存储器结构)。SSD可从主机接收与存储器操作相关联的命令,所述存储器操作例如用以在存储器系统和主机之间传递数据(例如,用户数据和相关联完整性数据,例如错误数据和地址数据等)的读取或写入操作,或者用以从存储器系统擦除数据的擦除操作。

附图说明

在不一定按比例绘制的图式中,相似标号可以在不同视图中描述类似组件。具有不同的字母后缀的相似标号可以表示类似组件的不同例子。图式大体上借助于实例而非限制性地示出本文件中所论述的各种实施例。

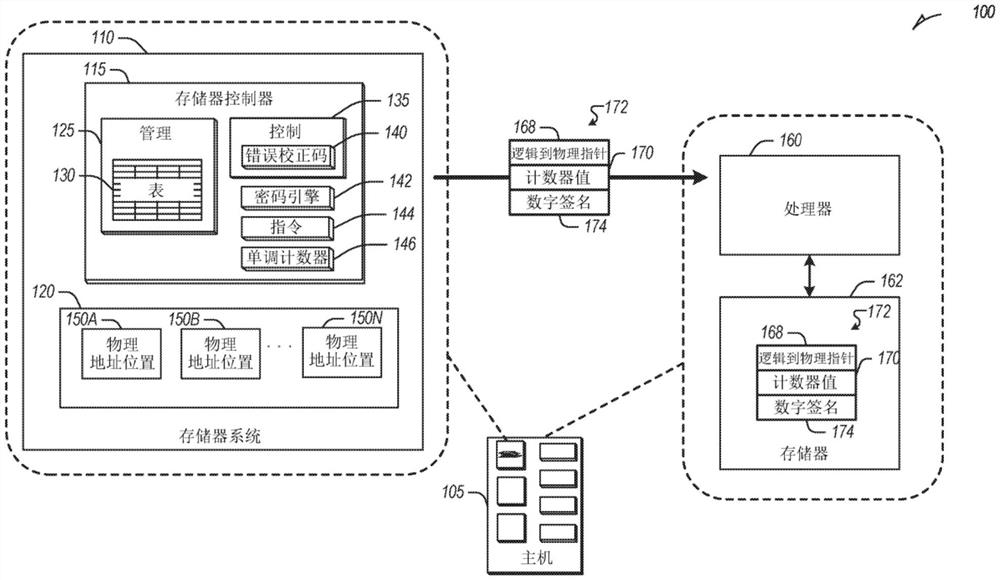

图1示出包含主机装置的环境的实例,所述主机装置包含被配置成经由通信接口通信的存储器系统。

图2是展示可由存储器系统执行以生成逻辑到物理(L2P)指针消息的过程流程的一个实例的流程图。

图3是展示可由主机装置执行以验证L2P指针消息的过程流程的一个实例的流程图。

图4是展示可由主机装置执行以验证L2P指针消息的过程流程的另一实例的流程图。

图5是展示可由主机装置执行以验证L2P指针消息的过程流程500的又一实例的流程图。

图6是展示可由存储器系统和主机装置执行以利用如本文所描述的安全L2P指针高速缓存处理读取/写入请求的过程流程的一个实例的流程图。

图7是展示可由存储器系统和主机装置执行以将一组一或多个L2P指针高速缓存在主机处的过程流程的一个实例的流程图。

图8是展示可由存储器系统和主机装置执行以利用高速缓存在主机装置处的L2P指针处理读取请求的过程流程的一个实例的流程图。

图9展示具有存储器系统作为一或多个设备的一部分的实例主机。

图10是示出其上可实施一或多个实施例的机器的实例的框图。

具体实施方式

本公开的方面是针对具有安全逻辑到物理(L2P)高速缓存的存储器系统。存储器系统可被配置成维持一组L2P指针。L2P指针使存储器系统的存储器阵列处的物理地址与例如主机装置处使用的逻辑地址相关。L2P指针可以例如L2P表等共同数据结构存储于存储器系统处。由主机装置作出的读取和写入请求可包含与待读取或写入的数据单元相关联的逻辑地址。存储器系统使用逻辑地址来生成L2P指针,和/或访问使逻辑地址与存储器阵列处的一或多个物理地址相关的先前生成的L2P指针。

为了维持持久性,L2P指针可存储于存储器系统的存储器阵列处。在存储器系统的使用期间,L2P指针可直接从存储器阵列读取。如果存储器系统控制器包含RAM,则L2P指针中的一些或全部可在使用期间存储于存储器系统控制器处以缩短时延。举例来说,访问存储器系统控制器RAM处的L2P指针的读取操作可比访问存储器阵列处的L2P指针的读取操作快。然而,对于一些应用,装置控制器RAM太小而不能加载存储器阵列的完整的L2P表。此外,一些存储器系统控制器不包含RAM。

相应地,在一些实例中,存储器系统被配置成将包含L2P指针的其L2P表中的一些或全部高速缓存在主机装置处。L2P指针可存储于主机装置的RAM处。当作出逻辑地址处的读取请求时,主机装置确定其是否已经高速缓存对应于所述逻辑地址的L2P指针的副本。如果主机装置具有L2P指针的高速缓存副本,则其使用L2P指针来解析存储器系统处的对应于逻辑地址的物理地址。主机装置可使用物理地址作出对存储器系统的读取请求。存储器系统传回存储于物理地址处的数据。有时,使用协议来执行L2P指针主机高速缓存,所述协议例如使用非易失性存储器主机控制器接口规范(NVMHCI)经由外围组件互连高速(PCIe)接口实施的主机内存缓冲区(HMB)协议,但预期其它协议和其它接口。

将L2P指针高速缓存在主机装置处可提供特定优点。举例来说,其可以允许较快地检索数据。相比于存储器系统原本能够从存储器阵列读取相同L2P指针的速度,主机装置可能够更快地读取高速缓存在主机装置存储器处的L2P指针。并且,将L2P指针高速缓存在主机装置处可减少对于存储器系统处的RAM的需要。举例来说,当来自主机装置的读取请求已经包含待访问的物理地址时,可减少将高速缓存L2P指针高速缓存在存储器系统控制器RAM处的需要。

另一方面,将L2P指针高速缓存在主机装置处可暴露存储器系统的物理地址结构。举例来说,恶意者可能尝试中间人攻击以拦截从存储器系统发送到主机装置的L2P指针。恶意者可修改拦截的L2P指针或提供假的L2P指针。在另一类型的攻击中,恶意者冒充存储器系统且向主机装置提供假的L2P指针。主机装置高速缓存且接着使用假的L2P指针。这可能导致存储器系统损毁。在一些实例中,假的L2P指针的使用可能导致存储器系统处的讹误。

本文中所描述的各种实例通过将L2P指针连同数字签名一起从存储器系统发送到主机装置来解决这些和/或其它挑战。存储器系统可使用待发送到主机装置的一或多个L2P指针和密码密钥来生成数字签名。所述一或多个L2P指针和所述数字签名在L2P指针消息中提供到主机装置。

主机装置还具有密码密钥的副本。主机装置使用其密码密钥的副本来使用密码密钥和随L2P指针消息包含的一或多个L2P指针生成主机侧数字签名。因为主机装置和存储器系统具有相同密码密钥,所以来自L2P指针消息的数字签名与主机侧数字签名应匹配。如果数字签名匹配,则主机装置将一或多个L2P指针高速缓存在其RAM处。如果数字签名不匹配,则主机装置拒绝将一或多个L2P指针高速缓存在其RAM处。

在一些实例中,主机装置被配置成在接收L2P指针消息后将L2P指针消息的内容中的一些或全部存储在其主机装置存储器处。可接着在L2P指针消息内容存储到RAM之后验证L2P指针消息的数字签名。以此方式,限制了修改L2P指针消息的内容的机会。如果主机侧数字签名与L2P指针消息数字签名不匹配,则从主机装置存储器移除所接收L2P指针。

在一些实例中,使用计数器值生成数字签名。存储器系统可实施单调计数器。单调计数器被配置成在特定事件发生后递增。举例来说,单调计数器可每当针对L2P指针消息生成数字签名时递增。在一些实例中,单调计数器在发生例如存储器系统加电等其它事件后递增。

存储器系统可使用来自单调计数器的值来生成用于L2P指针消息的数字签名。举例来说,存储器系统可使用密码密钥和来自单调计数器的当前计数器值生成交易密码密钥。存储器系统使用交易密码密钥生成数字签名,且随L2P指针消息提供计数器值的未加密副本。在主机装置侧,主机装置使用计数器值的未加密副本来生成交易密码密钥,且使用交易密码密钥来验证来自L2P指针消息的数字签名,如本文所描述。

因为单调计数器每当确定数字签名时递增,所以以此方式使用计数器值可抵御在不同时间拦截和尝试重新发送先前L2P指针消息的攻击者。举例来说,如果主机装置接收具有与先前L2P指针消息相同的单调计数器值的L2P指针消息,则其知道所述消息并非由存储器系统正确地生成。此外,如果攻击者尝试更新L2P指针消息中的未加密计数器值,则数字签名将与更新后的未加密计数器值不匹配且L2P指针消息将被主机装置拒绝。

图1示出包含主机装置105的环境100的实例,所述主机装置包含被配置成经由通信接口通信的存储器系统110。主机装置105或存储器系统110可包含在例如物联网(IoT)装置(例如,冰箱或其它电器、传感器、马达或致动器、移动通信装置、汽车、无人机等)等多种产品中以支持产品的处理、通信或控制。

存储器系统110包含存储器控制器115和存储器阵列120,其包含例如形成于相应裸片(在一些实例中,布置成二维或三维(3D)NAND裸片的堆叠)上的若干个别存储器系统。在3D架构半导体存储器技术中,堆叠竖直结构,从而增加给定占据面积内的层数、物理页且相应地增加存储器系统(例如,存储装置)的密度。在实例中,存储器系统110可以是主机装置105的离散存储器或存储装置组件。在其它实例中,存储器系统110可以是与主机装置105的一或多个其它组件堆叠或以其它方式一起包含的集成电路(例如,芯片上系统(SOC)等)的部分。

在图1的实例环境100中,主机装置105包含处理器160和主机装置存储器162。主机装置存储器162可包含随机存取存储器,例如DRAM、SDRAM,或任何其它合适的易失性或非易失性存储器组件。一或多个通信接口可用于在存储器系统110和主机装置105的一或多个其它组件之间传递数据,例如串行高级技术附件(SATA)接口、外围组件互连高速(PCIe)接口、通用串行总线(USB)接口、通用快闪存储(UFS)接口、eMMC

存储器控制器115可接收来自主机装置105的指令,且可与存储器阵列120通信,以便将数据传递到存储器阵列120的平面、子块、块或页中的一或多个(例如,写入或擦除),或从这些平面、子块、块或页中的一或多个传递数据(例如,读取)。存储器控制器115可以包含(尤其)电路系统或固件,包含一或多个组件或集成电路。举例来说,存储器控制器115可包含一或多个存储器控制单元、电路或组件,其被配置成控制存储器阵列120上的访问且在主机装置105与存储器系统110之间提供转译层。存储器控制器115可以包含一或多个输入/输出(I/O)电路、线或接口以向存储器阵列120传递数据或从存储器阵列120传递数据。存储器控制器115可以包含存储器管理器125和阵列控制器135。指令144可在存储器控制器115处执行以实施本文中所描述的安全L2P高速缓存。

存储器管理器125可包含(尤其)电路系统或固件,例如与各种存储器管理功能相关联的若干组件或集成电路。出于当前描述的目的,将在NAND存储器的背景下描述实例存储器操作和管理功能。所属领域的技术人员将认识到,其它形式的非易失性存储器可具有类似的存储器操作或管理功能。此类NAND管理功能包含损耗均衡(例如,垃圾收集或回收)、错误检测或校正、块引退,或一或多个其它存储器管理功能。存储器管理器125可将主机命令(例如,从主机接收到的命令)剖析或格式化为装置命令(例如,与存储器阵列的操作相关联的命令等),或生成用于阵列控制器135或存储器系统110的一或多个其它组件的装置命令(例如,以实现各种存储器管理功能)。

存储器管理器125可以包含一组管理表130,其被配置成维护与存储器系统110的一或多个组件相关联的各种信息(例如,与耦合到存储器控制器115的存储器阵列或一或多个存储器单元相关联的各种信息)。举例来说,管理表130可以包含关于耦合到存储器控制器115的一或多个存储器单元块的块年龄、块擦除计数、错误历史或者一或多个错误计数(例如,写入操作错误计数、读取位错误计数、读取操作错误计数、擦除错误计数等)的信息。在某些实例中,如果针对错误计数中的一或多个检测到的错误的数目高于阈值,则位错误可称为不可校正位错误。管理表130可以维持可校正或不可校正位错误的计数,以及其它。

管理表130还可包含一或多个L2P表,其包含使逻辑地址与存储器阵列120处的物理地址相关的L2P指针,如本文所描述。管理表130展示在管理器125处。举例来说,管理表130可存储于存储器控制器115的RAM处。在一些实例中,管理表130中的一些或全部存储于存储器阵列120处。举例来说,管理器125可从存储器阵列120读取管理表130和/或将管理表130中的一些或全部高速缓存在存储器控制器115的RAM处。

阵列控制器135可包含(尤其)被配置成控制与以下相关联的存储器操作的电路系统或组件:将数据写入到耦合到存储器控制器115的存储器系统110的一或多个存储器单元,从所述一或多个存储器单元读取数据,或擦除所述一或多个存储器单元。存储器操作可基于例如从主机装置105接收到或由存储器管理器125内部生成的主机命令(例如,与耗损均衡、错误检测或校正等相关联)。

阵列控制器135可包含错误校正码(ECC)组件140,其可包含(尤其)被配置成检测或校正与以下相关联的错误的ECC引擎或其它电路系统:将数据写入到耦合到存储器控制器115的存储器系统110的一或多个存储器单元或从所述一或多个存储器单元读取数据。存储器控制器115可被配置成有效地检测与各种操作或数据存储相关联的错误事件(例如,位错误、操作错误等)并从所述错误事件中恢复,同时维持在主机105与存储器系统110之间传递的数据的完整性,或维持所存储数据的完整性(例如,使用冗余RAID存储等),且可移除(例如,引退)发生故障的存储器资源(例如,存储器单元、存储器阵列、页、块等)以防止未来错误。

在图1的实例环境100中,存储器控制器115还包含密码引擎142。密码引擎142可被配置成对数据执行密码操作,例如如本文所描述。密码引擎142可包含一或多个密钥寄存器和一或多个数学引擎。密钥寄存器可存储用于执行密码操作的密码密钥。尽管密钥寄存器被描述为密码引擎142的组件,但在一些实例中,密钥寄存器可位于其它地方,例如位于存储器阵列121处的固定位置。数学引擎可被配置成执行密码操作,例如利用存储于密钥寄存器处的一或多个密码密钥。

密码引擎142可被配置成执行一或多个密码操作以生成如本文所描述的数字签名。密码引擎142可被配置成使用例如密码散列函数等任何合适的密码算法生成数字签名,所述密码散列函数例如SHA算法(例如,SHA256)、MD5算法等。密码具有函数将输入值映射到通常缩短的散列值。散列函数可选择为使得不大可能两个不同输入值将映射到相同散列值。密码引擎142可被配置成通过对与经数字签名的内容相关的输入值执行散列函数来生成数字签名。举例来说,密码引擎142可连结待执行的经签名命令、存储器系统计数器值和密码密钥以形成输入值。密码引擎142可接着对输入值执行散列函数以生成数字签名。

在一些实例中,密码引擎142被配置成结合主机装置105和存储器系统110A之间的通信接口操作。举例来说,密码引擎142可包括用于存储密码密钥的密钥寄存器或其它合适的存储位置,所述密码密钥用于加密和/或生成关于例如根据PCIe或其它合适的接口在存储器系统110A和主机装置105之间的通信的数字签名。并且,在一些实例中,密码引擎142包括存储服务器根密钥的密钥寄存器。用于存储器系统的服务器根密钥是用于验证经签名命令的密码密钥,如本文所描述。

存储器阵列120可包含布置于例如一或多个装置、一或多个平面、一或多个子块、一或多个块、一或多个页等中的若干存储器单元。作为一个实例,48GB TLC NAND存储器系统可包含每页18,592字节(B)的数据(16,384+2208字节)、每块1536页、每平面548块,以及每装置4个或更多个平面。作为另一实例,32GB MLC存储器系统(存储每单元两个数据位(即,4个可编程状态))可包含每页18,592字节(B)的数据(16,384+2208字节)、每块1024页、每平面548块,以及每装置4个平面,但相比于相应的TLC存储器系统具有一半的所需写入时间和两倍的编程/擦除(P/E)循环。其它实例可以包含其它数目或布置。在一些实例中,存储器系统或其部分可选择性地在SLC模式中或所要MLC模式中操作(例如TLC、QLC等)。

阵列120包含物理地址位置150A、150B、150N。物理地址位置是存储器阵列120处的与物理地址唯一地相关联的位置。在操作中,数据通常以页写入到存储器系统110或从所述存储器系统读取,且以块擦除。举例来说,物理地址位置150A、150B、150N可对应于页。然而,可按需要对更大或更小的存储器单元群组执行一或多个存储器操作(例如,读取、写入、擦除等)。相应地,在一些实例中,物理地址位置150A、150B、150N包含多于或少于一页。存储器系统110的数据传递大小通常称作页;而主机的数据传递大小通常称作扇区。

虽然数据页可包含若干字节的用户数据(例如,包含若干数据扇区的数据有效负载)及其对应的元数据,但页的大小经常仅指代用以存储用户数据的字节的数目。作为一实例,具有4KB的页大小的数据页可包含4KB的用户数据(例如,假定512B的扇区大小的8个扇区)以及对应于用户数据的若干字节(例如32B、54B、224B等)的元数据,例如完整性数据(例如错误检测或校正代码数据)、地址数据(例如逻辑地址数据等),或与用户数据相关联的其它元数据。用于存储元数据等的存储单元或子单元可被称为过度供给(over-provisioned)存储单元或子单元。

不同类型的存储器单元或存储器阵列120可提供不同页大小,或可需要与其相关联的不同量的元数据。举例来说,不同存储器系统类型可具有不同位错误率,其可导致确保数据页的完整性所必需的不同量的元数据(例如,具有较高位错误率的存储器系统相比于具有较低位错误率的存储器系统可需要更多字节的错误校正码数据)。作为实例,多层级单元(MLC)NAND快闪装置可具有与对应的单层级单元(SLC)NAND快闪装置相比更高的位错误率。因此,MLC装置可需要比对应SLC装置更多的用于错误数据的元数据字节。

在一些实例中,存储器控制器115还包括单调计数器146。单调计数器146包含用于递增计数器值的软件或硬件。单调计数器146被配置成使得计数器值始终在特定方向上移动。单调计数器146被配置成在生成用于L2P指针消息172的数字签名时递增,如本文所描述。在一些实例中,单调计数器被配置成基于存储器系统110处其它事件的发生而递增,例如当生成用于存储器系统110和主机装置105之间的其它通信的数字签名时、当存储器系统110断电或启动时等等。

图1的环境100还示出包括L2P指针168和数字签名174的L2P指针消息172。尽管实例L2P指针消息172包含单个L2P指针168,但一些L2P指针消息将包含除L2P指针168外的多个L2P指针。举例来说,L2P指针消息172可包含L2P指针表,所述L2P指针表包含存储于阵列120处的完整L2P指针表处的L2P指针中的一些或全部。可选地,L2P指针消息172还包含计数器值170。

存储器系统110至少部分使用L2P指针168、可包含在L2P指针消息172中的任何其它L2P指针和密码密钥生成数字签名174。举例来说,存储器系统110可使用密码密钥来生成L2P指针168(和其它L2P指针)的散列。数字签名174可包含散列的结果中的一些或全部。可使用任何合适的散列算法,例如SHA算法(例如SHA256)、MD5算法等。

密码密钥是存储器系统和主机装置已知的共享秘密。密码密钥可以任何合适的方式在存储器系统110和主机装置105之间安全地传送。在一些实例中,使用例如迪菲-赫尔曼或其它合适的密钥交换等密码密钥传递算法。在其它实例中,在制造过程处或期间将密码密钥写入到存储器系统110和/或主机装置105。在一些实例中,存储器系统110和主机装置使用已经作为例如PCIe等通信协议的一部分在存储器系统110和主机装置105之间共享的密码密钥。

在一些实例中,存储器系统110利用不对称密钥布置,其中存储器系统110包括公共密钥和私用密钥。私用密钥保持机密,且可例如存储在密码引擎142的密钥寄存器处。存储器系统110还具有公共密钥,其是共享的且可由证书颁发机构、存储器系统110或主机105的制造商或其他合适的一方验证。在使用不对称密钥布置的实例中,存储器系统110通过用其私用密钥加密一或多个L2P指针168而生成数字签名。主机装置105通过使用公共密钥解密数字签名174来验证数字签名174。如果解密的结果与L2P指针消息中的一或多个L2P指针168匹配,则数字签名得以验证。

将L2P指针消息172提供到主机装置105。主机装置105处的处理器160验证数字签名174,如本文所描述。如果数字签名174得以验证,则处理器160将L2P指针168高速缓存在主机装置105的RAM 162处。

在一些实例中,主机装置105将整个L2P指针消息172存储到RAM 162。为了验证数字签名174,主机装置105的处理器160从RAM 162读取L2P指针消息172来验证数字签名174。如果数字签名174未经验证,则从RAM 162移除L2P指针消息172。如果数字签名174得以验证,则L2P指针168保持存储于RAM 162中,例如在RAM 162处的L2P高速缓存位置处。

图2是展示可由例如存储器系统110等存储器系统执行以生成L2P指针消息的过程流程200的一个实例的流程图。相对于包含单个L2P指针的L2P指针消息描述图2。然而,在一些实例中,L2P指针消息包含一个以上L2P指针。举例来说,L2P指针消息可包含L2P指针表,所述L2P指针表包含多个L2P指针,如本文所描述。

在操作202处,存储器系统访问和/或生成L2P指针。(在其中L2P指针消息包含多个L2P指针的实例中,则存储器系统访问和/或生成多个L2P指针。)当存储器系统选择存储器阵列的存储单元以对应于特定逻辑地址时,存储器系统生成L2P指针。存储器系统生成使逻辑地址与同选定逻辑地址相关联的物理地址相关的L2P指针。或者,存储器系统可访问例如存储在存储器阵列和/或存储器控制器的RAM处的先前生成的L2P指针。

在任选操作204处,存储器系统依据密码密钥生成交易密码密钥,且依据单调计数器生成当前计数器值。这可以任何合适的方式执行。在一些实例中,存储器系统使用交易密码密钥处的结果连结计数器值和密码密钥。在另一实例中,存储器系统使用密码密钥和计数器值执行例如散列运算等密码操作。将结果用作交易密码密钥。

在操作206处,存储器系统使用来自操作202的一或多个L2P指针生成数字签名。此包含使用L2P指针和密钥执行例如散列运算等密码操作。如果在操作204处从计数器值生成交易密码密钥,则使用交易密码密钥生成数字签名。如果未生成交易密码密钥,则使用密码密钥生成数字签名。在一些实例中,数字签名为带密钥的散列消息认证码(HMAC)。

在操作208处,存储器系统110生成L2P指针消息。L2P指针消息包含待高速缓存在主机105处的L2P指针和在操作206处生成的数字签名。在使用计数器值的实例中,L2P指针消息还包含计数器值。

图3是展示可由主机装置执行以验证L2P指针消息的过程流程300的一个实例的流程图。相对于包含单个L2P指针的L2P指针消息描述图3。然而,在一些实例中,L2P指针消息包含一个以上L2P指针。举例来说,L2P指针消息可包含L2P指针表,所述L2P指针表包含多个L2P指针,如本文所描述。

在操作302处,主机装置接收L2P指针消息。在操作304处,主机装置生成主机侧数字签名。主机装置可使用密码密钥和包含在L2P指针消息中的L2P指针生成主机侧数字签名。为了生成主机侧数字签名,主机装置使用密码密钥和L2P指针执行密码操作。如果多个L2P指针包含在L2P指针消息中,则可使用L2P指针消息中的每一L2P指针生成主机侧数字签名。

在操作306处,主机装置确定主机侧数字签名是否等效于来自L2P指针消息放数字签名。因为将使用与数字签名相同的密码密钥和相同的L2P指针数据来生成主机侧数字签名,所以如果L2P指针消息由存储器系统正确地且可信地生成,则其应与数字签名匹配。

如果主机侧数字签名与数字签名匹配,则主机装置在操作310处高速缓存L2P指针。另一方面,如果主机侧数字签名与所述数字签名不匹配,则主机装置在操作308处丢弃一或多个L2P指针168且不进行高速缓存。举例来说,如果主机侧数字签名与所述数字签名不匹配,则其可指示L2P指针消息未由存储器系统生成,未由存储器系统正确地生成,和/或已被修改。

图4是展示可由主机装置执行以验证L2P指针消息的过程流程400的另一实例的流程图。相对于包含单个L2P指针的L2P指针消息描述图4。然而,在一些实例中,L2P指针消息包含一个以上L2P指针。举例来说,L2P指针消息可包含L2P指针表,所述L2P指针表包含多个L2P指针,如本文所描述。

在操作402处,主机装置接收L2P指针消息。在操作404处,主机装置将包含在L2P指针消息中的L2P指针写入到RAM,例如图1的主机装置存储器162。通过在验证数字签名之前将L2P指针和数字签名写入到主机装置存储器,主机装置可使在数字签名验证之前或期间L2P指针或数字签名被损毁的风险最小化。

在操作406处,主机装置从主机装置存储器读取L2P指针。在操作408处,主机装置使用从主机装置存储器读取的L2P指针生成主机侧签名。主机装置还使用密码密钥。

在操作410处,主机装置确定主机侧数字签名是否等效于来自L2P指针消息的数字签名。如果数字签名不等效,则主机装置在操作412处丢弃来自L2P指针消息的L2P指针。此可包含从主机装置的RAM删除L2P指针。如果数字签名等效,则主机装置在操作414处高速缓存L2P指针。在一些实例中,在操作404处,预先高速缓存L2P指针。如果情况如此,则高速缓存L2P指针包含将L2P指针留在主机装置存储器中的其在操作404处被存储的位置处。在其它实例中,高速缓存L2P指针包含将L2P指针从主机装置存储器处的其在操作404处被存储的位置移动到高速缓存位置。

图5是展示可由主机装置执行以验证L2P指针消息的过程流程500的又一实例的流程图。在图5的实例中,L2P指针消息包含来自存储器系统处的单调计数器的计数器值。在图5的实例中,L2P指针消息包含来自存储器系统处的单调计数器的计数器值。相对于包含单个L2P指针的L2P指针消息描述图5。然而,在一些实例中,L2P指针消息包含一个以上L2P指针。举例来说,L2P指针消息可包含L2P指针表,所述L2P指针表包含多个L2P指针,如本文所描述。

在操作502处,主机装置接收L2P指针消息。在操作504处,主机装置依据密码密钥和计数器值生成交易密码密钥。如本文所描述,可通过连结密码密钥和计数器值、使用密码密钥和计数器值执行密码操作等来生成交易密码密钥。在操作506处,主机装置使用交易密码密钥和来自L2P指针消息的L2P指针生成主机侧数字签名。举例来说,主机装置可使用交易密码密钥和L2P指针执行密码操作。

在操作508处,主机装置确定主机侧数字签名是否等效于随L2P指针消息一起接收的数字签名。如果否,则在操作512处丢弃来自L2P指针消息的L2P指针。如果主机侧数字签名等效于随L2P指针消息一起接收的数字签名,则主机装置在操作514处高速缓存L2P指针。

可选地,在操作514处高速缓存L2P指针之前,主机装置在操作510处确定是否之前已接收随L2P指针消息一起包含的计数器值。举例来说,如果计数器值已随由主机装置处理的先前L2P指针消息一起包含,则其可指示,L2P指针消息并非以来自存储器系统处的单调计数器的当前计数器值生成。(单调计数器将在生成先前L2P指针消息之后已经递增。)主机装置可保持来自从存储器系统接收的先前L2P指针消息的计数器值的记录。如果当前L2P指针消息中的计数器值不是新的,则主机装置在操作512处丢弃随L2P指针消息一起包含的L2P指针。如果计数器值是新的,则主机装置在操作514处高速缓存L2P指针。尽管图5中未确切地展示,但在一些实例中,过程流程500可包含在验证数字签名之前将L2P指针消息的全部或部分存储到主机装置的RAM。

图6是展示可由存储器系统和主机装置执行以利用如本文所描述的安全L2P指针高速缓存处理读取/写入请求的过程流程600的一个实例的流程图。过程流程600包含两列601、603。列601包含由例如主机装置105等主机执行的操作。列603包含由例如存储器系统110等存储器系统执行的操作。

在操作602处,主机将读取/写入请求605发送到存储器系统。读取/写入请求605可以是读取请求或写入请求。当读取/写入请求605为读取请求时,其包含逻辑地址。所述逻辑地址与存储数据的存储器系统处的数据单元的物理地址相关联。当读取/写入请求605为写入请求时,其包含待写入到存储器系统的一或多个存储单元的逻辑地址和数据。

在操作604处,存储器系统接收读取/写入请求605。在操作606处,存储器系统处理读取/写入请求605。举例来说,如果读取/写入请求605为读取请求,则存储器系统访问使随读取/写入请求605一起包含的逻辑地址与物理地址相关的L2P指针。存储器系统读取对应于物理地址的存储单元且将所读取数据传回到主机装置。如果读取/写入请求605为写入请求,则存储器系统选择用于存储包含在写入请求中的数据的一或多个存储单元。存储器系统还创建使来自写入请求的逻辑地址与选定存储单元的物理地址相关的L2P指针。

在操作608处,存储器系统生成包含数字签名和在操作606处访问和/或生成的L2P指针的L2P指针消息。举例来说,存储器系统可生成例如如本文相对于图2描述的L2P指针消息。

在操作610处,存储器系统将L2P消息607发送到主机装置。可选地,存储器系统还发送由于执行读取/写入请求605而产生的数据609。数据609可包含(例如)响应于读取请求从存储器阵列读取的数据、写入请求已完成的确认等。

主机装置接收L2P消息607,且在操作612处验证随L2P消息607一起包含的数字签名。主机装置可验证随L2P消息607一起包含的数字签名,例如如本文相对于图3-5所描述。假如L2P消息被验证,则主机装置在操作614处高速缓存随L2P指针消息607一起包含的L2P指针。

图6示出其中存储器系统响应于读取/写入请求提供L2P指针消息的实例。在一些实例中,主机请求一组一或多个L2P指针。图7是展示可由存储器系统和主机装置执行以将一组一或多个L2P指针高速缓存在主机处的过程流程700的一个实例的流程图。过程流程700包含两列701、703。列701包含由例如主机装置105等主机执行的操作。列703包含由例如存储器系统110等存储器系统执行的操作。

在操作702处,主机将针对一组L2P指针的请求705发送到存储器系统。请求705可包含(例如)一组逻辑地址。所请求的一组L2P指针可包含单个L2P指针和/或一组L2P指针。

存储器系统在操作704处接收请求705。在操作706处,存储器系统生成L2P指针消息707。举例来说,存储器系统可生成如本文相对于图2所描述的L2P指针消息。在操作708处,存储器系统将L2P指针消息707发送到主机装置。

主机装置接收L2P指针消息707,且在操作710处验证L2P指针消息707。主机装置可验证随例如如本文相对于图3-5所描述的L2P指针消息707一起包含的数字签名。假如随L2P指针消息707一起包含的数字签名得以验证,则主机装置在操作712处高速缓存随L2P指针消息707一起包含的一或多个L2P指针。

图8是展示可由存储器系统和主机装置执行以利用高速缓存在主机装置处的L2P指针处理读取请求的过程流程800的一个实例的流程图。过程流程800包含两列801、803。列801包含由例如主机装置105等主机执行的操作。列803包含由例如存储器系统110等存储器系统执行的操作。

在操作802处,主机生成指示逻辑地址的读取请求。读取请求可由主机的操作系统生成和/或可从在主机处执行的应用接收。在操作804处,主机搜索高速缓存在主机处的一或多个L2P指针以确定高速缓存的L2P指针中的任一个是否指示来自读取请求的逻辑地址。如果没有高速缓存的L2P指针指示逻辑地址,则主机和存储器系统在操作806处执行非高速缓存读取请求例程。本文中相对于图6描述实例非高速缓存请求例程。

如果在操作804处识别指示逻辑地址的L2P指针,则主机在操作808处访问高速缓存的L2P指针。在操作810处,主机将包含由L2P指针指示的物理地址的读取请求805发送到存储器系统。

存储器系统在操作812处接收读取请求805。在操作814处,存储器系统从存储单元读取对应于随读取请求805一起包含的物理地址的数据。存储器系统在操作816处将数据807传回到主机装置。主机装置在操作818处读取和处理数据。

图9展示具有存储器系统920(例如,本文中所描述的存储器系统中的任一个)作为一或多个设备930-950的一部分的实例主机装置910(例如,主机105)。设备包含可包含例如主机装置910等主机装置的任何装置。主机装置910可以是任何能够执行指令(循序或以其它方式)的装置。实例设备包含车辆930(例如,作为信息娱乐系统、控制系统等的一部分)、无人机950(例如,作为控制系统的一部分)、家具或电器940(例如,作为传感器系统、娱乐或信息娱乐系统的一部分)等。在其它实例中,虽然未展示,但设备可包含航空、船舶、物联网(IOT)和其它装置。

图10示出可在其上执行本文所论述的技术(例如,方法)中的任何一或多个的实例机器1000的框图。在替代实施例中,机器1000可以充当独立装置或可以连接(例如,联网)到其它机器。在联网部署中,机器1000可在服务器-客户端网络环境中作为服务器机器、客户端机器或两者操作。在实例中,机器1000可充当对等(P2P)(或其它分布式)网络环境中的对等机器。机器1000可以是个人计算机(PC)、平板PC、机顶盒(STB)、个人数字助理(PDA)、移动电话、网络电器、IoT装置、汽车系统,或能够执行(循序或以其它方式)指定将由所述机器采取的动作的指令的任何机器。另外,虽然仅说明单个机器,但术语“机器”也将视为包含个别地或共同地执行一(或多个)指令集以进行本文中所论述的方法中的任何一或多种的任何机器总集(例如,云计算、软件即服务(SaaS)、其它计算机集群配置)。

如本文所描述,实例可包含逻辑、组件、装置、封装或机制,或者可通过逻辑、组件、装置、封装或机制操作。电路系统是在包含硬件(例如,简单电路、门、逻辑等)的有形实体中实施的电路总集(例如,集合)。电路系统成员可随时间推移和基础硬件变化而为灵活的。电路系统包含在操作时可单独或组合地执行特定任务的部件。在实例中,电路系统的硬件可被永恒地设计成实行特定操作(例如,硬接线)。在实例中,电路系统的硬件可以包含可变连接的物理组件(例如,执行单元、晶体管、简单电路等),包含以物理方式修改(例如,恒定集结粒子的磁性、电气、可移动放置等)以编码特定操作的指令的计算机可读介质。在连接物理组件时,硬件构成的基础电特性例如从绝缘体改变成导体或反之亦然。指令使得参与的硬件(例如,执行单元或加载机构)能够经由可变连接以硬件创建电路系统部件以当在操作中时实行特定任务的部分。因此,当装置在操作时计算机可读介质以通信方式耦合到电路系统的其它组件。在一实例中,物理组件中的任一个可用于超过一个电路系统的超过一个部件中。例如,在操作下,执行单元可在一个时间点用于第一电路系统的第一电路,并且在不同时间由第一电路系统中的第二电路再使用,或由第二电路系统中的第三电路再使用。

机器(例如,计算机系统)1000(例如,主机装置105、存储器系统110等)可包含硬件处理器1002(例如,中央处理单元(CPU)、图形处理单元(GPU)、硬件处理器核心或其任何组合,例如存储器控制器115等)、主存储器1004和静态存储器1006,其中的一些或全部可经由互链路(例如,总线)1008彼此通信。机器1000可进一步包含显示单元1010、文数字输入装置1012(例如,键盘)和用户接口(UI)导航装置1014(例如,鼠标)。在一实例中,显示单元1010、输入装置1012和UI导航装置1014可以是触摸屏显示器。机器1000可另外包含存储装置(例如,驱动单元)1016、信号生成装置1018(例如,扬声器)、网络接口装置1020和一或多个传感器1017,例如全球定位系统(GPS)传感器、指南针、加速计或其它传感器。机器1000可包含输出控制器1028,例如串行(例如,通用串行总线(USB)、并行或其它有线或无线(例如,红外(IR)、近场通信(NFC)等)连接来使一或多个外围装置(例如,打印机、读卡器等)通信或对其进行控制。

存储装置1016可包含机器可读介质1022,其上存储体现本文中所描述的技术或功能中的任何一或多个或由本文中所描述的技术或功能中的任何一或多个利用的数据结构或指令1024(例如,软件)的一或多个集合。指令1024还可以在其由机器1000执行期间完全或至少部分地驻留于主存储器1004内、静态存储器1006内或硬件处理器1002内。在实例中,硬件处理器1002、主存储器1004、静态存储器1006或存储装置1016中的一个或任何组合可构成机器可读介质1022。

虽然机器可读介质1022说明为单个介质,但术语“机器可读介质”可包含被配置成存储所述一或多个指令1024的单个介质或多个介质(例如,集中式或分布式数据库,或相关联高速缓冲存储器和服务器)。

术语“机器可读介质”可包含能够存储、编码或载送用于由机器1000执行且使机器1000执行本公开的技术中的任何一或多个的指令,或能够存储、编码或载送由此类指令使用或与此类指令相关联的数据结构的任何介质。非限制性机器可读介质实例可包含固态存储器,以及光学和磁性介质。在一实例中,集结的机器可读介质包括具有多个粒子的机器可读介质,所述粒子具有不变(例如,静止)质量。因此,集结的机器可读介质是非暂时性传播信号。集结的机器可读介质的特定实例可包含:非易失性存储器,例如半导体存储器系统(例如,电可编程只读存储器(EPROM)、电可擦除可编程只读存储器(EEPROM))和快闪存储器系统;磁盘,例如内部硬盘和可移式盘;磁光盘;以及CD-ROM和DVD-ROM盘。

指令1024(例如,软件、程序、操作系统(OS)等)或其它数据存储在存储装置1021上,可由存储器1004存取以供处理器1002使用。存储器1004(例如,DRAM)通常为快速但易失性的,且因此是与适于长期存储(包含在“关断”条件中)的存储装置1021(例如,SSD)不同类型的存储装置。供用户或机器1000使用的指令1024或数据通常加载于存储器1004中以供处理器1002使用。在存储器1004已满时,可分配来自存储装置1021的虚拟空间以补充存储器1004;然而,因为存储装置1021通常比存储器1004慢且写入速度通常比读取速度慢至少两倍,所以虚拟存储器的使用归因于存储装置时延(与例如DRAM等存储器1004相比)可能极大地降低用户体验。另外,用于虚拟存储器的存储装置1021的使用可极大地缩短存储装置1021的使用寿命。

相比于虚拟存储器,虚拟存储器压缩(例如,

针对移动电子装置优化的存储装置或移动存储装置传统上包含MMC固态存储装置(例如,微安全数字(microSD

指令1024可使用发射介质经由网络接口装置1020利用若干传递协议中的任一个(例如,帧中继、因特网协议(IP)、发射控制协议(TCP)、用户数据报协议(UDP)、超文本传递协议(HTTP)等)在通信网络1026上进一步发射或接收。实例通信网络可包含局域网(LAN)、广域网(WAN)、包数据网络(例如因特网)、移动电话网络(例如蜂窝网络)、简易老式电话(POTS)网络和无线数据网络(例如称为

以上详细描述包含对附图的参考,附图形成详细描述的部分。图式借助于图示展示可实践本发明的特定实施例。这些实施例在本文中也称为“实例”。此类实例可包含除了所展示或描述的那些要素之外的要素。然而,本发明人还预期其中仅提供所展示或所描述的那些要素的实例。此外,本发明人还预期使用相对于特定实例(或其一或多个方面)或相对于本文展示或描述的其它实例(或其一或多个方面)而展示或描述的那些要素的任何组合或排列的实例(或其一或多个方面)。

在本文中,如专利文件中所常见而使用术语“一”以包含一个或多于一个,其独立于“至少一个”或“一或多个”的任何其它例子或使用。在本文中,术语“或”用于指代非排它性或,使得除非另有指示,否则“A或B”可包含“A而非B”、“B而非A”以及“A和B”。在所附权利要求书中,术语“包含(including)”及“其中(in which)”用作相应术语“包括(comprising)”及“其中(wherein)”的简洁英文等效术语。并且,在所附权利要求书中,术语“包含”和“包括”为开放式的,即,包含除权利要求中此术语之后所列的要素之外的要素的系统、装置、制品或过程仍被认为落在该权利要求的范围内。此外,在所附权利要求书中,术语“第一”、“第二”和“第三”等仅用作标记,且并不希望对其对象强加数值要求。

在不同实例中,本文中所描述的组件、控制器、处理器、单元、引擎或表可尤其包含存储于物理装置上的物理电路系统或固件。如本文中所使用,“处理器”意指任何类型的计算电路,例如但不限于微处理器、微控制器、图形处理器、数字信号处理器(DSP)或任何其它类型的处理器或处理电路,包含处理器或多核心装置的群组。

如在本文中所使用的术语“水平”被定义为平行于衬底的常规平面或表面的平面,例如下伏于晶片或裸片的常规平面或表面,而不管在任一时间点所述衬底的实际定向如何。术语“竖直”指代垂直于如上文所定义的水平的方向。例如“上”、“之上”和“之下”等介词是关于常规平面或表面在衬底的顶部或暴露表面上而定义,而无论衬底的定向如何;且同时“上”希望表明一个结构相对于该结构位于其“上”的另一结构的直接接触(在未明确指示相反情况时);术语“之上”和“之下”明确地希望指明结构(或层、特征等)的相对放置,其明确地包含--但不限于--所指出结构之间的直接接触,除非特定地如此指示。类似地,术语“之上”和“之下”并不限于水平定向,因为如果一结构在某个时间点是所论述的构造的最外部分,那么即使此类结构相对于参考结构竖直地延伸而不是在水平定向上延伸,此结构也可在参考结构“之上”。

术语“晶片”和“衬底”在本文中用于大体上指代上面形成集成电路的任何结构,并且还指代在集成电路制造的各个阶段期间的此类结构。因此,以下详细描述不应以限制性意义来理解,并且各种实施例的范围仅由所附权利要求书连同所述权利要求书授权的等效物的完整范围定义。

根据本公开且在本文中描述的各种实施例包含利用存储器单元的竖直结构(例如,存储器单元的NAND串)的存储器。如本文中所使用,将采用相对于其上形成存储器单元的衬底的表面的方向性形容词(即,竖直结构将视为远离衬底表面延伸,竖直结构的底端将视为最接近衬底表面的端部,且竖直结构的顶端将视为最远离衬底表面的端部)。

如本文中所使用,例如水平、竖直、正交、平行、垂直等方向性形容词可指相对定向,并且除非另外指出,否则并不希望要求严格遵守特定几何性质。举例来说,如本文中所使用,竖直结构不必严格地垂直于衬底的表面,而是可改为大体上垂直于衬底的表面,并且可与衬底的表面形成锐角(例如在60度与120度之间等)。

在本文中所描述的一些实施例中,不同掺杂配置可应用于源极侧选择栅极(SGS)、控制栅极(CG)和漏极侧选择栅极(SGD),其中的每一个在此实例中可由多晶硅形成或至少包含多晶硅,结果为使得这些层(例如,多晶硅等)当暴露于刻蚀溶液时可具有不同的蚀刻速率。举例来说,在3D半导体装置中形成单体柱的过程中,SGS和CG可形成凹陷,而SGD可保持较少凹陷乃至不凹陷。这些掺杂配置可因此通过使用蚀刻溶液(例如,四甲基铵氢氧化物(TMCH))来实现选择性蚀刻到3D半导体装置中的不同层(例如,SGS、CG和SGD)中。

如本文所使用,操作存储器单元包含从存储器单元读取、对存储器单元写入或擦除存储器单元。使存储器单元置于既定状态中的操作在本文中称为“编程”,且可以包含对存储器单元写入或从存储器单元擦除两者(即,存储器单元可经编程为擦除状态)。

根据本公开的一或多个实施例,位于存储器系统内部或外部的存储器控制器(例如处理器、控制器、固件等)能够确定(例如选择、设定、调整、计算、改变、清除、通信、适应、推导、定义、利用、修改、应用等)一定数量的耗损循环或耗损状态(例如,记录耗损循环、对存储器系统发生的操作计数、追踪存储器系统起始的操作、评估与耗损状态相对应的存储器系统特性等)。

根据本公开的一或多个实施例,存储器存取装置可被配置成利用每一存储器操作向存储器系统提供损耗循环信息。存储器系统控制电路系统(例如,控制逻辑)可经编程以补偿对应于损耗循环信息的存储器系统性能改变。存储器系统可接收损耗循环信息并且响应于损耗循环信息而确定一或多个操作参数(例如,值、特性)。

将理解,当一元件被称作“在另一元件上”、“连接到另一元件”或“与另一元件耦合”时,其可直接在另一元件上、与另一元件直接连接或耦合,或可存在中间元件。相比之下,当一元件被称作“直接在另一元件上”、“直接连接到另一元件”或“直接耦合到另一元件”时,不存在中间元件或层。如果两个元件在图式中展示为被线连接,那么除非另外指明,否则所述两个元件可耦合或直接耦合。

本文中描述的方法实例可至少部分地由机器或计算机实施。一些实例可包含编码有指令的计算机可读介质或机器可读介质,所述指令可操作以配置电子装置来执行如在以上实例中所描述的方法。这类方法的实施方案可包含代码,例如微码、汇编语言代码、高级语言代码或类似物。这类代码可包含用于执行各种方法的计算机可读指令。代码可以形成计算机程序产品的部分。此外,代码可例如在执行期间或在其它时间有形地存储于一或多个易失性或非易失性有形计算机可读介质上。这些有形计算机可读介质的实例可包含但不限于:硬盘、可移式磁盘、可移式光盘(例如,压缩光盘和数字视频光盘)、盒式磁带、存储卡或棒、随机存取存储器(RAM)、只读存储器(ROM)、固态驱动器(SSD)、通用快闪存储(UFS)装置、嵌入式MMC(eMMC)装置等。

实例:

实例1是一种系统,其包括:存储器系统;主机装置存储器;以及主机装置处理器,其中所述主机装置处理器被编程为执行包含以下的操作:从所述存储器系统接收第一逻辑到物理(L2P)指针消息,所述第一L2P指针消息包括:指示第一逻辑地址和所述存储器系统处的对应于所述第一逻辑地址的第一物理地址的第一L2P指针;以及第一数字签名;至少部分地基于所述第一L2P指针和密码密钥执行第一密码操作;至少部分地基于所述第一密码操作验证所述第一数字签名;以及由所述处理器将所述第一L2P指针高速缓存在所述主机装置存储器处。

在实例2中,实例1的主题任选地包含,其中所述主机装置处理器进一步被编程为执行包含以下的操作:接收第二L2P指针消息,所述第二L2P指针消息包括:指示第二逻辑地址和所述存储器系统处的对应于所述第二逻辑地址的第二物理地址的第二L2P指针;以及第二数字签名;至少部分地基于所述第二L2P指针和所述密码密钥执行第二密码操作;以及至少部分地基于所述第二密码操作确定所述第二数字签名未验证。

在实例3中,实例2的主题任选地包含,其中所述主机装置处理器进一步被编程为执行包含以下的操作:在执行所述第二密码操作之前,由所述处理器将所述第二L2P指针高速缓存在所述主机装置存储器处;从所述主机装置存储器读取所述第二L2P指针和所述第二数字签名;以及在确定所述第二数字签名未验证之后,从所述主机装置存储器移除所述第二L2P指针。

在实例4中,实例1-3中的任一或多个的主题任选地包含,P指针消息进一步包括第一计数器值,且其中执行所述第一密码操作还至少部分地基于所述第一计数器值。

在实例5中,实例4的主题任选地包含,其中所述处理器进一步被编程为执行操作,包括至少部分地基于所述密码密钥和所述第一计数器值生成交易密码密钥,其中执行所述密码密钥还至少部分地基于所述交易密码密钥。

在实例6中,实例4-5中的任一或多个的主题任选地包含来自所述存储器系统的P指针消息。

在实例7中,实例1-6中的任一或多个的主题任选地包含P指针。

在实例8中,实例1-7中的任一或多个的主题任选地包含,其中所述存储器系统包括:存储器阵列;以及控制器,其中所述控制器被编程为执行包含以下的操作:至少部分地基于第一L2P指针和密码密钥执行第三密码操作以生成所述第一数字签名;确定将所述第一L2P指针高速缓存在所述主机装置存储器处;以及将所述第一L2P指针消息发送到所述处理器以供存储在所述主机装置存储器处。

在实例9中,实例8的主题任选地包含,其中所述存储器系统进一步包括单调计数器,且其中所述控制器进一步被编程为执行操作,包括从所述单调计数器读取第一计数器值,其中所述第三密码操作还至少部分地基于所述第一计数器值。

在实例10中,实例9的主题任选地包含,其中所述控制器进一步被编程为执行操作,包括至少部分地基于所述密码密钥和所述第一计数器值生成交易密码密钥,其中所述第三密码操作还至少部分地基于所述交易密码密钥。

实例11是一种管理存储器系统的方法,其包括:由处理器接收存储器系统处发起的第一逻辑到物理(L2P)指针消息,所述第一L2P指针消息包括:指示第一逻辑地址和所述存储器系统处的对应于所述第一逻辑地址的第一物理地址的第一L2P指针;以及第一数字签名;由所述处理器至少部分地基于所述第一L2P指针和密码密钥执行第一密码操作;由所述处理器至少部分地基于所述第一密码操作验证所述第一数字签名;以及由所述处理器将所述第一L2P指针高速缓存在与所述处理器相关联的主机装置存储器处。

在实例12中,实例11的主题任选地包含,由所述处理器接收第二L2P指针消息,所述第二L2P指针消息包括:指示第二逻辑地址和所述存储器系统处的对应于所述第二逻辑地址的第二物理地址的第二L2P指针;以及第二数字签名;由所述处理器至少部分地基于所述第二L2P指针和所述密码密钥执行第二密码操作;以及由所述处理器至少部分地基于所述第二密码操作确定所述第二数字签名未验证。

在实例13中,实例12的主题任选地包含,由所述处理器将所述第二L2P指针高速缓存在所述主机装置存储器处;以及在确定所述第二数字签名未验证之后,从所述主机装置存储器移除所述第二L2P指针。

在实例14中,实例11-13中的任一或多个的主题任选地包含,P指针消息进一步包括第一计数器值,且其中执行所述第一密码操作还至少部分地基于所述第一计数器值。

在实例15中,实例14的主题任选地包含,至少部分地基于所述密码密钥和所述第一计数器值生成交易密码密钥,其中执行所述密码密钥还至少部分地基于所述交易密码密钥。

在实例16中,实例14-15中的任一或多个的主题任选地包含来自所述存储器系统的P指针消息。

在实例17中,实例11-16中的任一或多个的主题任选地包含P指针。

实例18是一种其上包括指令的有形计算机可读介质,所述指令在由处理器执行时致使所述处理器执行包含以下的操作:接收第一逻辑到物理(L2P)指针消息,所述第一L2P指针消息包括:指示第一逻辑地址和存储器系统处的对应于所述第一逻辑地址的第一物理地址的第一L2P指针;以及第一数字签名;至少部分地基于所述第一L2P指针和密码密钥执行第一密码操作;至少部分地基于所述第一密码操作验证所述第一数字签名;以及将所述第一L2P指针高速缓存在与所述处理器相关联的主机装置存储器处。

在实例19中,实例18的主题任选地包含,其中所述计算机可读介质进一步包括其上的指令,所述指令在由所述处理器执行时致使所述处理器执行包含以下的操作:接收第二L2P指针消息,所述第二L2P指针消息包括:指示第二逻辑地址和所述存储器系统处的对应于所述第二逻辑地址的第二物理地址的第二L2P指针;以及第二数字签名;至少部分地基于所述第二L2P指针和所述密码密钥执行第二密码操作;以及至少部分地基于所述第二密码操作确定所述第二数字签名未验证。

在实例20中,实例19的主题任选地包含,其中所述计算机可读介质进一步包括其上的指令,所述指令在由所述处理器执行时致使所述处理器执行包含以下的操作:由所述处理器将所述第二L2P指针高速缓存在所述主机装置存储器处;以及在确定所述第二数字签名未验证之后,从所述主机装置存储器移除所述第二L2P指针。

以上描述希望说明性的而非限制性的。例如,上文所描述的实例(或其一或多个方面)可彼此组合使用。例如所属领域的一般技术人员在查阅以上描述后可使用其它实施例。应理解,发明内容将不会用于解释或限制权利要求书的范围或含义。另外,在以上具体实施方式中,可将各个特征分组在一起以简化本公开。不应将此解释为意图未要求保护的所公开特征对任何权利要求来说是必不可少的。实际上,本发明主题可在于比特定所公开实施例的所有特征少的特征。因此,特此将所附权利要求书并入到具体实施方式中,其中每一权利要求作为单独实施例而独立存在,且预期这些实施例可以各种组合或排列彼此组合。本发明的范围应通过参考所附权利要求书以及此权利要求书所授予的等效物的完整范围来确定。

- 安全逻辑到物理高速缓存

- 混合逻辑到物理高速缓存方案