一种叠层环栅的沟道结构及其制备方法

文献发布时间:2023-06-19 11:32:36

技术领域

本发明属于半导体工艺技术领域,具体涉及一种叠层环栅的沟道结构及其制备方法。

背景技术

随着器件尺寸的缩小,短沟道效应问题逐渐突出。传统的沟道材料如Si、Ge等通过外延制备,生长条件严苛,制备二维沟道结构的传统方法需要转移,无法直接在晶圆/结构上生长。

此外,现有沟道结构所采用的材料为单层结构,导致沟道结构的载流子迁移率较低。

发明内容

鉴于上述分析,本发明旨在提供一种叠层环栅的沟道结构及其制备方法,解决了现有技术中传统的沟道材料的生长条件严苛、制备沟道结构的传统方法需要转移无法直接在晶圆/结构上生长、现有的沟道结构载流子迁移率较低的问题。

本发明的目的主要是通过以下技术方案实现的:

本发明提供了一种叠层环栅的沟道结构,包括硅衬底、沟道层以及多层硅层(Si层)和多层支撑层,多层硅层依次层叠在硅衬底上,所述支撑层设于硅衬底与硅层之间和相邻两层硅层之间,沟道层设于硅层的表面(即硅层的上表面、下表面和侧面),也就是说,硅层的表面包括支撑层接触面和非支撑层接触面,硅层的非支撑层接触面上设有沟道层。上述沟道层为WS

进一步地,上述支撑层为SiGe层。

进一步地,上述SiGe层中,Ge的含量为10wt.%~40wt.%。

进一步地,硅层的层数可以为3~5层。

进一步地,上述硅层的宽度为10~100nm,上述硅层的长度与宽度比为1:1~10:1。

进一步地,上述支撑层的厚度为10~30nm,上述沟道层的厚度为1~10nm。

本发明还提供了一种叠层环栅的沟道结构的制备方法,包括如下步骤:

提供一硅衬底;

在硅衬底上形成硅层和支撑层;

在硅层的表面形成沟道层,完成叠层环栅的沟道结构的制备。

进一步地,在硅衬底上形成硅层和支撑层包括如下步骤:

在硅衬底上形成依次层叠的待处理支撑层和待处理硅层;

对待处理支撑层和待处理硅层进行垂直刻蚀,得到待释放支撑层和硅层,需要说明的是,垂直刻蚀后得到的待释放支撑层和硅层的宽度影响最终叠层环栅的沟道结构中的沟道的尺寸;

对垂直刻蚀后的待释放支撑层进行部分释放刻蚀,得到支撑层。

进一步地,采用干法刻蚀的方式、以HBr/O

进一步地,采用干法刻蚀的方式、以CF

进一步地,在对待处理支撑层和待处理硅层进行垂直刻蚀得到硅层之后,对垂直刻蚀后的待处理支撑层进行部分释放刻蚀得到支撑层之前,还包括如下步骤:

在硅层的表面、垂直刻蚀后的待处理支撑层的表面以及硅衬底的上表面淀积SiO

进一步地,采用等离子体增强原子层沉积(PEALD)在硅层的表面形成沟道层。

进一步地,形成沟道层4材料的前驱体包括W前驱体和S前驱体,其中,W前驱体为WF

进一步地,采用等离子体增强原子层沉积(PEALD)在硅层的表面形成沟道层的工艺参数如下:基座温度为200℃~450℃,腔压为5-30Torr。

进一步地,采用等离子体增强原子层沉积(PEALD)在硅层的表面形成沟道层包括如下步骤:

步骤a:在硅层、支撑层和SiO

步骤b:保护层表面吸附WF

步骤c:惰性气体(例如,Ar和/或He)吹扫,惰性气体的流量为20~200sccm;

步骤d:采用H

步骤e:采用H

步骤f:惰性气体(例如,Ar和/或He)吹扫,惰性气体的流量为20~200sccm,形成待处理沟道层;

步骤g:对待处理沟道层进行遮掩刻蚀,刻蚀去除与支撑层和SiO

与现有技术相比,本发明至少可实现如下有益效果之一:

a)本发明提供的叠层环栅的沟道结构中,采用WS

b)本发明提供的叠层环栅的沟道结构中,设有用于形成沟道层的硅纳米片结构,通过支撑层将多层硅层分隔开来,形成部分悬空的硅层,硅层的上表面、下表面和侧面均形成沟道,从而能够形成多层沟道结构,进一步提高上述叠层环栅的沟道结构的整体载流子迁移率和叠层环栅的综合性能。

c)本发明提供的叠层环栅的沟道结构中,上述支撑层为SiGe层,SiGe和Si的选择比较高,在刻蚀工艺中选择比较高的两种材料,更有利于上述叠层环栅的沟道结构的制备。

d)本发明提供的叠层环栅的沟道结构中,硅层的宽度为10~100nm,长度与宽度比为1:1~10:1。这是因为,采用宽度较窄的硅层的纳米片则具有低功耗的特点,采用宽度较宽的硅层的纳米片则具有高性能的特点。

e)本发明提供的叠层环栅的沟道结构的制备方法中,兼容CMOS工艺,能够在8寸、12寸晶圆上制备二维材料,解决传统方法只能在小面积上制备的缺陷;同时,采用上述方法能够直接在硅衬底上生长沟道层,不需要传统制备方法中转移沟道层(即WS

f)本发明提供的叠层环栅的沟道结构的制备方法中,为了能够避免沟道层形成在硅衬底上,在对待处理支撑层和待处理硅层进行垂直刻蚀得到硅层之后,对垂直刻蚀后的待处理支撑层进行部分释放刻蚀得到支撑层之前,还包括如下步骤:在硅层的表面、垂直刻蚀后的待处理支撑层的表面以及硅衬底的上表面淀积SiO

g)本发明提供的叠层环栅的沟道结构的制备方法中,在形成沟道层之前,在硅层、支撑层和SiO

本发明的其他特征和优点将在随后的说明书中阐述,并且,部分的从说明书中变得显而易见,或者通过实施本发明而了解。本发明的目的和其他优点可通过在所写的说明书以及附图中所特别指出的结构来实现和获得。

附图说明

附图仅用于示出具体发明的目的,而并不认为是对本发明的限制,在整个附图中,相同的参考符号表示相同的部件。

图1为本发明实施例一提供的叠层环栅的沟道结构的俯视图;

图2为本发明实施例一提供的叠层环栅的沟道结构的正向剖视图(Y-Y剖视图);

图3为本发明实施例一提供的叠层环栅的沟道结构的侧向剖视图(X-X剖视图);

图4为本发明实施例一提供的叠层环栅的沟道结构的侧向剖视图(Z-Z剖视图);

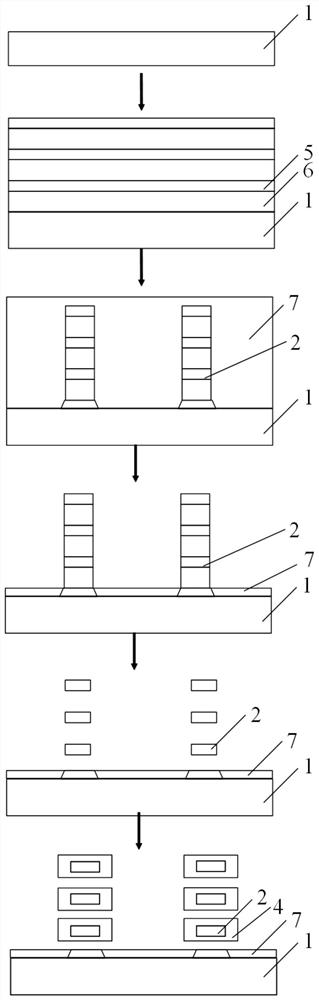

图5为本发明实施例二提供的叠层环栅的沟道结构的制备方法的流程图。

附图标记:

1-硅衬底;2-硅层;3-支撑层;4-沟道层;5-待处理硅层;6-待处理支撑层;7-SiO

具体实施方式

下面结合附图来具体描述本发明的优选发明,其中,附图构成本发明的一部分,并与本发明的发明一起用于阐释本发明的原理。

实施例一

本实施例提供了一种叠层环栅的沟道结构,参见图1至图4,包括硅衬底1、沟道层4以及多层硅层2(Si层)和多层支撑层3,其中,多层硅层2依次层叠在硅衬底1上,支撑层3设于硅衬底1与硅层2之间和相邻两层硅层2之间,上述沟道层4设于硅层2的表面(即硅层2的上表面、下表面和侧面),也就是说,硅层2的表面包括支撑层接触面和非支撑层接触面,硅层2的非支撑层接触面上设有沟道层4。上述沟道层4为WS

与现有技术相比,本实施例提供的叠层环栅的沟道结构中,采用WS

同时,上述叠层环栅的沟道结构中设有用于形成沟道层的硅纳米片结构,通过支撑层3将多层硅层2分隔开来,形成部分悬空的硅层2,硅层2的上表面、下表面和侧面均形成沟道,从而能够形成多层沟道结构,进一步提高上述叠层环栅的沟道结构的整体载流子迁移率和综合性能。

在实际应用中,为了便于上述硅层2的形成以及叠层环栅的沟道结构的制备,上述支撑层3为SiGe层,这是因为,SiGe和Si的选择比较高,在刻蚀工艺中选择比较高的两种材料,更有利于上述叠层环栅的沟道结构的制备。

为了进一步控制上述两种材料(SiGe和Si)的选择比,上述SiGe层中Ge的含量为10wt.%~40wt.%。

对于上述硅层2的层数,从载流子迁移率提高和结构简单的角度考虑,上述硅层2的层数可以为3~5层。但是,需要说明的是,叠层环栅的沟道结构中,硅层2的层数不限于3~5层,实际应用中,可以根据不同工艺条件以及叠层环栅的需求进行适当调整,在此不一一赘述。

考虑到沟道层4直接在硅层2的表面形成,因此,硅层2的宽度会直接影响上述叠层环栅的沟道结构的载流子迁移率,示例性地,上述硅层2的宽度为10~100nm,长度与宽度比为1:1~10:1。这是因为,将硅层2的宽度以及长度与宽度比限定在上述范围内,主要是根据使用需求进行设定的,采用宽度较窄的硅层2的纳米片具有低功耗的特点,采用宽度较宽的硅层2的纳米片则具有高性能的特点。

为了进一步提高上述叠层环栅的沟道结构的综合性能,示例性地,上述支撑层3的厚度为10~30nm,上述沟道层4的厚度为1~10nm。这样,通过设置合理的支撑层3和沟道层4的厚度,能够进一步提高上述叠层环栅的沟道结构的综合性能。

实施例二

本实施例提供了一种叠层环栅的沟道结构的制备方法,参见图5,包括如下步骤:

提供一硅衬底1;

在硅衬底1上形成硅层2和支撑层3;

在硅层2的表面形成沟道层4,完成叠层环栅的沟道结构的制备。

与现有技术相比,本实施例提供的叠层环栅的沟道结构的制备方法的有益效果与实施例一提供的叠层环栅的沟道结构的有益效果基本相同,在此不一一赘述。

此外,本实施例提供的叠层环栅的沟道结构的制备方法兼容CMOS工艺,能够在8寸、12寸晶圆上制备二维材料,解决传统方法只能在小面积上制备的缺陷;同时,采用上述方法能够直接在硅衬底1上生长沟道层4,不需要传统制备方法中转移沟道层4(即WS

具体来说,在硅衬底1上形成硅层2和支撑层3包括如下步骤:

在硅衬底1上形成依次层叠的待处理支撑层6和待处理硅层5;

采用干法刻蚀的方式、以HBr/O

采用干法刻蚀的方式、以CF

需要说明的是,垂直刻蚀后得到的待释放支撑层和硅层2的宽度影响最终叠层环栅的沟道结构中的沟道的尺寸。

同样需要说明的是,由于SiGe/Si具有高选择比,在释放待处理支撑层6的同时能够最大程度的保留硅层2的形貌。

为了能够避免沟道层4形成在硅衬底1上,示例性地,在对待处理支撑层6和待处理硅层5进行垂直刻蚀得到硅层2之后,对垂直刻蚀后的待处理支撑层6进行部分释放刻蚀得到支撑层3之前,还包括如下步骤:

在硅层2的表面、垂直刻蚀后的待处理支撑层6的表面以及硅衬底1的上表面淀积SiO

这样,通过在硅衬底1上形成SiO

需要说明的是,为了能够采用WS

示例性地,采用等离子体增强原子层沉积(PEALD)在硅层2的表面形成沟道层4的工艺参数如下:基座温度为200℃~450℃,腔压为5-30Torr。

具体来说,采用等离子体增强原子层沉积(PEALD)在硅层2的表面形成沟道层4包括如下步骤:

步骤a:在硅层2、支撑层3和SiO

步骤b:保护层表面吸附WF

步骤c:惰性气体(例如,Ar和/或He)吹扫,惰性气体的流量为20~200sccm;

步骤d:采用H

步骤e:采用H

步骤f:惰性气体(例如,Ar和/或He)吹扫,惰性气体的流量为20~200sccm,形成待处理沟道层;

步骤g:对待处理沟道层进行遮掩刻蚀,刻蚀去除与支撑层3和SiO

需要说明的是,本实施例提供的形成沟道层4的方法,在形成沟道层4之前,在硅层2、支撑层3和SiO

以上所述仅为本发明较佳的具体实施方式,但本发明的保护范围并不局限于此,任何熟悉本技术领域的技术人员在本发明揭露的技术范围内,可轻易想到的变化或替换,都应涵盖在本发明的保护范围之内。

- 一种叠层环栅的沟道结构及其制备方法

- 一种先栅工艺中叠层金属栅结构的制备方法