存储器结构及其制造方法

文献发布时间:2023-06-19 11:35:49

技术领域

本发明涉及一种半导体元件及其制造方法,尤其涉及一种存储器结构及其制造方法。

背景技术

非易失性存储器元件(如,快闪存储器元件)近年来逐渐成为存储媒体的主流技术之一。然而,在非易失性存储器元件的制造过程中,难以避免地会产生一些离子,且这些离子会对存储器操作造成不良影响,进而降低存储器元件的可靠度。

发明内容

本发明提供一种存储器结构及其制造方法,其可有效地降低离子对存储器操作所造成的不良影响。

本发明提出一种存储器结构的制造方法,包括以下步骤。在基底上形成多个栅极堆叠结构。在栅极堆叠结构的侧壁上形成间隙壁层。间隙壁层连接在相邻两个栅极堆叠结构之间。形成覆盖间隙壁层与栅极堆叠结构的保护材料层。在保护材料层上形成罩幕材料层。罩幕材料层在相邻两个栅极堆叠结构之间具有孔洞。位于栅极堆叠结构正上方的保护材料层的顶部与罩幕材料层的顶部之间的第一距离大于孔洞的顶部与孔洞正上方的罩幕材料层的顶部之间的第二距离与孔洞的底部与孔洞正下方的罩幕材料层的底部之间的第三距离的总和。对罩幕材料层进行蚀刻制程,而形成彼此分离的多个第一罩幕层。第一罩幕层覆盖位于栅极堆叠结构上的保护材料层,且暴露出位于相邻两个栅极堆叠结构的底部之间的部分保护材料层。移除由第一罩幕层所暴露出的部分保护材料层,而形成彼此分离的多个保护层。

本发明提出一种存储器结构,包括基底、栅极堆叠结构、间隙壁与保护层。栅极堆叠结构设置在基底上。间隙壁设置在栅极堆叠结构的侧壁上。间隙壁在邻近于基底处具有阶梯结构。阶梯结构包括彼此相连的第一阶与第二阶。第一阶位于栅极堆叠结构与第二阶之间。第一阶高于第二阶且低于间隙壁的顶部。保护层覆盖栅极堆叠结构与间隙壁。

基于上述,在本发明所提出的存储器结构的制造方法中,由于保护层覆盖间隙壁层与栅极堆叠结构,因此可通过保护层阻挡离子进入间隙壁层及栅极堆叠结构。藉此,可有效地降低离子对存储器操作所造成的不良影响,进而可提升存储器元件的可靠度。此外,罩幕材料层在相邻两个栅极堆叠结构之间具有孔洞,且位于栅极堆叠结构正上方的保护材料层的顶部与罩幕材料层的顶部之间的第一距离大于孔洞的顶部与孔洞正上方的罩幕材料层的顶部之间的第二距离与孔洞的底部与孔洞正下方的罩幕材料层的底部之间的第三距离的总和。如此一来,在对罩幕材料层进行的蚀刻制程中,可通过自对准的方式形成彼此分离的多个第一罩幕层,进而可降低制程复杂度与制造成本。

另外,在本发明所提出的存储器结构中,由于保护层覆盖间隙壁及栅极堆叠结构,因此可通过保护层阻挡离子进入间隙壁及栅极堆叠结构。此外,由于保护层仅暴露出间隙壁的阶梯结构中的高度较低的第二阶的侧壁,因此可有效地缩小离子进入间隙壁的通道,进而降低离子进入间隙壁的数量。藉此,可有效地降低离子对存储器操作所造成的不良影响,进而可提升存储器元件的可靠度。

为让本发明的上述特征和优点能更明显易懂,下文特举实施例,并配合附图作详细说明如下。

附图说明

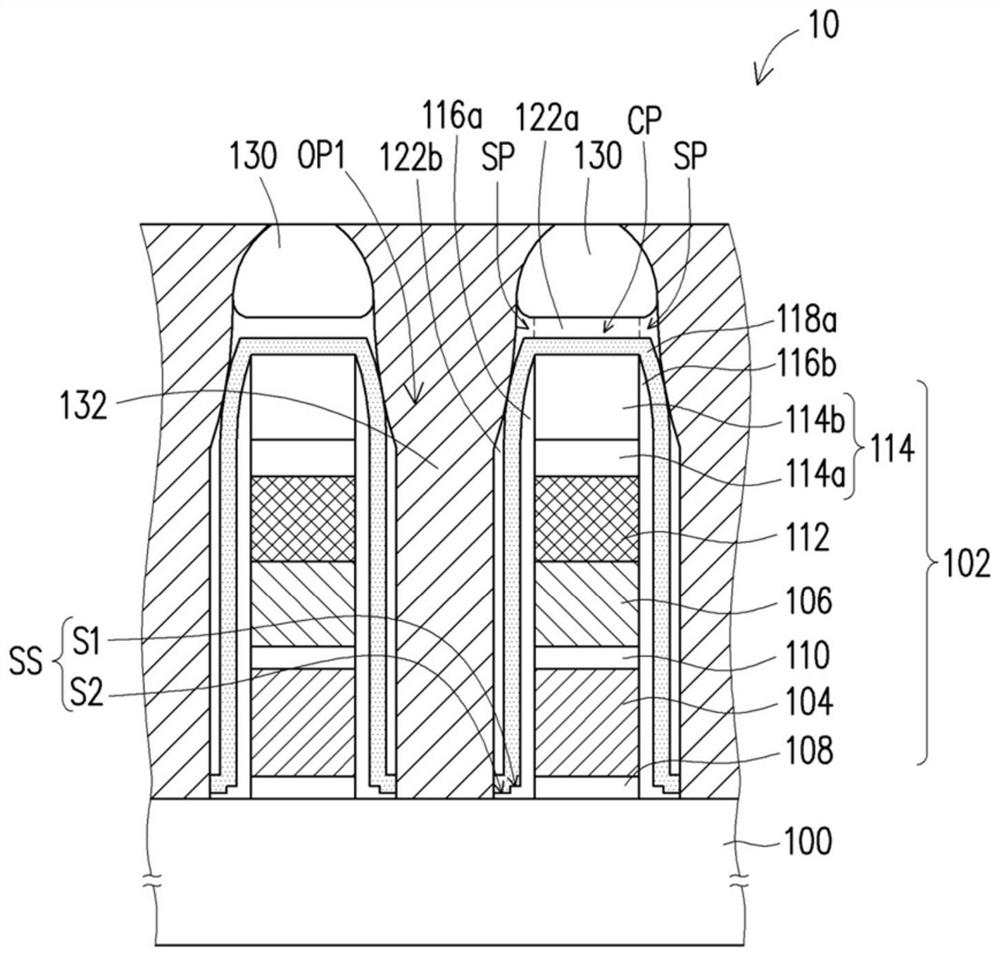

图1A至图1L为本发明一实施例的存储器结构的制造流程剖面图。

附图标号说明:

10:存储器结构

100:基底

102:栅极堆叠结构

104:电荷存储层

106:栅极

108、110、122a、122b:介电层

112:导体层

114、114a、114b:顶盖层

116:间隙壁材料层

116a:间隙壁层

116b:间隙壁

118:保护材料层

118a:保护层

120:罩幕材料罩

120a:幕幕层

122:介电材料层

124:非晶硅层

124a、126:多晶硅层

128:置换层

130:罩幕层

132:接触窗

CP:中央部

D1、D2、D3:距离

OP1、OP2:开口

S1:第一阶

S2:第二阶

SP:侧部

SS:阶梯结构

V1:孔洞

具体实施方式

请参照图1A,在基底100上形成多个栅极堆叠结构102。基底100例如是半导体基底,如硅基底。栅极堆叠结构102可包括彼此隔离的电荷存储层104与栅极106。电荷存储层104位于栅极106与基底100之间。电荷存储层104可为浮置栅极(floating gate)或电荷捕捉层(charge trapping layer)。浮置栅极的材料例如是掺杂多晶硅或未掺杂多晶硅。电荷捕捉层的材料例如是氮化硅。在本实施例中,电荷存储层104是以浮置栅极为例来进行说明,但本发明并不以此为限。此外,在相邻两个栅极堆叠结构102之间可具有开口OP1。

另外,栅极堆叠结构102还可包括介电层108、介电层110、导体层112与顶盖层114中的至少一者。介电层108位于电荷存储层104与基底100之间。介电层108的材料例如是氧化硅。介电层110位于栅极106与电荷存储层104之间,藉此电荷存储层104与栅极106可彼此隔离。介电层110的材料例如是氧化硅、氮化硅或其组合。在本实施例中,介电层110是以氧化硅层/氮化硅层/氧化硅层(ONO)的复合层为例来进行说明,但本发明并不以此为限。导体层112位于栅极106上。导体层112的材料例如是金属(如,钨)或金属硅化物(如,硅化钴或硅化镍)。顶盖层114位于导体层112上。顶盖层114可为单层结构或多层结构。在本实施例中,顶盖层114是以多层结构为例来进行说明。举例来说,顶盖层114可包括顶盖层114a与顶盖层114b。顶盖层114a位于顶盖层114b与导体层112之间。顶盖层114a的材料例如是氮化硅。顶盖层114b的材料例如是氧化硅。

另外,栅极堆叠结构102可通过沉积制程与图案化制程所形成,但本发明并不以此为限。

接着,形成覆盖栅极堆叠结构102的间隙壁材料层116。间隙壁材料层116的材料例如是氧化物材料,如氧化硅。间隙壁材料层116的形成方法例如是热氧化法或化学气相沉积法。

请参照图1B,对间隙壁材料层116进行蚀刻制程(如,干式蚀刻制程),而在栅极堆叠结构102的侧壁上形成间隙壁层116a,其中间隙壁层116a连接在相邻两个栅极堆叠结构102之间。间隙壁层116a可暴露出栅极堆叠结构102的顶部。在一些实施例中,在进行上述干式蚀刻制程的过程中,会有聚合物累积在邻近于基底100的间隙壁材料层116的角落,藉此间隙壁层116a在邻近于基底100处可具有阶梯结构SS。阶梯结构SS可包括彼此相连的第一阶S1与第二阶S2。第一阶S1位于栅极堆叠结构102与第二阶S2之间。第一阶S1可高于第二阶S2且可低于间隙壁层116a的顶部。第一阶S1与第二阶S2的连接面可包括垂直面、斜面或曲面。在本实施例中,第一阶S1与第二阶S2的连接面是以垂直面为例来进行说明。此外,虽然间隙壁层116a的形成方法是以上述方法为例,但本发明并不以此为限。

请参照图1C,形成覆盖间隙壁层116a与栅极堆叠结构102的保护材料层118。保护材料层118的材料例如是氮化物材料,如氮化硅。保护材料层118的形成方法例如是化学气相沉积法。

请参照图1D,在保护材料层118上形成罩幕材料层120。罩幕材料层120在相邻两个栅极堆叠结构102之间具有孔洞V1。位于栅极堆叠结构102正上方的保护材料层118的顶部与罩幕材料层120的顶部之间的距离D1大于孔洞V1的顶部与孔洞V1正上方的罩幕材料层120的顶部之间的距离D2与孔洞V1的底部与孔洞V1正下方的罩幕材料层120的底部之间的距离D3的总和。罩幕材料层120的材料例如是氧化物材料,如氧化硅。罩幕材料层120的形成方法例如是化学气相沉积法。

请参照图1E,对罩幕材料层120进行蚀刻制程(如,干式蚀刻制程),而形成彼此分离的多个罩幕层120a。罩幕层120a覆盖位于栅极堆叠结构102上的保护材料层118,且暴露出位于相邻两个栅极堆叠结构102的底部之间的部分保护材料层118。由于距离D1大于距离D2与距离D3的总和(图1D),因此在对罩幕材料层120进行的干式蚀刻制程中,可通过自对准的方式形成彼此分离的罩幕层120a,进而可降低制程复杂度与制造成本。

请参照图1F,移除由罩幕层120a所暴露出的部分保护材料层118,而形成彼此分离的保护层118a。保护层118a可覆盖栅极堆叠结构102的顶面与位于栅极堆叠结构102的侧壁上的间隙壁层116a。此外,保护层118a可暴露出位于相邻两个栅极堆叠结构102之间的部分间隙壁层116a。部分保护材料层118的移除方法例如是干式蚀刻法。

在一些实施例中,可在移除部分保护材料层118之后,移除罩幕层120a。举例来说,在移除部分保护材料层118的过程中,可能会消耗掉部分罩幕层120a。接着,可在移除部分保护材料层118之后,通过后续进行的清洗制程移除罩幕层120a。在一些实施例中,可在移除部分保护材料层118的过程中,同时移除罩幕层120a。

请参照图1G,可形成覆盖保护层118a与间隙壁层116a的介电材料层122。介电材料层122的材料例如是氧化物材料,如氧化硅。介电材料层122的形成方法例如是化学气相沉积法。

接着,可在介电材料层122上形成非晶硅层124。非晶硅层124的形成方法例如是化学气相沉积法。

请参照图1H,可对非晶硅层124进行回火制程,而形成多晶硅层124a。多晶硅层124a可用以作为晶种层(seed layer)。

然后,可在多晶硅层124a上沉积多晶硅层126。多晶硅层126的材料可为掺杂多晶硅或未掺杂多晶硅。在多晶硅层126的材料为掺杂多晶硅的情况下,多晶硅层126可具有较佳的填洞能力。

藉此,可在介电材料层122上形成置换层128。置换层128可包括多晶硅层124a与多晶硅层126。置换层128填满相邻两个栅极堆叠结构102之间的开口OP1。在通过上述方法来形成置换层128的情况下,置换层128可具有较佳的填洞能力,但本发明的置换层128的材料与形成方法并不以此为限。在本实施例中,置换层128是以双层结构为例,但本发明并不以此为限。在其他实施例中,置换层128可为单层结构或三层以上的结构。

请参照图1I,可移除栅极堆叠结构102的顶面上方的部分置换层128,而形成暴露出部分介电材料层122的多个开口OP2。开口OP2的形成方法例如是通过微影制程与蚀刻制程对置换层128进行图案化。此外,在形成开口OP2的制程中,可移除部分介电材料层122。

请参照图1J,可在开口OP2中形成罩幕层130。罩幕层130的材料例如是氮化物材料,如氮化硅。罩幕层130的形成方法可包括以下步骤,但本发明并不以此为限。首先,可通过沉积制程形成填满开口OP2的罩幕材料层(未示出)。然后,可通过化学机械研磨法移除开口OP2外部的罩幕材料层而形成罩幕层130。

请参照图1K,可移除置换层128。移除置换层128的移除方法例如是湿式蚀刻法或干式蚀刻法。

接着,可利用罩幕层130作为罩幕,移除位于相邻两个栅极堆叠结构102的底部之间的部分介电材料层122与部分间隙壁层116a,而在每个栅极堆叠结构102的侧壁上形成间隙壁116b,且暴露出基底100。部分介电材料层122与部分间隙壁层116a的移除方法例如是湿式蚀刻法或干式蚀刻法。在一些实施例中,在形成间隙壁116b的步骤中,可能会消耗掉部分罩幕层130,而使得罩幕层130的剖面形状近似于两边为弧形的圆角三角形。

此外,在形成间隙壁116b的步骤中,可移除位于相邻两个栅极堆叠结构102的顶部之间的部分介电材料层122,而在每个栅极堆叠结构102的顶面与侧面上方分别形成介电层122a与介电层122b,且介电层122a与介电层122b可彼此分离。介电层122a可包括中央部CP与连接于中央部CP的两侧的两个侧部SP。两个侧部SP的厚度可大于中央部CP的厚度。如此一来,介电层122a可具有近似于蝙蝠状的剖面形状。

另外,由于部分介电材料层122与部分间隙壁层116a是利用罩幕层130作为罩幕来进行移除,因此可通过自对准的方式形成间隙壁116b、介电层122a与介电层122b,进而可降低制程复杂度与制造成本。

请参照图1L,可在相邻两个栅极堆叠结构102之间的开口OP1中形成接触窗132。接触窗132可连接于基底100。接触窗132的材料例如是钨等金属。接触窗132的形成方法可包括以下步骤,但本发明并不以此为限。首先,可通过沉积制程形成填满开口OP1的接触窗材料层(未示出)。然后,可通过化学机械研磨制程移除开口OP1外部的接触窗材料层而形成接触窗132。在上述化学机械研磨制程中,可能会移除部分罩幕层130,而使得罩幕层130的剖面形状呈两侧边为弧形的梯形。

此外,在上述存储器结构10的制造方法中,可根据需求在基底100中形成所需的掺杂区(未示出)。由于在基底100中形成所需的掺杂区为所属技术领域中技术人员所周知的技术,故于此不再说明。

基于上述实施例可知,在存储器结构的制造方法10中,由于保护层118a覆盖间隙壁层116a及栅极堆叠结构102,因此可通过保护层118a阻挡离子进入间隙壁层116a及栅极堆叠结构102。藉此,可有效地降低离子对存储器操作所造成的不良影响,进而可提升存储器元件的可靠度。此外,罩幕材料层120在相邻两个栅极堆叠结构102之间具有孔洞V1,且距离D1大于距离D2与距离D3的总和(图1D)。如此一来,在对罩幕材料层120进行的干式蚀刻制程中,可通过自对准的方式形成彼此分离的多个罩幕层120a(图1E),进而可降低制程复杂度与制造成本。

以下,通过图1L来说明本实施例的存储器结构10。此外,虽然存储器结构10的形成方法是以上述方法为例进行说明,但本发明并不以此为限。

请参照图1L,存储器结构10包括基底100、栅极堆叠结构102、间隙壁116b与保护层118a。在本实施例中,存储器结构10可为反或型快闪存储器(NOR flash memory),但本发明并不以此为限。栅极堆叠结构102设置在基底100上。栅极堆叠结构102的详细内容已于上述实施例中进行说明,于此不再说明。间隙壁116b设置在栅极堆叠结构102的侧壁上。间隙壁116b在邻近于基底100处具有阶梯结构SS。阶梯结构SS包括彼此相连的第一阶S1与第二阶S2。第一阶S1位于栅极堆叠结构102与第二阶S2之间。第一阶S1高于第二阶S2且低于间隙壁116b的顶部。第一阶S1与第二阶S2的连接面可包括垂直面、斜面或曲面。间隙壁116b可暴露出栅极堆叠结构102的顶面。保护层118a覆盖栅极堆叠结构102与间隙壁116b,且暴露出第二阶S2的侧壁。保护层118a可覆盖栅极堆叠结构102的顶面。

此外,存储器结构10还可包括介电层122a、介电层122b、罩幕层130与接触窗132中的至少一者。介电层122a设置在栅极堆叠结构102的顶面上方的保护层118a上。介电层122b设置在栅极堆叠结构102的侧面上方的保护层118a上。介电层122a与介电层122b可彼此分离。介电层122a可包括中央部CP与连接于中央部CP的两侧的两个侧部SP。两个侧部SP的厚度可大于中央部CP的厚度。如此一来,介电层122a可具有近似于蝙蝠状的剖面形状。罩幕层130设置在介电层122a上。罩幕层130的剖面形状例如是两侧边为弧形的梯形,但本发明并不以此为限。接触窗132设置在栅极堆叠结构102的一侧的基底100上。接触窗132与栅极堆叠结构102可彼此隔离。接触窗可连接于基底100。

此外,存储器结构10中的各构件的材料、形成方法与功效已于上述实施例进行详尽地说明,于此不再重复说明。

基于上述实施例可知,在存储器结构10中,由于保护层118a覆盖间隙壁116b及栅极堆叠结构102,因此可通过保护层118a阻挡离子进入间隙壁116b及栅极堆叠结构102。此外,由于保护层118a仅暴露出间隙壁116b的阶梯结构SS中的高度较低的第二阶S2的侧壁,因此可有效地缩小离子进入间隙壁116b的通道,进而降低离子进入间隙壁116b的数量。藉此,可有效地降低离子对存储器操作所造成的不良影响,进而可提升存储器元件的可靠度。

综上所述,在上述实施例的存储器结构及其制造方法中,可通过保护层阻挡离子,因此可有效地降低离子对存储器操作所造成的不良影响,进而可提升存储器元件的可靠度。

虽然本发明已以实施例揭示如上,然其并非用以限定本发明,任何所属技术领域中的技术人员,在不脱离本发明的精神和范围内,当可作些许的更改与润饰,故本发明的保护范围当视权利要求所界定的为准。

- 存储器单元结构、制造存储器的方法以及存储器设备

- 存储器单元结构、制造存储器的方法以及存储器设备