图像感测装置

文献发布时间:2023-06-19 11:39:06

技术领域

本公开的各种实施方式涉及半导体设计技术,更具体地,涉及一种图像感测装置。

背景技术

图像感测装置是利用半导体的感光性质来捕获图像的装置。图像感测装置可大致分类为电荷耦合器件(CCD)图像感测装置和互补金属氧化物半导体(CMOS)图像感测装置。最近,由于CMOS图像感测装置可允许模拟控制电路和数字控制电路二者被直接实现在单个集成电路(IC)上,所以CMOS图像感测装置被广泛使用。

发明内容

本公开的各种实施方式涉及一种能够校正深度信息的图像感测装置。

根据实施方式,一种图像感测装置包括:图像传感器,其被设置为基于控制信号来校正深度信息,并且根据深度信息生成图像数据;以及控制器,其被设置为基于从图像传感器提供的第一周期信号和第二周期信号来分析深度信息的误差并且生成控制信号。

第一周期信号可用于生成发射到对象的光信号,并且第二周期信号可用于测量深度信息。

图像传感器可包括:光驱动器,其被设置为基于第一周期信号来向对象发射光信号;像素驱动器,其被设置为基于第二周期信号来生成像素驱动信号;像素阵列,其包括用于基于像素驱动信号来感测从对象反射的光信号的至少一个像素;以及校正器,其被设置为基于控制信号和时钟信号来生成各自具有占空比的第一周期信号和第二周期信号。

根据另一实施方式,一种图像感测装置包括:图像传感器,其被设置为基于控制信号来校正深度信息,并且根据深度信息生成图像数据;以及控制器,其被设置为基于图像数据来分析深度信息的误差并生成控制信号。

图像传感器可包括:光驱动器,其被设置为基于第一周期信号来向对象发射光信号;像素驱动器,其被设置为基于第二周期信号来生成像素驱动信号;像素阵列,其包括用于基于像素驱动信号来感测从对象反射的光信号的至少一个像素;以及校正器,其被设置为基于控制信号和时钟信号来生成各自具有占空比的第一周期信号和第二周期信号。

所述校正器可包括:第一负载,该第一负载被设置为生成与所述时钟信号对应的校正目标信号;占空比校正电路,该占空比校正电路被设置为基于所述控制信号,根据所述第二周期信号的占空比来校正所述校正目标信号的占空比,并生成所述第一周期信号;以及第二负载,该第二负载被设置为生成与所述时钟信号对应的所述第二周期信号。

所述占空比校正电路可包括:延迟电路,该延迟电路被设置为将所述校正目标信号依次延迟单位延迟时间,并生成多个延迟时钟信号;逻辑电路,该逻辑电路被设置为对所述多个延迟时钟信号执行逻辑运算,并生成多个操作时钟信号;以及选择电路,该选择电路被设置为基于所述控制信号来输出所述多个操作时钟信号中的任一个作为所述第一周期信号。

所述延迟电路可包括彼此串联联接的多个延迟元件组,并且可基于所述校正目标信号来输出所述多个延迟时钟信号,并且其中,各个所述延迟元件组可包括彼此串联联接的偶数个反相器。

所述逻辑电路可包括:第一逻辑元件组,该第一逻辑元件组被设置为基于所述多个延迟时钟信号当中的具有中等延迟量的延迟时钟信号和具有小于所述中等延迟量的延迟量的延迟时钟信号来生成与所述时钟信号相比具有负占空比的至少一个操作时钟信号;以及第二逻辑元件组,该第二逻辑元件组被设置为基于所述多个延迟时钟信号当中的具有所述中等延迟量的延迟时钟信号和具有大于所述中等延迟量的延迟量的延迟时钟信号来生成与所述时钟信号相比具有正占空比的至少一个操作时钟信号。

所述选择电路可包括:解码器,该解码器被设置为将所述控制信号解码,并生成选择代码信号;以及复用器,该复用器被设置为基于所述选择代码信号来输出所述多个操作时钟信号中的任一个作为所述第一周期信号。

所述校正器可包括:第一负载,该第一负载被设置为生成与所述时钟信号对应的所述第一周期信号;第二负载,该第二负载被设置为生成与所述时钟信号对应的校正目标信号;以及占空比校正电路,该占空比校正电路被设置为基于所述控制信号,根据所述第一周期信号的占空比来校正所述校正目标信号的占空比,并生成所述第二周期信号。

所述占空比校正电路可包括:延迟电路,该延迟电路被设置为将所述校正目标信号依次延迟单位延迟时间,并生成多个延迟时钟信号;逻辑电路,该逻辑电路被设置为对所述多个延迟时钟信号执行逻辑运算,并生成多个操作时钟信号;以及选择电路,该选择电路被设置为基于所述控制信号来输出所述多个操作时钟信号中的任一个作为所述第二周期信号。

所述延迟电路可包括彼此串联联接的多个延迟元件组,并且可基于所述校正目标信号来输出所述多个延迟时钟信号,并且其中,各个所述延迟元件组可包括彼此串联联接的偶数个反相器。

所述逻辑电路可包括:第一逻辑元件组,该第一逻辑元件组被设置为基于所述多个延迟时钟信号当中的具有中等延迟量的延迟时钟信号和具有小于所述中等延迟量的延迟量的延迟时钟信号来生成与所述时钟信号相比具有负占空比的至少一个操作时钟信号;以及第二逻辑元件组,该第二逻辑元件组被设置为基于所述多个延迟时钟信号当中的具有所述中等延迟量的延迟时钟信号和具有大于所述中等延迟量的延迟量的延迟时钟信号来生成与所述时钟信号相比具有正占空比的至少一个操作时钟信号。

所述选择电路可包括:解码器,该解码器被设置为将所述控制信号解码,并生成选择代码信号;以及复用器,该复用器被设置为基于所述选择代码信号来输出所述多个操作时钟信号中的任一个作为所述第二周期信号。

所述校正器可包括:第一负载,该第一负载被设置为生成与所述时钟信号对应的第一校正目标信号;第一占空比校正电路,该第一占空比校正电路被设置为基于所述控制信号和第一使能信号,根据所述第二周期信号的占空比来校正所述第一校正目标信号的占空比,并生成所述第一周期信号;第二负载,该第二负载被设置为生成与所述时钟信号对应的第二校正目标信号;以及第二占空比校正电路,该第二占空比校正电路被设置为基于所述控制信号和第二使能信号,根据所述第一周期信号的占空比来校正所述第二校正目标信号的占空比,并生成所述第二周期信号。

所述第一占空比校正电路可包括:延迟电路,该延迟电路被设置为将所述第一校正目标信号依次延迟单位延迟时间,并生成多个延迟时钟信号;逻辑电路,该逻辑电路被设置为对所述多个延迟时钟信号执行逻辑运算,并生成多个操作时钟信号;以及选择电路,该选择电路被设置为基于所述控制信号和所述第一使能信号来输出所述多个操作时钟信号中的任一个作为所述第一周期信号。

所述延迟电路可包括彼此串联联接的多个延迟元件组,并且可基于所述第一校正目标信号来输出所述多个延迟时钟信号,并且其中,各个所述延迟元件组可包括彼此串联联接的偶数个反相器。

所述逻辑电路可包括:第一逻辑元件组,该第一逻辑元件组被设置为基于所述多个延迟时钟信号当中的具有中等延迟量的延迟时钟信号和具有小于所述中等延迟量的延迟量的延迟时钟信号来生成与所述时钟信号相比具有负占空比的至少一个操作时钟信号;以及第二逻辑元件组,该第二逻辑元件组被设置为基于所述多个延迟时钟信号当中的具有所述中等延迟量的延迟时钟信号和具有大于所述中等延迟量的延迟量的延迟时钟信号来生成与所述时钟信号相比具有正占空比的至少一个操作时钟信号。

所述选择电路可包括:缓冲器,该缓冲器被设置为基于所述第一使能信号,生成与所述控制信号对应的信号,或者维持与所述控制信号无关地设定的信号;解码器,该解码器被设置为将所述信号解码,并生成选择代码信号;以及复用器,该复用器被设置为基于所述选择代码信号来输出所述多个操作时钟信号中的任一个作为所述第一周期信号。

所述第二占空比校正电路可包括:延迟电路,该延迟电路被设置为将所述第二校正目标信号依次延迟单位延迟时间,并生成多个延迟时钟信号;逻辑电路,该逻辑电路被设置为对所述多个延迟时钟信号执行逻辑运算,并生成多个操作时钟信号;以及选择电路,该选择电路被设置为基于所述控制信号和所述第二使能信号来输出所述多个操作时钟信号中的任一个作为所述第二周期信号。

所述延迟电路可包括彼此串联联接的多个延迟元件组,并且可基于所述第二校正目标信号来输出所述多个延迟时钟信号,并且其中,各个所述延迟元件组可包括彼此串联联接的偶数个反相器。

所述逻辑电路可包括:第一逻辑元件组,该第一逻辑元件组被设置为基于所述多个延迟时钟信号当中的具有中等延迟量的延迟时钟信号和具有小于所述中等延迟量的延迟量的延迟时钟信号来生成与所述时钟信号相比具有负占空比的至少一个操作时钟信号;以及第二逻辑元件组,该第二逻辑元件组被设置为基于所述多个延迟时钟信号当中的具有所述中等延迟量的延迟时钟信号和具有大于所述中等延迟量的延迟量的延迟时钟信号来生成与所述时钟信号相比具有正占空比的至少一个操作时钟信号。

所述选择电路可包括:缓冲器,该缓冲器被设置为基于所述第二使能信号,生成与所述控制信号对应的信号,或者维持与所述控制信号无关地设定的信号;解码器,该解码器被设置为将所述信号解码,并生成选择代码信号;以及复用器,该复用器被设置为基于所述选择代码信号来输出所述多个操作时钟信号中的任一个作为所述第二周期信号。

在测试模式下,所述控制器可对所述深度信息执行误差分析操作预定次数,并且静态地生成所述控制信号。

所述图像数据可以是数字信号,并且所述控制器可直接使用所述图像数据来生成所述控制信号。

所述控制器可包括:比较电路,该比较电路被设置为将所述图像数据与参考数据进行比较,并生成比较信号;以及确定电路,该确定电路被设置为基于所述比较信号,确定所述深度信息的所述误差,并生成所述控制信号。根据另一实施方式,一种图像感测装置包括:图像传感器,其被设置为基于第一控制信号和第二控制信号来校正深度信息,并且根据经校正的深度信息来生成图像数据;第一控制器,其被设置为在测试模式下基于图像数据来分析深度信息的误差并生成第一控制信号;以及第二控制器,其被设置为在正常模式下基于从图像传感器提供的第一周期信号和第二周期信号来分析深度信息的误差并生成第二控制信号。

第一周期信号可用于生成发射到对象的光信号,并且第二周期信号可用于测量深度信息。

图像传感器可包括:光驱动器,其被设置为基于第一周期信号来向对象发射光信号;像素驱动器,其被设置为基于第二周期信号来生成像素驱动信号;像素阵列,其包括用于基于像素驱动信号来感测从对象反射的光信号的至少一个像素;以及校正器,其被设置为基于第一控制信号和第二控制信号、时钟信号和测试模式信号来生成各自具有占空比的第一周期信号和第二周期信号。

所述校正器可包括:第一负载,该第一负载被设置为生成与所述时钟信号对应的校正目标信号;占空比校正电路,该占空比校正电路被设置为基于所述第一控制信号和所述第二控制信号以及所述测试模式信号,根据所述第二周期信号的占空比来校正所述校正目标信号的占空比,并生成所述第一周期信号;以及第二负载,该第二负载被设置为生成与所述时钟信号对应的所述第二周期信号。

所述占空比校正电路可包括:延迟电路,该延迟电路被设置为将所述校正目标信号依次延迟单位延迟时间,并生成多个延迟时钟信号;逻辑电路,该逻辑电路被设置为对所述多个延迟时钟信号执行逻辑运算,并生成多个操作时钟信号;以及选择电路,该选择电路被设置为基于所述第一控制信号和所述第二控制信号以及所述测试模式信号来输出所述多个操作时钟信号中的任一个作为所述第一周期信号。

所述延迟电路可包括彼此串联联接的多个延迟元件组,并且可基于所述校正目标信号输出所述多个延迟时钟信号,并且其中,各个所述延迟元件组可包括彼此串联联接的偶数个反相器。

所述逻辑电路可包括:第一逻辑元件组,该第一逻辑元件组被设置为基于所述多个延迟时钟信号当中的具有中等延迟量的延迟时钟信号和具有小于所述中等延迟量的延迟量的延迟时钟信号来生成与所述时钟信号相比具有负占空比的至少一个操作时钟信号;以及第二逻辑元件组,该第二逻辑元件组被设置为基于所述多个延迟时钟信号当中的具有所述中等延迟量的延迟时钟信号和具有大于所述中等延迟量的延迟量的延迟时钟信号来生成与所述时钟信号相比具有正占空比的至少一个操作时钟信号。

所述选择电路可包括:第一复用器,该第一复用器被设置为基于所述测试模式信号来输出所述第一控制信号和所述第二控制信号中的任一个作为控制信号;解码器,该解码器被设置为将所述控制信号解码,并生成选择代码信号;以及第二复用器,该第二复用器被设置为基于所述选择代码信号来输出所述多个操作时钟信号中的任一个作为所述第一周期信号。

所述校正器可包括:第一负载,该第一负载被设置为生成与所述时钟信号对应的所述第一周期信号;第二负载,该第二负载被设置为生成与所述时钟信号对应的校正目标信号;以及占空比校正电路,该占空比校正电路被设置为基于所述第一控制信号和所述第二控制信号以及所述测试模式信号,根据所述第一周期信号的占空比来校正所述校正目标信号的占空比,并生成所述第二周期信号。

所述占空比校正电路可包括:延迟电路,该延迟电路被设置为将所述校正目标信号依次延迟单位延迟时间,并生成多个延迟时钟信号;逻辑电路,该逻辑电路被设置为对所述多个延迟时钟信号执行逻辑运算,并生成多个操作时钟信号;以及选择电路,该选择电路被设置为基于所述第一控制信号和所述第二控制信号以及所述测试模式信号来输出所述多个操作时钟信号中的任一个作为所述第二周期信号。

所述延迟电路可包括彼此串联联接的多个延迟元件组,并且可基于所述校正目标信号来输出所述多个延迟时钟信号,并且其中,各个所述延迟元件组可包括彼此串联联接的偶数个反相器。

所述逻辑电路可包括:第一逻辑元件组,该第一逻辑元件组被设置为基于所述多个延迟时钟信号当中的具有中等延迟量的延迟时钟信号和具有小于所述中等延迟量的延迟量的延迟时钟信号来生成与所述时钟信号相比具有负占空比的至少一个操作时钟信号;以及第二逻辑元件组,该第二逻辑元件组被设置为基于所述多个延迟时钟信号当中的具有所述中等延迟量的延迟时钟信号和具有大于所述中等延迟量的延迟量的延迟时钟信号来生成与所述时钟信号相比具有正占空比的至少一个操作时钟信号。

所述选择电路可包括:第一复用器,该第一复用器被设置为基于所述测试模式信号来输出所述第一控制信号和所述第二控制信号中的任一个作为控制信号;解码器,该解码器被设置为将所述控制信号解码,并生成选择代码信号;以及第二复用器,该第二复用器被设置为基于所述选择代码信号来输出所述多个操作时钟信号中的任一个作为所述第二周期信号。

所述校正器可包括:第一负载,该第一负载被设置为生成与所述时钟信号对应的第一校正目标信号;第一占空比校正电路,该第一占空比校正电路被设置为基于所述第一控制信号和所述第二控制信号、所述测试模式信号和第一使能信号,根据所述第二周期信号的占空比来校正所述第一校正目标信号的占空比,并生成所述第一周期信号;第二负载,该第二负载被设置为生成与所述时钟信号对应的第二校正目标信号;以及第二占空比校正电路,该第二占空比校正电路被设置为基于所述第一控制信号和所述第二控制信号、所述测试模式信号和第二使能信号,根据所述第一周期信号的占空比来校正所述第二校正目标信号的占空比,并生成所述第二周期信号。

所述第一占空比校正电路可包括:延迟电路,该延迟电路被设置为将所述第一校正目标信号依次延迟单位延迟时间,并生成多个延迟时钟信号;逻辑电路,该逻辑电路被设置为对所述多个延迟时钟信号执行逻辑运算,并生成多个操作时钟信号;以及选择电路,该选择电路被设置为基于所述第一控制信号和所述第二控制信号、所述测试模式信号和所述第一使能信号来输出所述多个操作时钟信号中的任一个作为所述第一周期信号。

所述延迟电路可包括彼此串联联接的多个延迟元件组,并且可基于所述第一校正目标信号来输出所述多个延迟时钟信号,并且其中,各个所述延迟元件组可包括彼此串联联接的偶数个反相器。

所述逻辑电路可包括:第一逻辑元件组,该第一逻辑元件组被设置为基于所述多个延迟时钟信号当中的具有中等延迟量的延迟时钟信号和具有小于所述中等延迟量的延迟量的延迟时钟信号来生成与所述时钟信号相比具有负占空比的至少一个操作时钟信号;以及第二逻辑元件组,该第二逻辑元件组被设置为基于所述多个延迟时钟信号当中的具有所述中等延迟量的延迟时钟信号和具有大于所述中等延迟量的延迟量的延迟时钟信号来生成与所述时钟信号相比具有正占空比的至少一个操作时钟信号。

所述选择电路可包括:第一复用器,该第一复用器被设置为基于所述测试模式信号来输出所述第一控制信号和所述第二控制信号中的任一个作为控制信号;缓冲器,该缓冲器被设置为基于所述第一使能信号,生成与所述控制信号对应的信号,或者维持与所述控制信号无关地设定的信号;解码器,该解码器被设置为将所述信号解码,并生成选择代码信号;以及第二复用器,该第二复用器被设置为基于所述选择代码信号来输出所述多个操作时钟信号中的任一个作为所述第一周期信号。

所述第二占空比校正电路可包括:延迟电路,该延迟电路被设置为将所述第二校正目标信号依次延迟单位延迟时间,并生成多个延迟时钟信号;逻辑电路,该逻辑电路被设置为对所述多个延迟时钟信号执行逻辑运算,并生成多个操作时钟信号;以及选择电路,该选择电路被设置为基于所述第一控制信号和所述第二控制信号、所述测试模式信号和所述第二使能信号来输出所述多个操作时钟信号中的任一个作为所述第二周期信号。

所述延迟电路可包括彼此串联联接的多个延迟元件组,并且被设置为基于所述第二校正目标信号来输出所述多个延迟时钟信号,并且其中,各个所述延迟元件组可包括彼此串联联接的偶数个反相器。

所述逻辑电路可包括:第一逻辑元件组,该第一逻辑元件组被设置为基于所述多个延迟时钟信号当中的具有中等延迟量的延迟时钟信号和具有小于所述中等延迟量的延迟量的延迟时钟信号来生成与所述时钟信号相比具有负占空比的至少一个操作时钟信号;以及第二逻辑元件组,该第二逻辑元件组被设置为基于所述多个延迟时钟信号当中的具有所述中等延迟量的延迟时钟信号和具有大于所述中等延迟量的延迟量的延迟时钟信号来生成与所述时钟信号相比具有正占空比的至少一个操作时钟信号。

所述选择电路可包括:第一复用器,该第一复用器被设置为基于所述测试模式信号来输出所述第一控制信号和所述第二控制信号中的任一个作为控制信号;缓冲器,该缓冲器被设置为基于所述第二使能信号,生成与所述控制信号对应的信号,或者维持与所述控制信号无关地设定的信号;解码器,该解码器被设置为将所述信号解码,并生成选择代码信号;以及第二复用器,该第二复用器被设置为基于所述选择代码信号来输出所述多个操作时钟信号中的任一个作为所述第二周期信号。

在所述测试模式下,所述第一控制器可对所述深度信息执行误差分析操作预定次数,并可静态地生成所述第一控制信号,并且在所述正常模式下,所述第二控制器可对所述深度信息实时执行所述误差分析操作,并可动态地生成所述第二控制信号。

所述第一控制器可包括:比较电路,该比较电路被设置为将所述图像数据与参考数据进行比较,并生成比较信号;以及确定电路,该确定电路被设置为基于所述比较信号,确定所述深度信息的所述误差,并生成所述第一控制信号。

所述图像数据可以是数字信号,并且所述第一控制器可直接使用所述图像数据来生成所述控制信号。

所述第二控制器可包括:检测电路,该检测电路被设置为检测所述第一周期信号和所述第二周期信号之间的占空比差,并生成检测信号;以及转换电路,该转换电路被设置为将所述检测信号转换为数字信号,并输出所述控制信号。

根据另一实施方式,提出了一种用于校正包括在图像感测装置所获取的对象的图像数据中的深度信息的方法,其中,深度信息包括图像感测装置与对象之间的距离,该方法包括以下步骤:生成第一周期信号,该第一周期信号用于生成从图像感测装置发射到对象的光信号;生成用于测量深度信息的第二周期信号;比较第一周期信号的第一占空比和第二周期信号的第二占空比,以检测第一占空比和第二占空比之间的占空比差;以及调节第一占空比和第二占空比之间的占空比差以校正深度信息。

根据另一实施方式,提出了一种用于校正包括在图像感测装置所获取的对象的图像数据中的深度信息的方法,其中,深度信息包括图像感测装置与对象之间的距离,该方法包括以下步骤:生成第一周期信号,该第一周期信号用于生成从图像感测装置发射到对象的光信号;生成用于测量深度信息的第二周期信号;分析图像感测装置所获取的深度信息以检测深度信息的误差;以及调节第一周期信号的第一占空比和第二周期信号的第二占空比之间的差,以校正深度信息的误差。

对于本发明领域的技术人员而言,本公开的这些和其它特征和优点将从以下结合附图的详细描述而变得显而易见。

附图说明

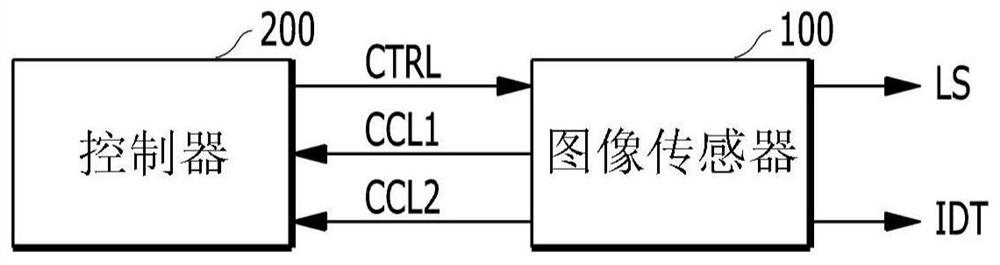

图1是示出根据本发明的各种实施方式的图像感测装置的框图。

图2是示出根据本发明的各种实施方式的图1所示的图像传感器的框图。

图3是示出根据本发明的各种实施方式的图2所示的校正器的示例的框图。

图4是示出根据本发明的各种实施方式的图3所示的占空比校正电路的框图。

图5是示出根据本发明的各种实施方式的图2所示的校正器的另一示例的框图。

图6是示出根据本发明的各种实施方式的图5所示的占空比校正电路的框图。

图7是示出根据本发明的各种实施方式的图2所示的校正器的另一示例的框图。

图8是示出根据本发明的各种实施方式的图7所示的第一占空比校正电路的框图。

图9是示出根据本发明的各种实施方式的图7所示的第二占空比校正电路的框图。

图10是示出根据本发明的各种实施方式的图1所示的控制器的框图。

图11是示出根据本发明的各种实施方式的图像感测装置的操作的示例的时序图。

图12是示出根据本发明的各种实施方式的图像感测装置的操作的另一示例的时序图。

图13是示出根据本发明的各种实施方式的图像感测装置的框图。

图14是示出根据本发明的各种实施方式的图13所示的图像传感器的框图。

图15是示出根据本发明的各种实施方式的图14所示的校正器的示例的框图。

图16是示出根据本发明的各种实施方式的图15所示的占空比校正电路的框图。

图17是示出根据本发明的各种实施方式的图14所示的校正器的另一示例的框图。

图18是示出根据本发明的各种实施方式的图17所示的占空比校正电路的框图。

图19是示出根据本发明的各种实施方式的图14所示的校正器的另一示例的框图。

图20是示出根据本发明的各种实施方式的图19所示的的第一占空比校正电路的框图。

图21是示出根据本发明的各种实施方式的图19所示的第二占空比校正电路的框图。

图22是示出根据本发明的各种实施方式的图13所示的控制器的框图。

图23是示出根据本发明的各种实施方式的图像感测装置的操作的示例的时序图。

图24是示出根据本发明的各种实施方式的图像感测装置的操作的另一示例的时序图。

图25是示出根据本发明的各种实施方式的图像感测装置的框图。

图26是示出根据本发明的各种实施方式的图25所示的图像传感器的框图。

图27是示出根据本发明的各种实施方式的图26所示的校正器的示例的框图。

图28是示出根据本发明的各种实施方式的图27所示的占空比校正电路的框图。

图29是示出根据本发明的各种实施方式的图26所示的校正器的另一示例的框图。

图30是示出根据本发明的各种实施方式的图29所示的占空比校正电路的框图。

图31是示出根据本发明的各种实施方式的图26所示的校正器的另一示例的框图。

图32是示出根据本发明的各种实施方式的图31所示的第一占空比校正电路的框图。

图33是示出根据本发明的各种实施方式的图31所示的第二占空比校正电路的框图。

图34是示出根据本发明的各种实施方式的图25所示的第一控制器的框图。

图35是示出根据本发明的各种实施方式的图25所示的第二控制器的框图。

图36是示出根据本发明的各种实施方式的图像感测装置的操作的示例的时序图。

图37是示出根据本发明的各种实施方式的图像感测装置的操作的另一示例的时序图。

具体实施方式

下面参照附图更详细地描述各种实施方式。提供这些实施方式以使得本公开彻底和完整,并且向本领域技术人员充分传达本公开的范围。

将理解,当元件被称为“连接到”或“联接到”另一元件时,它可直接在另一元件上、连接到另一元件或联接到另一元件,或者可存在一个或更多个中间元件。另外,还将理解,术语“包括”和“包含”当用在本说明书中时指定存在所述元件,并且不排除一个或更多个其它元件的存在或添加。如本文所使用的,除非上下文清楚地另外指示,否则单数形式也可包括复数形式,反之亦然。除非另外指明或者从上下文清楚指向单数形式,否则如本申请和所附权利要求中使用的冠词“一个”和“一种”通常应该解释为“一个或更多个”。

图1是示出根据本发明的各种实施方式的图像感测装置的框图。

参照图1,图像感测装置可包括图像传感器100和控制器200。

图像传感器100可基于控制信号CTRL来校正深度信息,并根据经校正的深度信息来生成图像数据IDT。深度信息可包括关于图像传感器100与对象(未示出)之间的距离的信息。

图像传感器100可向控制器200提供生成图像数据IDT所需的第一周期信号CCL1和第二周期信号CCL2。第一周期信号CCL1可用于生成发射到对象(未示出)的光信号LS。第二周期信号CCL2可用于测量深度信息。

基于从图像传感器100提供的第一周期信号CCL1和第二周期信号CCL2,控制器200可分析深度信息的误差,并生成控制信号CTRL。在正常模式下,控制器200可实时地对深度信息执行误差分析操作,并动态地生成控制信号CTRL。

控制器200和图像传感器100可被集成到同一芯片(即,芯片上)或不同的芯片(即,芯片外)中。

图2是示出图1所示的图像传感器100的框图。

参照图2,图像传感器100可包括时钟发生器110、校正器120、光驱动器130、像素驱动器140、行解码器150、像素阵列160、信号转换器170和图像处理器180。

在正常模式下,时钟发生器110可生成时钟信号CLK。例如,时钟发生器110可包括锁相环或振荡器。

校正器120可基于控制信号CTRL和时钟信号CLK来生成各自具有占空比的第一周期信号CCL1和第二周期信号CCL2。第一周期信号CCL1和第二周期信号CCL2可被设计为具有相同的占空比。另选地,第一周期信号CCL1和第二周期信号CCL2可被设计为具有不同的占空比。在本实施方式中,作为示例描述了第一周期信号CCL1和第二周期信号CCL2被设计为具有相同的占空比。

光驱动器130可基于第一周期信号CCL1向对象发射光信号LS。例如,光驱动器130可包括发光二极管或激光二极管。

像素驱动器140可基于第二周期信号CCL2来生成像素驱动信号PX_DRV。像素驱动信号PX_DRV可以是用于测量深度信息的信号之一。

行解码器150可生成用于逐行控制像素阵列160的行控制信号RCTRL。

像素阵列160可包括设置在多行和多列的交叉处的多个像素。多个像素可包括用于测量深度信息的至少一个深度测量像素。深度测量像素可基于像素驱动信号PX_DRV来感测从对象反射的光信号(未示出)。反射的光信号可以是通过从对象反射光信号LS而获得的信号。即,深度测量像素可基于像素驱动信号PX_DRV和反射的光信号来生成与深度信息对应的像素信号PX。

信号转换器170可将像素信号PX转换为数字信号DOUT。例如,信号转换器170可包括相关双采样电路和模数转换器。

图像处理器180可基于数字信号DOUT来生成图像数据IDT。图像数据IDT可包括深度信息。

图3是示出图2所示的校正器120的示例的框图。

参照图3,校正器120可包括第一负载L1、占空比校正电路DCC和第二负载L2。

第一负载L1可生成与时钟信号CLK对应的校正目标信号CCL11。第一负载L1可包括生成校正目标信号CCL11的第一路径中出现的第一线路负载。第一线路负载可包括在第一路径中直接或间接形成的所有负载。另外,第一负载L1可被设计为还包括用于调谐时钟信号CLK的第一电路。当经过第一负载L1时,校正目标信号CCL11的占空比可与时钟信号CLK的占空比不同地改变。即,可无意地调节校正目标信号CCL11的占空比。

占空比校正电路DCC可基于控制信号CTRL和校正目标信号CCL11来生成第一周期信号CCL1。例如,占空比校正电路DCC可通过将校正目标信号CCL11的占空比校正为与第二周期信号CCL2的占空比相一致来生成第一周期信号CCL1。

第二负载L2可生成与时钟信号CLK对应的第二周期信号CCL2。第二负载L2可包括生成第二周期信号CCL2的第二路径中出现的第二线路负载。第二线路负载可包括第二路径中直接或间接形成的所有负载。另外,第二负载L2可被设计为还包括用于调谐时钟信号CLK的第二电路。当经过第二负载L2时,第二周期信号CCL2的占空比可与时钟信号CLK的占空比不同地改变。换言之,可无意地调节第二周期信号CCL2的占空比。在这种情况下,第二周期信号CCL2的占空比可不同于校正目标信号CCL11的占空比。

图4是示出图3所示的占空比校正电路DCC的框图。要注意的是,包括在图4的占空比校正电路DCC中的元件、元件组和信号的数量是为了描述方便而作为示例描述,本公开不限于此。

参照图4,占空比校正电路DCC可包括延迟电路121、逻辑电路123和选择电路125。

延迟电路121可将校正目标信号CCL11依次延迟单位延迟时间,并生成第一延迟时钟信号D1至第五延迟时钟信号D5。延迟电路121可包括彼此串联联接的第一延迟元件组DLY1至第五延迟元件组DLY5。第一延迟元件组DLY1至第五延迟元件组DLY5中的每一个可将校正目标信号CCL11和先前延迟时钟信号D1至D4中的任一个延迟单位延迟时间,并输出延迟时钟信号D1至D5中的每一个。例如,第一延迟元件组DLY1可将校正目标信号CCL11延迟单位延迟时间以生成延迟时钟信号D1。第二延迟元件组DLY2可将延迟时钟信号D1延迟单位延迟时间以生成延迟时钟信号D2。第三延迟元件组DLY3可将延迟时钟信号D2延迟单位延迟时间以生成延迟时钟信号D3。第四延迟元件组DLY4可将延迟时钟信号D3延迟单位延迟时间以生成延迟时钟信号D4。第五延迟元件组DLY5可将延迟时钟信号D4延迟单位延迟时间以生成延迟时钟信号D5。第一延迟元件组DLY1至第五延迟元件组DLY5中的每一个可包括彼此串联联接的偶数个反相器。尽管在本实施方式中作为示例描述了各个延迟元件组包括反相器,但本公开不限于此。在各种实施方式中,各个延迟元件组可被设计为包括电阻器和电容器。

逻辑电路123可对第一延迟时钟信号D1至第五延迟时钟信号D5中的每一个执行逻辑运算,并生成第一操作时钟信号L1至第四操作时钟信号L4。逻辑电路123可包括第一逻辑元件组123A和第二逻辑元件组123B。

第一逻辑元件组123A可基于第一延迟时钟信号D1至第五延迟时钟信号D5当中的具有中等延迟量的第三延迟时钟信号D3以及具有小于中等延迟量的延迟量的第一延迟时钟信号D1和第二延迟时钟信号D2来生成第一操作时钟信号L1至第四操作时钟信号L4当中的与时钟信号CLK相比具有负占空比的第一操作时钟信号L1和第二操作时钟信号L2。例如,第一逻辑元件组123A可包括第一与门AG1和第二与门AG2。第一与门AG1可对第一延迟时钟信号D1和具有中等延迟量的第三延迟时钟信号D3执行逻辑与运算,并生成第一操作时钟信号L1。第二与门AG2可对第二延迟时钟信号D2和具有中等延迟量的第三延迟时钟信号D3执行逻辑与运算,并生成第二操作时钟信号L2。另外,可分别基于第一功率门控信号PG1和第二功率门控信号PG2来启用或禁用第一与门AG1和第二与门AG2。因此,可节省由第一与门AG1和第二与门AG2不必要地消耗的功率。

第二逻辑元件组123B可基于具有中等延迟量的第三延迟时钟信号D3以及具有大于中等延迟量的延迟量的第四延迟时钟信号D4和第五延迟时钟信号D5来生成与时钟信号CLK相比具有正占空比的第三操作时钟信号L3和第四操作时钟信号L4。例如,第二逻辑元件组123B可包括第一或门OG1和第二或门OG2。第一或门OG1可对第四延迟时钟信号D4和具有中等延迟量的第三延迟时钟信号D3执行逻辑或运算,并生成第三操作时钟信号L3。第二或门OG2可对第五延迟时钟信号D5和具有中等延迟量的第三延迟时钟信号D3执行逻辑或运算,并生成第四操作时钟信号L4。另外,可分别基于第三功率门控信号PG3和第四功率门控信号PG4来启用或禁用第一或门OG1和第二或门OG2。因此,可节省由第一或门OG1和第二或门OG2不必要地消耗的功率。

选择电路125可包括解码器DEC和复用器MUX。

解码器DEC可将控制信号CTRL解码,并生成选择代码信号DO。例如,当必须减小校正目标信号CCL11的占空比时,解码器DEC可生成用于允许第一操作时钟信号L1和第二操作时钟信号L2之一被选为第一周期信号CCL1的选择代码信号DO。另一方面,当必须增大校正目标信号CCL11的占空比时,解码器DEC可生成用于允许第三操作时钟信号L3和第四操作时钟信号L4之一被选为第一周期信号CCL1的选择代码信号DO。另外,解码器DEC可生成第一功率门控信号PG1至第四功率门控信号PG4。例如,当选择第一操作时钟信号L1时,解码器DEC可停用第一功率门控信号PG1,并启用第二功率门控信号PG2至第四功率门控信号PG4。

复用器MUX可基于选择代码信号DO来输出第一操作时钟信号L1至第四操作时钟信号L4中的任一个作为第一周期信号CCL1。

图5是示出图2所示的校正器120的另一示例的框图。

参照图5,校正器120可包括第一负载L1、第二负载L2和占空比校正电路DCC。

第一负载L1可生成与时钟信号CLK对应的第一周期信号CCL1。第一负载L1可包括生成第一周期信号CCL1的第一路径中出现的第一线路负载。第一线路负载可包括第一路径中直接或间接形成的所有负载。另外,第一负载L1可被设计为还包括用于调谐时钟信号CLK的第一电路。当经过第一负载L1时,第一周期信号CCL1的占空比可与时钟信号CLK的占空比不同地改变。换言之,可无意地调节第一周期信号CCL1的占空比。

第二负载L2可生成与时钟信号CLK对应的校正目标信号CCL22。第二负载L2可包括生成校正目标信号CCL22的第二路径中出现的第二线路负载。第二线路负载可包括第二路径中直接或间接形成的所有负载。另外,第二负载L2可被设计为还包括用于调谐时钟信号CLK的第二电路。当经过第二负载L2时,校正目标信号CCL22的占空比可与时钟信号CLK的占空比不同地改变。换言之,可无意地调节校正目标信号CCL22的占空比。在这种情况下,校正目标信号CCL22的占空比可不同于第一周期信号CCL1的占空比。

占空比校正电路DCC可基于控制信号CTRL和校正目标信号CCL22来生成第二周期信号CCL2。例如,占空比校正电路DCC可通过将校正目标信号CCL22的占空比校正为与第一周期信号CCL1的占空比相一致来生成第二周期信号CCL2。

图6是示出图5所示的占空比校正电路DCC的框图。要注意的是,包括在图6的占空比校正电路DCC中的元件、元件组和信号的数量是为了描述方便而作为示例描述,本公开不限于此。

参照图6,占空比校正电路DCC可包括延迟电路121、逻辑电路123和选择电路125。

延迟电路121可将校正目标信号CCL22依次延迟单位延迟时间,并生成第一延迟时钟信号D1至第五延迟时钟信号D5。延迟电路121可包括彼此串联联接的第一延迟元件组DLY1至第五延迟元件组DLY5。第一延迟元件组DLY1至第五延迟元件组DLY5中的每一个可将校正目标信号CCL22和先前延迟时钟信号D1至D4中的任一个延迟单位延迟时间,并输出延迟时钟信号D1至D5中的每一个。例如,第一延迟元件组DLY1可将校正目标信号CCL22延迟单位延迟时间以生成延迟时钟信号D1。第二延迟元件组DLY2可将延迟时钟信号D1延迟单位延迟时间以生成延迟时钟信号D2。第三延迟元件组DLY3可将延迟时钟信号D2延迟单位延迟时间以生成延迟时钟信号D3。第四延迟元件组DLY4可将延迟时钟信号D3延迟单位延迟时间以生成延迟时钟信号D4。第五延迟元件组DLY5可将延迟时钟信号D4延迟单位延迟时间以生成延迟时钟信号D5。第一延迟元件组DLY1至第五延迟元件组DLY5中的每一个可包括彼此串联联接的偶数个反相器。尽管在本实施方式中作为示例描述了各个延迟元件组包括反相器,但本公开不限于此。在各种实施方式中,各个延迟元件组可被设计为包括电阻器和电容器。

逻辑电路123可对第一延迟时钟信号D1至第五延迟时钟信号D5中的每一个执行逻辑运算,并生成第一操作时钟信号L1至第四操作时钟信号L4。逻辑电路123可包括第一逻辑元件组123A和第二逻辑元件组123B。

第一逻辑元件组123A可基于第一延迟时钟信号D1至第五延迟时钟信号D5当中的具有中等延迟量的第三延迟时钟信号D3以及具有小于中等延迟量的延迟量的第一延迟时钟信号D1和第二延迟时钟信号D2来生成与时钟信号CLK相比具有负占空比的第一操作时钟信号L1和第二操作时钟信号L2。例如,第一逻辑元件组123A可包括第一与门AG1和第二与门AG2。第一与门AG1可对第一延迟时钟信号D1和具有中等延迟量的第三延迟时钟信号D3执行逻辑与运算,并生成第一操作时钟信号L1。第二与门AG2可对第二延迟时钟信号D2和具有中等延迟量的第三延迟时钟信号D3执行逻辑与运算,并生成第二操作时钟信号L2。另外,可分别基于第一功率门控信号PG1和第二功率门控信号PG2来启用或禁用第一与门AG1和第二与门AG2。因此,可节省由第一与门AG1和第二与门AG2不必要地消耗的功率。

第二逻辑元件组123B可基于第一延迟时钟信号D1至第五延迟时钟信号D5当中的具有中等延迟量的第三延迟时钟信号D3以及具有大于中等延迟量的延迟量的第四延迟时钟信号D4和第五延迟时钟信号D5来生成与时钟信号CLK相比具有正占空比的第三操作时钟信号L3和第四操作时钟信号L4。例如,第二逻辑元件组123B可包括第一或门OG1和第二或门OG2。第一或门OG1可对第四延迟时钟信号D4和具有中等延迟量的第三延迟时钟信号D3执行逻辑或运算,并生成第三操作时钟信号L3。第二或门OG2可对第五延迟时钟信号D5和具有中等延迟量的第三延迟时钟信号D3执行逻辑或运算,并生成第四操作时钟信号L4。另外,可分别基于第三功率门控信号PG3和第四功率门控信号PG4来启用或禁用第一或门OG1和第二或门OG2。因此,可节省由第一或门OG1和第二或门OG2不必要地消耗的功率。

选择电路125可包括解码器DEC和复用器MUX。

解码器DEC可将控制信号CTRL解码,并生成选择代码信号DO。例如,当必须减小校正目标信号CCL22的占空比时,解码器DEC可生成用于允许第一操作时钟信号L1和第二操作时钟信号L2之一被选为第二周期信号CCL2的选择代码信号DO。另一方面,当必须增大校正目标信号CCL22的占空比时,解码器DEC可生成用于允许第三操作时钟信号L3和第四操作时钟信号L4之一被选为第二周期信号CCL2的选择代码信号DO。另外,解码器DEC可生成第一功率门控信号PG1至第四功率门控信号PG4。例如,当选择第一操作时钟信号L1时,解码器DEC可停用第一功率门控信号PG1,并启用第二功率门控信号PG2至第四功率门控信号PG4。

复用器MUX可基于选择代码信号DO来输出第一操作时钟信号L1至第四操作时钟信号L4之一作为第二周期信号CCL2。

图7是示出图2所示的校正器120的另一示例的框图。

参照图7,校正器120可包括第一负载L1、第一占空比校正电路DCC1、第二负载L2和第二占空比校正电路DCC2。

第一负载L1可生成与时钟信号CLK对应的第一校正目标信号CCL11。第一负载L1可包括生成第一校正目标信号CCL11的第一路径中出现的第一线路负载。第一线路负载可包括第一路径中直接或间接形成的所有负载。另外,第一负载L1可被设计为还包括用于调谐时钟信号CLK的第一电路。当经过第一负载L1时,第一校正目标信号CCL11的占空比可与时钟信号CLK的占空比不同地改变。即,可无意地调节第一校正目标信号CCL11的占空比。

第一占空比校正电路DCC1可基于控制信号CTRL和第一校正目标信号CCL11来生成第一周期信号CCL1。例如,第一占空比校正电路DCC1可通过将第一校正目标信号CCL11的占空比校正为与第二周期信号CCL2的占空比相一致来生成第一周期信号CCL1。可基于第一使能信号EN来启用第一占空比校正电路DCC1。第一使能信号EN可在图像传感器100中生成或从控制器200提供。

第二负载L2可生成与时钟信号CLK对应的第二校正目标信号CCL22。第二负载L2可包括生成第二校正目标信号CCL22的第二路径中出现的第二线路负载。第二线路负载可包括第二路径中直接或间接形成的所有负载。另外,第二负载L2可被设计为还包括用于调谐时钟信号CLK的第二电路。当经过第二负载L2时,第二校正目标信号CCL22的占空比可与时钟信号CLK的占空比不同地改变。即,可无意地调节第二校正目标信号CCL22的占空比。在这种情况下,第二校正目标信号CCL22的占空比可不同于第一校正目标信号CCL11的占空比。

第二占空比校正电路DCC2可基于控制信号CTRL和第二校正目标信号CCL22来生成第二周期信号CCL2。例如,第二占空比校正电路DCC2可通过将第二校正目标信号CCL22的占空比校正为与第一周期信号CCL1的占空比相一致来生成第二周期信号CCL2。可基于第二使能信号ENB来启用第二占空比校正电路DCC2。第二使能信号ENB可以是通过将第一使能信号EN反相而获得的信号。

图8是示出图7所示的第一占空比校正电路DCC1的框图。包括在图8的第一占空比校正电路DCC1中的元件、元件组和信号的数量是为了描述方便而作为示例描述,本公开不限于此。

参照图8,第一占空比校正电路DCC1可包括延迟电路121、逻辑电路122和选择电路123。

延迟电路121可将第一校正目标信号CCL11依次延迟单位延迟时间,并生成第一延迟时钟信号D11至第五延迟时钟信号D15。延迟电路121可包括彼此串联联接的第一延迟元件组DLY11至第五延迟元件组DLY15。第一延迟元件组DLY11至第五延迟元件组DLY15中的每一个可将第一校正目标信号CCL11以及先前延迟时钟信号D11至D14中的任一个延迟单位延迟时间,并输出延迟时钟信号D11至D15。例如,第一延迟元件组DLY11可将校正目标信号CCL11延迟单位延迟时间以生成延迟时钟信号D1。第二延迟元件组DLY12可将延迟时钟信号D1延迟单位延迟时间以生成延迟时钟信号D2。第三延迟元件组DLY13可将延迟时钟信号D2延迟单位延迟时间以生成延迟时钟信号D3。第四延迟元件组DLY14可将延迟时钟信号D3延迟单位延迟时间以生成延迟时钟信号D4。第五延迟元件组DLY15可将延迟时钟信号D4延迟单位延迟时间以生成延迟时钟信号D5。第一延迟元件组DLY11至第五延迟元件组DLY15中的每一个可包括彼此串联联接的偶数个反相器。尽管在本实施方式中作为示例描述了各个延迟元件组包括反相器,但本公开不限于此。在各种实施方式中,各个延迟元件组可被设计为包括电阻器和电容器。

逻辑电路122可对第一延迟时钟信号D11至第五延迟时钟信号D15中的每一个执行逻辑运算,并生成第一操作时钟信号L11至第四操作时钟信号L14。逻辑电路122可包括第一逻辑元件组122A和第二逻辑元件组122B。

第一逻辑元件组122A可基于第一延迟时钟信号D11至第五延迟时钟信号D15当中的具有中等延迟量的第三延迟时钟信号D13以及具有小于中等延迟量的延迟量的第一延迟时钟信号D11和第二延迟时钟信号D12来生成与时钟信号CLK相比具有负占空比的第一操作时钟信号L11和第二操作时钟信号L12。例如,第一逻辑元件组122A可包括第一与门AG11和第二与门AG12。第一与门AG11可对第一延迟时钟信号D11和具有中等延迟量的第三延迟时钟信号D13执行逻辑与运算,并生成第一操作时钟信号L11。第二与门AG12可对第二延迟时钟信号D12和具有中等延迟量的第三延迟时钟信号D13执行逻辑与运算,并生成第二操作时钟信号L12。另外,可分别基于第一功率门控信号PG11和第二功率门控信号PG12来启用或禁用第一与门AG11和第二与门AG12。因此,可节省由第一与门AG11和第二与门AG12不必要地消耗的功率。

第二逻辑元件组122B可基于第一延迟时钟信号D11至第五延迟时钟信号D15当中的具有中等延迟量的第三延迟时钟信号D13以及具有大于中等延迟量的延迟量的第四延迟时钟信号D14和第五延迟时钟信号D15来生成与时钟信号CLK相比具有正占空比的第三操作时钟信号L13和第四操作时钟信号L14。例如,第二逻辑元件组122B可包括第一或门OG11和第二或门OG12。第一或门OG11可对第四延迟时钟信号D14和具有中等延迟量的第三延迟时钟信号D13执行逻辑或运算,并生成第三操作时钟信号L13。第二或门OG12可对第五延迟时钟信号D15和具有中等延迟量的第三延迟时钟信号D13执行逻辑或运算,并生成第四操作时钟信号L14。另外,可分别基于第三功率门控信号PG13和第四功率门控信号PG14来启用或禁用第一或门OG11和第二或门OG12。因此,可节省由第一或门OG11和第二或门OG12不必要地消耗的功率。

选择电路123可包括缓冲器BK1、解码器DEC1和复用器MUX1。

缓冲器BK1可基于控制信号CTRL和第一使能信号EN来生成信号CTRL1。例如,当第一使能信号EN被启用时,缓冲器BK1可生成与控制信号CTRL对应的信号CTRL1。另一方面,当第一使能信号EN被停用时,缓冲器BK1可维持与控制信号CTRL无关地设定的信号CTRL1。

解码器DEC1可将信号CTRL1解码,并生成选择代码信号DO1。例如,当必须减小第一校正目标信号CCL11的占空比时,解码器DEC1可生成用于允许第一操作时钟信号L11和第二操作时钟信号L12之一被选为第一周期信号CCL1的选择代码信号DO1。另一方面,当必须增大第一校正目标信号CCL11的占空比时,解码器DEC1可生成用于允许第三操作时钟信号L13和第四操作时钟信号L14之一被选为第一周期信号CCL1的选择代码信号DO1。另外,解码器DEC1可生成第一功率门控信号PG11至第四功率门控信号PG14。例如,当选择第一操作时钟信号L11时,解码器DEC1可停用第一功率门控信号PG11,并启用第二功率门控信号PG12至第四功率门控信号PG14。

复用器MUX1可基于选择代码信号DO1来输出第一操作时钟信号L11至第四操作时钟信号L14中的任一个作为第一周期信号CCL1。

图9是示出图7所示的第二占空比校正电路DCC2的框图。要注意的是,包括在图9的第二占空比校正电路DCC2中的元件、元件组和信号的数量是为了描述方便而作为示例描述,本公开不限于此。

参照图9,第二占空比校正电路DCC2可包括延迟电路125、逻辑电路126和选择电路127。

延迟电路125可将第二校正目标信号CCL22依次延迟单位延迟时间,并生成第一延迟时钟信号D21至第五延迟时钟信号D25。延迟电路125可包括彼此串联联接的第一延迟元件组DLY21至第五延迟元件组DLY25。例如,第一延迟元件组DLY21可将校正目标信号CCL22延迟单位延迟时间以生成延迟时钟信号D1。第二延迟元件组DLY22可将延迟时钟信号D1延迟单位延迟时间以生成延迟时钟信号D2。第三延迟元件组DLY23可将延迟时钟信号D2延迟单位延迟时间以生成延迟时钟信号D3。第四延迟元件组DLY24可将延迟时钟信号D3延迟单位延迟时间以生成延迟时钟信号D4。第五延迟元件组DLY25可将延迟时钟信号D4延迟单位延迟时间以生成延迟时钟信号D5。第一延迟元件组DLY21至第五延迟元件组DLY25中的每一个可将第二校正目标信号CCL22以及先前延迟时钟信号D21至D24中的任一个延迟单位延迟时间,并输出延迟时钟信号D21至D25。第一延迟元件组DLY21至第五延迟元件组DLY25中的每一个可包括彼此串联联接的偶数个反相器。尽管在本实施方式中作为示例描述了各个延迟元件组包括反相器,但本公开不限于此。在各种实施方式中,各个延迟元件组可被设计为包括电阻器和电容器。

逻辑电路126可对第一延迟时钟信号D21至第五延迟时钟信号D25中的每一个执行逻辑运算,并生成第一操作时钟信号L21至第四操作时钟信号L24。逻辑电路126可包括第一逻辑元件组126A和第二逻辑元件组126B。

第一逻辑元件组126A可基于第一延迟时钟信号D21至第五延迟时钟信号D25当中的具有中等延迟量的第三延迟时钟信号D23以及具有小于中等延迟量的延迟量的第一延迟时钟信号D21和第二延迟时钟信号D22来生成与时钟信号CLK相比具有负占空比的第一操作时钟信号L21和第二操作时钟信号L22。例如,第一逻辑元件组126A可包括第一与门AG21和第二与门AG22。第一与门AG21可对第一延迟时钟信号D21和具有中等延迟量的第三延迟时钟信号D23执行逻辑与运算,并生成第一操作时钟信号L21。第二与门AG22可对第二延迟时钟信号D22和具有中等延迟量的第三延迟时钟信号D23执行逻辑与运算,并生成第二操作时钟信号L22。另外,可分别基于第一功率门控信号PG21和第二功率门控信号PG22来启用或禁用第一与门AG21和第二与门AG22。因此,可节省由第一与门AG21和第二与门AG22不必要地消耗的功率。

第二逻辑元件组126B可基于第一延迟时钟信号D21至第五延迟时钟信号D25当中的具有中等延迟量的第三延迟时钟信号D23以及具有大于中等延迟量的延迟量的第四延迟时钟信号D24和第五延迟时钟信号D25来生成与时钟信号CLK相比具有正占空比的第三操作时钟信号L23和第四操作时钟信号L24。例如,第二逻辑元件组126B可包括第一或门OG21和第二或门OG22。第一或门OG21可对第四延迟时钟信号D24和具有中等延迟量的第三延迟时钟信号D23执行逻辑或运算,并生成第三操作时钟信号L23。第二或门OG22可对第五延迟时钟信号D25和具有中等延迟量的第三延迟时钟信号D23执行逻辑或运算,并生成第四操作时钟信号L24。另外,可分别基于第三功率门控信号PG23和第四功率门控信号PG24来启用或禁用第一或门OG21和第二或门OG22。因此,可节省由第一或门OG21和第二或门OG22不必要地消耗的功率。

选择电路127可包括缓冲器BK2、解码器DEC2和复用器MUX2。

缓冲器BK2可基于控制信号CTRL和第二使能信号ENB来生成信号CTRL2。例如,当第二使能信号ENB被启用时,缓冲器BK2可生成与控制信号CTRL对应的信号CTRL2。另一方面,当第二使能信号ENB被停用时,缓冲器BK2可维持与控制信号CTRL无关地设定的信号CTRL2。

解码器DEC2可将信号CTRL2解码,并生成选择代码信号DO2。例如,当必须减小第二校正目标信号CCL22的占空比时,解码器DEC2可生成用于允许第一操作时钟信号L21和第二操作时钟信号L22之一被选为第二周期信号CCL2的选择代码信号DO2。另一方面,当必须增大第二校正目标信号CCL22的占空比时,解码器DEC2可生成用于允许第三操作时钟信号L23和第四操作时钟信号L24之一被选为第二周期信号CCL2的选择代码信号DO2。另外,解码器DEC2可生成第一功率门控信号PG21至第四功率门控信号PG24。例如,当在第一操作时钟信号L21至第四操作时钟信号L24当中选择第一操作时钟信号L21时,解码器DEC2可停用第一功率门控信号PG21,并启用第二功率门控信号PG22至第四功率门控信号PG24。

复用器MUX2可基于选择代码信号DO2来输出第一操作时钟信号L21至第四操作时钟信号L24中的任一个作为第二周期信号CCL2。

图10是示出图1所示的控制器200的框图。

参照图10,控制器200可包括检测电路210和转换电路220。

检测电路210可检测第一周期信号CCL1和第二周期信号CCL2之间的占空比差。例如,在单个周期期间,检测电路210可通过检测第一周期信号CCL1处于逻辑高电平(或逻辑低电平)的时段与第二周期信号CCL2处于逻辑高电平(或逻辑低电平)的时段之间的差来检测占空比差。检测电路210可生成与检测结果对应的检测信号DET。

转换电路220可生成与检测信号DET对应的控制信号CTRL。例如,转换电路220可将检测信号DET转换为作为数字信号的控制信号CTRL。

以下,描述根据本实施方式的具有上述配置的图像感测装置的操作。

在本实施方式中,代表性地描述包括图3所示的校正器120的图像感测装置的操作。

在正常模式下,控制器200可基于从图像传感器100实时提供的第一周期信号CCL1和第二周期信号CCL2来动态地生成控制信号CTRL。例如,控制器200可检测第一周期信号CCL1和第二周期信号CCL2之间的占空比差,并实时生成与检测结果对应的控制信号CTRL。

图像传感器100可基于控制信号CTRL来校正深度信息。例如,图像传感器100可通过去除第一周期信号CCL1和第二周期信号CCL2之间的占空比差来校正深度信息。具体地,包括在图像传感器100中的校正器120可基于控制信号CTRL来去除第一周期信号CCL1和第二周期信号CCL2之间的占空比差。

图11是示出图3所示的校正器120的操作的示例的时序图。

参照图11,基于控制信号CTRL,校正器120可校正校正目标信号CCL11的占空比,并生成第一周期信号CCL1。换言之,校正器120可通过根据第二周期信号CCL2的占空比校正校正目标信号CCL11的占空比来生成具有正占空比的第一周期信号CCL1。

图12是示出图3所示的校正器120的操作的另一示例的时序图。

参照图12,基于控制信号CTRL,校正器120可校正校正目标信号CCL11的占空比,并生成第一周期信号CCL1。换言之,校正器120可通过根据第二周期信号CCL2的占空比校正校正目标信号CCL11的占空比来生成具有负占空比的第一周期信号CCL1。

根据本实施方式,可在正常模式下通过去除第一周期信号和第二周期信号之间的占空比差来校正深度信息。

图13是示出根据本发明的各种实施方式的图像感测装置的框图。

参照图13,图像感测装置可包括图像传感器300和控制器400。

图像传感器300可基于控制信号CTRL来校正深度信息,并根据深度信息生成图像数据IDT。深度信息可包括关于图像传感器300与对象(未示出)之间的距离的信息。

基于从图像传感器300提供的图像数据IDT,控制器400可分析深度信息的误差,并生成控制信号CTRL。在测试模式下,控制器400可对深度信息执行误差分析操作至少一次,并静态地生成控制信号CTRL。控制器400可被包括在测试装置(未示出)中。

图14是示出图13所示的图像传感器300的框图。

参照图14,图像传感器300可包括时钟发生器310、校正器320、光驱动器330、像素驱动器340、行解码器350、像素阵列360、信号转换器370和图像处理器380。

在测试模式下,时钟发生器310可生成时钟信号CLK。例如,时钟发生器310可包括锁相环或振荡器。

校正器320可基于控制信号CTRL和时钟信号CLK来生成各自具有占空比的第一周期信号CCL1和第二周期信号CCL2。第一周期信号CCL1和第二周期信号CCL2可被设计为具有相同的占空比。另选地,第一周期信号CCL1和第二周期信号CCL2可被设计为具有不同的占空比。在本实施方式中,作为示例描述了第一周期信号CCL1和第二周期信号CCL2被设计为具有相同的占空比。

光驱动器330可基于第一周期信号CCL1来向对象发射光信号LS。例如,光驱动器330可包括发光二极管或激光二极管。

像素驱动器340可基于第二周期信号CCL2来生成像素驱动信号PX_DRV。像素驱动信号PX_DRV可以是用于测量深度信息的信号之一。

行解码器350可生成用于逐行控制像素阵列360的行控制信号RCTRL。

像素阵列360可包括设置在多行和多列的交叉处的多个像素。多个像素可包括用于测量深度信息的至少一个深度测量像素。深度测量像素可基于像素驱动信号PX_DRV来感测从对象反射的光信号(未示出)。换言之,深度测量像素可基于像素驱动信号PX_DRV和反射的光信号来生成与深度信息对应的像素信号PX。

信号转换器370可将像素信号PX转换为数字信号DOUT。例如,信号转换器370可包括相关双采样电路和模数转换器。

图像处理器380可基于数字信号DOUT来生成图像数据IDT。图像数据IDT可包括深度信息。

图15是示出图14所示的校正器320的示例的框图。

参照图15,校正器320可包括第一负载L1、占空比校正电路DCC和第二负载L2。由于图15所示的第一负载L1、占空比校正电路DCC和第二负载L2分别与图3所示的那些相同,所以省略其详细描述。

图16是示出图15所示的占空比校正电路DCC的框图。要注意的是,包括在图16的占空比校正电路DCC中的元件、元件组和信号的数量是为了描述方便而作为示例描述,本公开不限于此。

参照图16,占空比校正电路DCC可包括延迟电路321、逻辑电路323和选择电路325。由于图16所示的延迟电路321、逻辑电路323和选择电路325分别与图4所示的延迟电路121、逻辑电路123和选择电路125相同,所以省略其详细描述。

图17是示出图14所示的校正器320的另一示例的框图。

参照图17,校正器320可包括第一负载L1、第二负载L2和占空比校正电路DCC。由于图17所示的第一负载L1、第二负载L2和占空比校正电路DCC分别与图5所示的那些相同,所以省略其详细描述。

图18是示出图17所示的占空比校正电路DCC的框图。要注意的是,包括在图18的占空比校正电路DCC中的元件、元件组和信号的数量是为了描述方便而作为示例描述,本公开不限于此。

参照图18,占空比校正电路DCC可包括延迟电路321、逻辑电路323和选择电路325。由于图18所示的延迟电路321、逻辑电路323和选择电路325分别与图6所示的延迟电路121、逻辑电路123和选择电路125相同,所以省略其详细描述。

图19是示出图14所示的校正器320的另一示例的框图。

参照图19,校正器320可包括第一负载L1、第一占空比校正电路DCC1、第二负载L2和第二占空比校正电路DCC2。由于图19所示的第一负载L1、第一占空比校正电路DCC1、第二负载L2和第二占空比校正电路DCC2分别与图7所示的那些相同,所以省略其详细描述。

图20是示出图19所示的第一占空比校正电路DCC1的框图。要注意的是,包括在图20的第一占空比校正电路DCC1中的元件、元件组和信号的数量是为了描述方便而作为示例描述,本公开不限于此。

参照图20,第一占空比校正电路DCC1可包括延迟电路321、逻辑电路322和选择电路323。由于图20所示的延迟电路321、逻辑电路322和选择电路323分别与图8所示的延迟电路121、逻辑电路122和选择电路123相同,所以省略其详细描述。

图21是示出图19所示的第二占空比校正电路DCC2的框图。要注意的是,包括在图21的第二占空比校正电路DCC2中的元件、元件组和信号的数量是为了描述方便而作为示例描述,本公开不限于此。

参照图21,第二占空比校正电路DCC2可包括延迟电路325、逻辑电路326和选择电路327。由于图21所示的延迟电路325、逻辑电路326和选择电路327分别与图9所示的延迟电路125、逻辑电路126和选择电路127相同,所以省略其详细描述。

图22是示出图13所示的控制器400的框图。

参照图22,控制器400可包括比较电路410、确定电路420和存储电路430。

比较电路410可将图像数据IDT与参考数据RDT进行比较,并生成比较信号CMP。例如,比较电路410可将包括在图像数据IDT中的各自与数字信号DOUT对应的数字值中的一些或全部与包括在参考数据RDT中的数字值进行比较。

基于比较信号CMP,确定电路420可确定深度信息的误差,并生成控制信号CTRL。例如,当确定结果指示“失败”时,确定电路420可改变控制信号CTRL,当确定结果指示“通过”时,确定电路420可维持(即,固定)控制信号CTRL。

存储电路430可存储参考数据RDT。尽管在本公开的实施方式中描述了存储电路430可被配置在控制器400中,但本发明构思不限于此,存储电路430可被配置在控制器400外部。

以下,描述根据本实施方式的具有上述配置的图像感测装置的操作。

在本实施方式中,代表性地描述包括图15所示的校正器320的图像感测装置的操作。

在测试模式下,控制器400可基于从图像传感器300提供的图像数据IDT来静态地生成控制信号CTRL。例如,控制器400可将图像数据IDT与参考数据RDT进行比较并生成与比较结果对应的控制信号CTRL至少一次。

图像传感器300可基于控制信号CTRL来校正深度信息。例如,图像传感器300可通过去除第一周期信号CCL1和第二周期信号CCL2之间的占空比差来校正深度信息。具体地,包括在图像传感器300中的校正器320可基于控制信号CTRL来去除第一周期信号CCL1和第二周期信号CCL2之间的占空比差。

图23是示出图15所示的校正器320的操作的示例的时序图。

参照图23,基于控制信号CTRL,校正器320可校正校正目标信号CCL11的占空比,并生成第一周期信号CCL1。换言之,校正器320可通过根据第二周期信号CCL2的占空比校正校正目标信号CCL11的占空比来生成具有正占空比的第一周期信号CCL1。

图24是示出图15所示的校正器320的操作的另一示例的时序图。

参照图24,基于控制信号CTRL,校正器320可校正校正目标信号CCL11的占空比,并生成第一周期信号CCL1。换言之,校正器320可通过根据第二周期信号CCL2的占空比校正校正目标信号CCL11的占空比来生成具有负占空比的第一周期信号CCL1。

根据本实施方式,可在测试模式下通过容易地去除第一周期信号和第二周期信号之间的占空比差来校正深度信息。

图25是示出根据本发明的各种实施方式的图像感测装置的框图。

参照图25,图像感测装置可包括图像传感器500、第一控制器600和第二控制器700。

图像传感器500可基于第一控制信号CTRL1和第二控制信号CTRL2来校正深度信息,并根据深度信息生成图像数据IDT。深度信息可包括关于图像传感器500与对象(未示出)之间的距离的信息。

图像传感器500可在测试模式下向第一控制器600提供图像数据IDT并且在正常模式下向第二控制器700提供生成图像数据IDT所需的第一周期信号CCL1和第二周期信号CCL2。第一周期信号CCL1可用于生成发射到对象(未示出)的光信号LS。第二周期信号CCL2可用于测量深度信息。

基于从图像传感器500提供的图像数据IDT,第一控制器600可分析深度信息的误差,并生成第一控制信号CTRL1。在测试模式下,第一控制器600可对深度信息执行误差分析操作至少一次,并静态地生成第一控制信号CTRL1。第一控制器600可被包括在测试装置(未示出)中。

基于从图像传感器500提供的第一周期信号CCL1和第二周期信号CCL2,第二控制器700可分析深度信息的误差,并生成第二控制信号CTRL2。在正常模式下,第二控制器700可实时地对深度信息执行误差分析操作,并动态地生成第二控制信号CTRL2。第二控制器700和图像传感器500可被集成到同一芯片(即,芯片上)或不同的芯片(即,芯片外)中。

图26是示出图25所示的图像传感器500的框图。

参照图26,图像传感器500可包括时钟发生器510、校正器520、光驱动器530、像素驱动器540、行解码器550、像素阵列560、信号转换器570和图像处理器580。

在测试模式和正常模式下,时钟发生器510可生成时钟信号CLK。例如,时钟发生器510可包括锁相环或振荡器。

校正器520可基于第一控制信号CTRL1和第二控制信号CTRL2、时钟信号CLK和测试模式信号TM来生成各自具有占空比的第一周期信号CCL1和第二周期信号CCL2。第一周期信号CCL1和第二周期信号CCL2可被设计为具有相同的占空比。另选地,第一周期信号CCL1和第二周期信号CCL2可被设计为具有不同的占空比。在本实施方式中,作为示例描述了第一周期信号CCL1和第二周期信号CCL2被设计为具有相同的占空比。

光驱动器530可基于第一周期信号CCL1向对象发射光信号LS。例如,光驱动器530可包括发光二极管或激光二极管。

像素驱动器540可基于第二周期信号CCL2来生成像素驱动信号PX_DRV。像素驱动信号PX_DRV可以是用于测量深度信息的信号之一。

行解码器550可生成用于逐行控制像素阵列560的行控制信号RCTRL。

像素阵列560可包括设置在多行和多列的交叉处的多个像素。多个像素可包括用于测量深度信息的至少一个深度测量像素。深度测量像素可基于像素驱动信号PX_DRV来感测从对象反射的光信号(未示出)。换言之,深度测量像素可基于像素驱动信号PX_DRV和反射的光信号来生成与深度信息对应的像素信号PX。

信号转换器570可将像素信号PX转换为数字信号DOUT。例如,信号转换器570可包括相关双采样电路和模数转换器。

图像处理器580可基于数字信号DOUT来生成图像数据IDT。图像数据IDT可包括深度信息。

图27是示出图26所示的校正器520的示例的框图。

参照图27,校正器520可包括第一负载L1、占空比校正电路DCC和第二负载L2。

第一负载L1可生成与时钟信号CLK对应的校正目标信号CCL11。第一负载L1可包括生成校正目标信号CCL11的第一路径中出现的第一线路负载。第一线路负载可包括第一路径中直接或间接形成的所有负载。另外,第一负载L1可被设计为还包括用于调谐时钟信号CLK的第一电路。当经过第一负载L1时,校正目标信号CCL11的占空比可与时钟信号CLK的占空比不同地改变。换言之,可无意地调节校正目标信号CCL11的占空比。

占空比校正电路DCC可基于第一控制信号CTRL1和第二控制信号CTRL2、测试模式信号TM和校正目标信号CCL11来生成第一周期信号CCL1。例如,占空比校正电路DCC可在测试模式下通过将校正目标信号CCL11的占空比校正为与第二周期信号CCL2的占空比相一致来静态地生成第一周期信号CCL1,并且在正常模式下通过将校正目标信号CCL11的占空比实时校正为与第二周期信号CCL2的占空比相一致来动态地生成第一周期信号CCL1。

第二负载L2可生成与时钟信号CLK对应的第二周期信号CCL2。第二负载L2可包括生成第二周期信号CCL2的第二路径中出现的第二线路负载。第二线路负载可包括第二路径中直接或间接形成的所有负载。另外,第二负载L2可被设计为还包括用于调谐时钟信号CLK的第二电路。当经过第二负载L2时,第二周期信号CCL2的占空比可与时钟信号CLK的占空比不同地改变。换言之,可无意地调节第二周期信号CCL2的占空比。在这种情况下,第二周期信号CCL2的占空比可不同于校正目标信号CCL11的占空比。

图28是示出图27所示的占空比校正电路DCC的框图。要注意的是,包括在图28的占空比校正电路DCC中的元件、元件组和信号的数量是为了描述方便而作为示例描述,本公开不限于此。

参照图28,占空比校正电路DCC可包括延迟电路521、逻辑电路523和选择电路525。由于图28所示的延迟电路521和逻辑电路523分别与图4所示的延迟电路121和逻辑电路123相同,所以省略其详细描述。

选择电路525可包括第一复用器MUX1、解码器DEC和第二复用器MUX2。

第一复用器MUX1可基于测试模式信号TM来输出第一控制信号CTRL1和第二控制信号CTRL2之一作为控制信号CTRL。例如,第一复用器MUX1可在测试模式下输出第一控制信号CTRL1作为控制信号CTRL,并且在正常模式下输出第二控制信号CTRL2作为控制信号CTRL。

解码器DEC可将控制信号CTRL解码,并生成选择代码信号DO。例如,当必须减小校正目标信号CCL11的占空比时,解码器DEC可生成用于允许第一操作时钟信号L1和第二操作时钟信号L2之一被选为第一周期信号CCL1的选择代码信号DO。另一方面,当必须增大校正目标信号CCL11的占空比时,解码器DEC可生成用于允许第三操作时钟信号L3和第四操作时钟信号L4之一被选为第一周期信号CCL1的选择代码信号DO。另外,解码器DEC可生成第一功率门控信号PG1至第四功率门控信号PG4。例如,当选择第一操作时钟信号L1时,解码器DEC可停用第一功率门控信号PG1,并启用第二功率门控信号PG2至第四功率门控信号PG4。

第二复用器MUX2可基于选择代码信号DO来输出第一操作时钟信号L1至第四操作时钟信号L4中的任一个作为第一周期信号CCL1。

图29是示出图26所示的校正器520的另一示例的框图。

参照图29,校正器520可包括第一负载L1、第二负载L2和占空比校正电路DCC。

第一负载L1可生成与时钟信号CLK对应的第一周期信号CCL1。第一负载L1可包括生成第一周期信号CCL1的第一路径中出现的第一线路负载。第一线路负载可包括第一路径中直接或间接形成的所有负载。另外,第一负载L1可被设计为还包括用于调谐时钟信号CLK的第一电路。当经过第一负载L1时,第一周期信号CCL1的占空比可与时钟信号CLK的占空比不同地改变。换言之,可无意地调节第一周期信号CCL1的占空比。

第二负载L2可生成与时钟信号CLK对应的校正目标信号CCL22。第二负载L2可包括生成校正目标信号CCL22的第二路径中出现的第二线路负载。第二线路负载可包括第二路径中直接或间接形成的所有负载。另外,第二负载L2可被设计为还包括用于调谐时钟信号CLK的第二电路。当经过第二负载L2时,校正目标信号CCL22的占空比可与时钟信号CLK的占空比不同地改变。换言之,可无意地调节校正目标信号CCL22的占空比。在这种情况下,校正目标信号CCL22的占空比可不同于第一周期信号CCL1的占空比。

占空比校正电路DCC可基于第一控制信号CTRL1和第二控制信号CTRL2、测试模式信号TM和校正目标信号CCL22来生成第二周期信号CCL2。例如,占空比校正电路DCC可在测试模式下通过将校正目标信号CCL22的占空比校正为与第一周期信号CCL1的占空比相一致来静态地生成第二周期信号CCL2,并且在正常模式下通过将校正目标信号CCL22的占空比实时校正为与第一周期信号CCL1的占空比相一致来动态地生成第二周期信号CCL2。

图30是示出图29所示的占空比校正电路DCC的框图。要注意的是,包括在图30的占空比校正电路DCC中的元件、元件组和信号的数量是为了描述方便而作为示例描述,本公开不限于此。

参照图30,占空比校正电路DCC可包括延迟电路521、逻辑电路523和选择电路525。由于图30所示的延迟电路521和逻辑电路523分别与图6所示的延迟电路121和逻辑电路123相同,所以省略其详细描述。

选择电路525可包括第一复用器MUX1、解码器DEC和第二复用器MUX2。

第一复用器MUX1可基于测试模式信号TM来输出第一控制信号CTRL1和第二控制信号CTRL2之一作为控制信号CTRL。例如,第一复用器MUX1可在测试模式下输出第一控制信号CTRL1作为控制信号CTRL,并且在正常模式下输出第二控制信号CTRL2作为控制信号CTRL。

解码器DEC可将控制信号CTRL解码并生成选择代码信号DO。例如,当必须减小校正目标信号CCL22的占空比时,解码器DEC可生成用于允许第一操作时钟信号L1和第二操作时钟信号L2之一被选为第一周期信号CCL1的选择代码信号DO。另一方面,当必须增大校正目标信号CCL22的占空比时,解码器DEC可生成用于允许第三操作时钟信号L3和第四操作时钟信号L4之一被选为第一周期信号CCL1的选择代码信号DO。另外,解码器DEC可生成第一功率门控信号PG1至第四功率门控信号PG4。例如,当在第一操作时钟信号L1至第四操作时钟信号L4当中选择第一操作时钟信号L1时,解码器DEC可停用第一功率门控信号PG1,并启用第二功率门控信号PG2至第四功率门控信号PG4。

第二复用器MUX2可基于选择代码信号DO来输出第一操作时钟信号L1至第四操作时钟信号L4中的任一个作为第一周期信号CCL1。

图31是示出图26所示的校正器520的另一示例的框图。

参照图31,校正器520可包括第一负载L1、第一占空比校正电路DCC1、第二负载L2和第二占空比校正电路DCC2。

第一负载L1可生成与时钟信号CLK对应的第一校正目标信号CCL11。第一负载L1可包括生成第一校正目标信号CCL11的第一路径中出现的第一线路负载。第一线路负载可包括第一路径中直接或间接形成的所有负载。另外,第一负载L1可被设计为还包括用于调谐时钟信号CLK的第一电路。当经过第一负载L1时,第一校正目标信号CCL11的占空比可与时钟信号CLK的占空比不同地改变。换言之,可无意地调节第一校正目标信号CCL11的占空比。

第一占空比校正电路DCC1可基于第一控制信号CTRL1和第二控制信号CTRL2、测试模式信号TM和第一校正目标信号CCL11来生成第一周期信号CCL1。例如,第一占空比校正电路DCC1可在测试模式下通过将第一校正目标信号CCL11的占空比校正为与第二周期信号CCL2的占空比相一致来静态地生成第一周期信号CCL1,并且在正常模式下通过将第一校正目标信号CCL11的占空比实时校正为与第二周期信号CCL2的占空比相一致来动态地生成第一周期信号CCL1。可基于第一使能信号EN来启用第一占空比校正电路DCC1。第一使能信号EN可在图像传感器500中生成或从第一控制器600和第二控制器700提供。

第二负载L2可生成与时钟信号CLK对应的第二校正目标信号CCL22。第二负载L2可包括生成第二校正目标信号CCL22的第二路径中出现的第二线路负载。第二线路负载可包括第二路径中直接或间接形成的所有负载。另外,第二负载L2可被设计为还包括用于调谐时钟信号CLK的第二电路。当经过第二负载L2时,第二校正目标信号CCL22的占空比可与时钟信号CLK的占空比不同地改变。换言之,可无意地调节第二校正目标信号CCL22的占空比。在这种情况下,第二校正目标信号CCL22的占空比可不同于第一校正目标信号CCL11的占空比。

第二占空比校正电路DCC2可基于第一控制信号CTRL1和第二控制信号CTRL2、测试模式信号TM和第二校正目标信号CCL22来生成第二周期信号CCL2。例如,第二占空比校正电路DCC2可在测试模式下通过将第二校正目标信号CCL22的占空比校正为与第一周期信号CCL1的占空比相一致来静态地生成第二周期信号CCL2,并且在正常模式下通过将第二校正目标信号CCL22的占空比实时校正为与第一周期信号CCL1的占空比相一致来动态地生成第二周期信号CCL2。可基于第二使能信号ENB来启用第二占空比校正电路DCC2。第二使能信号ENB可以是通过将第一使能信号EN反相而获得的信号。

图32是示出图31所示的第一占空比校正电路DCC1的框图。要注意的是,包括在图32的第一占空比校正电路DCC1中的元件、元件组和信号的数量是为了描述方便而作为示例描述,本公开不限于此。

参照图32,第一占空比校正电路DCC1可包括延迟电路521、逻辑电路522和选择电路523。由于图32所示的延迟电路521和逻辑电路522分别与图8所示的延迟电路121和逻辑电路122相同,所以省略其详细描述。

选择电路523可包括第一复用器MUX11、缓冲器BK11、解码器DEC11和第二复用器MUX12。

第一复用器MUX11可基于测试模式信号TM来输出第一控制信号CTRL1和第二控制信号CTRL2之一作为控制信号CTRL11。例如,第一复用器MUX11可在测试模式下输出第一控制信号CTRL1作为控制信号CTRL11,并且在正常模式下输出第二控制信号CTRL2作为控制信号CTRL11。

缓冲器BK11可基于控制信号CTRL11和第一使能信号EN来生成信号CTRL111。例如,当第一使能信号EN被启用时,缓冲器BK11可生成与控制信号CTRL11对应的信号CTRL111。另一方面,当第一使能信号EN被停用时,缓冲器BK11可维持与控制信号CTRL11无关地设定的信号CTRL111。

解码器DEC11可将信号CTRL111解码,并生成选择代码信号DO1。例如,当必须减小第一校正目标信号CCL11的占空比时,解码器DEC11可生成用于允许第一操作时钟信号L11和第二操作时钟信号L12之一被选为第一周期信号CCL1的选择代码信号DO1。另一方面,当必须增大第一校正目标信号CCL11的占空比时,解码器DEC11可生成用于允许第三操作时钟信号L13和第四操作时钟信号L14之一被选为第一周期信号CCL1的选择代码信号DO1。另外,解码器DEC11可生成第一功率门控信号PG11至第四功率门控信号PG14。例如,当在第一操作时钟信号L11至第四操作时钟信号L14当中选择第一操作时钟信号L11时,解码器DEC11可停用第一功率门控信号PG11,并启用第二功率门控信号PG12至第四功率门控信号PG14。

第二复用器MUX12可基于选择代码信号DO1来输出第一操作时钟信号L11至第四操作时钟信号L14之一作为第一周期信号CCL1。

图33是示出图31所示的第二占空比校正电路DCC2的框图。要注意的是,包括在图33的第二占空比校正电路DCC2中的元件、元件组和信号的数量是为了描述方便而作为示例描述,本公开不限于此。

参照图33,第二占空比校正电路DCC2可包括延迟电路525、逻辑电路526和选择电路527。由于图33所示的延迟电路525和逻辑电路526分别与图9所示的延迟电路125和逻辑电路126相同,所以省略其详细描述。

选择电路527可包括第一复用器MUX21、缓冲器BK21、解码器DEC21和第二复用器MUX22。

第一复用器MUX21可基于测试模式信号TM来输出第一控制信号CTRL1和第二控制信号CTRL2之一作为控制信号CTRL22。例如,第一复用器MUX21可在测试模式下输出第一控制信号CTRL1作为控制信号CTRL22,并且在正常模式下输出第二控制信号CTRL2作为控制信号CTRL22。

缓冲器BK21可基于控制信号CTRL22和第二使能信号ENB来生成信号CTRL222。例如,当第二使能信号ENB被启用时,缓冲器BK21可生成与控制信号CTRL22对应的信号CTRL222。另一方面,当第二使能信号ENB被停用时,缓冲器BK21可维持与控制信号CTRL22无关地设定的信号CTRL222。

解码器DEC21可将信号CTRL222解码,并生成选择代码信号DO2。例如,当必须减小第二校正目标信号CCL22的占空比时,解码器DEC21可生成用于允许第一操作时钟信号L21和第二操作时钟信号L22之一被选为第二周期信号CCL2的选择代码信号DO2。另一方面,当必须增大第二校正目标信号CCL22的占空比时,解码器DEC21可生成用于允许第三操作时钟信号L23和第四操作时钟信号L24之一被选为第二周期信号CCL2的选择代码信号DO2。另外,解码器DEC21可生成第一功率门控信号PG21至第四功率门控信号PG24。例如,当在第一操作时钟信号L21至第四操作时钟信号L24当中选择第一操作时钟信号L21时,解码器DEC21可停用第一功率门控信号PG21,并启用第二功率门控信号PG22至第四功率门控信号PG24。

第二复用器MUX22可基于选择代码信号DO2来输出第一操作时钟信号L21至第四操作时钟信号L24中的任一个作为第二周期信号CCL2。

图34是示出图25所示的第一控制器600的框图。

参照图34,第一控制器600可包括比较电路610、确定电路620和存储电路630。

比较电路610可将图像数据IDT与参考数据RDT进行比较,并生成比较信号CMP。例如,比较电路610可将包括在图像数据IDT中的各自与数字信号DOUT对应的数字值中的一些或全部与包括在参考数据RDT中的数字值进行比较。

基于比较信号CMP,确定电路620可确定深度信息的误差,并生成第一控制信号CTRL1。例如,当确定结果指示“失败”时,确定电路620可改变第一控制信号CTRL1,并且当确定结果指示“通过”时,确定电路620可维持(即,固定)第一控制信号CTRL1。

存储电路630可存储参考数据RDT。尽管在本公开的实施方式中描述了存储电路630可被配置在第一控制器600中,但本发明构思不限于此,存储电路630可被配置在第一控制器600外部。

图35是示出图25所示的第二控制器700的框图。

参照图35,第二控制器700可包括检测电路710和转换电路720。

检测电路710可检测第一周期信号CCL1和第二周期信号CCL2之间的占空比差。例如,在单个周期期间,检测电路710可通过检测第一周期信号CCL1处于逻辑高电平(或逻辑低电平)的时段与第二周期信号CCL2处于逻辑高电平(或逻辑低电平)的时段之间的差来检测占空比差。检测电路710可生成与检测结果对应的检测信号DET。

转换电路720可生成与检测信号DET对应的第二控制信号CTRL2。例如,转换电路720可将检测信号DET转换为作为数字信号的第二控制信号CTRL2。

以下,描述根据本实施方式的具有上述配置的图像感测装置的操作。

在本实施方式中,代表性地描述包括图27所示的校正器520的图像感测装置的操作。

在测试模式下,第一控制器600可基于从图像传感器500提供的图像数据IDT静态地生成第一控制信号CTRL1。例如,第一控制器600可将图像数据IDT与参考数据RDT进行比较并生成与比较结果对应的第一控制信号CTRL1至少一次。

在测试模式下,图像传感器500可基于第一控制信号CTRL1来校正深度信息。例如,图像传感器500可通过去除第一周期信号CCL1和第二周期信号CCL2之间的占空比差来校正深度信息。具体地,在测试模式下,包括在图像传感器500中的校正器520可基于第一控制信号CTRL1来去除第一周期信号CCL1和第二周期信号CCL2之间的占空比差。

图36是示出图27所示的校正器520的操作的示例的时序图。

参照图36,基于第一控制信号CTRL1,校正器520可校正校正目标信号CCL11的占空比,并生成第一周期信号CCL1。换言之,校正器520可通过根据第二周期信号CCL2的占空比校正校正目标信号CCL11的占空比来生成具有正占空比的第一周期信号CCL1。

图37是示出图27所示的校正器520的操作的另一示例的时序图。

参照图37,基于第一控制信号CTRL1,校正器520可校正校正目标信号CCL11的占空比,并生成第一周期信号CCL1。换言之,校正器520可通过根据第二周期信号CCL2的占空比校正校正目标信号CCL11的占空比来生成具有负占空比的第一周期信号CCL1。

在正常模式下,第二控制器700可基于从图像传感器500实时提供的第一周期信号CCL1和第二周期信号CCL2来动态地生成第二控制信号CTRL2。例如,第二控制器700可检测第一周期信号CCL1和第二周期信号CCL2之间的占空比差并实时生成与检测结果对应的第二控制信号CTRL2。

在正常模式下,图像传感器500可基于第二控制信号CTRL2来校正深度信息。例如,图像传感器500可通过去除第一周期信号CCL1和第二周期信号CCL2之间的占空比差来校正深度信息。具体地,在正常模式下,包括在图像传感器500中的校正器520可基于第二控制信号CTRL2来去除第一周期信号CCL1和第二周期信号CCL2之间的占空比差。例如,校正器520可通过根据第二周期信号CCL2的占空比校正校正目标信号CCL11的占空比来生成具有正占空比的第一周期信号CCL1(参照图36)。另选地,校正器520可通过根据第二周期信号CCL2的占空比校正校正目标信号CCL11的占空比来生成具有负占空比的第一周期信号CCL1(参照图37)。

根据本实施方式,可在测试模式和正常模式下通过容易地去除第一周期信号和第二周期信号之间的占空比差来校正深度信息。

根据本公开的实施方式,由于可容易地校正深度信息,所以可改进图像感测装置的操作可靠性。

尽管针对特定实施方式示出和描述了本发明,但所公开的实施方式并非旨在限制。此外,要注意的是,本领域技术人员根据本公开将认识到,在不脱离本公开的精神和/或范围的情况下,本发明可通过置换、改变和修改来以各种方式实现。本发明旨在涵盖落在以下权利要求的范围内的所有这些置换、改变和修改。

相关申请的交叉引用

本申请要求2019年12月27日提交的韩国专利申请No.10-2019-0176828的优先权,其公开通过引用整体并入本文。

- 图像感测装置的镜头安装组件和图像感测装置及其制造方法

- 图像感测装置及图像感测装置的控制方法