一种对称互感耦合小型化多频带通LTCC滤波器芯片

文献发布时间:2023-06-19 11:45:49

技术领域

本发明涉及无源射频滤波器技术领域,特别是涉及一种对称互感耦合小型化多频带通LTCC滤波器芯片。

背景技术

随着5G技术的不断发展,5G移动通信系统需要满足5G通信的高速率、大容量以及高精确度的需求。滤波器作为5G移动通信系统中的核心器件,需要发挥精确处理信号的作用。

然而,现有技术中的单频带通滤波器仅能接收和处理单一频段的信号,无法满足5G通信的要求。因此,亟需一种多频带通滤波器,以能够对多频段的信号进行处理。

发明内容

本发明实施例的目的在于提供一种对称互感耦合小型化多频带通LTCC滤波器芯片,以能够对多频段的信号进行处理。具体技术方案如下:

第一方面,本发明实施例提供了一种对称互感耦合小型化多频带通LTCC滤波器芯片,所述滤波器芯片包括:信号输入端口、信号输出端口、多个滤波电路,所述信号输入端口、信号输出端口和多个滤波电路通过低温共烧陶瓷LTCC技术被集成于多层介质基板、且所述多层介质基板以堆叠方式集成于一体;

每一滤波电路与一个频段对应,用于对所对应频段的信号进行带通滤波;

各滤波电路并联,各滤波电路的输入端分别与所述信号输入端口连接,各滤波电路的输出端分别与所述信号输出端口连接。

本发明的一个实施例中,上述滤波电路包括:第一电容、第二电容、第三电容、第一谐振器和第二谐振器,其中,所述第一电容和第二电容的电容值相同,所述第一谐振器和第二谐振器所产生的谐振频率相同;

所述第一电容的一端与所述信号输入端口连接,另一端与所述第一谐振器的输入端连接;

所述第一谐振器的输出端与所述第二谐振器的输入端、所述第三电容的一端连接;

所述第二谐振器的输出端与所述第二电容的一端连接;

所述第二电容的另一端与所述信号输出端口连接;

所述第三电容的另一端接地。

本发明的一个实施例中,各滤波电路包括的第一电容的电容值不相同、第二电容的电容值不相同、第三电容的电容值不相同、第一谐振器所产生的谐振频率不同、且第二谐振器所产生的谐振频率不同。

本发明的一个实施例中,上述第一谐振器和第二谐振器均为:包括第四电容和第一电感的谐振器;

所述第四电容与第一电感并联形成并联电路,所述并联电路的一端作为所述谐振器的输入端,所述并联电路的另一端作为所述谐振器的输出端;

所述第一谐振器和所述第二谐振器通过第一电感间的互感耦合方式相连接。

本发明的一个实施例中,各滤波电路包括的谐振器中第四电容的电容值不相同、且第一电感的电感值不相同。

本发明的一个实施例中,上述滤波器为双频带通滤波器,

在所述滤波电路对应频段范围为[4.60GHz,5.26GHz]内,所述第一电容的电容值在[0.50pF,0.55pF]内,所述第三电容的电容值在[1.20pF,1.25pF]内,所述第四电容的电容值在[1.50pF,1.55pF]内,所述第一电感的电感值在[0.55nH,0.60nH]内,两个谐振器中第一电感302间的耦合电感的互感值在[0.20nH,0.25nH]内;

和/或

在所述滤波电路对应频段范围为[3.15GHz,3.75GHz]内,所述第一电容(31)的电容值在[1.40pF,1.45pF]内,所述第三电容的电容值在[15.65pF,15.70pF]内,所述第四电容的电容值在[1.55pF,1.60pF]内,所述第一电感的电感值在[1.00nH,1.05nH]内,两个谐振器中第一电感302间的耦合电感在[0.050nH,0.055nH]内。

本发明的一个实施例中,上述滤波器为双频带通滤波器,

在所述滤波电路对应频段范围为[4.60GHz,5.26GHz]内,所述第一电容、第二电容、第三电容、第四电容为平面电容器,所述第一电感为平面螺旋电感器;

和/或

在所述滤波电路对应频段范围为[3.15GHz,3.75GHz]内,所述第一电容、第二电容、第四电容为平面电容器、所述第三电容为垂直交趾电容器,所述第一电感为垂直螺旋电感器。

本发明的一个实施例中,每一层介质基板的介质材料为生瓷带材料,每一层介质基板附着的金属导体材料为金属银。

本发明的一个实施例中,所述介质基板的厚度为0.094mm、所述金属导体材料的厚度为0.01mm。

本发明的一个实施例中,所述生瓷带材料为:介电常数5.9、损耗角正切值为0.002的FerroA6M。

由以上可见,由于本发明实施例提供的滤波器芯片中各滤波电路与一个频段对应,且用于对所对应频段的信号进行带通滤波,相较于现有技术,能够对多频段的信号进行处理。

并且,由于是将各滤波电路并联,各滤波电路的输入端分别与信号输入端口连接,各滤波电路的输出端分别与信号输出端口连接,所形成的滤波器的插入损耗较小、信号匹配度较高。

另外,采用LTCC技术将信号输入端口、信号输出端口和多个滤波电路集成于多层介质基板,由于LTCC技术能够提高电路的集成度、减小电路体积,因此,本发明实施例提供的滤波器芯片的集成度较高、所占空间较小。

当然,实施本发明的任一产品或方法并不一定需要同时达到以上所述的所有优点。

附图说明

为了更清楚地说明本发明实施例或现有技术中的技术方案,下面将对实施例或现有技术描述中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本发明的一些实施例,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其他的附图。

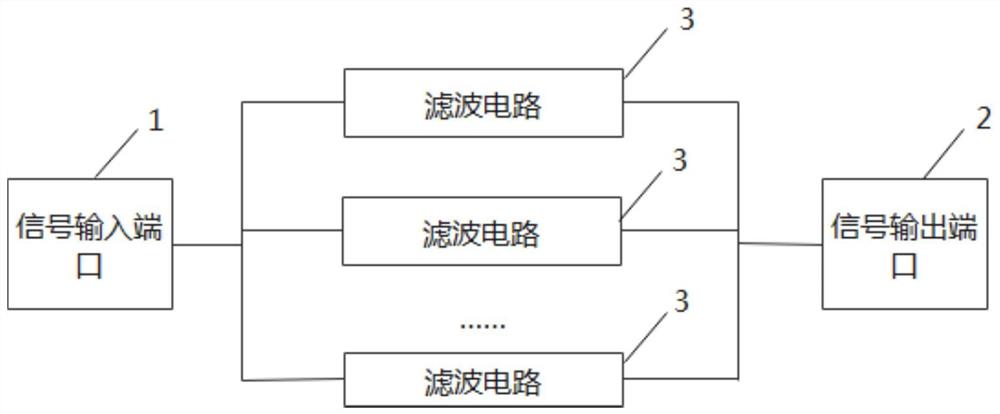

图1为本发明实施例提供的一种对称互感耦合小型化多频带通LTCC滤波器芯片的结构示意图;

图2为本发明实施例提供的第一种滤波电路的结构示意图;

图3为本发明实施例提供的第二种滤波电路的结构示意图;

图4a为本发明实施例提供的一种四频带带通滤波器芯片的结构示意图;

图4b为本发明实施例提供的一种三频带通滤波器芯片的结构示意图;

图4c为本发明实施例提供的一种双频带通滤波器芯片的结构示意图;

图5a为本发明实施例提供的第一层电路结构的示意图;

图5b为本发明实施例提供的第二层电路结构的示意图;

图5c为本发明实施例提供的第三层电路结构的示意图;

图5d为本发明实施例提供的第四层电路结构的示意图;

图5e为本发明实施例提供的第五层电路结构的示意图;

图5f为本发明实施例提供的第六层电路结构的示意图;

图5g为本发明实施例提供的第七层电路结构的示意图;

图5h为本发明实施例提供的第八层电路结构的示意图;

图5i为本发明实施例提供的第九层电路结构的示意图;

图5j为本发明实施例提供的第十层电路结构的示意图;

图5k为本发明实施例提供的第十一层电路结构的示意图;

图5l为本发明实施例提供的第十二层电路结构的示意图;

图5m为本发明实施例提供的第十三层电路结构的示意图;

图5n为本发明实施例提供的一种双频带通滤波器芯片的三维立体版图;

图5o为本发明实施例提供的一种双频带通滤波器芯片的三维立体版图的侧视图;

图6a为本发明实施例提供的第一种仿真结果的示意图;

图6b为本发明实施例提供的第二种仿真结果的示意图;

图6c为本发明实施例提供的第三种仿真结果的示意图;

图6d为本发明实施例提供的第四种仿真结果的示意图。

具体实施方式

下面将结合本发明实施例中的附图,对本发明实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例仅仅是本发明一部分实施例,而不是全部的实施例。基于本发明中的实施例,本领域普通技术人员基于本申请所获得的所有其他实施例,都属于本发明保护的范围。

参见图1,图1为本发明实施例提供的一种对称互感耦合小型化多频带通LTCC滤波器芯片的结构示意图,上述滤波器芯片包括:信号输入端口1、信号输出端口2、多个滤波电路3。

上述信号输入端口1、信号输出端口2和多个滤波电路3通过LTCC(LowTemperature Co-fired Ceramic,低温共烧陶瓷)技术被集成于多层介质基板、且各层介质基板以堆叠方式集成于一体。

上述信号输入端口1、信号输出端口2用于与射频前端器件连接。

具体的,各层介质基板上金属导体可以通过LTCC技术附着于各层介质基板,各导体间采用信号通孔的形式进行电气连接。

上述每一层介质基板的介质材料可以为生瓷带材料,如,上述生瓷带材料可以为介电常数5.9、损耗角正切值为0.002的FerroA6M;每一层介质基板附着的金属导体材料为金属银。上述介质基板的厚度可以为0.094mm,金属导体材料的厚度可以为0.01mm。

LTCC技术能在更小的空间上集成电容电感滤波器、双工器、功能模块、收发开关功能模块、耦合器、功率分配器等射频通信器件,元件加工精度可精确到毫微米量级,显著提高电子电路的集成度。

LTCC技术采用包括但不局限于流延,下料,通孔填充,导电介质的印刷,要层和热压,切片,共烧先进等加工技术,可以加工传输线、耦合线、螺旋电感、交趾或平面电容等结构,加工精度精确到毫米量级,通过将无源器件埋置在具有优良的高频,高速传输以及宽通带特性的陶瓷材料中,不仅提高了电路性能,还缩小了电路的体积。

每一滤波电路3与一个频段对应,用于对所对应频段的信号进行带通滤波。具体的,上述多频带通滤波器可以为双频带通滤波器、三频带通滤波器、四频带通滤波器等。

各滤波电路3并联,各滤波电路3的输入端分别与信号输入端口1连接,各滤波电路的输出端分别与信号输出端口2连接。

由以上可见,由于本发明实施例提供的滤波器芯片中各滤波电路与一个频段对应,且用于对所对应频段的信号进行带通滤波,相较于现有技术,能够对多频段的信号进行处理。

并且,由于是将各滤波电路并联,各滤波电路的输入端分别与信号输入端口连接,各滤波电路的输出端分别与信号输出端口连接,所形成的滤波器的插入损耗较小、信号匹配度较高。

另外,采用LTCC技术将信号输入端口、信号输出端口和多个滤波电路集成于多层介质基板,由于LTCC技术能够提高电路的集成度、减小电路体积,因此,本发明实施例提供的滤波器芯片的集成度较高、所占空间较小。

参见图2,图2为本发明实施例提供的第一种滤波电路的结构示意图。滤波电路3包括:第一电容31、第二电容32、第三电容33、第一谐振器34和第二谐振器35。

上述第一电容31和第二电容32的电容值相同,上述第一谐振器34和第二谐振器35所产生的谐振频率相同。

具体的,第一电容31的一端与信号输入端口1连接,另一端与第一谐振器34的输入端连接;第一谐振器34的输出端与第二谐振器35的输入端、第三电容33的一端连接;第二谐振器35的输出端与第二电容32的一端连接;第二电容32的另一端与信号输出端口2连接;第三电容33的另一端接地。

上述第一电容31、第二电容32用于增强电路匹配特性、加强阻带的信号抑制,从而提高多频带宽滤波器的性能。

上述第三电容33用于产生传输零点,控制滤波器的带宽和提高信号的选择性。

由于每一滤波电路对应一个频段,用于对所对应频段的信号进行带通滤波,所以各滤波电路包括的第一电容31的电容值可以不相同、第二电容32的电容值可以不相同、第三电容33的电容值可以不相同、第一谐振器34所产生的谐振频率可以不同、且第二谐振器35所产生的谐振频率可以不同。

参见图3,图3为本发明实施例提供的第二种滤波电路的结构示意图。在图2的基础上,第一谐振器34和第二谐振器35可以均为:包括第四电容301和第一电感302的谐振器。

上述第四电容301与第一电感302并联形成并联电路,并联电路的一端作为谐振器的输入端,上述并联电路的另一端作为谐振器的输出端。

在这种情况下,第一谐振器34和第二谐振器35可以通过第一电感302间的互感耦合方式相连接。在图3中以双向虚线箭头表示。

由于是以第一电感302间的互感耦合方式相连接,减少了基本元件数量、缩小滤波器电路尺寸,实现芯片小型化。

具体的电路连接的描述可以参见图2中电路连接的描述。

在第一谐振器34和第二谐振器35均为:包括第四电容301和第一电感302的谐振器的情况下,各滤波电路包括的谐振器中第四电容301的电容值可以不相同、且第一电感302的电感值可以不相同。

以下结合图4a、图4b以及图4c分别对四频带通滤波器芯片、三频带通滤波器芯片以及双频带通滤波器芯片进行说明。

参见图4a,图4a为本发明实施例提供的一种四频带带通滤波器芯片的结构示意图。

上述滤波器芯片包括信号输入端口1、信号输出端口2,四个滤波电路3。

其中,滤波电路3中包括第一电容31、第二电容32、第三电容33、第一谐振器34、第二谐振器35。

第一谐振器34、第二谐振器35均为:包括第四电容301和第一电感302的谐振器,第四电容301和第一电感并联形成并联电路。第一谐振器34和第二谐振器35间可以通过第一电感302间互感耦合方式相连接。

具体电路连接的描述可以参见图1、图2中电路连接的描述。

滤波电路3对应的频段范围可以分别为:[3.15,3.43]、[4.78,4.86]、[6.43,6.55]、[8.46,8.64]。单位为GHz。

当滤波电路3对应的频段范围为[3.15,3.43]时,第一电容31/第二电容32的电容值可以在[1.40pF,1.50pF]内,第四电容301的电容值可以在[1.50pF,1.55pF]内,第三电容33的电容值可以在[17.00pF,17.50pF]内,第一电感302的电感值可以在[1.00nH,1.05nH]内,两个谐振器中第一电感302间的耦合电感的互感值可以在[0.15nH,0.20nH]内。

例如:第一电容31/第二电容32的电容值可以为1.40pF,第四电容301的电容值可以为1.53pF,第三电容33的电容值可以为17.00pF,第一电感302的电感值可以为1.02nH,互感值可以为0.17nH

当滤波电路3对应的频段范围为[4.78,4.86]时,第一电容31/第二电容32的电容值可以在[0.55pF,0.60pF]内,第四电容301的电容值可以在[1.50pF,1.55pF]内,第三电容33的电容值可以在[1.25pF,1.30pF]内,第一电感302的电感值可以在[0.55nH,0.60nH]内,两个谐振器中第一电感302间的耦合电感的互感值可以在[0.01nH,0.05nH]内。

例如:第一电容31/第二电容32的电容值可以为0.55pF,第四电容301的电容值可以为1.53pF,第三电容33的电容值可以为1.25pF,第一电感302的电感值可以为0.59nH,互感值可以为0.04nH。

当滤波电路3对应的频段范围为[6.43,6.55]时,第一电容31/第二电容32的电容值可以在[0.40pF,0.45pF]内,第四电容301的电容值可以在[0.50pF,0.55pF]内,第三电容33的电容值可以在[1.45pF,1.50pF]内,第一电感302的电感值可以在[0.70nH,0.75nH]内,两个谐振器中第一电感302间的耦合电感的互感值可以在[0.05nH,0.10nH]内。

例如:第一电容31/第二电容32的电容值可以为0.44pF,第四电容301的电容值可以为0.55pF,第三电容33的电容值可以为1.48pF,第一电感302的电感值可以为0.72nH,互感值可以为0.08nH。

当滤波电路3对应的频段范围为[8.46,8.64]时,第一电容31/第二电容32的电容值可以在[0.50pF,0.55pF]内,第四电容301的电容值可以在[0.50pF,0.55pF]内,第三电容33的电容值可以在[0.55pF,0.60pF]内,第一电感302的电感值可以在[0.40nH,0.45nH]内,两个谐振器中第一电感302间的耦合电感的互感值可以在[0.05nH,0.10nH]内。

例如:第一电容31/第二电容32的电容值可以为0.52pF,第四电容301的电容值在0.55pF,第三电容33的电容值在0.56pF,第一电感302的电感值在0.44nH,互感值为0.07nH。

参见图4b,图4b为本发明实施例提供的一种三频带通滤波器芯片的结构示意图。

上述滤波器芯片包括信号输入端口1、信号输出端口2,三个滤波电路3。

其中,滤波电路3中包括第一电容31、第二电容32、第三电容33、第一谐振器34、第二谐振器35。

第一谐振器34、第二谐振器35均为:包括第四电容301和第一电感302的谐振器,第四电容301和第一电感并联形成并联电路。第一谐振器34和第二谐振器35间可以通过第一电感302间互感耦合方式相连接。

具体电路连接的描述可以参见图1、图2中电路连接的描述。

滤波电路3对应的频段范围可以分别为:[3.16,3.52]、[4.80,4.90]、[6.53,6.75]。单位为GHz。

当滤波电路3对应的频段范围为[3.16,3.52]时,第一电容31/第二电容32的电容值可以在[1.00pF,1.50pF]内,第四电容301的电容值可以在[1.55pF,1.60pF]内,第三电容33的电容值可以在[18.00pF,18.50pF]内,第一电感302的电感值可以在[1.00nH,1.05nH]内,两个谐振器中第一电感302间的耦合电感的互感值可以为[0.15nH,0.20nH]内。

例如:第一电容31/第二电容32的电容值可以为1.40pF,第四电容301的电容值可以为1.59pF,第三电容33的电容值可以为18.20pF,第一电感302的电感值可以为1.02nH,互感值可以为0.19nH

当滤波电路3对应的频段范围为[4.80,4.90]时,第一电容31/第二电容32的电容值可以在[0.50pF,0.55pF]内,第四电容301的电容值可以在[1.50pF,1.55pF]内,第三电容33的电容值可以在[1.30pF,1.35pF]内,第一电感302的电感值可以在[0.55nH,0.60nH]内,两个谐振器中第一电感302间的耦合电感的互感值可以在[0.01nH,0.05nH]内。

例如:第一电容31/第二电容32的电容值可以为0.53pF,第四电容301的电容值可以为1.53pF,第三电容33的电容值可以为1.35pF,第一电感302的电感值可以为0.59nH,互感值可以为0.04nH。

当滤波电路3对应的频段范围为[6.53,6.78]时,第一电容31/第二电容32的电容值可以在[0.40pF,0.45pF]内,第四电容301的电容值可以在[0.50pF,0.55pF]内,第三电容33的电容值可以在[1.50pF,1.55pF]内,第一电感302的电感值可以在[0.70nH,0.75nH]内,两个谐振器中第一电感302间的耦合电感的互感值可以在[0.05nH,0.10nH]内。

例如:第一电容31/第二电容32的电容值可以为0.44pF,第四电容301的电容值可以为0.54pF,第三电容33的电容值可以为1.53pF,第一电感302的电感值可以为0.72nH,互感值可以为0.08nH。

参见图4c,图4c为本发明实施例提供的一种双频带通滤波器芯片的结构示意图,双频带通滤波器中包含两个滤波电路3。

上述滤波器芯片包括信号输入端口1、信号输出端口2,两个滤波电路3。

其中,滤波电路3中包括第一电容31、第二电容32、第三电容33、第一谐振器34、第二谐振器35。

第一谐振器34、第二谐振器35均为:包括第四电容301和第一电感302的谐振器,第四电容301和第一电感并联形成并联电路。第一谐振器34和第二谐振器35间可以通过第一电感302间互感耦合方式相连接。

具体电路连接的描述可以参见图1、图2中电路连接的描述。

滤波电路3对应的频段范围可以分别为:[4.60,5.26]、[3.15,3.75]。单位为GHz。

当滤波电路3对应频段范围为[4.60,5.26]时,第一电容31/第二电容32的电容值可以在[0.50pF,0.55pF]内,第三电容33的电容值可以在[1.20pF,1.25pF]内,第四电容301的电容值可以在[1.50pF,1.55pF]内,第一电感302的电感值可以在[0.55nH,0.60nH]内,两个谐振器中第一电感302间的耦合电感的互感值可以在[0.20nH,0.25nH]内。

例如:上述第一电容31/第二电容32的电容值可以为0.54pF,第三电容33的电容值可以为1.25pF,第四电容301的电容值可以为1.53pF,第一电感的电感值可以为0.59nH,互感值可以为0.24nH。

第一电容31、第二电容32、第三电容33、第四电容301可以为平面电容器,第一电感302可以为平面螺旋电感器。

当滤波电路3对应频段范围为[3.15GHz,3.75GHz]时,第一电容31/第二电容32的电容值可以在[1.40pF,1.45pF]内,第三电容33的电容值可以在[15.65pF,15.70pF]内,第四电容301的电容值可以在[1.55pF,1.60pF]内,第一电感302的电感值可以在[1.00nH,1.05nH]内,两个谐振器中第一电感302间的耦合电感可以在[0.050nH,0.055nH]内。

例如:上述第一电容31/第二电容32的电容值可以为1.40pF,第三电容33的电容值可以为15.66pF,第四电容301的电容值可以为1.59pF,第一电感的电感值可以为1.02nH,互感值可以为0.051nH。

第一电容31、第二电容32、第四电容301可以为垂直交趾电容器、第三电容33可以为平面电容器,第一电感302可以为垂直螺旋电感器。

在多频带通滤波器芯片为双频带通滤波器芯片的情况下,可以将信号输入端口1、信号输出端口2和两个滤波电路3通过LTCC技术被集成于13层介质基板,且13层介质基板以堆叠方式集成于一体。

以下结合图5a-图5m,按照所集成的电路由顶部到底部的顺序依次对各层介质基板中的电路结构进行说明。

第一层电路结构:如图5a所示。

在图5a中黑色部分是金属导体、白色部分是介质材料。

其中,边长为L

具体的,L

第二层电路结构:如图5b所示。

在图5b中黑色部分是金属导体、白色部分是介质材料。

其中,边长为L

具体的,L

第三层电路结构:如图5c所示。

在图5c中黑色部分为金属导体,白色部分为介质材料。

其中,边长为L

具体的,L

第四层电路结构:如图5d所示。

在图5d中黑色部分为金属导体,白色部分为介质材料。

其中,边长为L

具体的,L

第五层电路结构:如图5e所示。

在图5e中黑色部分为金属导体,白色部分为介质材料。

其中,边长为L

具体的,L

第六层电路结构:如图5f所示。

在图5f中黑色部分为金属导体,白色部分为介质材料。

其中,边长为L

具体的,L

第七层电路结构:如图5g所示。

在图5g中黑色部分为金属导体,白色部分为介质材料。

其中,边长为L

具体的,L

第八层电路结构:如图5h所示。

在图5h中黑色部分为金属导体,白色部分为介质材料。

其中,边长为L

具体的,L

第九层电路结构:如图5i所示。

图5i所示的电路结构均为介质材料,除必要的金属信号孔外,无其他导体。

第十层电路结构:如图5j所示。

在图5j中黑色部分为金属导体,白色部分为介质材料。

其中,边长为L

具体的,L

第十一层电路结构:如图5k所示。

在图5k中黑色部分为金属导体,白色部分为介质材料。

其中,边长为L

具体的,L

第十二层电路结构:如图5l所示。

在图5l中黑色部分为金属导体,白色部分为介质材料。

其中,边长为L

具体的,L

第十三层电路结构:如图5m所示。

在图5m中黑色部分为金属导体,白色部分为介质材料。

其中,边长为L

具体的,L

基于上述各层电路结构所得到的双频带通滤波器的三维立体版图模型如图5n所示,其中,上述三维立体版图模型的版图尺寸为:3.2mm*3.5mm*1.1mm。

图5o为图5n所示的三维立体版图模型的侧视图。从图5o可以看到各层介质基板以堆叠方式集成于一体。

图6a为本发明实施例提供的第一种仿真结果的示意图。图6a中横坐标为:频率,单位为:GHz,纵坐标为:S参数,单位为:dB。

从图6a中可以看到,两个仿真结果的带内回波损耗都在-20dB以下,通带内的匹配效果很好,紧贴低,高两通带两侧各有一个传输零点,提高了信号的选择性,并且阻带的插入损耗都在-15dB以下,阻带信号的抑制效果很好。

图6b为本发明实施例提供的第二种仿真结果的示意图。图6b中横坐标为:频率,单位为:GHz,纵坐标为:S参数,单位为:dB。

从图6b中可以看到,通带内插入损耗小于1.0dB,回波损耗在两通带内均大于15dB,低通带范围为3.15GHz-3.75GHz,相对带宽为17.4%,高通带范围为4.60GHz-5.26GHz,相对带宽为13.4%。

图6a、图6b均为双频带通滤波器芯片的仿真结果。

图6c为本发明实施例提供的第三种仿真结果的示意图。图6c中横坐标为:频率,单位为:GHz,纵坐标为:S参数,单位为:dB。

图6c为三频带通滤波器芯片的仿真结果。

图6d为本发明实施例提供的第四种仿真结果的示意图。图6c中横坐标为:频率,单位为:GHz,纵坐标为:S参数,单位为:dB。

图6d为四频带通滤波器芯片的仿真结果。

需要说明的是,在本文中,诸如第一和第二等之类的关系术语仅仅用来将一个实体或者操作与另一个实体或操作区分开来,而不一定要求或者暗示这些实体或操作之间存在任何这种实际的关系或者顺序。而且,术语“包括”、“包含”或者其任何其他变体意在涵盖非排他性的包含,从而使得包括一系列要素的过程、方法、物品或者设备不仅包括那些要素,而且还包括没有明确列出的其他要素,或者是还包括为这种过程、方法、物品或者设备所固有的要素。在没有更多限制的情况下,由语句“包括一个……”限定的要素,并不排除在包括所述要素的过程、方法、物品或者设备中还存在另外的相同要素。

以上所述仅为本发明的较佳实施例而已,并非用于限定本发明的保护范围。凡在本发明的精神和原则之内所作的任何修改、等同替换、改进等,均包含在本发明的保护范围内。

- 一种对称互感耦合小型化多频带通LTCC滤波器芯片

- 一种基于多频耦合的LTCC平衡式带通滤波器