层叠式半导体器件及其测试方法

文献发布时间:2023-06-19 11:45:49

相关申请的交叉引用

本申请要求于2019年12月23日提交的申请号为10-2019-0173005的韩国专利申请以及2019年12月24日提交的申请号为10-2019-0174014的韩国专利申请的优先权,其全部内容通过引用合并于此。

技术领域

本发明的各种实施例涉及半导体设计技术,并且更具体地,涉及用于待层叠的层叠式半导体器件的测试方法。

背景技术

随着半导体技术的飞速发展,用于半导体集成器件的封装技术需要高集成度和高性能。因此,除了具有形成在其中的集成电路的半导体芯片通过导线或凸块(bump)二维布置在印刷电路板(PCB)上的二维(2D)结构之外,已经开发了用于其中竖直层叠有多个半导体芯片的三维(3D)结构的各种技术。

这样的3D结构可以通过其中竖直地层叠有多个半导体芯片的层叠式半导体器件来实现。在垂直方向上层叠的半导体芯片可以安装在半导体封装衬底上,同时通过多个穿通电极(例如,穿通硅通孔(TSV))彼此电连接。

在TSV中,可能发生各种类型的缺陷。这些缺陷可以包括TSV的空隙故障、凸块接触故障或裂纹故障(crack fail)。当TSV未被导电材料完全填充时发生空隙故障,并且当芯片被弯曲或凸块材料被移动时发生凸块接触故障。有故障的TSV(faulty TSV)无法电连接多个芯片。因此,需要使用测试来检测任何潜在的TSV缺陷以便可以采取校正措施,包括用无故障的TSV替换有故障的TSV。

发明内容

本发明的各个实施例针对一种层叠式半导体器件,其能够在将该层叠式半导体器件与控制器封装在一起之前在晶片级验证穿通电极是否正常地操作。

本发明的各个实施例针对一种能够根据信号传输速率来测试穿通电极的操作特性的层叠式半导体器件。

本发明的各个实施例针对一种能够仅测试穿通电极及其接口电路的层叠式半导体器件。

在一个实施例中,层叠式半导体器件可以包括:基底裸片;以及多个核心裸片,其层叠在所述基底裸片上方,并且经由多个穿通电极和参考穿通电极彼此耦接,其中,所述基底裸片包括:第一测试电路,其适用于在测试操作期间,向多个穿通电极之中的至少一个目标穿通电极传送测试振荡信号,并且通过将基于测试振荡信号产生的测试基底信号与经由参考穿通电极传送来的测试核心信号进行比较来输出测试输出信号;以及其中,所述多个核心裸片中的每个包括:第二测试电路,其适用于在测试操作期间,产生与经由目标穿通电极传送来的测试振荡信号相对应的测试核心信号,并且向参考穿通电极传送测试核心信号。

在一个实施例中,一种层叠式半导体器件的测试方法,所述层叠式半导体器件包括:基底裸片;以及多个核心裸片,其层叠在所述基底裸片上方并且经由多个穿通电极和参考穿通电极彼此耦接,所述测试方法可以包括:在基底裸片处向多个穿通电极之中的目标穿通电极传送测试振荡信号,并且基于测试振荡信号来产生测试基底信号;在多个核心裸片中的任意一个处,基于经由目标穿通电极传送来的测试振荡信号来产生测试核心信号;以及在基底裸片处,通过将经由参考穿通电极传送来的测试核心信号与测试基底信号进行比较来输出测试输出信号。

通过以下结合附图对本发明各个实施例的详细描述,本发明所属领域的普通技术人员将更好地理解本发明的这些以及其他特征和优点。

附图说明

图1是示出根据本发明的实施例的半导体存储系统的截面图。

图2是示出根据本发明的实施例的图1所示的层叠式存储器件的透视图。

图3是示出根据本发明的各种实施例的用于测试层叠式存储器件的配置的示图。

图4是用于描述根据本发明的各种实施例的图3所示的错误检测电路的操作的时序图。

图5是示出根据本发明的各种实施例的半导体器件的电路图。

图6是示出根据本发明的各种实施例的图5所示的第一错误检测电路的详细电路图。

图7和图8是用于描述根据本发明的各种实施例的半导体器件的测试操作的流程图和时序图。

图9是示出根据本发明的各种实施例的半导体器件的电路图。

图10是描述根据本发明的实施例的设置在图2所示的基底裸片上的凸块的平面图。

图11是描述根据本发明的实施例的设置在图2所示的核心裸片上的凸块的平面图。

图12是示出根据本发明实施例的层叠式存储器件的配置的示图。

图13是示出根据本发明的实施例的层叠式存储器件的配置的示图。

图14是示出根据本发明的第一实施例的、图13的层叠式存储器件的第一测试电路和第二测试电路的详图。

图15是示出根据本发明的第二实施例的、图13的层叠式存储器件的第一测试电路和第二测试电路的详图。

图16是描述根据本发明实施例的层叠式存储器件的测试操作的流程图。

图17是示出根据本发明的第三实施例的、图13的层叠式存储器件的第一测试电路和第二测试电路的详图。

图18是示出根据本发明的实施例的层叠式存储器件的配置的示图。

具体实施方式

下面将参考附图更详细地描述本发明的各种实施例。然而,本发明可以以不同的形式实施,并且不应被解释为限于本文中所阐述的实施例。相反,提供这些实施例以使得本公开将是透彻和完整的,并将向本领域技术人员充分传达本发明的范围。贯穿本公开,在本发明的各个附图和实施例中,相同的附图标记指代相同的部件。还应注意,在本说明书中,“连接/耦接”不仅指一个组件直接与另一组件耦接,而且还指其通过中间组件而间接与另一组件耦接。另外,如果未在语句中专门提及,则单数形式可以包括复数形式。

在下文中,将层叠式半导体器件作为示例来描述半导体存储系统。根据实施例的半导体存储系统可以以系统级封装(SIP)模块、多芯片封装(MCP)模块或片上系统(SoC)模块的形式来实施,或以包括多个封装体的层叠式封装(PoP)模块的形式来实施。

图1是示出根据本发明的实施例的半导体存储系统100的示图。

参考图1,存储系统100可以包括层叠式存储器件110和控制器(或处理器)120。由于控制器120通常被包括在诸如中央处理单元(CPU)、图形处理单元(GPU)和应用程序处理器(AP)之类的各种处理器中,因此控制器120也可以被称为如图1指定的处理器。存储系统100还可以包括插入器130和封装衬底140。插入器130可以形成在封装衬底140上方。

层叠式存储器件110和控制器120均可以形成在插入器130上方。层叠式存储器件110与控制器120可以在竖直方向上彼此不重叠。

层叠式存储器件110的物理区域(PHY)1142可以经由插入器130耦接到控制器120的物理区域(PHY)122。用于在层叠式存储器件110与控制器120之间的通信的接口电路可以设置在物理区域1142和122的每一个中。

层叠式存储器件110可以形成高带宽存储器(HBM)。HBM可以具有与通过在竖直方向上层叠多个裸片(即,半导体芯片)并经由穿通电极TSV将它们电连接而得到的I/O单元的增加数量相对应的高带宽。

多个裸片可以包括基底裸片114和多个核心裸片112。核心裸片112可以层叠在基底裸片114上方。核心裸片112和基底裸片114可以经由穿通电极TSV彼此耦接。虽然图1的实施例示出了层叠有四个核心裸片112(即,第一核心裸片112_0至第四核心裸片112_3)的情况,但是本发明的构思和精神不限于此,并且被层叠的核心裸片的数量可以根据半导体器件的设计而变化。

每个核心裸片112可以用存储芯片来实施。每个核心裸片112可以包括用于储存数据的多个存储单元以及用于支持对存储单元的核心操作的电路。基底裸片114提供了核心裸片112与控制器120之间的接口,使得可以执行半导体系统100内的各种功能,诸如存储管理功能(例如,针对存储单元的刷新管理功能和电力管理功能)以及在核心裸片112与控制器120之间的时序调整功能。

基底裸片114可以包括物理区域1142和直接访问(DA)区域1146。在物理区域1142中,可以设置用于与控制器120通信的接口电路。在直接访问区域1146中,可以设置用于直接测试层叠式存储器件110的接口电路。基底裸片114还被称为缓冲裸片。

图2是根据本发明的一个实施例的图1所示的层叠式存储器件110的透视图。

参考图2,第一核心裸片112_0至第四核心裸片112_3中的每一个可以包括一个或更多个通道。在图2的示例中,每个核心裸片包括两个通道,并且层叠式存储器件110包括第一通道CH0至第八通道CH7。例如,第一核心裸片112_0可以包括与第一通道CH0和第三通道CH2相对应的存储区域,并且第二核心裸片112_1可以包括与第二通道CH1和第四通道CH3相对应的存储区域。第三核心裸片112_2可以包括与第五通道CH4和第七通道CH6相对应的存储区域,并且第四核心裸片112_3可以包括与第六通道CH5和第八通道CH7相对应的存储区域。

例如,第一存储体至第八存储体可以对应于每个通道。此外,穿过第一核心裸片112_0至第四核心裸片112_3的多个穿通电极TSV可以被设置为分别对应于第一通道CH0至第八通道CH7。当每个通道具有128比特位的带宽(即,每个裸片有两个128比特位的通道)时,穿通电极TSV和对应的I/O单元可以被配置为传输1024比特位的数据。每个通道可以类似于标准DDR接口,但是可以完全独立并且因此在一个层叠式存储器件内甚至在一个裸片内的每个通道可以以不同的频率和/或不同的定时工作。

基底裸片114可以与控制器120通信(参见图1)。例如,基底裸片114可以从控制器120接收命令、地址和数据,并且可以向第一核心裸片112_0至第四核心裸片112_3提供所接收到的命令、地址和数据。

物理区域(PHY)1142、TSV区域(TSVA)1144和直接访问区域(DA)1146可以设置在基底裸片114中。

物理区域1142可以设置有用于与控制器120交互的I/O电路。物理区域1142可以设置在基底裸片114的、与控制器120相邻的第一边缘区域中。直接访问区域1146可以设置有用于直接与外部测试设备(未示出)交互的I/O电路。直接访问区域1146可以设置在基底裸片114的、与外部测试设备相邻的第二边缘区域中。第二边缘区域可以处于与第一边缘区域相对的方向上。TSV区域1144可以是用于与穿过第一核心芯片112_0至第四核心芯片112_3的穿通电极TSV交互的区域。TSV区域1144可以设置在物理区域1142与直接访问区域1146之间,即,TSV区域1144可以设置在基底裸片114的中央区域。

物理区域1142可以向TSV区域1144传送从控制器120接收的信号。直接访问区域1146可以向TSV区域1144传送从外部测试设备接收的测试信号。TSV区域1144可以对从物理区域1142接收的信号或从直接访问区域1146接收的测试信号执行预定的信号处理操作(例如缓冲操作),以便经由穿通电极TSV向第一核心芯片112_0至第四核心芯片112_3传送被缓冲的信号。

由于穿通电极TSV需要保证物理连接,因此穿通电极TSV需要通过测试,例如,开路/短路(OS)测试。当在对在列方向上连接的穿通电极TSV执行的OS测试期间检测到缺陷时,可以用冗余穿通电极替换具有缺陷的穿通电极TSV。

图3是示出用于测试图2所示的层叠式存储器件110的配置的示图。

参考图3,层叠式存储器件110可以包括基底裸片114和多个核心裸片112_0至112_3,其被层叠并利用通过多个穿通电极TSV0X至TSV4X所分配的通道来通信。如图3所示,核心裸片112_0-112_3可以在竖直方向上层叠。然而,在另一实施例中,在不脱离本发明的范围的情况下,核心裸片112_0-112_3可以在水平方向上层叠。为了描述的方便,尽管图3示出了穿通电极TSV0X至TSV4X,一个穿通电极针对在列方向上的每个核心裸片,但是可以针对每个核心裸片形成多个穿通电极。

第一核心裸片112_0至第四核心裸片112_3可以分别包括穿通电极扫描电路(through-electrode scan circuit)23_1至23_4和错误检测电路24_1至24_4。

穿通电极扫描电路23_1至23_4可以对穿通电极之中的在列方向上连接的穿通电极TSV0X至TSV4X执行下行扫描(down-scan)和上行扫描(up-scan)。下行扫描可以指使信号沿向下的方向穿过穿通电极TSV0X至TSV4X,并且上行扫描可以指使信号沿向上的方向穿过穿通电极TSV0X至TSV4X。错误检测电路24_1至24_4可以基于下行扫描和上行扫描来检测穿通电极TSV0X至TSV4X是否具有缺陷。

穿通电极扫描电路23_1至23_4中的每个可以包括下行扫描单元和上行扫描单元。下行扫描单元可以通过使电流向下流过在列方向上连接的穿通电极TSV0X至TSV4X来执行下行扫描。下行扫描单元可以包括电流源PM4。电流源PM4可以响应于下行扫描信号DN_SCAN而向穿通电极TSV1X至TSV4X的一个端子NO1至NO4提供源电流。上行扫描单元可以通过使电流向上流过在列方向上连接的穿通电极TSV0X至TSV4X来执行上行扫描。上行扫描单元可以包括电流阱(current sink)NM4。电流阱NM4可以响应于上行扫描信号UP_SCAN来吸收经由穿通电极TSV1X至TSV4X的端子NO1至NO4所传输的信号。作为参考,由于下行扫描信号DN_SCAN和上行扫描信号UP_SCAN被激活为逻辑高电平,因此下行扫描单元还可以包括反相器以用于驱动由PMOS晶体管构成的电流源PM4。

错误检测电路24_1至24_4可以根据下行扫描信号DN_SCAN和锁存信号OS_LAT而将下行扫描结果储存为第一值,并且可以根据上行扫描信号UP_SCAN和锁存信号OS_LAT而将上行扫描结果储存为第二值。然后,错误检测电路24_1至24_4可以将所储存的第一值与第二值进行组合以产生故障确定信号FAIL

基底裸片114可以包括穿通电极扫描电路23_0和错误检测电路24_0。穿通电极扫描电路23_0可以包括电流阱NM0和电流源PM0。电流阱NM0可以响应于下行扫描信号DN_SCAN而吸收在向下的方向上经由穿通电极TSV0X的一个端子NO0传输的信号。电流源PM0可以响应于上行扫描信号UP_SCAN而向穿通电极TSV0X的端子NO0提供与在向上的方向上传输的信号相对应的源电流。基底裸片114的电流源PM0可以响应于上行扫描信号UP_SCAN而被导通,而第一核心裸片112_0至第四核心裸片112_3的电流源PM4可以响应于下行扫描信号DN_SCAN而被导通。因此,电流源PM0可以与电流源PM4互补地操作。同样地,基底裸片114的电流阱NM0可以响应于下行扫描信号DN_SCAN而被导通,而第一核心裸片112_0至第四核心裸片112_3的电流阱NM4可以响应于上行扫描信号UP_SCAN而被导通。因此,电流阱NM0可以与电流阱NM4互补地操作。错误检测电路24_0可以与第一核心裸片112_0至第四核心裸片112_3的错误检测电路24_1至24_4中的每一个具有基本上相同的配置。

基底裸片114和第一核心裸片112_0至第四核心裸片112_3可以包括修复电路25_0至25_4。修复电路25_0至25_4可以基于故障确定信号FAIL

在启动操作或初始操作期间,可以向第一核心裸片112_0至第四核心裸片112_3中的每一个分配芯片标识(ID)信号。例如,可以向第一核心芯片112_0分配芯片ID信号“00”,可以向第二核心芯片112_1分配芯片ID信号“01”,可以向第三核心裸片112_2分配芯片ID信号“10”,并且可以向第四核心裸片112_3分配芯片ID信号“11”。根据一个实施例,使用这种具有叠层信息的芯片ID信号,下行扫描信号DN_SCAN和上行扫描信号UP_SCAN可以被施加到在第一核心裸片112_0至第四核心裸片112_3中的选定核心裸片中所包括的电流源PM4和电流阱NM4,而未选定的核心裸片的电流源PM4和电流阱NM4可以被浮置。

图4是用于描述图3所示的错误检测电路24_1至24_4的操作的时序图。

参考图4,当下行扫描信号DN_SCAN被激活时,第四核心裸片112_3的电流源PM4可以向穿通电极TSV4X的一个端子NO4提供源电流,而基底裸片114的电流阱NM0可以吸收在向下的方向上经由穿通电极TSV0X的一个端子NO0传输的信号。因此,可以执行针对穿通电极TSV0X至TSV4X的下行扫描。每个裸片的错误检测电路24_0至24_4可以根据下行扫描信号DN_SCAN和锁存信号OS_LAT将下行扫描结果储存为第一值。

当上行扫描信号UP_SCAN被激活时,基底裸片114的电流源PM0可以向穿通电极TSV0X的端子NO0提供与在向上的方向上传输的信号相对应的源电流,并且第四核心裸片112_3的电流阱NM4可以吸收经由穿通电极TSV4X的端子NO4传输的信号。因此,可以执行针对穿通电极TSV0X至TSV4X的上行扫描。每个裸片的错误检测电路24_0至24_4可以根据上行扫描信号UP_SCAN和锁存信号OS_LAT将上行扫描结果储存为第二值。

最后,每个裸片的错误检测电路24_0至24_4可以基于第一值和第二值来产生故障确定信号FAIL

如上所述,每个裸片的穿通电极扫描电路23_0至23_4和错误检测电路24_0至24_4可以通过对穿通电极TSV0X至TSV4X执行下行扫描和上行扫描来检测穿通电极TSV0X至TSV4X是否具有缺陷。然而,当在错误检测电路24_0至24_4中存在缺陷时,即使穿通电极TSV0X至TSV4X没有缺陷,故障确定信号FAIL

在下文中,将描述一种能够在将半导体器件的多个裸片层叠之前对用于对穿通电极执行测试的错误检测电路的操作进行检测/验证的方法。

图5是示出根据本发明的各种实施例的半导体器件200的电路图。作为参考,图5的半导体器件200可以对应于图1至图3中的多个裸片(即,核心裸片和基底裸片)中的每个裸片(在所述裸片被层叠之前)。即,图5的半导体器件200可以对应于晶片级的所述裸片中的每个裸片。

参考图5,半导体器件200可以包括:第一穿通电极TSV1至第n穿通电极TSVn,第一穿通电极驱动电路210_1至第n穿通电极驱动电路210_n以及第一错误检测电路220_1至第n错误检测电路220_n。

第一穿通电极驱动电路210_1至第n穿通电极驱动电路210_n可以分别被耦接到第一穿通电极TSV1至第n穿通电极TSVn。第一穿通电极驱动电路210_1至第n穿通电极驱动电路210_n中的每一个可以被耦接到第一穿通电极TSV1至第n穿通电极TSVn中的对应一个的一个端子NOX1至NOXn。第一穿通电极驱动电路210_1至第n穿通电极驱动电路210_n可以将第一穿通电极TSV1至第n穿通电极TSVn充电至第一电压电平(例如,供电电压(VDD)电平),或可以将第一穿通电极TSV1至第n穿通电极TSVn放电至第二电压电平(例如,接地电压(VSS)电平)。

在一个实施例中,第一穿通电极驱动电路210_1至第n穿通电极驱动电路210_n中的每个可以包括上拉驱动器PMX和下拉驱动器NMX。上拉驱动器PMX可以根据上拉驱动信号PU_EN而将对应的穿通电极上拉至第一电压电平。例如,上拉驱动器PMX可以用PMOS晶体管来实施,所述PMOS晶体管耦接在供电电压(VDD)端子与对应的穿通电极的一个端子之间,并且具有用于接收上拉驱动信号PU_EN的栅极。下拉驱动器NMX可以根据下拉驱动信号PD_EN而将对应的穿通电极下拉至第二电压电平。例如,下拉驱动器NMX可以用NMOS晶体管来实施,所述NMOS晶体管耦接在对应的穿通电极的一个端子与接地电压(VSS)端子之间,并且具有用于接收下拉驱动信号PD_EN的栅极。优选地,由于上拉驱动信号PU_EN和下拉驱动信号PD_EN被激活为逻辑高电平,因此第一穿通电极驱动电路210_1至第n穿通电极驱动电路210_n中的每一个还可以包括反相器INVX以驱动由PMOS晶体管组成的上拉驱动器PMX。

作为参考,第一穿通电极驱动电路210_1至第n穿通电极驱动电路210_n可以对应于图3中所示的每个裸片(在层叠所述裸片之后)的穿通电极扫描电路(例如,23_0至23_4)。上拉驱动器PMX和下拉驱动器NMX可以对应于图3中所示的每个裸片(在层叠所述裸片之后)的电流源(例如,PM0和PM4)和电流阱(例如,NM0和MM4)。即,在层叠所述裸片之前,第一穿通电极驱动电路210_1至第n穿通电极驱动电路210_n可以将对应的穿通电极上拉至第一电压电平,或者可以将对应的穿通电极下拉至第二电压电平。在层叠所述裸片之后,第一穿通电极驱动电路210_1至第n穿通电极驱动电路210_n可以对如图3所示的在列方向上连接的穿通电极(例如,TSV0X至TSV4X)执行下行扫描和上行扫描。

第一错误检测电路220_1至第n错误检测电路220_n可以分别被耦接到第一穿通电极TSV1至第n穿通电极TSVn。第一错误检测电路220_1至第n错误检测电路220_n中的每一个可以被耦接到第一穿通电极TSV1至第n穿通电极TSVn中的对应穿通电极的一个端子NOX1至NOXn。第一错误检测电路220_1至第n错误检测电路220_n中的每一个可以将第一穿通电极TSV1至第n穿通电极TSVn中的对应的穿通电极的电压电平储存为下行检测信号DN_DET和上行检测信号UP_DET,并可以通过顺序地掩蔽下行检测信号DN_DET和上行检测信号UP_DET而输出第一错误检测信号至第n错误检测信号FAIL<1:n>中的对应的错误检测信号。

在一个实施例中,第一错误检测电路220_1至第n错误检测电路220_n中的每一个可以包括下行锁存电路222、上行锁存电路224、判定电路226和掩蔽电路228。下行锁存电路222可以响应于下行扫描信号DN_SCAN和锁存信号OS_LAT而将对应的穿通电极的电压电平储存为下行检测信号DN_DET。上行锁存电路224可以响应于上行扫描信号UP_SCAN和锁存信号OS_LAT而将对应的穿通电极的电压电平储存为上行检测信号UP_DET。判定电路226可以基于下行检测信号DN_DET和上行检测信号UP_DET来产生对应的错误检测信号。掩蔽电路228可以通过顺序地掩蔽从下行锁存电路222输出的下行检测信号DN_DET和从上行锁存电路224输出的上行检测信号UP_DET而向判定电路226提供下行检测信号DN_DET和上行检测信号UP_DET。掩蔽电路228可以根据下行掩蔽信号DN_PASS来掩蔽下行检测信号DN_DET,并且可以根据上行掩蔽信号UP_PASS来掩蔽上行检测信号UP_DET。下行掩蔽信号DN_PASS和上行掩蔽信号UP_PASS可以被顺序地激活。将参考图6详细描述下行锁存电路222、上行锁存电路224、判定电路226和掩蔽电路228。

作为参考,第一错误检测电路220_1至第n错误检测电路220_n可以对应于图3中所示的每个裸片(在层叠所述裸片之后)的错误检测电路(24_0至24_4)。在层叠所述裸片之后,下行掩蔽信号DN_PASS和上行掩蔽信号UP_PASS可以被保持为预定的逻辑电平。因此,在层叠所述裸片之后,不管下行掩蔽信号DN_PASS和上行掩蔽信号UP_PASS如何,第一错误检测电路220_1至第n错误检测电路220_n可以根据下行扫描和上行扫描而对穿通电极TSV0X至TSV4X执行缺陷检测操作。

半导体器件200还可以包括第一移位电路230_1至第n移位电路230_n。第一移位电路230_1至第n移位电路230_n可以分别对应于第一错误检测电路220_1至第n错误检测电路220_n。第一移位电路230_1至第n移位电路230_n中的每一个可以被耦接到第一错误检测电路220_1至第n错误检测电路220_n中的对应的错误检测电路。根据选择信号SEL和移位时钟SCLK,第一移位电路230_1至第n移位电路230_n中的每一个可以储存从对应的错误检测电路输出的错误检测信号或在第一移位信号SRO<1>至第n移位信号SRO

在一个实施例中,第一移位电路230_1至第n移位电路230_n中的每一个可以包括选择器232和移位器234。选择器232可以响应于选择信号SEL来选择错误检测信号FAIL

根据上述配置,第一移位电路230_1至第n移位电路230_n可以根据移位时钟SCLK的触发(toggle)而顺序地输出第一错误检测电路220_1至第n错误检测电路220_n的第一错误检测信号至第n错误检测信号FAIL<1:n>作为第n移位信号SRO

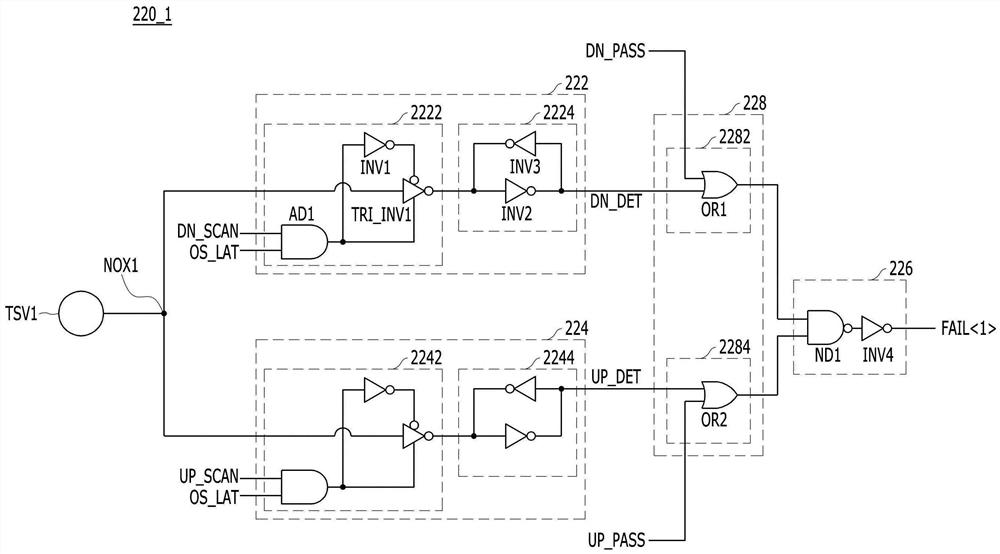

图6是示出图5所示的第一错误检测电路220_1的详细电路图。作为参考,第二错误检测电路220_2至第n错误检测电路220_n可以具有与第一错误检测电路220_1基本上相同的配置。

参考图6,第一错误检测电路220_1的下行锁存电路222可以响应于下行扫描信号DN_SCAN和锁存信号OS_LAT而将第一穿通电极TSV1的电压电平储存为下行检测信号DN_DET。下行锁存电路222可以包括第一发送器2222和第一锁存器2224。第一发送器2222可以基于下行扫描信号DN_SCAN和锁存信号OS_LAT而向第一锁存器2224传送从第一穿通电极TSV1的一个端子NOX1提供的信号(即,第一穿通电极TSV1的电压电平)。第一锁存器2224可以将从第一发送器2222传送的电压电平锁存为下行检测信号DN_DET。

例如,第一发送器2222可以包括第一与门AD1、第一反相器INV1和第一三相反相器TRI_INV1。第一与门AD1可以对下行扫描信号DN_SCAN和锁存信号OS_LAT执行逻辑与运算。第一反相器INV1可以将第一与门AD1的输出反相。第一三相反相器TRI_INV1可以根据第一与门AD1的输出和第一反相器INV1的输出而被使能,并且使经由第一穿通电极TSV1的端子NOX1传输的信号反相。第一锁存器2224可以包括交叉耦接的反相器INV2和INV3。根据上述配置,当下行扫描信号DN_SCAN和锁存信号OS_LAT两者都被激活时,下行锁存电路222可以将从第一穿通电极TSV1的端子NOX1提供的信号储存为下行检测信号DN_DET。

第一错误检测电路220_1的上行锁存电路224可以响应于上行扫描信号UP_SCAN和锁存信号OS_LAT而将第一穿通电极TSV1的电压电平储存为上行检测信号UP_DET。上行锁存电路224可以包括第二发送器2242和第二锁存器2244。第二发送器2242可以基于上行扫描信号UP_SCAN和锁存信号OS_LAT而向第二锁存器2244传送从第一穿通电极TSV1的一个端子NOX1提供的信号(即,第一穿通电极TSV1的电压电平)。第二锁存器2244可以将从第二发送器2242传送的电压电平锁存为上行检测信号UP_DET。第二发送器2242和第二锁存器2244可以分别与第一发送器2222和第一锁存器2224具有基本上相同的配置。根据上述配置,当上行扫描信号UP_SCAN和锁存信号OS_LAT两者都被激活时,上行锁存电路224可以将从第一穿通电极TSV1的端子NOX1提供的信号储存为上行检测信号UP_DET。

第一错误检测电路220_1的判定电路226可以通过将从下行锁存电路222输出的下行检测信号DN_DET和从上行锁存电路224输出的上行检测信号UP_DET进行组合来产生第一错误检测信号FAIL<1>。例如,判定电路226可以包括与非门ND1,其对下行检测信号DN_DET和上行检测信号UP_DET执行逻辑与非运算以输出第一错误检测信号FAIL<1>。

第一错误检测电路220_1的掩蔽电路228可以顺序地掩蔽从下行锁存电路222输出的下行检测信号DN_DET和从上行锁存电路224输出的上行检测信号UP_DET。掩蔽电路228可以包括下行掩蔽电路2282和上行掩蔽电路2284。下行掩蔽电路2282可以根据下行掩蔽信号DN_PASS来掩蔽下行检测信号DN_DET。上行掩蔽电路2284可以根据上行掩蔽信号UP_PASS来掩蔽上行检测信号UP_DET。优选地,下行掩蔽电路2282和上行掩蔽电路2284可以分别利用第一或门OR1和第二或门OR2来实施。即,下行掩蔽电路2282可以在下行掩蔽信号DN_PASS具有逻辑高电平时将下行检测信号DN_DET掩蔽为逻辑高电平,而可以在下行掩蔽信号DN_PASS具有逻辑低电平时输出下行检测信号DN_DET。上行掩蔽电路2284可以在上行掩蔽信号UP_PASS具有逻辑高电平时掩蔽上行检测信号UP_DET,而可以在上行掩蔽信号UP_PASS具有逻辑低电平时输出上行检测信号UP_DET。在层叠裸片(或半导体器件)之后,下行掩蔽信号DN_PASS和上行掩蔽信号UP_PASS可以被保持为逻辑低电平,从而防止由掩蔽电路228执行掩蔽操作。

在层叠之前,第一错误检测电路220_1至第n错误检测电路220_n可以产生指示下行锁存电路222或上行锁存电路224是否具有缺陷的第一错误检测信号至第n错误检测信号FAIL<1:n>。此外,在层叠之后,基于对在列方向上连接的穿通电极TSV0X至TSV4X的下行扫描操作和上行扫描操作,第一错误检测电路220_1至第n错误检测电路220_n可以产生指示穿通电极TSV0X至TSV4X(图3的)是否具有缺陷的第一错误检测信号至第n错误检测信号FAIL<1:n>。

在下文中,参考图5至图8,将描述根据本实施例的半导体器件200的测试操作。

图7和图8是用于描述根据本发明的各种实施例的半导体器件的测试操作的流程图和时序图。

参考图7和图8,可以执行对上行锁存电路224的高测试(步骤S810)。对于高测试,第一穿通电极驱动电路210_1至第n穿通电极驱动电路210_n可以将第一穿通电极TSV1至第n穿通电极TSVn充电至第一电压电平。当上拉驱动信号PU_EN被激活时,第一穿通电极驱动电路210_1至第n穿通电极驱动电路210_n可以将第一穿通电极TSV1至第n穿通电极TSVn上拉至供电电压VDD。第一错误检测电路220_1至第n错误检测电路220_n中的每一个可以在掩蔽下行检测信号DN_DET的情况下将对应的穿通电极的电压电平储存为上行检测信号UP_DET,从而输出对应的错误检测信号。

在一个实施例中,当上行扫描信号UP_SCAN和锁存信号OS_LAT被激活时,上行锁存电路224可以将对应的穿通电极的电压电平储存为上行检测信号UP_DET。此时,由于下行掩蔽信号DN_PASS被激活,因此掩蔽电路228可以掩蔽下行检测信号DN_DET。判定电路226可以基于上行检测信号UP_DET和被掩蔽为逻辑高电平的下行检测信号DN_DET来产生对应的错误检测信号。结果,在对上行锁存电路224的高测试期间,不管下行锁存电路222的操作如何,都可以根据从上行锁存电路224输出的上行检测信号UP_DET而产生第一错误检测信号至第n错误检测信号FAIL<1:n>。

尽管未在图8中示出,当选择信号SEL转变为逻辑高电平并且移位时钟SCLK触发一次时,第一移位电路230_1至第n移位电路230_n可以分别储存第一错误检测信号至第n错误检测信号FAIL<1:n>。此外,当选择信号SEL转变为逻辑低电平并且移位时钟SCLK触发n次时,第一移位电路230_1至第n移位电路230_n可以顺序地将第一错误检测信号至第n错误检测信号FAIL<1:n>移位,以经由测试焊盘TPAD将第n移位信号SRO

外部测试设备可以基于第n移位信号SRO

接下来,可以执行对下行锁存电路222的高测试(步骤S820)。对于高测试,上拉驱动信号PU_EN可以被激活,并且因此第一穿通电极驱动电路210_1至第n穿通电极驱动电路210_n可以将第一穿通电极TSV1至第n穿通电极TSVn上拉至供电电压VDD。第一错误检测电路220_1至第n错误检测电路220_n中的每一个可以在掩蔽上行检测信号UP_DET的情况下将对应的穿通电极的电压电平储存为下行检测信号DN_DET,从而输出对应的错误检测信号。

在一个实施例中,当下行扫描信号DN_SCAN和锁存信号OS_LAT被激活时,下行锁存电路222可以将对应的穿通电极的电压电平储存为下行检测信号DN_DET。此时,由于上行掩蔽信号UP_PASS被激活,因此掩蔽电路228可以掩蔽上行检测信号UP_DET。判定电路226可以基于下行检测信号DN_DET和被掩蔽为逻辑高电平的上行检测信号UP_DET而产生对应的错误检测信号。结果,在对下行锁存电路222的高测试期间,不管上行锁存电路224的操作如何,都可以根据从下行锁存电路222输出的下行检测信号DN_DET而产生第一错误检测信号至第n错误检测信号FAIL<1:n>。

此后,根据选择信号SEL和移位时钟SCLK,第一移位电路230_1至第n移位电路230_n可以分别储存第一错误检测信号至第n错误检测信号FAIL<1:n>并将第一错误检测信号至第n错误检测信号FAIL<1:n>顺序地移位,以经由测试焊盘TPAD将第n移位信号SRO

接下来,可以执行对上行锁存电路224的低测试(步骤S830)。对于低测试,下拉驱动信号PD_EN可以被激活,然后第一穿通电极驱动电路210_1至第n穿通电极驱动电路210_n可以将第一穿通电极TSV1至第n穿通电极TSVn下拉至接地电压VSS。当上行扫描信号UP_SCAN、锁存信号OS_LAT和下行掩蔽信号DN_PASS被激活时,第一错误检测电路220_1至第n错误检测电路220_n中的每一个可以在掩蔽下行检测信号DN_DET的情况下将对应的穿通电极的电压电平储存为上行检测信号UP_DET,从而输出对应的错误检测信号。此后,根据选择信号SEL和移位时钟SCLK,第一移位电路230_1至第n移位电路230_n可以分别储存第一错误检测信号至第n错误检测信号FAIL<1:n>并将第一错误检测信号至第n错误检测信号FAIL<1:n>顺序地移位,以经由测试焊盘TPAD将第n移位信号SRO

外部测试设备可以基于第n移位信号SRO

接下来,可以执行对下行锁存电路222的低测试(步骤S840)。对于低测试,下拉驱动信号PD_EN可以被激活,并且因此第一穿通电极驱动电路210_1至第n穿通电极驱动电路210_n可以将第一穿通电极TSV1至第n穿通电极TSVn下拉至接地电压VSS。当下行扫描信号DN_SCAN、锁存信号OS_LAT和上行掩蔽信号UP_PASS被激活时,第一错误检测电路220_1至第n错误检测电路220_n中的每一个可以在掩蔽上行检测信号UP_DET的情况下将对应的穿通电极的电压电平储存为下行检测信号DN_DET,从而输出对应的错误检测信号。此后,根据选择信号SEL和移位时钟SCLK,第一移位电路230_1至第n移位电路230_n可以分别储存第一错误检测信号至第n错误检测信号FAIL<1:n>并将第一错误检测信号至第n错误检测信号FAIL<1:n>顺序地移位,以经由测试焊盘TPAD将第n移位信号SRO

图7和图8示出了其中可以顺序地执行对上行锁存电路224的高测试S810、对下行锁存电路222的高测试S820、对上行锁存电路224的低测试S830以及对下行锁存电路222的低测试S840的情况。然而,本发明的构思和精神不限于此,并且可以在不脱离本发明的范围的情况下改变测试S810至S840的次序。例如,在一个实施例中,对上行锁存电路224的高测试S810、对上行锁存电路224的低测试S830、对下行锁存电路222的高测试S820以及对下行锁存电路222的低测试S840可以按照所述顺序来顺序地执行。

图9是示出根据本发明的各种实施例的半导体器件300的电路图。

参考图9,半导体器件300可以包括第一穿通电极TSV1至第n穿通电极TSVn、第一穿通电极驱动电路310_1至第n穿通电极驱动电路310_n和第一错误检测电路320_1至第n错误检测电路320_n。第一穿通电极驱动电路310_1至第n穿通电极驱动电路310_n和第一错误检测电路320_1至第n错误检测电路320_n可以具有与图5的配置基本上相同的配置。

与图5中的半导体器件200的不同,半导体器件300可以压缩从第一错误检测电路320_1至第n错误检测电路320_n输出的第一错误检测信号至第n错误检测信号FAIL<1:n>,从而一次输出第一压缩信号FAIL_H

半导体器件300可以包括第一压缩电路330和第二压缩电路340。

当在高测试期间第一穿通电极TSV1至第n穿通电极TSVn被充电至第一电压电平时,第一压缩电路330可以压缩第一错误检测信号至第n错误检测信号FAIL<1:n>以输出第一压缩信号FAIL_H

在一个实施例中,第一压缩电路330可以包括第一高压缩器330_1至第n高压缩器330_n。第一高压缩器330_1至第n高压缩器330_n可以对从前一位置的高压缩器330_1至330_n-1输出的信号FAIL_H<1:n-1>和第一错误检测信号至第n错误检测信号FAIL<1:n>执行逻辑与运算。位于第一级的第一高压缩器330_1可以对第一错误检测信号FAIL<1>和第一判断信号JUDGE_H执行逻辑与运算。位于最后一级的第n高压缩器330_n可以通过对从第(n-1)高压缩器330_n-1输出的信号FAIL_H

当在低测试期间第一穿通电极TSV1至第n穿通电极TSVn被放电至第二电压电平时,第二压缩电路340可以压缩第一错误检测信号至第n错误检测信号FAIL<1:n>以输出第二压缩信号FAIL_L

在一个实施例中,第二压缩电路340可以包括第一低压缩器340_1至第n低压缩器340_n。第一低压缩器340_1至第n低压缩器340_n可以对从前一位置的低压缩器340_1至340_n-1输出的信号FAIL_L<1:n-1>和第一错误检测信号至第n错误检测信号FAIL<1:n>执行逻辑或运算。位于第一级的第一低压缩器340_1可以对第一错误检测信号FAIL<1>和第二判断信号JUDGE_L执行逻辑或运算。位于最后一级的第n低压缩器340_n可以通过对从第(n-1)低压缩器340_n-1输出的信号FAIL_L

在下文中,参考图7至图9,将描述根据本实施例的半导体器件300的测试操作。

首先,可以执行对上行锁存电路的高测试(步骤S810)。在高测试期间,上拉驱动信号PU_EN可以被激活,并且上行扫描信号UP_SCAN、锁存信号OS_LAT和下行掩蔽信号DN_PASS可以被激活。因此,不管下行锁存电路的操作如何,都可以根据从上行锁存电路输出的上行检测信号UP_DET而产生第一错误检测信号至第n错误检测信号FAIL<1:n>。当第一判断信号JUDGE_H转变为逻辑高电平时,第一压缩电路330可以对第一错误检测信号至第n错误检测信号FAIL<1:n>执行逻辑与运算,以输出第一压缩信号FAIL_H

接下来,可以执行对下行锁存电路的高测试(步骤S820)。同样,不管上行锁存电路的操作如何,都可以根据从下行锁存电路输出的下行检测信号DN_DET而产生第一错误检测信号至第n错误检测信号FAIL<1:n>。当第一判断信号JUDGE_H转变为逻辑高电平时,第一压缩电路330可以对第一错误检测信号至第n错误检测信号FAIL<1:n>执行逻辑与运算,以输出第一压缩信号FAIL_H

接下来,可以执行对上行锁存电路的低测试(步骤S830)。在低测试期间,下拉驱动信号PD_EN可以被激活,并且上行扫描信号UP_SCAN、锁存信号OS_LAT和下行掩蔽信号DN_PASS可以被激活。因此,不管下行锁存电路的操作如何,都可以根据从上行锁存电路输出的上行检测信号UP_DET来产生第一错误检测信号至第n错误检测信号FAIL<1:n>。当第二判断信号JUDGE_L转变为逻辑低电平时,第二压缩电路340可以对第一错误检测信号至第n错误检测信号FAIL<1:n>执行逻辑或运算以输出第二压缩信号FAIL_L

接下来,可以执行对下行锁存电路的低测试(步骤S840)。同样,不管上行锁存电路的操作如何,都可以根据从下行锁存电路输出的下行检测信号DN_DET而产生第一错误检测信号至第n错误检测信号FAIL<1:n>。当第二判断信号JUDGE_L转变为逻辑低电平时,第二压缩电路340可以对第一错误检测信号至第n错误检测信号FAIL<1:n>执行逻辑或运算,以输出第二压缩信号FAIL_L

根据一个实施例,可以根据设计选项来调整测试S810至S840的次序。图5的半导体器件200甚至可以识别错误检测电路中发生缺陷的位置。即,半导体器件200可以识别多个错误检测电路中的哪一个具有缺陷。尽管图9的半导体器件300不可以识别错误检测电路中发生缺陷的位置,但是半导体器件300可以在短的时间段内判断任意的错误检测电路是否具有缺陷。

根据本实施例,半导体器件可以通过检测针对穿通电极的错误检测电路是否正常工作来提高整体芯片制造产率。此外,半导体器件可以通过在层叠芯片/裸片之前检测针对穿通电极的错误检测电路的正常操作来减少/最小化封装/层叠芯片/裸片所花费的不必要的成本和时间。

图10是描述设置在图2所示的基底裸片114上的凸块的平面图。

参考图10,可以在基底裸片114中设置物理区域1142、TSV区域1144和直接访问区域1146。在物理区域1142中,可以设置用于与第一核心裸片112_0至第四核心裸片112_3的第一通道CH0至第八通道CH7接口的通道接口区域IF_CH0至IF_CH7。

用于与控制器120接口的多个PHY凸块PB可以形成在物理区域1142上。用于与穿通电极TSV接口的多个TSV凸块TB可以形成在TSV区域1144上。用于通过插入器130与外部测试设备接口以测试层叠式存储器件110的多个DA凸块DAB可以形成在直接访问区域1146上。PHY凸块PB、TSV凸块TB和DA凸块DAB可以由微型凸块构成。尽管未示出,但是可以在直接访问区域1146上另外形成与DA凸块DAB耦接的多个DA焊盘DAP。DA焊盘DAP的物理尺寸可以相对较大,并且其数量可以比PHY凸块PB和DA凸块DAB少。

如上所述,由于PHY凸块PB的物理尺寸非常小,并且PHY凸块PB的数量非常大且超过1000个,因此事实上难以使用PHY凸块PB来测试层叠式存储器件110。此外,由于层叠式存储器件110以系统级封装(SIP)的形式与控制器120通信,因此更难以使用PHY凸块PB来测试层叠式存储器件110。由于这些原因,可以使用DA凸块DAB或DA焊盘DAP来测试层叠式存储器件110,所述DA凸块DAB或DA焊盘DAP的物理尺寸比PHY凸块PB大而数量比PHY凸块PB少。

图11是描述设置在图2所示的第一核心裸片112_0上的凸块的平面图。作为参考,第二核心裸片112_1至第四核心裸片112_3可以具有与第一核心裸片112_0基本相同的配置。

参考图11,根据本发明的实施例,第一核心芯片112_0可以包括核心区域和外围区域。

在核心区域中,可以设置多个单元阵列区域12,例如,四个单元阵列区域12。四个单元阵列区域12可以设置在第一核心裸片112_0的四个角处,从而在它们之间形成十字形区域(cross-shaped area)。可以将多个存储单元置于每个单元阵列区域12中。例如,如图11所示,在单元阵列区域12之中的下部单元阵列区域12A和12B可以被分配给第一通道CH0,而上部单元阵列区域12C和12D可以被分配给第三通道CH2。此外,在核心区域中,可以设置多个列解码器区域14和多个行解码器区域16。例如,如图11所示,可以在存储单元区域12A与12C之间设置多个列解码器区域14(例如,两个列解码器区域)。另外,可以在存储单元区域12B与12D之间设置多个列解码器区域14(例如,两个列解码器区域)。可以在存储单元区域12D与12C之间设置多个行解码器区域16(例如,两个行解码器区域)。另外,可以在存储单元区域12B与12A之间设置多个行解码器区域16(例如,两个行解码器区域)。可以将与命令/地址控制相关的多个列解码器(未示出)置于列解码器区域14中。列解码器可以通过接收列地址并对其进行解码来选择它们各自的单元阵列区域12的列线(即,位线)。此外,可以将多个写入驱动器(未示出)和多个输入/输出(I/O)感测放大器(未示出)置于列解码器区域14中。可以将与命令/地址控制相关的多个行解码器(未示出)置于行解码器区域16中。行解码器可以通过接收行地址并对其进行解码来选择单元阵列区域12的行线(即,字线)。包括穿通电极TSV的外围区域可以设置在每对行解码器区域16之间。更具体地,外围区域可以包括位于存储单元区域12C与12D之间的一对行解码器区域16之间的第一区域。外围区域可以包括位于存储单元区域12A与12B之间的一对行解码器区域16之间的第二区域。

在外围区域中,可以设置:外围电路(未示出),其用于控制设置在核心区域中的组件;接口电路(未示出),其用于与穿通电极TSV接口;以及穿通电极TSV。具体地,设置有接口电路和穿通电极TSV的区域可以被定义为TSV区域20。第一核心裸片112_0可以经由穿通电极TSV从外部(例如,基底裸片114)接收输入信号,或者经由穿通电极TSV将输出信号发送到外部。根据实施例,从平面的角度来看,TSV区域20可以位于第一核心芯片112_0的中央。然而,本发明的构思和精神不限于此,并且TSV区域20的平面布局可以根据设计选项而进行各种各样地变化。

图12是示出根据本发明实施例的层叠式存储器件100的配置的示图。为了便于解释,图12针对每个裸片示出了一个穿通电极TSV,但是在实践中可以部署多个穿通电极TSV。在图12中,主要示出了与基底裸片114和第一核心裸片112_0至第四核心裸片112_3之间的数据输入/输出操作有关的组件(composition)。

参考图12,层叠式存储器件110可以包括基底裸片114和第一核心裸片112_0至第四核心裸片112_3。第一核心裸片112_0至第四核心裸片112_3和基底裸片114可以经由穿通电极TSV竖直地耦接到衬底以在其间传输信号。

基底裸片114可以包括物理区域、TSV区域和直接访问(DA)区域。在物理区域中,可以设置数据焊盘DQ_uBUMP和第一输入/输出(I/O)缓冲器电路410。在TSV区域中,可以设置双向中继器(B-RPT,bi-directional repeater)430、第二I/O缓冲器电路440以及用于穿透第一核心裸片112_0至第四核心裸片112_3和基底裸片114的穿通电极TSV。在DA区域中,可以设置多个DA凸块DAB。尽管在图12中示出了一个数据焊盘DQ_uBUMP及与其对应的电路,但是,在实践中可以部署多个数据焊盘和与其对应的电路。

数据焊盘DQ_uBUMP可以由用于与控制器(图1的120)接口的微型凸块构成,并且对应于PHY凸块(图10的PB)。第一I/O缓冲器电路410可以接收从控制器120传送来的数据(或信号)并将数据(或信号)输出到控制器120。第一I/O缓冲器电路410可以包括输入缓冲器(或接收器)RX1和输出缓冲器(或输出驱动器或发送器)TX1。在写入操作期间,输入缓冲器RX1可以对经由数据焊盘DQ_uBUMP从控制器120输入的写入数据进行缓冲,以向双向中继器430提供已缓冲的写入数据。在读取操作期间,输出缓冲器TX1可以对从双向中继器430传送来的读取数据进行缓冲,以经由数据焊盘DQ_uBUMP向控制器120输出已缓冲的读取数据。

双向中继器430可以在写入操作期间复制和放大从输入缓冲器RX1提供的写入数据。双向中继器430可以在读取操作期间复制和放大从第二I/O缓冲器电路440传送来的读取数据。第二I/O缓冲器电路440可以接收从穿通电极TSV来传送的数据(或信号)并将数据(或信号)输出到穿通电极TSV。第二I/O缓冲器电路440可以包括输入缓冲器(或接收器)RX2和输出缓冲器(或输出驱动器或发送器)TX2。在写入操作期间,输出缓冲器TX2可以对从双向中继器430传送来的写入数据进行缓冲,以向穿通电极TSV输出已缓冲的写入数据。在读取操作期间,输入缓冲器RX2可以对从穿通电极TSV传送来的读取数据进行缓冲,以向双向中继器430提供已缓冲的读取数据。第二I/O缓冲器电路440可以用作针对穿通电极TSV的接口电路。

由于第一核心裸片112_0至第四核心裸片112_3具有基本相同的配置,因此将以第四核心裸片112_3为例进行说明。第四核心裸片112_3可以包括核心区域和外围区域。在核心区域中,可以设置单元阵列区域(图11的12)中的任意一个。此外,可以将I/O感测放大器(IOSA)532和写入驱动器(WDRV)534置于核心区域中。在外围区域中,可以设置第三I/O缓冲器电路510、读取管道锁存器(RPIPE)522、写入管道锁存器(WPIPE)524以及用于穿透第一核心裸片112_0至第四核心裸片112_3和基底裸片114的穿通电极TSV。在外围区域中,穿通电极TSV和用于与穿通电极TSV接口的第三I/O缓冲器电路510所位于的区域可以被定义为TSV区域。

第三I/O缓冲器电路510可以接收从穿通电极TSV传送来的数据(或信号)并将数据(或信号)输出到穿通电极TSV。第三I/O缓冲器电路510可以包括输入缓冲器(或接收器)RX3和输出缓冲器(或输出驱动器或发送器)TX3。在写入操作期间,输入缓冲器RX3可以对从穿通电极TSV传送来的写入数据进行缓冲,以向写入管道锁存器524提供已缓冲的写入数据。在读取操作期间,输出缓冲器TX3可以对从读取管道锁存器522传送来的读取数据进行缓冲,以向穿通电极TSV输出已缓冲的读取数据。第三I/O缓冲器电路510可以用作针对穿通电极TSV的接口电路。在写入操作期间,写入管道锁存器524可以对齐从输入缓冲器RX3提供的写入数据,以向写入驱动器534提供已对齐的写入数据。在读取操作期间,读取管道锁存器522可以对齐从I/O感测放大器532输出的读取数据,以向输出缓冲器TX3输出已对齐的读取数据。写入驱动器534可以在写入操作期间将写入数据写入到单元阵列区域中。I/O感测放大器532可以在读取操作期间感测并放大从单元阵列区域输出的读取数据。

由于制造过程中的各种因素而被异常地形成的穿通电极TSV的电阻或电容值可以大于与正常形成的穿通电极TSV相对应的电阻或电容值的目标值。此时,即使异常形成的穿通电极TSV通过了为保证穿通电极TSV的物理连接的开/短路测试(open/short test),它们也可能不适用于信号传输。为了测试穿通电极TSV的信号传输状态,需要以下过程:将测试数据写入核心区域的单元阵列区域,读出测试数据,并验证所读出的测试数据是否与目标数据相同。换言之,必须操作附加组件诸如核心区域中的单元阵列区域、I/O感测放大器和写入驱动器以及外围区域中的管道锁存器,以便测试穿通电极TSV的信号传输状态。结果,难以仅对穿通电极TSV的固有特性和工作电流进行确认。

在下文中,将说明除了设置在核心区域中的附加组件之外,通过使用穿通电极TSV和针对穿通电极TSV的接口电路而在晶片级对穿通电极TSV的信号传输状态进行测试的方法。

图13是示出根据本发明实施例的层叠式存储器件110的配置的示图。在图12和图13中,相同的组件被赋予相同的附图标记,并且省略了相关细节。

参考图13,层叠式存储器件110可以包括基底裸片114和第一核心裸片112_0至第四核心裸片112_3。第一核心裸片112_0至第四核心裸片112_3和基底裸片114可以经由穿通电极TSV和参考穿通电极REF_TSV竖直地耦接到衬底以在其间传输信号。

基底裸片114可以包括第一测试电路450。根据在测试操作期间被激活的测试信号TEST_EN,第一测试电路450可以将测试振荡信号TOSC传送到穿通电极TSV中的至少一个(以下被称为“目标穿通电极TSV”)。目标穿通电极TSV可以包括穿通电极TSV之中的在列方向上连接的穿通电极。在测试操作期间,第一测试电路450可以向第二I/O缓冲器电路440的输出缓冲器TX2提供测试振荡信号TOSC。第一测试电路450可以通过将基于测试振荡信号TOSC产生的测试基底信号(test base signal,TBASE,未示出)与经由参考穿通电极REF_TSV传送来的测试核心信号TCORE进行比较而输出测试输出信号TOUT。基底裸片114可以包括物理区域、TSV区域和直接访问(DA)区域。在一个实施例中,第一测试电路450可以设置在基底裸片114的TSV区域中。图13的数据焊盘DQ_uBUMP、第一I/O缓冲器电路410、双向中继器430和第二I/O缓冲器电路440可以与图12的配置基本相同。

另外,用于将测试输出信号TOUT输出到外部设备(例如,测试设备)的测试输出焊盘TPAD_OUT可以设置在基底裸片114中。此外,用于从外部设备接收测试振荡信号TOSC的测试输入焊盘TPAD_IN可以设置在基底裸片114中。测试输出焊盘TPAD_OUT和测试输入焊盘TPAD_IN可以由形成在DA区域上的DA凸块DAB构成。

第一核心裸片112_0至第四核心裸片112_3中的每个可以包括第二测试电路550。第二测试电路550可以根据测试信号TEST_EN而产生与经由目标穿通电极TSV传送来的测试振荡信号TOSC相对应的测试核心信号TCORE,并向参考穿通电极REF_TSV传送所述测试核心信号TCORE。在测试操作期间,第二测试电路550可以接收从第三I/O缓冲器电路510的输入缓冲器RX3提供的测试振荡信号TOSC。第一核心裸片112_0至第四核心裸片112_3中的每一个可以包括核心区域和外围区域。在一个实施例中,第二测试电路550可以被设置在第一核心裸片112_0至第四核心裸片112_3中的每一个的外围区域中。在一个实施例中,第二测试电路550可以被设置在外围区域的TSV区域中。图13的第三I/O缓冲器电路510、读取管道锁存器522、写入管道锁存器524、I/O感测放大器532、写入驱动器534和单元阵列区域可以与图12的配置基本相同。

在启动操作或初始操作期间,可以向第一核心裸片112_0至第四核心裸片112_3中的每一个分配芯片标识(ID)信号。例如,可以向第一核心裸片112_0分配芯片ID信号“00”,可以向第二核心裸片112_1分配芯片ID信号“01”,可以向第三核心裸片112_2分配芯片ID信号“10”,并且可以向第四核心裸片112_3分配芯片ID信号“11”。根据一个实施例,利用这种具有层叠信息的芯片ID信号,可以将测试信号TEST_EN施加到第一核心裸片112_0至第四核心裸片112_3中的对应一个,以便操作第二测试电路550。

在下文中,将说明第一测试电路450和第二测试电路550的详细配置。

图14是示出根据本发明的第一实施例的、图13的层叠式存储器件110的第一测试电路450和第二测试电路550的详图。在图14中,假设第一核心裸片112_0至第四核心裸片112_3之中的核心裸片112_x的第二测试电路550被激活。

参考图14,数据焊盘DQ_uBUMP和第一I/O缓冲器电路410可以被设置在基底裸片114的物理区域中,并且目标穿通电极TSV、参考穿通电极REF_TSV和第二I/O缓冲器电路440可以被设置在基底裸片114的TSV区域中。第一测试电路450可以设置在基底裸片114的TSV区域中。双向中继器430可以被设置在第一I/O缓冲器电路410与第二I/O缓冲器电路440之间的TSV区域中。

第一测试电路450可以包括模式生成器PG、第一计数器CNT1、第一串行器SER1和比较器CMP。

根据测试信号TEST_EN,模式生成器PG可以产生测试振荡信号TOSC,并将所述测试振荡信号TOSC提供给第二I/O缓冲器电路440的输出缓冲器TX2。输出缓冲器TX2可以通过目标穿通电极TSV向核心裸片112_x传送所述测试振荡信号TOSC。测试信号TEST_EN可以在测试操作期间被激活。测试信号TEST_EN可以是具有频率信息(FREQ_INF)的多比特位信号。例如,当测试信号TEST_EN由3比特位的信号TEST_EN<0:2>组成时,最低有效位TEST_EN<0>在测试操作期间可能变为逻辑高电平,而其他两个比特位TEST_EN<1:2>可以根据频率信息(FREQ_INF)而具有“00”、“01”、“10”和“11”之中的任意值。模式生成器PG可以根据测试信号TEST_EN<0:2>中所包括的频率信息(FREQ_INF)来产生以设定的周期进行触发的测试振荡信号TOSC。例如,当测试信号TEST_EN<0:2>可以具有值“101”时,模式生成器PG可以产生以第一频率触发的测试振荡信号TOSC。当测试信号TEST_EN<0:2>可以具有值“110”时,模式生成器PG可以产生以高于第一频率的第二频率触发的测试振荡信号TOSC。当测试信号TEST_EN<0:2>可以具有值“111”时,模式生成器PG可以产生以高于第二频率的第三频率触发的测试振荡信号TOSC。根据一个实施例,测试振荡信号TOSC可以以设定的周期进行触发,或者根据预设模式进行触发。

第一计数器CNT1可以根据测试信号TEST_EN而对测试振荡信号TOSC进行计数以产生基底计数信号BCNT<0:n>。例如,第一计数器CNT1可以响应于最低有效位TEST_EN<0>而被激活,并且对测试振荡信号TOSC的触发次数进行计数。第一串行器SER1可以使基底计数信号BCNT<0:n>串行化,以输出测试基底信号TBASE。比较器CMP可以将测试核心信号TCORE与测试基底信号TBASE进行比较,以输出测试输出信号TOUT。测试核心信号TCORE可以通过参考穿通电极REF_TSV来提供。

此外,第一测试电路450可以包括:第一寄存器REG1,其用于储存从第一计数器CNT1输出的基底计数信号BCNT<0:n>,以向第一串行器SER1提供所储存的基底计数信号BCNT<0:n>。在一个实施例中,第一寄存器REG1可以同步于测试时钟TCLK来储存基底计数信号BCNT<0:n>。

单元阵列区域、I/O感测放大器532和写入驱动器534可以被设置在核心裸片112_x的核心区域中,并且第三I/O缓冲器电路510、读取管道锁存器522、写入管道锁存器524、目标穿通电极TSV和参考穿通电极REF_TSV可以被设置在核心裸片112_x的外围区域中。第二测试电路550可以设置在外围区域的TSV区域中。

第二测试电路550可以包括第二计数器CNT2和第二串行器SER2。

第二计数器CNT2可以根据测试信号TEST_EN而对从第三I/O缓冲器电路510的输入缓冲器RX3传送来的测试振荡信号TOSC进行计数,以产生核心计数信号CCNT<0:n>。例如,第二计数器CNT2可以响应于最低有效位TEST_EN<0>而被激活,并且对测试振荡信号TOSC的触发次数进行计数。第二串行器SER2可以使核心计数信号CCNT<0:n>串行化,以向参考穿通电极REF_TSV输出测试核心信号TCORE。

此外,第二测试电路550可以包括:第二寄存器REG2,其用于储存从第二计数器CNT2输出的核心计数信号CCNT<0:n>,以向第二串行器SER2提供所储存的核心计数信号CCNT<0:n>。在一个实施例中,第二寄存器REG2可以同步于测试时钟TCLK来储存核心计数信号CCNT<0:n>。由于在同步于相同的测试时钟TCLK来储存基底计数信号BCNT<0:n>和核心计数信号CCNT<0:n>之后使它们串行化,因此在核心裸片112_x与基底裸片114之间的信号传输期间发生的偏斜(skew)能够被最小化。

在第一实施例中说明了在基底裸片114内部产生测试振荡信号TOSC的情况。在下文中,将说明从外部测试设备输入或在基底裸片114内部产生测试振荡信号TOSC的情况。

图15是示出根据本发明的第二实施例的、图13的层叠式存储器件110的第一测试电路450和第二测试电路550的详图。在图14和图15中,相同的组件被赋予相同的附图标记,并且省略了相关细节。

参考图15,第一测试电路450可以包括模式生成器PG、多路复用器M1、第一计数器CNT1、第一寄存器REG1、第一串行器SER1和比较器CMP。

模式生成器PG可根据测试信号TEST_EN而产生第一预振荡信号POSC1。测试信号TEST_EN可以在测试操作期间被激活,并且可以是具有频率信息(FREQ_INF)的多比特位信号。模式生成器PG可以根据测试信号TEST_EN中所包括的频率信息(FREQ_INF)来产生以设定的周期触发的第一预振荡信号POSC1。

多路复用器M1可以通过响应于测试选择信号TEST_EN_S而选择第一预振荡信号POSC1和第二预振荡信号POSC2中的一个来向第二I/O缓冲器电路440的输出缓冲器TX2输出测试振荡信号TOSC。输出缓冲器TX2可以通过目标穿通电极TSV向核心裸片112_x传送测试振荡信号TOSC。当从外部测试设备接收到测试振荡信号TOSC时,测试选择信号TEST_EN_S可以被设定为第一逻辑电平(例如,逻辑低电平),而当在基底裸片114内部产生测试振荡信号TOSC时,测试选择信号TEST_EN_S可以被设定为第二逻辑电平(例如,逻辑高电平)。第二预振荡信号POSC2可以通过测试输入焊盘TPAD_IN而从外部测试设备输入。例如,多路复用器M1可以响应于逻辑高电平的测试选择信号TEST_EN_S而选择第一预振荡信号POSC1,并且响应于逻辑低电平的测试选择信号TEST_EN_S而选择第二预振荡信号POSC2。

第一计数器CNT1可以根据测试信号TEST_EN而对第一预振荡信号POSC1或第二预振荡信号POSC2进行计数,以产生基底计数信号BCNT<0:n>。第一寄存器REG1可以同步于测试时钟TCLK来储存基底计数信号BCNT<0:n>。第一串行器SER1可以使第一寄存器REG1中所储存的基底计数信号BCNT<0:n>串行化以输出测试基底信号TBASE。比较器CMP可以将测试核心信号TCORE与测试基底信号TBASE进行比较以输出测试输出信号TOUT。

由于图15的第二测试电路550具有与图14的第二测试电路550基本相同的配置,所以将省略详细的描述。

图16是描述根据本发明的实施例的层叠式存储器件的测试操作的流程图。

参考图16,说明对如图14和图15所示的、包括经由多个穿通电极TSV和至少一个参考穿通电极REF_TSV竖直地层叠到衬底的基底裸片114和第一核心裸片112_0至第四核心裸片112_3的层叠式存储器件110的测试操作。

基底裸片114可以向穿通电极TSV之中的目标穿通电极TSV传送测试振荡信号TOSC,并且基于测试振荡信号TOSC而产生测试基底信号TBASE(在步骤S910处)。更详细地,基底裸片114的第一测试电路450可以根据测试信号TEST_EN中所包括的频率信息(FREQ_INF)来产生以设定的周期触发的测试振荡信号TOSC。可替代地,第一测试电路450可以通过经由测试输入焊盘TPAD_IN从外部测试设备接收第二预振荡信号POSC2来产生测试振荡信号TOSC。第一测试电路450可以通过对测试振荡信号TOSC进行计数以产生基底计数信号BCNT<0:n>、根据测试时钟TCLK来储存基底计数信号BCNT<0:n>以及使所储存的基底计数信号BCNT<0:n>串行化来产生测试基底信号TBASE。作为参考,为了在测试操作期间使层叠的裸片及其穿通电极TSV的负载影响(loading effect)最小化,第一测试电路450可以产生测试振荡信号TOSC,从而以比在正常操作(诸如读取或写入操作)期间传输的正常信号的传输速度低的速度来运行。

核心裸片112_x可以基于经由目标穿通电极TSV传送来的测试振荡信号TOSC而产生测试核心信号TCORE(在步骤S920处)。更详细地,核心裸片112_x的第二测试电路550可以通过对测试振荡信号TOSC进行计数以产生核心计数信号CCNT<0:n>、根据测试时钟TCLK来储存核心计数信号CCNT<0:n>以及使所储存的核心计数信号CCNT<0:n>串行化来产生测试核心信号TCORE。此时,由于基底计数信号BCNT<0:n>和核心计数信号CCNT<0:n>被同时储存,因此在核心裸片112_x与基底裸片114之间的信号传输期间产生的偏斜可以被最小化。

随后,基底裸片114的第一测试电路450可以通过对经由参考穿通电极REF_TSV从核心裸片112_x传送的测试核心信号TCORE与测试基底信号TBASE进行比较来输出测试输出信号TOUT(在步骤S930处)。第一测试电路450可以通过设置在基底裸片114的DA区域中的测试输出焊盘TPAD_OUT来将测试输出信号TOUT输出到外部测试设备(在步骤S940处)。

另一方面,外部测试设备可以改变测试信号TEST_EN的频率信息(FREQ_INF)。例如,测试设备可以依次将3比特位的测试信号TEST_EN<0:2>改变为“100”、“101”、“110”和“111”的顺序。可替代地,测试设备可以通过测试输入焊盘TPAD_IN顺序地提供测试振荡信号TOSC,所述测试振荡信号TOSC以彼此不同的第一频率至第四频率中的任意一种进行触发。基底裸片114的第一测试电路450和核心裸片112_x的第二测试电路550可以利用以不同的频率进行触发的测试振荡信号TOSC来重复上述步骤S910至S930。基于针对每个频率的测试输出信号TOUT,测试设备可以根据信号传输速率来确认目标穿通电极的操作特性。

如上所述,在将层叠式存储器件与控制器封装之前,可以在晶片级执行根据所描述的实施例的层叠式存储器件的测试操作。通过仅使用针对穿通电极的接口电路来测试穿通电极,层叠式存储器件能够在晶片级准确地确定穿通电极的信号传输状态。另外,根据所描述的实施例的层叠存储器件的测试操作可以利用以各种频率进行触发的振荡信号来执行,从而根据信号传输速率来确定穿通电极的操作特性。因此,可以提高信号传输的准确性和效率,并且可以通过在晶片级验证针对正常操作的信号传输来提高整体芯片产率。

在下文中,将说明在不进行计数操作和串行化操作的情况下测试穿通电极TSV的信号传输状态的方法。

图17是根据本发明的第三实施例、示出图13的层叠式存储器件110的第一测试电路450和第二测试电路550的详图。在图14和图17中,相同的组件被赋予相同的附图标记,并且省略了相关细节。

参考图17,第一测试电路450可以包括模式生成器PG、第一计数器CNT1、第一寄存器REG1、第一串行器SER1、比较器CMP和第一多路复用器M2。由于图17的模式生成器PG、第一计数器CNT1、第一寄存器REG1、第一串行器SER1和比较器CMP具有与图14的那些组件基本相同的配置,所以将省略详细的描述。第一多路复用器M2可以通过响应于测试选择信号TEST_EN_S而选择从比较器CMP输出的预测试输出信号TOUT_PRE和从参考穿通电极REF_TSV传送来的测试核心信号TCORE中的一个来输出测试输出信号TOUT。例如,第一多路复用器M2可以响应于逻辑低电平的测试选择信号TEST_EN_S来选择测试核心信号TCORE,而可以响应于逻辑高电平的测试选择信号TEST_EN_S来选择预测试输出信号TOUT_PRE。

第二测试电路550可以包括第二计数器CNT2、第二寄存器REG2、第二串行器SER2和第二多路复用器M3。由于图17的第二计数器CNT2、第二寄存器REG2和第二串行器SER2具有与图14的那些组件基本相同的配置,所以将省略详细描述。第二多路复用器M3可以通过响应于测试选择信号TEST_EN_S而选择从第二串行器SER2输出的预测试核心信号TCORE_PRE和从第三I/O缓冲器电路510的输入缓冲器RX3传送来的测试振荡信号TOSC中的一个来输出测试核心信号TCORE。第二多路复用器M3可以将测试核心信号TCORE输出到参考穿通电极REF_TSV。例如,第二多路复用器M3可以响应于逻辑高电平的测试选择信号TEST_EN_S来选择预测试核心信号TCORE_PRE,而可以响应于逻辑低电平的测试选择信号TEST_EN_S来选择测试振荡信号TOSC。

以下将说明图17的层叠式存储器件110的测试操作。

当测试选择信号TEST_EN_S被设定为逻辑高电平时,层叠式存储器件110的测试操作与图16中所述的S910至S940中的测试操作步骤基本相同。

当测试选择信号TEST_EN_S被设定为逻辑低电平时,在基底裸片114的第一测试电路450中的模式生成器PG可以根据测试信号TEST_EN而产生测试振荡信号TOSC,并可以将其提供给第二I/O缓冲器电路440的输出缓冲器TX2。在核心裸片112_x的第二测试电路550中的第二多路复用器M3可以通过选择测试振荡信号TOSC而将测试核心信号TCORE输出到参考穿通电极REF_TSV。第一多路复用器M2可以通过选择经由参考穿通电极REF_TSV传送来的测试核心信号TCORE来输出测试输出信号TOUT。测试输出信号TOUT可以通过设置在基底裸片114的DA区域中的测试输出焊盘TPAD_OUT而被输出到外部测试设备。

在下文中,将说明利用一个参考穿通电极REF_TSV来测试多个穿通电极TSV的信号传输状态的方法。

图18是示出根据本发明的实施例的层叠式存储器件110的配置的示图。图18仅示出了图13的配置之中的测试层叠式存储器件110所需的配置,并省略了其余配置的描述。

参考图18,基底裸片114可以包括第一测试电路450和第一选择电路460,并且核心裸片112_x可以包括第二测试电路550和第二选择电路560。图18的第一测试电路450和第二测试电路550可以与图14、图15和图17中的任意一种的配置基本相同。

第一测试电路450可以向第一选择电路460提供测试振荡信号TOSC。第一选择电路460可以根据穿通电极选择信号TSV_SEL<0:m-1>来选择第一目标穿通电极TSV1至第m目标穿通电极TSVm中的一个,并可以向与所选择的目标穿通电极耦接的输出缓冲器TX2提供从第一测试电路450提供的测试振荡信号TOSC。

第二选择电路560可以根据穿通电极选择信号TSV_SEL<0:m-1>来选择第一目标穿通电极TSV1至第m目标穿通电极TSVm中的一个,并可以向第二测试电路550提供经由与所选择的目标穿通电极耦接的输入缓冲器RX3传送来的测试振荡信号TOSC。

在图17的层叠式存储器件110的测试操作中,响应于穿通电极选择信号TSV_SEL<0:m-1>的第一比特位TSV_SEL<0>的激活来选择第一目标穿通电极TSV1,并且可以执行如图16所述的步骤S910至S940。此时,随着测试信号TEST_EN的频率信息(FREQ_INF)改变,可以重复步骤S910至S940。基于针对每个频率的测试输出信号TOUT,测试设备可以根据信号传输速率来确认目标穿通电极的操作特性。

随后,随着穿通电极选择信号TSV_SEL<0:m-1>的每个比特位被顺序地激活,可以顺序地选择第二目标穿通电极TSV2至第m目标穿通电极TSVm,并且可以执行步骤S910至S940。类似地,随着测试信号TEST_EN的频率信息(FREQ_INF)改变,重复执行步骤S910至S940使得测试设备可以基于针对每个频率的测试输出信号TOUT而根据信号传输速率来确认目标穿通电极的操作特性。

如上所述,可以通过单个参考穿通电极来监测多个穿通电极的特性。即,通过统一地监测多个穿通电极的特性,能够根据信号传输速率而更准确地确认穿通电极的操作特性。

根据本发明的实施例,层叠式半导体器件可以通过在将层叠式半导体器件与控制器封装之前在晶片级验证穿通电极是否正常运行来提高整体芯片产率。此外,层叠式半导体器件可以通过根据信号传输速率而确认穿通电极的操作特性来提高信号传输的准确性和效率。此外,层叠式半导体器件可以通过仅测试穿通电极及其接口电路来准确地确定穿通电极的信号传输状态。

尽管已经出于说明性目的描述了各种实施例,但是对于本领域技术人员显而易见的是,在不脱离如所附权利要求所限定的本发明的精神和范围的情况下,可以进行各种改变和修改。

例如,以上实施例中示出的逻辑门和晶体管可以根据输入信号的极性而具有不同的位置和类型。

- 层叠式半导体器件及其测试方法

- 半导体器件、层叠式半导体器件和半导体器件的制造方法