半导体结构及其制造方法

文献发布时间:2023-06-19 11:45:49

技术领域

本发明有关于一种半导体结构及其制造方法,且特别是有关于一种具有沟槽隔离件的半导体结构及其制造方法。

背景技术

随着集成电路(IC)的快速发展,为了符合消费者对于小型化电子装置的需求,存储器装置的元件的尺寸缩小,存储器单元的集积度(integration degree)也随之增加。当元件的尺寸缩小而提高积集度时,在各元件之间的隔离结构也必须跟着缩小。因此,隔离元件是否具有良好的隔离效果,也是影响存储器装置的电性的重要因素之一。目前,浅沟槽隔离(shallow trench isolation;STI)技术已广泛地被应用在次微米(sub micron)或更小的集成电路制造工艺上。再者,位于隔离结构两侧的主动区上则形成存储器装置所需的元件。

然而,在目前的制造工艺中,隔离结构可能因制造工艺步骤造成损伤而有所耗损,致使隔离结构的表面不平坦、或是难以控制隔离结构的顶面与主动区的顶面之间的高度差。因此,以目前制造工艺所形成的隔离结构在隔离效果上仍不尽理想,使得在隔离结构两侧的主动区上形成的元件可能会有漏电流、或是写入速率低等问题,进而影响制得的存储器装置的电性表现。上述这些问题皆降低了最终产品的成品率及可靠度。

因此,虽然现存的半导体结构中其隔离结构及其制造方法可以应付它们原先预定的用途,但目前它们在结构和制法上仍有需要克服的问题。如何改良电阻式随机存取存储器结构,以避免上述情形的发生,对于本领域技术人员而言实为一重要议题。

发明内容

本发明的一些实施例揭示一种半导体结构,包括一衬底,具有一沟槽(trench)。一氧化层共形地(conformally)位于沟槽中。一保护层位于沟槽中,且保护层共形地位于氧化层上。一绝缘材料层填充于沟槽中,且绝缘材料层位于保护层的上方。其中,绝缘材料层的顶面高于保护层的顶面。另外,一些实施例的半导体结构还包括一氮化层位于沟槽中且共形地位于保护层上,且绝缘材料层位于氮化层上,其中氮化层的顶面与绝缘材料层的顶面共平面。

本发明的一些实施例揭示一种半导体结构的制造方法,包括:提供一衬底,此衬底具有沟槽。在衬底上依序形成一氧化层和一保护层,且氧化层和保护层顺应性地形成于沟槽中,并于沟槽中形成一开口。在保护层的上方形成一牺牲材料,且此牺牲材料填入开口。移除部分的牺牲材料,并暴露出保护层的顶面。移除留下的牺牲材料,以暴露出开口。在开口中形成一绝缘材料层,以及移除部分的保护层以暴露出氧化层的顶面,其中绝缘材料层的顶面高于保护层的顶面。

附图说明

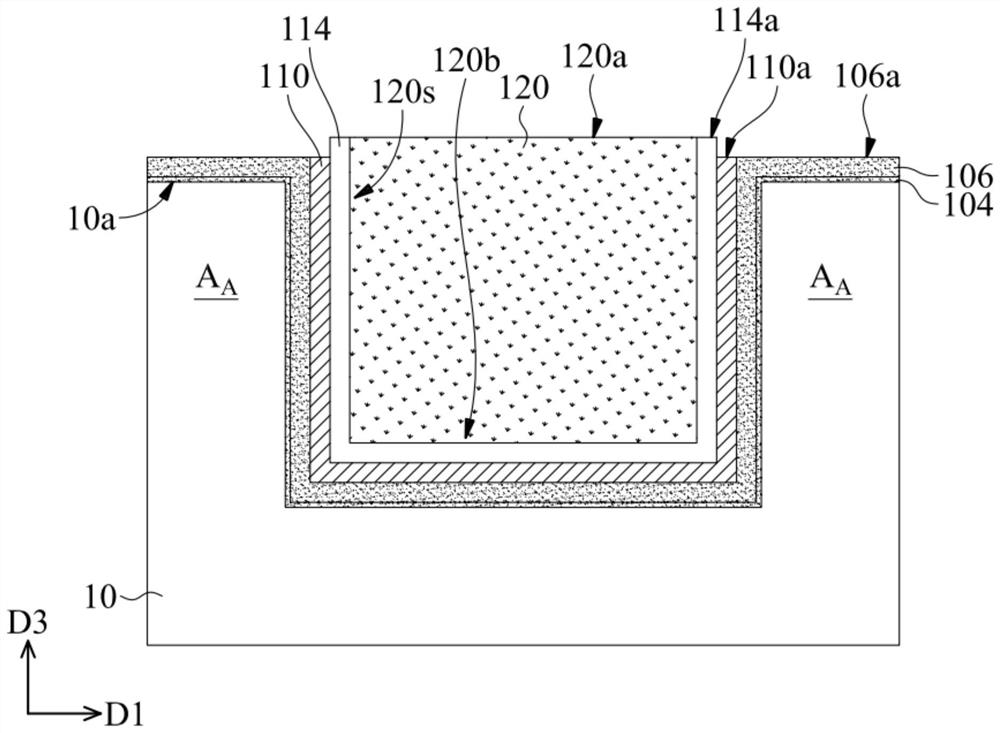

图1A至图12为根据本发明的一些实施例的制造半导体结构的各步骤中所对应的剖面示意图。其中,图1A、图8A、图9A、图10A、图11A以及图12A分别对应图1B、图8B、图9B、图10B、图11B以及图12B中的剖面线2-2所绘制;

图13为根据本发明的一些实施例的半导体结构的剖面示意图。

符号说明

10~衬底; 102~沟槽; 104~第一氧化层;

106~第二氧化层; 110~保护层; 112~开口;

114~氮化层; 116~原生氧化物; 118~牺牲材料;

120~绝缘材料层; AA~主动区; 120s~侧壁;

10a、106a、110a、114a、116a、118a、120a~顶面;

120b~底面; D1~第一方向; D2~第二方向;

D3~第三方向; T1~厚度; H1~高度差。

具体实施方式

以下参照本发明实施例的图式以更全面地阐述本发明。然而,本发明亦可以各种不同的形式体现,而不应限于本文中所述的实施例。为了清楚起见,图式中的层与区域的厚度可能会放大,或者调整特征之间的尺寸比例。相同或相似的元件标号表示相同或相似的元件,以下段落将不再一一赘述。

本发明实施例提供一种半导体结构及其制造方法,所形成的半导体结构是一种具有沟槽隔离件(trench isolation components)的基板结构。实施例中,基板结构的衬底具有沟槽,且沟槽中共形地具有一氧化层,通过在氧化层上共形地形成一保护层以及相关制造工艺步骤,经由保护层的厚度可以控制沟槽隔离件与沟槽外的氧化层的顶面之间的高度差(step height),而解决传统制造工艺中沟槽隔离件的氧化物损耗而造成高度难以控制的问题,进而提升后续在基板结构上形成的元件的电性以及操作表现。

另外,文中实施例所提出的半导体结构例如是位于一半导体装置的周边区域(peripheral region),并在上视图中简绘四个主动区(active area)A

为简化图式以利清楚说明,图1A至图12是绘制关于一半导体装置的周边区域中,于两相邻主动区之间的一个沟槽隔离件的半导体结构的制造方法。

请同时参照图1A和图1B,提供一衬底10。一些实施例中,衬底10包含多个沟槽102以及分别以沟槽102隔开的多个主动区A

于提供衬底10之后,进行一氧化制造工艺,以于衬底10的表面上形成第一氧化层104。如图1A所示,第一氧化层104顺应性的形成于沟槽102的侧壁和底部以及沟槽102之外的衬底10的顶面10a上。因此,第一氧化层104的剖面轮廓对应且相同于包含沟槽102的衬底10的剖面轮廓。在一些实施例中,氧化制造工艺可包括热氧化制造工艺,用以氧化衬底10。在此实施例中,衬底10的材料为硅,且第一氧化层104的材料为氧化硅。

请参照图2,在衬底10上方顺应性的形成第二氧化层106。第一氧化层104的形成可以消除衬底10表面的损伤和缺陷,使后续沉积出高品质的第二氧化层106。再者,前述氧化层更延伸并覆盖衬底10的顶面10a,以覆盖衬底10的顶面10a,因而在沟槽102之外的衬底10的顶面10a上方可定义出氧化层的顶面106a,如图2所示。

在一些实施例中,第二氧化层106为氧化硅,且可利用原子层沉积法(AtomicLayer Deposition,ALD)形成。在一些实施例中,第二氧化层106的厚度约在6nm至10nm之间。

根据本发明的一些实施例,在形成氧化层之后,于氧化层上先形成一保护层。保护层的设置可以控制后续形成的沟槽隔离件与沟槽外的氧化层的顶面之间的高度差。说明如下。

请参照图3,在一些实施例中,于第二氧化层106上顺应性的形成一保护层110。保护层110具有厚度T1。在一些实施例中,保护层110包括一多晶硅层,其可利用化学气相沉积法(chemical vapor deposition,CVD)或是其他适合的沉积方式而形成。在一些实施例中,保护层110的厚度约在20nm至30nm之间。

请参照图4,在一些实施例中,于保护层110上顺应性的形成一氮化层114,并在沟槽102中形成凹陷的开口。在一些实施例中,氮化层114为氮化硅,其可利用化学气相沉积法(CVD)形成。在一些实施例中,氮化层114的厚度约在20nm至30nm之间。

请参照图5,一些实施例中,在形成氮化层114后,在氮化层114上迅速生成共形的一原生氧化物116(native oxide)。

在此示例中,于开口112处填充适当的绝缘材料之前,先填充一牺牲材料于开口112处并搭配相关制造工艺,以定义出后续结构中邻接于沟槽隔离件的氮化层114的顶面高度。说明如下。

请同时参照图6,在氮化层114的上方形成一牺牲材料118,且牺牲材料118填入开口112。如在此示例中,形成于氮化层114上方的牺牲材料118直接接触原生氧化物116。在一些实施例中,可利用旋涂(spin-on)的沉积方式在氮化层114上形成牺牲材料118。牺牲材料118例如是旋涂碳(spin-on-carbon,SOC),或是其他合适的材料。在半导体制造工艺中可做为硬质遮罩的旋涂碳具有良好的间隙填充特性,可填满开口112。

接着,请参照图7,可利用回刻蚀(etching back)步骤,以移除部分的牺牲材料118,暴露出原生氧化物116的顶面116a。如图7所示,利用回刻蚀而移除位于衬底10的顶面10a的上方以及位于开口112上方的部分的牺牲材料118。在一些实施例中,于此回刻蚀步骤后,暴露出的原生氧化物116的顶面116a与留下的牺牲材料118的顶面118a大致上共平面。

请同时参照图8A和图8B,移除部分的原生氧化物116及部分的氮化层114,以暴露出保护层110的顶面110a。在一些实施例中,先利用刻蚀方式移除部分的原生氧化物116,以暴露出位于衬底10的顶面10a的上方的氮化层114的顶面114a,再移除位于衬底10的顶面10a的上方的氮化层114,以暴露出保护层110的顶面110a。在一些实施例中,氮化层114例如是利用回刻蚀步骤移除。在一示例中,例如是以氢氟酸溶液去除部分的原生氧化物116,例如是以热磷酸去除部分的氮化层114。

另外,在一些实施例中,在移除部分的氮化层114后,可再移除高于氮化层114的顶面114a的原生氧化物116,使氮化层114的顶面114a与原生氧化物116的顶面116a大致等高。如图8A所示,刻蚀步骤后,原生氧化物116的顶面116a、氮化层114的顶面114a及保护层110的顶面110a大致上共平面。

接着,请同时参照图9A和图9B,移除留下的牺牲材料118,以暴露出开口112。在一些实施例中,可利用灰化(ashing)方式去除开口112中的牺牲材料118。

另外,如图9B所示,此时所形成的氮化层114自上视观之,是环绕于主动区A

之后,请同时参照图10A和图10B,在保护层110上形成一绝缘材料层120,且绝缘材料层120填入开口112。在一些实施例中,绝缘材料层120例如是介电常数小于4的低介电常数介电材料(low-k dielectric material)。在一示例中,绝缘材料层120为旋涂玻璃(spin-on-glass,SOG)。旋涂玻璃的介电常数小于3.5,且具有良好的间隙填充特性及阶梯覆盖能力,可填满开口112。在一些实施例中,可利用旋涂或其他合适的沉积方式形成绝缘材料层120,其形成方式视选择的实际绝缘材料而定。

接着,请同时参照图11A和图11B,在一些实施例中,移除部分的绝缘材料层120,以暴露出保护层110的顶面110a,而留下的绝缘材料层120填满开口112。在一些实施例中,可利用化学机械抛光(CMP)制造工艺移除位于衬底10的顶面10a的上方以及位于开口112上方的部分的绝缘材料层120,其中化学机械抛光制造工艺是抛光至暴露出保护层110的顶面110a为止。因此,在此实施例的制造工艺中,保护层110可作为一停止层,以定义出开口112中的绝缘材料层120的顶面120a。如图11A所示,移除步骤之后,绝缘材料层120的顶面120a、原生氧化物116的顶面116a、氮化层114的顶面114a及保护层110的顶面110a大致上共平面。

另外,如图11B所示,位于两主动区A

然后,请同时参照图12A和图12B,移除部分的保护层110,以暴露出第二氧化层106的顶面。在一实施例中,可利用回刻蚀步骤移除部分的保护层110。至此,完成具有沟槽隔离件的半导体结构的制作。

如图12A所示,根据一些实施例的制造方法所制得的半导体结构中,衬底10处沿着第三方向D3向下延伸的沟槽隔离件至少由沟槽侧壁的氧化层(包括第一氧化层104和第二氧化层106)、保护层110、氮化层114和绝缘材料层120所构成。

再者,在一些实施例中,进行此移除步骤后,保护层110与第二氧化层106的高度相同,而在开口112中的绝缘材料层120与氮化层114的高度相同,如图12A所示。值得注意的是,绝缘材料层120的顶面120a与氮化层114顶面114a高于保护层110的顶面110a与第二氧化层106的顶面106a。

另外,请同时参照图11B和图12B。如图12B所示,自上视观之,第二氧化层106的顶面106a更暴露于对应主动区A

根据上述实施例,是在具有沟槽102的衬底10上顺应性的形成氧化层和保护层110,之后再进行后续相关制造工艺步骤,例如形成氮化层114和绝缘材料层120于沟槽102的开口112中。通过保护层的设置,可以良好控制后续形成的沟槽隔离件与沟槽外的氧化层的顶面之间的一高度差。例如上述示例,绝缘材料层120的顶面120a与第二氧化层106的顶面106a之间的高度差H1与保护层110的厚度T1相等。再者,根据上述实施例的制法,不会损耗绝缘材料层120,因此可以制得具有轮廓完整且顶面平坦的沟槽隔离件的一种半导体结构,进而提升后续在半导体结构上所形成的元件的电性表现。

在上述实施例中,移除留下的牺牲材料118之后,是将绝缘材料层120填入开口112中(图9A至图10A),使绝缘材料层120直接与原生氧化物116接触。然而,本发明并不以此步骤为限。在一些其他实施例中,在氮化层114上所生成的原生氧化物116可以在形成牺牲材料118之前就先去除,或者在去除牺牲材料118之后及绝缘材料层120填入开口112之前进行去除。

以下系示例说明本发明的一些其他实施例中,于移除开口112中的牺牲材料118后,先去除原生氧化物116,再进行后续绝缘材料层120的制作,以及此方法所制得的结构。

图13为根据本发明的一些实施例的半导体结构的剖面示意图。在形成如图13所示的结构之前,请先参照图1A、图2至图7、图8A、图9A的制造工艺步骤及上述实施例的说明。而在这些图式中,相同于前述实施例中的构件则沿用相同的标号,且其材料与制法可参照上述,在此不赘述。

如图8A、图9A所示,移除开口112中的牺牲材料118,以暴露出开口112内的原生氧化物116。之后,先移除原生氧化物116(例如利用氢氟酸溶液),以暴露出开口112中的氮化层114。

在去除原生氧化物116后,随即于保护层110上形成一绝缘材料层120,且绝缘材料层120填入开口112。绝缘材料层120直接接触保护层110的顶面110a及氮化层114。在一些实施例中,可利用旋涂的沉积方式形成绝缘材料层120,以填满开口112。绝缘材料层120例如是旋涂玻璃(spin-on-glass,SOG),或是其他合适的材料。

接着,例如利用化学机械抛光制造工艺移除部分的绝缘材料层120,以暴露出保护层110的顶面110a,而留下的绝缘材料层120填满开口112。因此,保护层110在此实施例的制造工艺中可作为一停止层。于此步骤中,绝缘材料层120的顶面120a、氮化层114的顶面114a及保护层110的顶面110a大致上共平面。

之后,如图13所示,移除部分的保护层110(例如利用回刻蚀),以暴露出第二氧化层106的顶面106a。

如图13所示,根据此实施例所制得的半导体结构中,衬底10处沿着第三方向D3向下延伸的沟槽隔离件至少由沟槽侧壁的氧化层(包括第一氧化层104和第二氧化层106)、保护层110、氮化层114和绝缘材料层120所构成,其中绝缘材料层120的顶面120a与氮化层114顶面114a大致上共平面,且高于保护层110的顶面110a。相较于如图12A所示的半导体结构中于氮化层114和绝缘材料层120之间存在原生氧化物116,如图13所示的半导体结构的氮化层114直接接触并包覆绝缘材料层120的侧壁120s与底面120b。

值得注意的是,原生氧化物116的去除方式除了如上述所示例的方式,还可以在形成牺牲材料118之前就先去除。例如在一些其他的实施例中,生成原生氧化物116后(如图5所示),移除原生氧化物116,且随即将牺牲材料填入开口112中,再进行后续制造工艺(例如移除部分的牺牲材料118以暴露出氮化层114的顶面114a、移除部分的氮化层114以暴露出保护层110的顶面110a、以绝缘材料层120置换开口112中的牺牲材料118、移除部分的保护层110以暴露出氧化层的顶面)。而最终形成的具有沟槽隔离件的半导体结构与上述如图13所示的半导体结构相同,在此不赘述。

综合上述,根据本发明实施例的制造方法,是在具有沟槽102的衬底10上形成氧化层之后,先顺应性的形成一保护层110于氧化层上(例如上述的第二氧化层106),再进行后续相关制造工艺步骤。通过保护层的设置可以控制后续形成的沟槽隔离件与沟槽外的氧化层的顶面之间的高度差。在一些实施例中,绝缘材料层120的顶面120a与第二氧化层106的顶面106a之间的高度差(step height)H1是与保护层110的厚度T1相等。因此,可根据实际制造工艺或应用所需的沟槽隔离件与氧化层的顶面之间的高度差H1,选择适当的保护层厚度和应用上述实施例所揭示的制法,而完成如上述实施例所提出的半导体结构。

再者,由于本发明的一些实施例中是在氧化层和氮化层114之间设置保护层110,并且利用牺牲材料118先定义出氮化层114的顶面高度,再将开口112处的牺牲材料118置换为绝缘材料层120后,移除部分的保护层110以暴露出氧化层的顶面。其中,移除部分的保护层110时并不会损耗绝缘材料层120。因此,根据本发明的实施例所提出的半导体结构的制造方法,可制得一种具有良好廓形的半导体结构,例如具有轮廓完整且有平坦顶面的沟槽隔离件的一种基板结构。因此,根据本发明的实施例所提出的半导体结构及其制造方法,可以解决传统制造工艺中因沟槽隔离件有所损耗而造成高度难以控制的问题,提高制得基板结构的成品率,进而提升后续在基板结构上所形成的元件的电性表现。

虽然本发明已以多个较佳实施例揭露如上,然其并非用以限定本发明,任何所属技术领域中技术人员在不脱离本发明的精神和范围内,当可作任意的更动与润饰,因此本发明的保护范围当视权利要求范围所界定者为准。

- 氮化物半导体结构、氮化物半导体发光元件、氮化物半导体晶体管元件、氮化物半导体结构的制造方法以及氮化物半导体元件的制造方法

- 用于制造腔结构、制造用于半导体结构的腔结构的方法和使用该方法制造的半导体传声器