半导体装置及其形成方法

文献发布时间:2023-06-19 11:49:09

技术领域

本发明实施例涉及半导体装置及其形成方法,特别是涉及能够提升集成密度的半导体装置及其形成方法。

背景技术

半导体装置用于各种电子应用,诸如:举例而言个人电脑、移动电话、数码相机及其他电子设备。通常通过在半导体基板之上按顺序地沉积绝缘或介电层、导电层及半导体层的材料,并使用微影使各种材料层图案化,以形成电路组件及元件在半导体基板上而制造出半导体装置。

半导体产业通过不断地缩减最小部件(feature)的尺寸,而持续改善了各种电子组件(例如:晶体管、二极管、电阻器、电容器等)的集成密度,这使得更多的组件可以被整合至指定的面积内。然而,随着最小部件的尺寸缩减,需要解决其所衍生出的其他问题。

发明内容

一实施例是关于一种形成方法。所述形成方法包括:形成鳍片于半导体基板之上。沉积虚设栅极材料层于鳍片之上。通过使虚设栅极材料层图案化,来形成虚设栅极电极的顶部。沿着虚设栅极电极的顶部的侧壁形成顶部间隔物。通过蚀刻穿过虚设栅极材料层且穿过鳍片的开口,形成虚设栅极电极的底部。沿着开口的侧壁形成底部间隔物。形成源极/漏极区域在开口中。移除虚设栅极电极。沉积栅极堆叠物于鳍片之上。

另一实施例是关于一种形成方法。所述形成方法包括:形成鳍片于半导体基板之上。沉积虚设栅极材料层于鳍片之上。蚀刻虚设栅极材料层至第一深度。在蚀刻虚设栅极材料层之后,沉积第一间隔物于虚设栅极材料层之上。在沉积第一间隔物之后,蚀刻穿过虚设栅极材料层的开口,以形成虚设栅极电极。沉积第二间隔物于第一间隔物之上且沿着开口的侧壁。形成源极/漏极区域于开口中,第二间隔物使虚设栅极电极与源极/漏极区域分离(separating。移除虚设栅极电极。沉积栅极堆叠物于鳍片之上。

又另一实施例是关于一种半导体装置。所述半导体装置包括鳍片、栅极电极堆叠物、第一顶部间隔物、第一底部间隔物及第一源极/漏极区域。鳍片位于基板之上。栅极电极堆叠物位于鳍片之上。第一顶部间隔物相邻于栅极电极堆叠物。第一底部间隔物位于第一顶部间隔物之下。第一源极/漏极区域相邻于鳍片且通过第一底部间隔物与栅极电极堆叠物独立(isolated)。

附图说明

根据以下的详细说明并配合所附图式阅读,能够最好的理解本公开的所有态样。应注意的是,根据本产业的标准作业,各种部件并未必按照比例绘制。事实上,可能任意的放大或缩小各种部件的尺寸,以做清楚的说明。

图1A是根据一些实施例,描绘半导体装置的透视图;

图1B、图1C、图2A、图2B、图3A及图3B是根据一些实施例,描绘在形成半导体装置的中间步骤中,形成在基板中的鳍片、形成在介于鳍片之间的隔离区域以及形成在鳍片之上的虚设栅极电极的剖面图。

图4A至图4C是根据一些实施例,描绘形成穿过虚设栅极材料的剩余部分且穿过鳍片的开口。

图5A至图5C是根据一些实施例,描绘执行蚀刻拉回(pull-back)制程以使虚设栅极电极的底部凹入。

图6A、图6B、图7A、图7B、图8A、图8B、图8C及图8D是根据一些实施例,描绘在虚设栅极电极的凹部中形成底部间隔物以及在穿过鳍片的开口中形成源极/漏极区域。

图9A至图9E是根据一些实施例,描绘移除虚设栅极电极以及形成取代虚设栅极电极的栅极电极堆叠物。

图10A、图10B、图11A及图11B是根据一些其他实施例,描绘使顶部间隔物凹入及/或使底部间隔物凹入,且进一步描绘形成栅极电极堆叠物。

图12A、图12B、图13A、图13B、图14A、图14B、图15A、图15B、图16A及图16B是根据又一些其他实施例,描绘顶部间隔物及底部间隔物。

其中,附图标记说明如下:

100:半导体装置

101:基板

111:隔离区域

113:鳍片

115:虚设栅极介电质

117:虚设栅极电极

119:第一虚设栅极材料

121:第二虚设栅极材料

123:栅极遮罩

125:复合虚设栅极材料层

201:开口

203:顶部

301:顶部间隔物

401:底部

601:底部间隔物

801:源极/漏极区域

901:层间介电层

903:栅极堆叠物

905:第一部分

907:第二部分

909:间隔物界面

1301:第一介电膜

1303:第二介电膜

1401:第三介电膜

1501:第一介电层

1503:第二介电层

1601:第三介电层

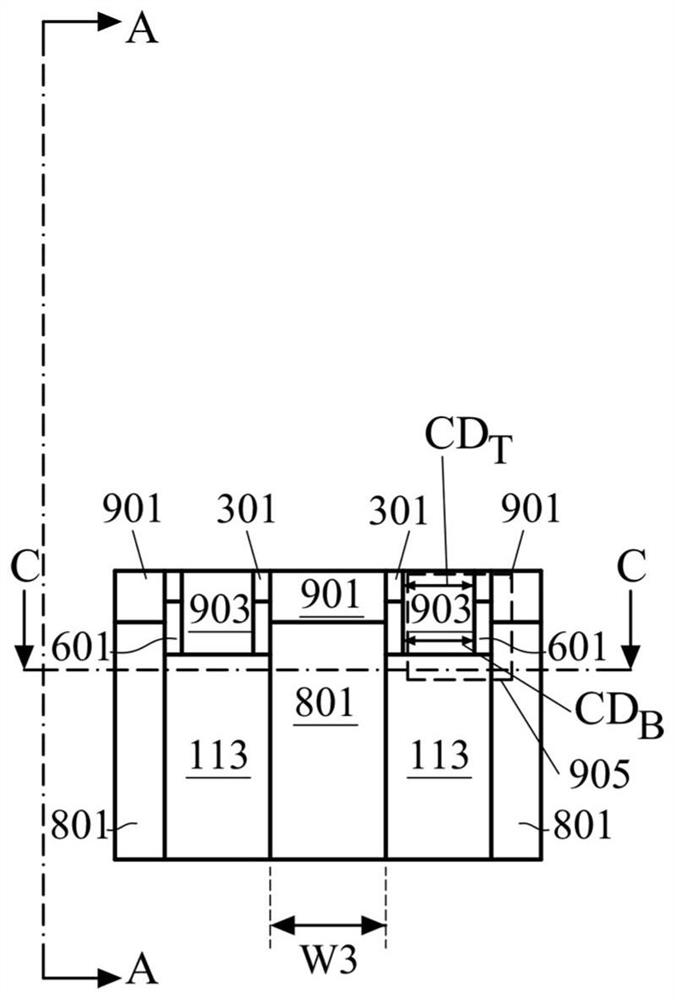

CDT:顶部临界尺寸

CDB:底部临界尺寸

D1:第一深度

D2:第二深度

D3:第三深度

Dist1:第一距离

Dist2:第二距离

Dist3:第三距离

H1:第一高度

H2:第二高度

Th1:第一厚度

Th2:第二厚度

Th3:第三厚度

Th4:第四厚度

Th5:第五厚度

Th6:第六厚度

Th7:第七厚度

Th8:第八厚度

Th9:第九厚度

Th10:第十厚度

Th11:第十一厚度

Th12:第十二厚度

Th13:第十三厚度

W1:第一宽度

W2:第二宽度

W3:第三宽度

θ’:第一角度

具体实施方式

以下的公开内容提供许多不同的实施例或范例,以实施本公开的不同部件(features)。以下叙述组件及排列方式的特定范例,以简化本公开。当然,这些特定的范例仅为示例,而非用以限定。举例而言,若是本公开书叙述了将一第一部件形成于一第二部件之上(over)或上(on),即表示其可能包括上述第一部件与上述第二部件是直接接触(indirect contact)的实施例,且亦可能包括了将其他部件形成于上述第一部件与上述第二部件之间,而使上述第一部件与第二部件可能未直接接触的实施例。另外,本公开不同范例可能重复使用相同的元件符号及/或标记。这些重复是为了简化与清晰的目的,并非用以限定所讨论的不同实施例及/或配置之间有特定的关系。

再者,在本文中所用的空间相关用词,诸如“在…下方(beneath)”、“之下(below)”、“较低的(lower)”、“上方(above)”、“较高的(upper)”及类似的用词,是为了便于描述图式中一个元件(element)或部件与另一个(些)元件或部件之间的关系。除了在图式中绘示的方位外,这些空间相关用词意欲包括使用中或操作中的装置的不同方位。设备可能被转向不同方位(旋转90度或其他方位),则在本文中使用的空间相关用词也可依此相同解释。

现在参照图1A,显示半导体装置100的形成的透视图,半导体装置100具有至少部分地形成在基板101之上的鳍式场效晶体管(fin field effect transistor,FinFET)107。半导体装置100可以位于核心(core)区域或输入/输出(input/output,I/O)区域中,且可以包括逻辑装置、存储器装置、其组合或其类似物的一部分,前述逻辑装置、存储器装置、其组合或其类似物用于执行半导体装置100的所需功能,或者用于传输且接收半导体装置100输入及输出的信号。然而,可以利用任何合适的区域及任何合适的功能。

基板101可以是硅(silicon)基板,但是也可以使用其他基板,诸如绝缘层上覆半导体(semiconductor-on-insulator,SOI)、应变的绝缘层上覆半导体(strained SOI)及绝缘层上覆硅锗(silicon germanium on insulator)。基板101可以是p型半导体,尽管在其他实施例中,基板101可以是n型半导体。

在其他实施例中,可以选择基板101为将特定地提高(boost)由基板101形成的装置的性能(例如,提高载子迁移率)的材料。举例而言,在一些实施例中,可以选择基板101的材料为外延生长的半导体材料层,诸如外延生长的硅锗,前述外延生长的硅锗有助于提高由外延生长的硅锗形成的装置的一些性能测量。然而,使用这些材料可能能够提高装置的一些性能特性的同时,使用这些相同的材料可能会影响装置的其他性能特性。

在半导体装置100的核心区域及/或I/O区域内,形成多个鳍式场效晶体管(FinFET)107,为清楚起见,在图1A中仅显示一个这样的装置。在形成在核心区域中的装置中,可以实施较少的鳍片以形成相应的晶体管,且介于邻近栅极之间的间隔(spacing)(因此,居间的(intervening)源极/漏极区域的宽度)可以小于其他区域(例如,I/O区域)。

可以在最终形成隔离区域111中,移除基板101的一部分作为初始步骤。可以使用遮罩层(图1A中未单独显示)以及合适的蚀刻制程移除基板101的一部分。举例而言,遮罩层可以是包括通过诸如化学气相沉积(chemical vapor deposition,CVD)的制程形成的氮化硅(silicon nitride)的硬遮罩,尽管可以使用其他材料,诸如氧化物(oxides)、氧氮化物(oxynitrides)、碳化硅(silicon carbide)、其组合或其类似物以及其他制程,诸如等离子体辅助化学气相沉积(plasma enhanced chemical vapor deposition,PECVD)、低压化学气相沉积(low pressure chemical vapor deposition,LPCVD)或甚至形成氧化硅然后执行氮化制程(nitridation)的方法。一旦经形成,就可以通过合适的光微影(photolithographic)制程对遮罩层进行图案化,以暴露将被移除的基板101的那些部分。

然而,如所属技术领域中具有通常知识者将认识到的是,前述用于形成遮罩层的制程及材料并不是可用于保护基板101的一部分并同时暴露基板101的其他部分的唯一方法。可以使用任何合适制程,诸如经图案化且经显影的光阻剂,以暴露基板101的要被移除的一部分。所有这样的方法完全旨在包括在本实施例的范围内。

一旦已经形成并图案化遮罩层,可以移除基板101的一部分。尽管可以使用任何合适的制程,可以通过诸如反应性离子蚀刻(reactive ion etching,RIE)的合适制程,来移除经暴露的基板101,以移除基板101的一部分。在一实施例中,可以移除基板101的一部分至第一深度,前述第一深度是从基板101的表面小于大约

然而,如所属技术领域中具有通常知识者将认识到的是,前述制程仅仅是一个潜在的制程,并且并不意味着是唯一的实施例。而是,可以利用通过其可以移除基板101的一部分的任何合适的制程,并且可以使用包括任何数量的遮罩及移除步骤的任何合适的制程。

另外,遮罩及蚀刻制程附加地(additionally)从基板101留下的那些未移除的部分形成鳍片113。为方便起见,鳍片113在图式中显示为与基板101分离(separated),尽管分离的物理指示(physical indication)可以存在或不存在。如下所述,这些鳍片113可用于形成多栅极FinFET晶体管(multiple-gate FinFET transistors)的通道区域。尽管图1A仅显示由基板101形成的鳍片113之一者,但是可以使用任何数量的鳍片113。

可以形成鳍片113,使得鳍片113在基板101的表面处(at)具有在介于大约5nm与大约80nm之间的宽度。此外,尽管已经描述形成鳍片113的特定制程,但是可以通过任何合适的方法使鳍片113图案化。举例而言,可以使用一或多种光微影制程来使鳍片113图案化,前述光微影制程包括双重图案化(double-patterning)或多重图案化(multi-patterning)制程。一般而言,双重图案化或多重图案化制程与光微影及自对准(self-aligned)制程结合,从而允许创造具有举例而言,间距(pitches)小于使用单一且直接的光微影法可获得的其他间距的图案。举例而言,在一实施例中,形成牺牲层在基板之上,并使用光微影制程使牺牲层图案化。使用自对准制程在经图案化的牺牲层旁边(alongside)形成间隔物。然后移除牺牲层,然后可以使用剩余的间隔物来使鳍片113图案化。

一旦已经形成鳍片113,可以沉积介电材料且可以使介电材料凹入(recessed)以形成隔离区域111。介电材料可以是氧化物材料、高密度等离子体(high-density plasma,HDP)氧化物或其类似物。在可选择的(optional)清洗(cleaning)及形成衬层(lining)的步骤之后,可以使用化学气相沉积(CVD)方法(例如,高深宽比(high-aspect ratio process,HARP)制程)、高密度等离子体CVD(high density plasma CVD)方法、或本领域已知的其他合适的形成方法来形成介电材料。

沉积制程可以填充(fill)或过度填充(overfill)鳍片113周围的区域,然后可以通过诸如化学机械抛光(chemical mechanical polishing,CMP)、蚀刻、其组合或其类似物的合适的制程,从鳍片113之上移除过量的材料。在一实施例中,移除制程亦移除位于鳍片113之上的任何介电材料,使得介电材料的移除制程将使鳍片113的表面暴露于进一步的制程步骤。

一旦经平坦化,然后可以使介电材料远离(away from)鳍片113的表面凹入。可以执行凹入,以暴露与鳍片113的顶表面相邻的鳍片113的侧壁的至少一部分。可以通过将鳍片113的顶表面浸入至(dipping into)诸如HF的蚀刻剂中,而使用湿式蚀刻使介电材料凹入,但是可以使用诸如H

然而,如所属技术领域中具有通常知识者将认识到的是,前述步骤可能仅是用于填充介电材料及使介电材料凹入的整个制程流程的一部分。举例而言,也可以使用形成衬层的步骤、清洗步骤、退火步骤、间隙填充(gap filling)步骤、其组合或其类似物。所有潜在的制程步骤完全旨在包括在本实施例的范围内。

在已经形成隔离区域111之后,可以在每个鳍片113之上形成虚设栅极介电质115及虚设栅极电极117。在一实施例中,虚设栅极介电质115可以通过热氧化、化学气相沉积、溅射(sputtering)或本领域中已知且用于形成栅极介电质的任何其他方法来形成。取决于形成栅极介电质的技术,在鳍片113的顶部上的虚设栅极介电质115的厚度可以与在鳍片113的侧壁上的栅极介电质的厚度不同。

虚设栅极介电质115可以包括诸如二氧化硅(silicon dioxide)或氮氧化硅的材料,其厚度范围从介于大约

根据一些实施例,在形成虚设栅极介电质115之前,可以形成栅极氧化物(例如,氧化物衬层)在鳍片113之上。如上所述,一旦已经形成栅极氧化物,则可以形成虚设栅极介电质115在鳍片113及栅极氧化物之上,且可以使虚设栅极介电质115图案化。

虚设栅极电极117可以包括导电材料或非导电材料,且可以是硅基(silicon-based)的材料,诸如硅、SiGe、SiN、SiC、SiON、其组合或其类似物,但是可以使用诸如多晶硅的任何合适的材料。根据一些实施例,可以使用复合(complex)虚设栅极材料层125(例如,参照图1B及图1C)来形成虚设栅极电极117,前述复合虚设栅极材料层125包括:包含第一虚设栅极材料119的底层以及包含第二虚设栅极材料119的顶层,且第二虚设栅极材料119与第一虚设栅极材料119不同。

在一些实施例中,可以选择第一虚设栅极材料119为具有大于鳍片113的蚀刻速率。如下面更详细描述的,选择具有不同蚀刻速率的第一虚设栅极材料119、第二虚设栅极材料121及鳍片113的材料有助于使虚设栅极电极117图案化。举例而言,在使用硅(Si)形成鳍片113的实施例中,可以使用硅锗(SiGe)形成第一虚设栅极材料119,并且可以使用硅(Si)形成第二虚设栅极材料121。如此一来,第一虚设栅极材料119的蚀刻速率可以大于鳍片113的蚀刻速率。在鳍片113是诸如硅锗的材料的其他实施例中,第一虚设栅极材料119也可以是硅锗,但是为了产生不同的蚀刻速率,第一虚设栅极材料119可具有更高浓度的锗。

根据一些实施例,可以通过诸如化学气相沉积(CVD)、物理气相沉积(physicalvapor deposition,PVD)、等离子体辅助化学气相沉积(PECVD)、原子层沉积(atomic layerdeposition)、溅射沉积(sputter deposition)、外延生长或本领域已知且用于沉积材料的其他技术的一或多种制程,来沉积复合虚设栅极材料层125的材料。根据一些实施例,尽管可以使用任何合适的厚度,复合虚设栅极材料层125的厚度可以在介于大约

一旦已经形成复合虚设栅极材料层125,可以使虚设栅极电极117图案化。虚设栅极电极117可以定义(define)单一通道或者可以定义位于虚设栅极介电质115之下的鳍片113内的多个通道区域。可以通过举例而言,使用本领域已知的沉积及光微影技术,来初始沉积并图案化栅极遮罩123于虚设栅极材料层上,来形成虚设栅极电极117。栅极遮罩123可以结合常用的遮罩及牺牲材料,诸如(但不限于)氧化硅、氮氧化硅、SiCON、SiC、SiOC及/或氮化硅,并且可以沉积到介于大约

图1A进一步显示穿过半导体装置100的几条切割线,且将在以下的讨论中以及其余的图式中参考这些切割线。具体而言,图1A显示穿过在鳍片113中的垂直部分的第一切割线AA(例如,鳍片上切割(cut-on-fin)视图)以及穿过相邻于鳍片113的垂直部分的第二切割线BB(例如,鳍片外切割(cut-without-fin)视图)。

图1B及图1C根据一些实施例,显示在形成FinFET 107的中间步骤中,沿着第一切割线AA(例如,鳍片上切割(cut-on-fin)视图)以及第二切割线BB(例如,鳍片外切割(cut-without-fin)视图)的剖面图。根据一些实施例,中间步骤包括将虚设栅极材料层形成为复合虚设栅极材料层125,以及在复合虚设栅极材料层125之上形成两个栅极遮罩123。

图2A及图2B根据一些实施例,显示沿着第一切割线AA及第二切割线BB的剖面图,且附加显示在形成FinFET 107的中间步骤中的第一图案化步骤以形成虚设栅极电极117的顶部203。根据一些实施例,一旦已经形成栅极遮罩123,可以使用干式蚀刻制程在第二虚设栅极材料121(例如,硅(Si))中及/或至第一虚设栅极材料119(例如,硅锗(SiGe))中形成开口201。然而,可以使用任何合适的蚀刻制程来形成开口201。如此一来,虚设栅极电极117的顶部203形成在复合虚设栅极材料层125中。

在一些实施例中,虚设栅极电极117的顶部203包括单一材料(例如,第二虚设栅极材料121)。在其他实施例中,顶部203包括多种材料(例如,第二虚设栅极材料121及第一虚设栅极材料119)。根据一些实施例,开口201可以形成为在介于大约5nm与大约300nm之间的第一深度D1。但是,可以使用任何合适的深度。

图3A及图3B显示沿着第一切割线AA及第二切割线BB的剖面图,并且附加显示与栅极遮罩123及虚设栅极电极117相邻并在第一虚设栅极材料119的经暴露表面之上的顶部间隔物301的初始形成。顶部间隔物301的材料可以包括一个材料层(例如,单层膜),或者可以包括多个材料层(例如,多层膜),诸如两层膜、三层膜、或者甚至多达十层膜。根据一些实施例,顶部间隔物301的材料可以包括第一介电材料,诸如硅基材料,且前述硅基材料诸如SiN、SiON、SiOCN、SiC、SiOC及SiO

图4A及图4B显示沿着第一切割线AA及第二切割线BB的剖面图,并且附加显示图案化步骤。根据一些实施例,图案化步骤包括蚀刻顶部间隔物301。一旦形成,可以使顶部间隔物301的材料图案化以形成顶部间隔物301。在一实施例中,使用诸如反应性离子蚀刻(reactive ion etches)的一或多种非等向性(anisotropic)蚀刻制程,使顶部间隔物301的材料图案化,以从结构的至少一些水平表面(horizontal surfaces)移除顶部间隔物301的材料。

举例而言,在一些实施例中,可以从结构的每个水平表面移除顶部间隔物301的材料。在其他实施例中,可以从基板101及隔离区域111的水平表面移除顶部间隔物301的材料,且同时移除在诸如栅极遮罩123的其他水平表面或接近(nearly)水平的表面之上的顶部间隔物301的材料,仅仅减薄(thinned)顶部间隔物301的材料,且移除顶部间隔物301的材料不足以暴露下层的(underlying)结构。可以利用任何合适的图案化制程。

图案化步骤进一步包括使开口201延伸穿过复合虚设栅极材料层125的剩余部分(例如,第一虚设栅极材料119),且延伸穿过鳍片113的下层材料(例如,通道蚀刻(channeletch))。在图案化步骤期间,栅极遮罩123及顶部间隔物301保护虚设栅极电极117的顶部203。如此一来,虚设栅极电极117的底部401由复合虚设栅极材料层125的剩余材料形成。在一些实施例中,虚设栅极电极117的底部401包括多种材料(例如,第二虚设栅极材料121及第一虚设栅极材料119)。在其他实施例中,底部401包括单一材料(例如,第一虚设栅极材料119)。

可以通过使用栅极遮罩123、虚设栅极电极117及顶部间隔物301作为硬遮罩的反应性离子蚀刻(RIE),或者通过任何其他合适的移除制程,来执行第一虚设栅极材料119的暴露部分的经暴露部分以及来自那些未被保护的区域中的鳍片113的下层材料的移除。可以继续移除,直到鳍片113与隔离区域111的表面为平坦(planar with)或在隔离区域111的表面之下。在图案化步骤中以第一虚设栅极材料119蚀刻鳍片113的经暴露部分时,对介于鳍片113之间的间隔(space)没有限制(例如,通道至通道的间隔(channel to channelspace)),这允许较大的蚀刻能力(etching capability)。此外,通过选择第一虚设栅极材料119的材料为不同于鳍片113的材料(例如,通道区域),可以使用蚀刻条件调整,来执行图案化步骤,以最小化及/或防止切割穿过(cutting through)鳍片113时,对通道区域的顶部的损坏。

根据一些实施例,开口201延伸到鳍片113的基底(base),前述鳍片113的基底停止在基板101上(图4A中未显示),且鳍片113的外部停止在隔离区域111上。在其他实施例中,开口201可以在鳍片113的基底之下延伸,并延伸到基板101中,且在鳍片113的外部延伸到隔离区域111中。根据一些实施例,开口201在虚设栅极电极117的顶部203之下延伸第二深度D2,前述第二深度D2在介于大约10nm至大约300nm之间。然而,可以使用任何合适的深度。

图4C显示在已经执行图案化步骤之后,在通道之下的俯视图(在进入及离开图4A及图4B的纸面的方向上)。具体而言,图4C显示穿过两个鳍片113的开口201的形成。鳍片113可以具有介于大约0.5nm与大约20nm之间的第一宽度W1。在一些实施例中,鳍片113可以彼此分离为介于大约1nm至大约300nm之间的第一距离Dist1。图4C进一步显示的是,形成开口201使第一虚设栅极材料119分离成如图4A及图4B所显示的虚设栅极电极117的两个底部401,且亦将每个鳍片113切割成两个分离的通道区域。根据一些实施例,介于两个底部401之间的间隔(separation)及介于鳍片113的通道区域之间的间隔可以是介于大约5nm及大约1000nm之间的第二距离Dist2。然而,任何合适的距离可以用于第二距离Dist2。

图5A至图5C显示执行蚀刻拉回(etch pull-back)制程,以使虚设栅极电极117的底部401凹入。在蚀刻拉回制程期间,暴露底部401且通过顶部间隔物301及栅极遮罩123保护顶部203。此外,经选择来用于蚀刻拉回制程的前驱物对虚设栅极电极117的经暴露材料具有高选择比,而对鳍片113的材料(例如,通道区域)具有较低的选择比。举例而言,对于所使用的蚀刻剂,虚设栅极电极117的蚀刻速率大于鳍片113的通道材料的蚀刻速率。如此一来,虚设栅极电极117的底部401可以从侧壁凹入第三距离Dist3,且使鳍片113很少或没有凹入。根据一些实施例,第三距离Dist3可以是介于大约0.3nm及大约50nm之间的距离。然而,可以使用任何合适的距离。

根据一些实施例,可以使用等离子体蚀刻(plasma etch)、远程等离子体蚀刻(remote plasma etch)、自由基蚀刻(radical etch)、其组合或其类似物来执行蚀刻拉回制程。蚀刻拉回制程可以使用第一前驱物(例如,主气体(main gas))、第二前驱物(例如,钝化气体(passivation gas))及/或第三前驱物(例如,稀释气体(dilute gas))。根据一些实施例,第一前驱物包括但不限于诸如Cl

根据一些实施例,可以使用介于大约10W及大约3,000W之间的等离子体源功率(plasma source power)(控制离子/自由基比(ion/radical ratio))来执行拉回制程。然而,可以利用任何合适的等离子体源功率。此外,可以使用大约0W至大约3,000W之间的等离子体偏置功率(plasma bias power)来执行蚀刻拉回制程。然而,可以使用任何合适的等离子体偏置功率。可以控制等离子体蚀刻的方向。等离子体蚀刻可以是等向性蚀刻或非等向性蚀刻。根据一些实施例,可以在介于大约1mTorr与大约800mTorr之间的制程压力下,执行蚀刻拉回制程。然而,可以利用任何合适的压力。在一些实施例中,可以使用在介于大约1每分钟标准立方公分(Standard cubic centimeters per minute,sccm)与大约5,000sccm之间的制程流量(process flow)的蚀刻气体,来执行蚀刻拉回制程。但是,可以利用任何合适的制程流程。

根据其他实施例,蚀刻拉回制程包括湿式清洗蚀刻(wet clean etch)。可以使用诸如氢氟酸(hydrofluoric acid,HF)、氟(fluorine,F2)、其组合或其类似物的第一蚀刻剂(例如,主要化学品)来执行湿式清洗蚀刻。根据一些实施例,可以添加反应物以辅助特定材料的化学蚀刻,且反应物可以用于选择性调整湿式清洗蚀刻。反应物包括但不限于诸如H

图5C以俯视图显示蚀刻拉回制程。具体而言,图5C显示在第一虚设栅极材料119中形成的凹部(recess)的第三距离Dist3。开口201的形成及蚀刻拉回制程允许用于将被形成的源极/漏极区域的较大间隔,且没有通道-通道限制(channel-channel restrictions),从而增加虚设栅极残留缺陷(dummy gate residue defect)的裕度(window)。如此一来,由于留下虚设栅极材料的残留物,较大的虚设栅极残留缺陷裕度能够提升蚀刻能力,且具有较小的缺陷风险(例如,金属栅极短路)。

转到图6A及图6B,这些图显示沿着第一切割线AA及第二切割线BB的剖面图,并且附加显示相邻于顶部间隔物301、第一虚设栅极材料119及鳍片113,且在基板101(图6A及图6B中未显示)及隔离区域111的经暴露表面之上的底部间隔物601的初始形成。底部间隔物601可以包括一个材料层(例如,单层膜),或者可以包括多个材料层(例如多层膜),诸如两层膜、三层膜、甚至多达十层膜。可以使用适合于形成顶部间隔物301的任何材料及任何制程来形成底部间隔物601。在一些实施例中,为底部间隔物601选择的材料不同于为顶部间隔物301选择的材料,但是材料也可以为相同。举例而言,在顶部间隔物301是氮化硅(SiN)的实施例中,底部间隔物601可以是氮氧化硅(SiON)。然而,可以使用任何合适的材料。

在沉积期间,底部间隔物601的材料填充在虚设栅极电极117的底部401处的凹部中。根据一些实施例,底部间隔物601的材料可以在顶部间隔物301之上形成为介于大约

图7A及图7B显示沿着第一切割线AA及第二切割线BB的剖面图,且附加显示对底部间隔物601、隔离区域111及/或基板101(图7A及图7B中未显示)的材料的蚀刻。一旦已经形成用于底部间隔物601的材料,可以使底部间隔物601的材料图案化,以形成底部间隔物601。在一实施例中,使用一或多种非等向性蚀刻制程,诸如反应性离子蚀刻制程,使底部间隔物601的材料图案化,以从结构的水平表面移除底部间隔物601。然而,可以利用任何合适的图案化制程。

根据一些实施例,可以使底部间隔物601图案化为在鳍片113之上具有第一高度H1及第一宽度W1。在一些实施例中,第一高度H1可以在介于大约

在一实施例中,用于从结构的水平表面移除底部间隔物601的一或多个非等向性蚀刻制程的图案化制程,还可用于使通过图案化制程暴露的隔离区域111的一部分凹入。如此一来,可以使虚设栅极电极117及底部间隔物601未覆盖的隔离区域111凹入至第三深度D3,前述第三深度D3位于经覆盖的隔离区域111的一部分之下,从而将开口201延伸到隔离区域111。根据一些实施例,可以使隔离区域111凹入到介于大约0.5nm至大约50nm之间的第三深度D3。然而,在其他实施例中,没有使隔离区域111凹入,且隔离区域111的任何合适的图案完全旨在包括在实施例的范围内。

图8A及图8B根据一些实施例,显示沿着第一切割线AA及第二切割线BB的剖面图,且附加显示源极/漏极区域801的形成。一旦已经延伸开口201以移除鳍片113的一部分,可以形成与每个鳍片113接触的源极/漏极区域801。在一实施例中,可以形成源极/漏极区域801,且在一些实施例中,可以形成源极/漏极区域801以形成应力源(stressor),前述应力源将向位于虚设栅极电极117之下的鳍片113的通道区域施加应力。在一实施例中,其中鳍片113包括硅并且FinFET为p-型装置,可以通过以诸如硅或其他具有与通道区域不同的晶格常数(lattice constant)的材料,诸如硅锗(silicon germanium)的材料,来进行选择性(selective)外延制程而形成源极/漏极区域801。外延生长制程可以使用诸如硅烷(silane)、二氯硅烷(dichlorosilane)、锗烷(germane)或其类似物的前驱物,且可以持续介于大约5分钟至大约120分钟。

在一实施例中,可以形成源极/漏极区域801为具有在介于大约

一旦形成源极/漏极区域801,可以通过植入合适的掺质来使掺质植入到源极/漏极区域801中,以补充鳍片113中的掺质来。举例而言,可以植入诸如硼(boron)、镓(gallium)、铟(indium)或其类似物的p型掺质以形成p型金属氧化物半导体场效晶体管(p-type Metal Oxide Semiconductor Field Effect Transistor,PMOS)装置。可替代地(alternatively),可以植入诸如磷(phosphorous)、砷(arsenic)、锑(antimony)或其类似物的n型掺质以形成n型金属氧化物半导体场效晶体管(n-type Metal OxideSemiconductor Field Effect Transistor,NMOS)装置。可以使用虚设栅极电极117、顶部间隔物301及底部间隔物601作为遮罩来植入这些掺质。应当注意的是,所属技术领域中具有通常知识者将认识到的是,可以使用许多其他制程、步骤或其类似方法来植入掺质。举例而言,所属技术领域中具有通常知识者将认识到的是,可以使用间隔物及衬层的各种组合来执行多个植入,或者甚至在形成期间原位植入以形成具有适用于特定目的的特定形状或特性的源极/漏极区域。这些制程中的任何一种都可以用于植入掺质,且以上描述并不意味着将本发明的实施例限于前述步骤。

图8C及图8D分别显示沿着第一切割线AA及第二切割线BB的剖面图,且进一步显示层间介电层901的形成以及用栅极堆叠物903替换虚设栅极电极117,其中图8C对应于图8A的结构,且图8D对应于图8B的结构。一旦已经形成源极/漏极区域801,在图8A及图8B中的结构的源极/漏极区域801、底部间隔物601、顶部间隔物301及隔离区域111的经暴露表面之上,形成接触蚀刻停止层(未显示)的毯覆式沉积。接触蚀刻停止层是用来从通过进一步制程引起的损害来保护下层结构,并提供用于进一步的蚀刻制程的控制点。在一实施例中,虽然可以可替代地使用其他材料诸如氮化物、氮氧化物、碳化物(carbide)、硼化物(boride)、其组合或其类似物,且可以可替代地使用形成接触蚀刻停止层的替代技术,诸如低压CVD(LPCVD)、PVD或其类似制程,接触蚀刻停止层可以使用等离子体辅助化学气相沉积(PECVD)由氮化硅来形成。接触蚀刻停止层可以具有介于大约

根据一些实施例,一旦已经形成接触蚀刻停止层,沉积层间介电层901在接触蚀刻停止层之上。尽管可以使用任何合适的介电,层间介电层901可以包括诸如硼磷硅酸盐玻璃(boron phosphorous silicate glass,BPSG)的材料。虽然可以可替代地使用诸如LPCVD的其他制程,可以使用诸如PECVD的制程来形成层间介电层901。层间介电层901可以形成为在介于大约

一旦形成,层间介电层901及接触蚀刻停止层可以与顶部间隔物301及虚设栅极电极117一起平坦化。在一实施例中,虽然可以使用任何合适的制程,可以使用举例而言,诸如化学机械研磨(chemical mechanical polishing)制程的平坦化制程来使层间介电层901、接触蚀刻停止层及顶部间隔物301平坦化。在一些实施例中,可以利用平坦化制程来移除栅极遮罩123并暴露虚设栅极电极117。

图9A及图9B显示的是,一旦已经暴露虚设栅极电极117,可以移除虚设栅极电极117及下层的虚设栅极介电质115。根据一些实施例,使用例如一或多种湿式或干式蚀刻制程来移除虚设栅极电极117及虚设栅极介电质115,前述湿式或干式蚀刻制程利用对虚设栅极电极117及/或虚设栅极介电质115的材料具有选择比的蚀刻剂,而不是利用对于下层的鳍片113的材料(例如,通道区域)具有选择比的蚀刻剂。然而,可以使用任何合适的移除制程或其他制程。

在移除虚设栅极电极117期间,或者举例而言,在移除虚设栅极电极117之后的栅极氧化物移除步骤中,蚀刻制程可以移除顶部间隔物301及/或底部间隔物601的一些材料。如此一来,顶部间隔物301及/或底部间隔物601的厚度可以从顶部间隔物301及/或底部间隔物601的原始厚度(例如,第三距离Dist3)减小。此外,基于介于顶部间隔物301及底部间隔物601的材料之间的蚀刻速率的差异,且基于用于移除虚设栅极电极117的蚀刻剂的选择比,可以相较于底部间隔物601的厚度进一步减小顶部间隔物301的厚度。然而,在其他实施例中,亦可以相较于顶部间隔物301的厚度进一步减小底部间隔物601的厚度,可以以相同的量来减小厚度,或者可以不从顶部间隔物301及/或底部间隔物601的原始厚度(例如,如图5C所示的第三距离Dist3)来减小厚度。根据图9A至图9E所显示的实施例,顶部间隔物301及底部间隔物601的厚度并未从其原始厚度(例如,第三距离Dist3)减小。

一旦已经暴露鳍片113的通道区域,可以形成栅极堆叠物903。在一实施例中,可以通过先沉积一系列层来形成栅极堆叠物903。在一实施例中,前述一系列层可以包括界面(interfacial)层、第一栅极介电材料、第一金属材料及第一p型金属功函数层(为清楚起见,在图9A及图9B中未分别显示每个层)。

可选择地(optionally),可以在形成第一栅极介电材料之前形成界面层。在一实施例中,界面层可以是通过诸如原位蒸气产生(in situ steam generation,ISSG)的制程,或者诸如化学气相沉积或原子层沉积的沉积制程来形成的诸如二氧化硅(silicondioxide)的材料。在另一实施例中,界面层可以是高k材料,诸如HfO

一旦形成界面层,可以在界面层之上使第一栅极介电材料形成为盖层。在一实施例中,第一栅极介电材料是通过诸如原子层沉积、化学气相沉积或其类似制程的制程来沉积的高k材料,诸如HfO

可选地,第一金属材料或金属栅极盖层可以与第一栅极介电材料相邻地形成(formed adjacent)为阻障层,且可以由诸如TaN、Ti、TiAlN、TaC、TaCN、TaSiN、Mn、Zr、TiN、Ru、Mo、WN、其他金属氧化物(metal oxides)、金属氮化物(metal nitrides)、金属硅酸盐(metal silicates)、过渡金属氧化物(transition metal-oxides)、过渡金属氮化物(transition metal-nitrides)、过渡金属硅酸盐(transition metal-silicates)、金属的氮氧化物(oxynitrides of metals)、金属铝酸盐(metal aluminates)、硅酸锆(zirconiumsilicate)、铝酸锆(zirconium aluminate)、其组合或其类似物。虽然可以使用任何合适的沉积制程或厚度,可以使用诸如原子层沉积、化学气相沉积、溅射或其类似制程的沉积制程,使第一金属材料沉积至介于大约

第一p型金属功函数层可以相邻于第一金属材料形成,且在特定实施例中,可以类似于第一金属材料。举例而言,第一p型金属功函数层可以由诸如W、Al、Cu、TiN、Ti、TiAlN、Ta、TaN、Co、Ni、TaC、TaCN、TaSiN、TaSi2、NiSi2、Mn、Zr、ZrSi2、TaN、Ru、AlCu、Mo、MoSi2、WN、其它金属氧化物、金属氮化物、金属硅酸盐、过渡金属氧化物、过渡金属氮化物,过渡金属硅酸盐、金属的氮氧化物、金属铝酸盐、硅酸锆、铝酸锆、其组合或其类似物的金属材料形成。另外,虽然可以使用任何合适的沉积制程或厚度,第一p型金属功函数层可以使用诸如原子层沉积、化学气相沉积、溅射或其类似制程的沉积制程来沉积至介于大约

一旦已经形成第一p型金属功函数层,可以沉积第一n型金属功函数层。在一实施例中,第一n型金属功函数层可以是诸如W、Cu、AlCu、TiAlC、TiAlN、Ti、TiN、Ta、TaN、Co、Ni、Ag、Al、TaAl、TaAlC、TaC、TaCN、TaSiN、Mn、Zr、其他合适的n型功函数材料或其组合。举例而言,可以利用原子层沉积(ALD)制程、CVD制程或其类似制程,使第一n型金属功函数层沉积至介于大约

在栅极堆叠物903内,亦沉积粘胶层及填充材料。一旦已经形成第一n型金属功函数层,可以形成粘胶层,以助于使上层的填充材料与下层的第一n型金属功函数层粘着,并提供用于形成填充材料的成核层。在一实施例中,粘胶层可以是诸如氮化钛(titaniumnitride)的材料,或者可以是与第一n型金属功函数层相似的材料,并且可以使用诸如ALD的类似制程,来使粘胶层形成为介于大约

一旦已经形成粘胶层,使用粘胶层沉积填充材料以填充开口的剩余部分。在一实施例中,填充材料可以是诸如钨、Al、Cu、AlCui、Ti、TiAlN、TaC、TaCN、TaSiN、Mn、Zr、TiN、Ta、TaN、Co、Ni、其组合或其类似物的材料,且可以使用诸如镀膜(plating)、化学气相沉积、原子层沉积、物理气相沉积、其组合或其类似物的沉积制程来形成。另外,可以将填充材料沉积到藉于大约

图9A及图9B进一步显示的是,在已经沉积填充材料以填充及过度填充(overfill)开口之后,可以将材料平坦化以形成栅极堆叠物903。在一实施例中,虽然可以使用任何合适的制程,诸如研磨(grinding)或蚀刻,可以使用例如化学机械抛光来使材料平坦化。尽管为清楚起见没有明确显示,但是界面层可以沿着栅极堆叠物903的底表面为平坦(planar);且第一栅极介电材料、第一金属材料、第一p型金属功函数层、第一n型金属功函数层、粘胶层及填充材料可以填充栅极堆叠物903的剩余空间。图9A进一步突显出沿着第一切割线AA的结构的第一部分905,且图9B进一步突显出沿着第二切割线BB的结构的第二部分907。在下面关于图9D及图9E的讨论中引用前述第一部分905及第二部分907。

图9A至图9C进一步说明栅极堆叠物903的底部临界尺寸(bottom portioncritical dimension)CD

图9D显示在图9A中突显出的第一部分905的放大图,且图9E显示在图9B中突显示的第二部分907的放大图。具体而言,图9D及图9E进一步显示的是,在栅极堆叠物903的顶部临界尺寸CD

根据一些实施例,在间隔物界面909处顶部间隔物301与底部间隔物601相交(intersect)。根据一些实施例,间隔物界面909具有大约等于第三距离Dist3的长度。在一些实施例中,虽然间隔物界面909也可以位于源极/漏极区域801的顶部的水平面处或水平面之下,间隔物界面909位于源极/漏极区域801的顶部的水平面(level)之上。

图9D进一步显示的是,底部间隔物601位于与栅极堆叠物903相邻且与通道区域(例如,鳍片113)的顶部相邻。在介于底部间隔物601及栅极堆叠物903之间的界面及底部间隔物601及通道区域之间的界面形成第一角度θ’。根据一些实施例,第一角度θ’为大约90°,诸如在介于大约60°与大约120°之间的范围内。

转为参照图10A及图10B,根据一些其他实施例,这些图式分别显示在图9A中突显出的第一部分905及在图9B中突显出的第二部分907的放大图。具体而言,图10A及图10B显示另一实施例的栅极堆叠物903、顶部间隔物301及底部间隔物601的一些部件,其中栅极堆叠物903的顶部临界尺寸CD

根据一些实施例,顶部间隔物301包括第一介电材料(例如,SiN)的单层膜,且底部间隔物601包括第二介电材料的单层膜,且前述第二介电材料可以是前述关于第一介电材料的任何材料(例如,SiON),且其中第一介电材料的第一蚀刻速率大于第二介电材料的第二蚀刻速率。在移除虚设栅极电极117及/或移除虚设栅极介电质115的制程期间中,顶部间隔物301的厚度减小到介于大约0.3nm及大约49.8nm之间的第三厚度Th3,且底部间隔物601的厚度不从其初始厚度(例如:第三距离Dist3)减小,或者底部间隔物601的厚度仅最小地减少。如此一来,栅极堆叠物903的顶部临界尺寸CD

继续图11A及图11B,根据又一其他实施例,这些图分别显示在图9A中突显出的第一部分905及在图9B中突显出的第二部分907的放大图。具体而言,图11A及图11B显示又一实施例的栅极堆叠物903、顶部间隔物301及底部间隔物601的一些部件,其中栅极堆叠物903的底部临界尺寸CD

根据一些实施例,顶部间隔物301包括第一介电材料(例如,SiOCN)的单层膜,且底部间隔物601包括第二介电材料(例如,SiC)的单膜,其中第二介电材料的第四蚀刻速率大于第一介电材料的第三蚀刻速率。在移除虚设栅极电极117及/或移除虚设栅极介电质115的制程期间中,底部间隔物601的厚度减小到介于大约0.3nm及大约49.8nm之间的第四厚度Th4,且顶部间隔物301的厚度不从其初始厚度(例如:第三距离Dist3)减小,或者顶部间隔物301的厚度仅最小地减少。如此一来,栅极堆叠物903的底部临界尺寸CD

现在参照图12A及图12B,根据一些其他实施例,这些图式分别显示在图9A中突显出的第一部分905及在图9B中突显出的第二部分907的放大图。具体而言,图12A及图12B显示又一实施例的栅极堆叠物903、顶部间隔物301及底部间隔物601的一些部件,其中在蚀刻制程期间中(例如,参照图6A、图6B、图7A及图7B)保留(retained)用于形成底部间隔物601的间隔物材料的一部分以与顶部间隔物301的外侧壁及鳍片113的侧壁相邻。

根据一些实施例,如关于图6A、图6B、图7A及图7B所讨论的是,底部间隔物601的材料可以从顶部间隔物301、基板101及隔离区域111的水平表面移除。然而,在这些图式中沿着垂直表面形成的底部间隔物601的材料可以以较小的程度移除。如此一来,底部间隔物601的材料的剩余部分可以沿着侧壁从初始厚度减小,从第一厚度Th1(在图6A及图6B中显示)至第五厚度Th5。此外,底部间隔物601的材料可以在虚设栅极电极117的底部401的凹部中从第二厚度Th2(在图6A及图6B中所显示)减小到第六厚度Th6。根据一些实施例,第五厚度Th5可以在介于大约0.3nm与大约50nm之间,且第六厚度Th6可以在介于大约0.6nm与大约100nm之间。然而,可以使用任何合适的厚度。

图12A及图12B进一步显示的是,介于底部间隔物601及顶部间隔物301之间的间隔物界面909沿着顶部间隔物301的底表面及外侧壁表面形成反向(backwards)“L形(L-shape)”。底部间隔物601亦可与鳍片113形成界面,前述界面沿着鳍片113的顶表面及外侧壁形成为上下颠倒(upside down)的反向“L形”。

转为参照图13A及图13B,根据又一实施例,这些图式分别显示类似于图12A及图12B的第一部分905及第二部分907的放大图。具体而言,图13A及图13B显示又一实施例的栅极堆叠物903、顶部间隔物301及底部间隔物601的一些部件,其中顶部间隔物301包括多层膜。

根据一些实施例,顶部间隔物301包括第一介电膜1301及第二介电膜1303。第一介电膜1301可以包括第一介电材料(例如,SiN),且第二介电膜1303可以包括第二介电材料(例如,SiOCN)。根据一些实施例,可以使第一介电膜1301沉积到介于大约0.3nm及大约50nm之间的第七厚度Th7,且可以使第二介电膜1303沉积在第一介电膜1301之上。然而,可以使用任何合适的厚度。

一旦已经沉积第二介电膜1303,则如以上关于图4A至图4C所讨论的是,可以通过顶部间隔物301、第一虚设栅极材料119及鳍片113延伸开口201。如此一来,可以将第一介电膜1301形成为具有(with)间隔物界面909,第一介电膜1301可以背向(face away)栅极堆叠物903形成“L形”;且第二介电膜1303可以形成为“I形(I-shape)”。另外,可以使第二介电膜1303图案化为具有在介于大约0.3nm及大约50nm之间的第八厚度Th8。然而,可以使用任何合适的厚度。

转为参照图14A及图14B,根据又一实施例,这些图式分别显示类似于图13A及图13B的第一部分905及第二部分907的放大图。具体而言,图14A及图14B显示又一实施例的栅极堆叠物903、顶部间隔物301及底部间隔物601的一些部件,其中顶部间隔物301包括多个介电膜。

根据一些实施例,顶部间隔物301包括第一介电膜1301、第二介电膜1303及第三介电膜1401。第三介电膜1401可以包括第一介电材料(例如,SiC)。如图3A及图3B所示,可以使用上述用于形成顶部间隔物301的任何材料及制程使第三介电膜1401毯覆式沉积在第二介电膜1303之上。根据一些实施例,可以使第一介电膜1301沉积至介于大约0.3nm至大约50nm之间的第九厚度Th9,且可以使第二介电膜1303沉积至介于大约0.3nm至大约50nm之间的第十厚度Th10。

一旦已经沉积第三介电膜1401,则如以上关于图4A至图4C所讨论的是,可以通过顶部间隔物301、第一虚设栅极材料119及鳍片113延伸开口201。如此一来,可以将第一介电膜1301形成为具有间隔物界面909。另外,第一介电膜1301及第二介电膜1303的两者都可以形成为背向栅极堆叠物903的“L形”,且第三介电膜1401可以形成为“I形”。另外,一旦已经沉积第三介电膜1401并使第三介电膜1401图案化,则第三介电膜1401可以具有在介于大约0.3nm与大约50nm之间的第十一厚度Th11。然而,可以使用任何合适的厚度。

转为参照图15A及图15B,根据又一实施例,这些图式分别显示类似于图12A及图12B的第一部分905及第二部分907的放大图。具体而言,图15A及图15B显示又一实施例的栅极堆叠物903、顶部间隔物301及底部间隔物601的一些部件,其中用于形成底部间隔物601的间隔物材料的一部分包括多层,且保留前述间隔物材料的一部分以与顶部间隔物301的外侧壁及鳍片113的侧壁相邻。

根据一些实施例,底部间隔物601包括第一介电层1501及第二介电层1503。第一介电层1501可以包括第一介电材料(例如,SiON),且第二介电层1503可以包括第二介电材料(例如,SiOC)。如图6A及图6B所显示,可以使用上述用于形成底部间隔物601的任何材料及制程,使第一介电层1501毯覆式沉积在结构之上,且可以使第二介电层1503毯覆式沉积在第一介电层1501之上。根据一些实施例,如上所述,可以使第一介电层1501沉积到第五厚度Th5。

一旦已经沉积第二介电层1503,可相对于图6A、图6B、图7A及图7B所讨论的是,可以从顶部间隔物301、基板101及隔离区域111的水平表面移除底部间隔物601的材料。然而,沿着结构的垂直表面形成的底部间隔物601的材料可以以较小的程度移除。图15A及图15B进一步显示的是,间隔物界面909在介于顶部间隔物301的底表面与外侧壁表面及第一介电层1501之间形成反向“L形”。第一介电层1501亦可以与鳍片113形成界面,前述界面沿着鳍片113的顶表面及外侧壁形成为上下颠倒的反向“L形”的形状。此外,根据一些实施例,第二介电层1503将层间介电层901及源极/漏极区域801从第一介电层1501分离。最后,根据一些实施例,在图案化之后,第二介电层1503可以具有介于大约0.3nm与大约50nm之间的第十二厚度Th12。然而,可以使用任何合适的厚度。

继续参照图16A及图16B,根据又一实施例,这些图式分别显示类似于图15A及图15B的第一部分905及第二部分907的放大图。具体而言,图16A及图16B显示又一实施例的栅极堆叠物903、顶部间隔物301及底部间隔物601的一些部件,其中用于形成底部间隔物601的间隔物材料的一部分包括多层,且保留前述间隔物材料的一部分以与顶部间隔物301的外侧壁及鳍片113的侧壁相邻。

在一些实施例中,底部间隔物601包括第一介电层1501、第二介电层1503及第三介电层1601。如图6A及图6B所示,可以使用上述用于形成底部间隔物601的任何材料及制程使第三介电层1601毯覆式沉积在第二介电层1503之上。根据一些实施例,可以使用第一介电材料(例如,SiO

一旦已经沉积第三介电层1601,则如关于图6A、图6B、图7A及图7B所讨论的是,可以从顶部间隔物301、基板101及隔离区域111的水平表面移除底部间隔物601的材料。然而,沿着结构的垂直表面形成的底部间隔物601的材料可以以较小的程度移除。图16A及图16B进一步显示的是,间隔物界面909在介于顶部间隔物301的底表面与外侧壁表面及第一介电层1501之间形成反向“L形”。第一介电层1501亦可以与鳍片113形成界面,前述界面沿着鳍片113的顶表面及外侧壁形成为上下颠倒的反向“L形”的形状。此外,根据一些实施例,第三介电层1601将层间介电层901及源极/漏极区域801从第二介电层1503分离。根据一些实施例,一旦图案化,第三介电层1601可以具有在介于大约0.3nm与大约50nm之间的第十三厚度Th13。然而,可以使用任何合适的厚度。

上述先进的微影制程、方法及材料可用于许多应用,前述应用包括鳍式场效晶体管(FinFET)。举例而言,可以使鳍片图案化,以在介于部件之间产生相对紧密的间隔,这些间隔非常适合用于前述公开内容。另外,可以根据以上公开内容来制造用于形成FinFET的鳍片的间隔物,且前述间隔物也称为心轴(mandrels)。

另外,虽然已经描述了关于形成FinFET装置的上述实施例,但是本文描述的材料及制程可以等效地应用于其他半导体装置且完全包括在实施例的范围内,前述其他半导体装置诸如:梯度通道(gradient-channel)装置、多通道(multi-channel)装置、其组合或其类似物。举例而言,鳍片113的形成可以指向从组合(compound)材料层堆叠物(例如,渐变组合材料(gradient compound materials)、纳米片或其类似物)图案化鳍片。如此一来,梯度通道装置及/或多通道装置(例如,纳米片FET(nanosheet FET,NSFET)、全绕式栅极FET(gate-all-around FET,GAAFET)或其类似物)也可以使用前述技术及制程来形成,且完全包括在实施例的范围内。

根据一些实施例,FinFET装置可以形成有梯度通道。鳍片113可以由在基板101之上形成的梯度材料层形成为梯度通道。梯度材料层可以包括第一硅基梯度化合物(silicon-based gradient compound)(例如,SiGe

在又一实施例中,多通道FET装置(例如,纳米片FET(NSFET)、全绕栅极FET(GAAFET)或其类似物)由形成在基板101之上的半导体材料的多层堆叠物来形成。根据一些实施例,多层堆叠物包括第一纳米片材料层(例如,SiGe)及第二纳米片材料层(例如,Si)的交错纳米片(alternating nanosheets)。第一纳米片材料层也可以称为牺牲通道层。初始使用上述的图案化技术使鳍片113形成为多层堆叠物。一旦已经使鳍片113图案化,就在介于鳍片113之间形成隔离区域111,且在鳍片113及隔离区域111之上形成复合虚设栅极材料层125。复合虚设栅极材料层125包括第一虚设栅极材料119及第二虚设栅极材料121。根据一些实施例,第一虚设栅极材料119包括第一硅基材料(例如,SiGe),且第二虚设栅极材料121包括第二硅基材料(例如,Si)。一旦已经形成复合虚设栅极材料层125,就使用上述技术使虚设栅极电极117的顶部203图案化为第二虚设栅极材料121,然后由顶部间隔物301来保护。上述的用于延伸开口201以使虚设栅极电极117的底部401图案化并蚀刻穿过鳍片113的技术可以等效地应用于这些实施例。根据一些实施例,前述用于使第一虚设栅极材料119凹入的蚀刻拉回技术也可以应用于这些实施例,且可以进一步用于使第一纳米片材料层(例如,SiGe)在通道区域内凹入。一旦凹入,沉积以形成底部间隔物601的材料也可以用于在第二纳米片材料层的凹部中形成内间隔物(inner spacers)。一旦开口201已经延伸穿过鳍片113,就可以在开口201中形成源极/漏极区域801。根据一些实施例,选择第一虚设栅极材料119(例如,SiGe)为用于鳍片113的牺牲通道层(例如,SiGe)相同的材料,且牺牲通道层(例如,SiGe)的蚀刻速率大于第二纳米片材料层(例如,Si)的蚀刻速率。如此一来,在用于移除虚设栅极电极117的第一虚设栅极材料119的制程中,移除在鳍片113的通道区域中的第一纳米片材料层(例如,SiGe)(例如,通过纳米线释放(wire-release)技术)。第二纳米片材料层(例如,Si)的剩余材料形成在通道区域内的被内间隔物分离的纳米结构。一旦已经形成纳米结构,就可以在通道区域内围绕纳米结构形成栅极介电质及栅极电极。

本文公开半导体装置及形成诸如FinFET、NSFET及GAA装置的此些装置的方法的实施例。所公开的实施例的一些部件提供包括大的装置生产良率的益处,并且如下实现装置性能。

本文公开的方法及装置提供以下一或多个优点及益处。在复合虚设栅极材料层125上使用的两步骤(two-step)蚀刻制程允许形成虚设栅极电极117,且前述虚设栅极电极117具有包括第一材料的顶部203及包括第二材料的底部401。在对虚设栅极电极117的底部401进行图案化的期间中,顶部间隔物301形成在虚设栅极电极117的顶部203之上并保护虚设栅极电极117的顶部203。此外,在相同的蚀刻步骤中,使虚设栅极电极117的底部及用于源极/漏极区域801的开口图案化。如此一来,在形成虚设栅极电极117的底部401以及在源极/漏极区域801中形成开口的制程期间中,鳍片113的顶部受到保护,这最小化或完全消除通道顶部(channel-top)的损伤、虚设栅极残留物缺陷(dummy gate residue defects)以及通道-通道之间空间的限制(channel-channel space restrictions)。一旦形成,底部间隔物601与鳍片113的顶部形成第一界面,且与栅极堆叠物903形成第二界面,介于第一界面及第二界面之间的角度为大约90°。此外,可以通过顶部间隔物301及/或底部间隔物601的成形(shaping),在很大程度上控制金属栅极电极的临界尺寸。这些部件在具有高装置性能的半导体装置的制造期间中提供高良率。

根据一些实施例,方法包括:形成鳍片于半导体基板之上。沉积虚设栅极材料层于鳍片之上。对虚设栅极材料层图案化来形成虚设栅极电极的顶部。沿着虚设栅极电极的顶部的侧壁形成顶部间隔物。蚀刻穿过虚设栅极材料层且穿过鳍片的开口,以形成虚设栅极电极的底部。沿着开口的侧壁形成底部间隔物。形成源极/漏极区域在开口中。移除虚设栅极电极。沉积栅极堆叠物于鳍片之上。在一实施例中,前述方法包括沉积第一虚设栅极材料于鳍片之上,以及沉积第二虚设栅极材料于第一虚设栅极材料之上,第二虚设栅极材料不同于第一虚设栅极材料。在一实施例中,第二虚设栅极材料具有不同于第一虚设栅极材料的蚀刻选择比。在前述方法的一实施例中,第一虚设栅极材料具有第一蚀刻选择比,且鳍片具有第二蚀刻选择比,第一蚀刻选择比不同于第二蚀刻选择比。在一实施例中,形成顶部间隔物包括沉积多层膜。在一实施例中,前述方法进一步包括在形成底部间隔物之前,使虚设栅极电极的底部凹入(recessing)。在前述方法的一实施例中,形成底部间隔物以通过第二间隔物材料来填充通过使底部凹入而留下的间隔。在一实施例中,前述方法进一步包括使顶部间隔物相较于底部间隔物更加凹入。在一实施例中,前述方法进一步包括使底部间隔物相较于顶部间隔物更加凹入。

根据一些实施例,方法包括:形成鳍片于半导体基板之上。沉积虚设栅极材料层于鳍片之上。蚀刻虚设栅极材料层至第一深度。在蚀刻虚设栅极材料层之后,沉积第一间隔物于虚设栅极材料层之上。在沉积第一间隔物之后,蚀刻穿过虚设栅极材料层的开口,以形成虚设栅极电极。沉积第二间隔物于第一间隔物之上且沿着开口的侧壁。形成源极/漏极区域于开口中,第二间隔物使虚设栅极电极与源极/漏极区域分离(separating)。移除虚设栅极电极。沉积栅极堆叠物于鳍片之上。在前述方法的一实施例中,蚀刻开口进一步包括形成第一凹部在介于鳍片及第一间隔物之间的虚设栅极电极的侧壁中;以及沉积第二间隔物进一步包括以第二间隔物填充第一凹部。在前述方法的一实施例中,移除虚设栅极电极进一步包括使第二间隔物凹入第一距离。在前述方法的一实施例中,移除虚设栅极电极进一步包括使第一间隔物凹入第二距离,且第二距离小于第一距离。在前述方法的一实施例中,移除虚设栅极电极进一步包括使第一间隔物凹入第二距离,且第二距离大于第一距离。在前述方法的一实施例中,沉积第一间隔物包括沉积介电膜的多层。在前述方法的一实施例中,沉积第二间隔物包括沉积介电膜的多层。

根据一些实施例,半导体装置包括:鳍片、栅极电极堆叠物、第一顶部间隔物、第一底部间隔物以及第一源极/漏极区域。鳍片位于基板之上。栅极电极堆叠物位于鳍片之上。第一顶部间隔物相邻于栅极电极堆叠物。栅极电极堆叠物具有相邻于第一顶部间隔物的第一宽度。第一底部间隔物位于第一顶部间隔物之下。栅极电极堆叠物具有相邻于第一底部间隔物的第二宽度。第二宽度不同于第一宽度。第一源极/漏极区域相邻于鳍片且通过第一底部间隔物与栅极电极堆叠物独立(isolated)。在半导体装置的一实施例中,第一顶部间隔物包括具有L形(L-shape)形状的多层膜。在半导体装置的一实施例中,第一底部间隔物包括具有倒L形(backwards L-shape)形状的多层膜。在半导体装置的一实施例中,第一宽度大于第二宽度。在半导体装置的一实施例中,第一宽度小于第二宽度。在半导体装置的一实施例中,第一顶部间隔物包括第一材料,且第二底部间隔物包括不同于第一材料的第二材料。

前述内文概述了各种实施例的部件,使所属技术领域中具有通常知识者可以从各个方面更佳地了解本公开。所属技术领域中具有通常知识者应可理解的是,他们可轻易地以本公开为基础来设计或修饰其他制程及结构,并以此达到相同的目的及/或达到与在本文中介绍的各种实施例相同的优点。所属技术领域中具有通常知识者也应理解的是,这些等效的构型并未背离本公开的发明精神与范围,且在不背离本公开的发明精神与范围的前提下,可对本公开进行各种改变、置换或修改。

- 芯片封装及其形成方法、半导体器件及其形成方法、半导体装置及其形成方法、三相系统

- 半导体膜的形成方法、半导体器件的形成方法和半导体器件