数据存储装置修复方法

文献发布时间:2023-06-19 11:52:33

技术领域

本发明涉及一种修复方法,尤其涉及一种能使数据存储装置进入只读存储器模式,以自动执行修复程序的数据存储装置修复方法。

背景技术

随着技术的发展,固态数据存储装置(SSD)成为市场上的主流将是一个趋势。这都归功于它的几个优点,例如:快速的读取和写入速度、超强的抗震能力、极低的功率消耗等等。但尽管有这些优秀的数据存储装置特性,还是无法避免会在一些情况下无法正常启动或无法被识别。举例来说,固件损毁或固件的程序错误所造成的死锁(deadlock),皆会造成电脑主机无法识别固态数据存储装置或者造成固态数据存储装置无法正常的启动。现有的作法是,将固态数据存储装置取出,并通过硬件上的处理,将固态数据存储装置强制进入初始模式(initial mode),使固态数据存储装置重新与电脑主机连结,然后再作调试(debug)或更新(upgrade)的动作,以达到修复的目的。然而,这些动作都需要使用者将固态数据存储装置取出并送至维修站处理。因此,如何提供一种在不需要拆装固态数据存储装置,也不需要将固态数据存储装置送至维修站的情况下,仍可以对此固态数据存储装置进行修复的动作,将是本案所要着重的问题与解决的重点。

发明内容

有鉴于此,本发明实施例提供一种数据存储装置修复方法,适用于数据存储装置。数据存储装置包括固态数据存储装置(SSD)控制器、电源管理电路、非易失性存储器及重置电路,数据存储装置修复方法包括:电源管理电路判断是否在预定时间内,收到SSD控制器所发出的正常信号;若否,电源管理电路重新对数据存储装置供电,但停止对非易失性存储器供电。

在本发明的一实施例中,其中在电源管理电路重新对数据存储装置供电,但停止对非易失性存储器供电的步骤后,更包括:SSD控制器在第一缓冲时间内完成只读存储器程序的执行,但SSD控制器无法在第二缓冲时间内读取启动程序,致使SSD控制器停留在只读存储器(ROM)模式下。

在本发明的一实施例中,其中数据存储装置耦接于主机,在SSD控制器停留在ROM模式下的步骤后,更包括:SSD控制器在ROM模式下自主机下载调试程序;SSD控制器执行调试程序以产生错误信息;SSD控制器上传错误信息至主机;以及SSD控制器自主机下载更新程序,并执行更新程序,以完成数据存储装置的修复。

本发明实施例另提供一种数据存储装置修复方法,适用于数据存储装置,数据存储装置包括SSD控制器、电源管理电路、非易失性存储器及重置电路,数据存储装置修复方法包括:电源管理电路判断是否在预定时间内,收到SSD控制器所发出的正常信号;若否,电源管理电路通过修复端口将SSD控制器的致能端口下拉至低准位;以及电源管理电路重新对数据存储装置供电。

在本发明的一实施例中,其中在电源管理电路通过修复端口将SSD控制器的致能端口下拉至低准位的步骤后,更包括:SSD控制器在第一缓冲时间内完成只读存储器程序的执行,但SSD控制器无法在第二缓冲时间内读取启动程序,致使SSD控制器停留在ROM模式下。

在本发明的一实施例中,其中数据存储装置耦接于主机,在SSD控制器停留在ROM模式下的步骤后,更包括:SSD控制器在ROM模式下自主机下载调试程序;SSD控制器执行调试程序以产生错误信息;SSD控制器上传错误信息至主机;以及SSD控制器自主机下载更新程序,并执行更新程序,以完成数据存储装置的修复。

本发明实施例所提供的数据存储装置修复方法,第一种实施方式是对非易失性存储器作电源屏蔽的动作,使得数据存储装置的SSD控制器无法在预设时间内从非易失性存储器载入启动程序或启动载入程序,从而迫使SSD控制器停留在ROM模式下,对数据存储装置执行本发明数据存储装置修复方法。第二种实施方式是电源管理电路通过修复端口将数据存储装置的致能端口下拉至低准位。由于致能端口为低准位,因此在重新对数据存储装置供电的阶段,SSD控制器仅会执行只读存储器程序(ROM Code),而不会载入启动程序。从而迫使SSD控制器停留在ROM模式下,对数据存储装置执行本发明数据存储装置修复方法。借此,数据存储装置可以在不需要被拆装的情况下,或者送至维修站的情况下,自动执行数据存储装置修复的程序,以大幅度改善处理数据存储装置修复所花费的时间与便利性。

上述说明仅是本发明技术方案的概述,为了能够更清楚了解本发明的技术手段,而可依照说明书的内容予以实施,并且为了让本发明的上述和其他目的、特征和优点能够更明显易懂,以下特举较佳实施例,并配合附图,详细说明如下。

附图说明

图1是依照本发明实施例数据存储装置的系统架构示意图。

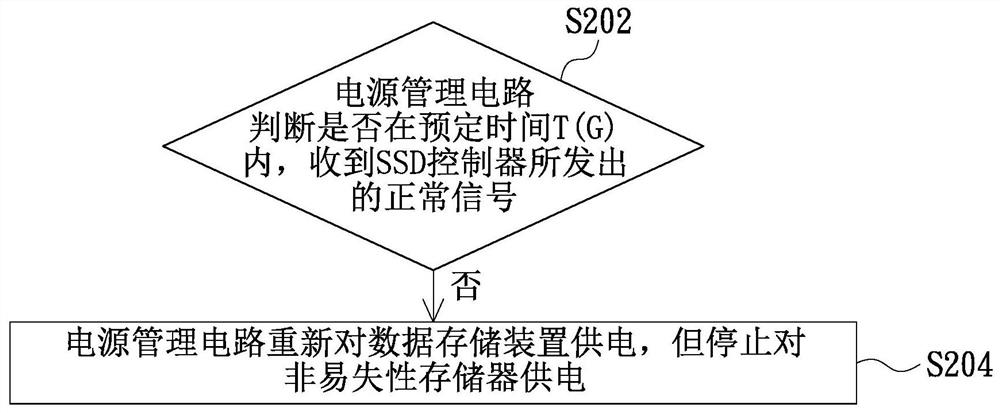

图2是依照本发明实施例数据存储装置进入只读存储器(ROM)模式方法的流程示意图。

图3是依照本发明实施例数据存储装置进入ROM模式的时序示意图。

图4是依照本发明实施例数据存储装置在ROM模式下进行数据修复方法的流程示意图。

图5是依照本发明另一实施例数据存储装置的系统架构示意图。

图6是依照本发明另一实施例数据存储装置进入ROM模式方法的流程示意图。

图7是依照本发明另一实施例数据存储装置进入ROM模式的时序示意图。

图8是依照本发明另一实施例数据存储装置在ROM模式下进行数据修复方法的流程示意图。

具体实施方式

本发明实施例所提供之数据存储装置进入只读存储器(ROM)模式的方法以及数据存储装置在ROM模式下进行数据修复的方法,其可应用于诸如可携式数据存储装置例如固态数据存储装置(SSD)或其他使用到非易失性存储器例如快闪存储器(Nand Flash)作为数据存储装置的电子产品。

数据存储装置的初始化主要包括两个阶段,第一阶段为数据存储装置的系统单晶片控制电路执行只读存储器程序(Read-Only Memory Code,ROM Code),第二阶段为载入且执行启动程序(Boot Code),以载入且执行固件(Firmware)。如果初始化顺利完成,则数据存储装置进入待命(Ready)状态。本发明实施例所提供之数据存储装置修复方法主要是监控数据存储装置的初始化过程。若数据存储装置顺利地初始化并进入待命状态(Ready)时,则数据存储装置的系统单晶片控制电路将发出正常信号给电源管理器,无需启动本发明数据存储装置修复(Restore)程序。反之,启动本发明数据存储装置修复程序。

本发明数据存储装置进入ROM模式方法可以分为两种实施的方式。第一种实施方式是对非易失性存储器作电源屏蔽(Power Mask)的动作,由于电源被屏蔽,因此非易失性存储器无法正常运作,这将导致数据存储装置的SSD控制器无法在预设时间内从非易失性存储器载入启动程序或启动载入程序,如此一来,SSD控制器避免载入有问题的启动程序或固件而造成数据存储装置无法正常运作的情况,达到本发明的目的。实施的方式如以下步骤:首先SSD控制器命令电源管理电路重置(Reset)电源,接着,电源管理电路对SSD控制器供电,让SSD控制器执行ROM Code,之后,电源管理电路对重置电路供电。最后,电源管理电路对非易失性存储器供电。由于电源管理电路并未及时供电至非易失性存储器,因此,非易失性存储器无法及时地运作,这导致SSD控制器无法及时地从非易失性存储器载入BootCode/Boot Loader,进而迫使SSD控制器仅执行ROM Code,或停留在ROM模式下。由于ROMCode可正常运作,此时可以对数据存储装置执行本发明数据存储装置修复方法。

第二种实施方式是电源管理电路通过修复端口将数据存储装置的致能端口下拉至低准位,接着重置数据存储装置的所有电源,然后重新对数据存储装置供电。由于致能端口为低准位,因此在重新对数据存储装置供电的阶段,系统单晶片控制电路仅执行ROMCode,不会载入Boot Code/Boot Loader。由于ROM Code可正常运作,因此,此时可以对数据存储装置执行本发明数据存储装置在ROM模式下进行数据修复的方法。

首先要说明的是第一种实施方式。请参阅图1,图1是依照本发明实施例数据存储装置的系统架构示意图,数据存储装置10可连接至主机20并处理来自主机20的主机命令,例如:数据读取或数据写入。数据存储装置10主要包括SSD控制器110、电源管理电路120、非易失性存储器140及重置电路150,其中,SSD控制器110内部设置只读存储器(ROM)130且具有状态端口SP,电源管理电路120具有监视端口MP。此外,SSD控制器110的电源线可以是耦接于电源管理电路120。非易失性存储器140的信号线及电源线可以是分别耦接于SSD控制器110与电源管理电路120。重置电路150的信号线及电源线可以是分别耦接于SSD控制器110与电源管理电路120。SSD控制器110主要包括中央处理器(CPU)、通用输入与输出(GPIO)接口、主机通信接口、非易失性存储器通信接口。只读存储器130存储有只读存储器程序。非易失性存储器140,例如是快闪存储器,存储有Boot Code/BootLoader。电源管理电路120较佳透过GPIO接口而与SSD控制器110进行数据/信号传输,状态端口SP以及监视端口MP可建构在GPIO接口上,亦可为独立的数据端口。需注意的是,电源管理电路120可以是集成电路的型式,也可以是离散元件(Discrete Component)组成的型式,又或者是整合至SSD控制器110。此外,重置电路150可以是集成电路的型式,也可以是离散元件组成的型式,又或者是整合至SSD控制器110。

图2是依照本发明实施例数据存储装置进入ROM模式方法的流程示意图,图3是依照本发明实施例数据存储装置进入ROM模式的时序示意图。在步骤S202中,电源管理电路120判断是否在预定时间T(G)内,收到SSD控制器110所发出的正常信号GOOD,如图3之GPIO_GOOD的波形(以链线绘之)所表示,这表示SSD控制器110可以正常载入并执行启动程序,且可以正常载入并执行固件,此正常信号GOOD例如是高准位信号。更进一步的说,SSD控制器110可以是通过状态端口SP传送正常信号GOOD给电源管理电路120,而电源管理电路120可以是通过监视端口MP接收正常信号GOOD。这里所提到的监视端口MP及状态端口SP,例如是使用GPIO接口。

如上所述,在初始化的第一阶段,如图3之Core Power的波形以及Flash Power的波形所表示,电源管理电路120依序对SSD控制器110及非易失性存储器140供电后,对SSD控制器110及非易失性存储器140供电之间具有一段第一缓冲时间T(R)。SSD控制器110较佳可在第一缓冲时间T(R)内完成ROM Code的执行,并SSD控制器110较佳可在第二缓冲时间T(B)内完成Boot Code/Boot Loader的执行。接着,电源管理电路120对重置电路150供电,如RESET的波形所表示,SSD控制器110较佳可在预定时间T(G)内发出的正常信号GOOD至电源管理电路120。

在步骤S204中,电源管理电路120重新对数据存储装置10供电,但停止对非易失性存储器140供电。电源管理电路120未在预定时间T(G)内收到来自SSD控制器110的正常信号GOOD,可立即或在缓冲时间T(Restore)后对SSD控制器110、非易失性存储器140及重置电路150停止供电,然后,再重新对SSD控制器110及重置电路150供电,但停止对非易失性存储器140供电,或对非易失性存储器140作电源屏蔽的动作。供电至SSD控制器110后,SSD控制器110较佳可在第一缓冲时间T(R)内完成ROM Code的执行。由于未供电至非易失性存储器140,这导致非易失性存储器140无法运作,SSD控制器110无法在第二缓冲时间T(B)内读取Boot Code/Boot Loader,使得SSD控制器110停留在ROM模式下。另外,电源管理电路120亦可在第二缓冲时间T(B)之后,再供电至非易失性存储器140,使得SSD控制器110停留在ROM模式下,但是,非易失性存储器140可正常运作。

请参阅图4,图4是本发明实施例数据存储装置在ROM模式下进行数据修复方法的流程示意图。在步骤S402中,SSD控制器110在ROM模式下自主机20下载调试程序。在步骤S404中,SSD控制器110执行调试程序以产生错误信息。在步骤S406中,SSD控制器110上传错误信息至主机装置20。在收到来自SSD控制器110所上传的错误信息之后,主机装置20分析此错误信息以产生更新程序。在步骤S408中,SSD控制器110自主机20下载更新程序,并执行更新程序,以完成数据存储装置10的修复。更新程序较佳为更新之后的Boot Code/BootLoader或是固件,SSD控制器110较佳将更新之后的Boot Code/Boot Loader或是固件存储至非易失性存储器140。借此,数据存储装置10可以在不需要拆装的情况下,或者送至维修站的情况下,便可自动执行数据存储装置修复的程序,大幅度的改善处理数据存储装置修复所花费的时间与便利性。

接着要说明的是第二种实施方式。请参阅图5,图5是依照本发明另一实施例数据存储装置的系统架构示意图。数据存储装置30可连接至主机20并处理来自主机20的主机命令,例如:数据读取或数据写入。数据存储装置30主要包括SSD控制器310、电源管理电路320、非易失性存储器340及重置电路350,其中SSD控制器310内部设置只读存储器(ROM)330且具有状态端口SP及致能端口EP,电源管理电路320具有监视端口MP及修复端口RP。需要说明的是,由于数据存储装置30的架构和数据存储装置10的架构大致雷同,雷同的部分已于前述实施例所详加叙述,在此不再赘述,仅作重点概述。电源管理电路320较佳透过GPIO接口而与SSD控制器310进行数据传输,致能端口EP及修复端口RP可建构在GPIO接口上,亦可为独立的数据端口。

图6是依照本发明另一实施例数据存储装置进入ROM模式方法的流程示意图,图7是依照本发明另一实施例数据存储装置进入ROM模式的时序示意图。在步骤S602中,电源管理电路320判断是否在预定时间T(G)内,收到SSD控制器310所发出的正常信号GOOD,如图7之GPIO_GOOD的波形所表示(以链线绘之),这表示SSD控制器310可以正常载入并执行启动程序,且可以正常载入并执行固件。更进一步的说,SSD控制器310可以是通过状态端口SP传送正常信号GOOD给电源管理电路320,而电源管理电路320可以是通过监视端口MP接收正常信号GOOD。

在步骤S604中,电源管理电路320通过修复端口RP将SSD控制器310的致能端口EP下拉至低准位,如图7之#GPIO_ROM的波形所表示,这表示SSD控制器310仅会执行ROM Code,而不会去载入Boot Code/Boot Loader。更进一步的说,电源管理电路320未在预定时间T(G)内收到来自SSD控制器310的正常信号GOOD,可立即或在缓冲时间T(Restore)后通过修复端口RP将SSD控制器310的致能端口EP下拉至低准位。

在步骤S606中,在修复端口RP作动下,电源管理电路320重新对数据存储装置10供电。如图7所示,电源管理电路320在缓冲时间T(Restore)后对SSD控制器310、非易失性存储器340及重置电路350停止供电,然后,再重新对SSD控制器310、非易失性存储器340及重置电路350供电。供电至SSD控制器310后,SSD控制器310较佳可在第一缓冲时间T(R)内完成ROM Code的执行。由于SSD控制器310判断致能端口EP为低准位,所以无论电源管理电路320是否对非易失性存储器340供电,SSD控制器310无法在第二缓冲时间T(B)内读取BootCode/Boot Loader,致使SSD控制器310停留在ROM模式下。换言之,SSD控制器310仅会执行ROM Code,而不会载入Boot Code/Boot Loader。

请参阅图8,图8是依照本发明另一实施例数据存储装置在ROM模式下进行数据修复方法的流程示意图。在步骤S802中,SSD控制器310在ROM模式下自主机20下载调试程序。在步骤S804中,SSD控制器310执行调试程序以产生错误信息。在步骤S806中,SSD控制器310上传错误信息至主机装置20。在收到来自SSD控制器310所上传的错误信息之后,主机装置20分析此错误信息以产生更新程序。在步骤S808中,SSD控制器310自主机20下载更新程序,并执行更新程序,以完成数据存储装置30的修复。更新程序较佳为更新之后的Boot Code/Boot Loader或是固件,SSD控制器310较佳将更新之后的Boot Code/Boot Loader或是固件存储至非易失性存储器340。借此,数据存储装置30可以在不需要拆装的情况下,或者送至维修站的情况下,便可自动的执行数据存储装置修复的程序,大幅度的改善处理数据存储装置修复所花费的时间与便利性。

综上所述,本发明实施例所提供的数据存储装置修复方法,第一种实施方式是对非易失性存储器作电源屏蔽的动作,使得数据存储装置的SSD控制器无法在预设时间内从非易失性存储器载入启动程序或启动载入程序,从而迫使SSD控制器停留在ROM模式下,对数据存储装置执行本发明数据存储装置修复方法。第二种实施方式是电源管理电路通过修复端口将数据存储装置的致能端口下拉至低准位。由于致能端口为低准位,因此在重新对数据存储装置供电的阶段,SSD控制器仅会执行ROM Code,而不会载入启动程序。从而迫使SSD控制器停留在ROM模式下,对数据存储装置执行本发明数据存储装置修复方法。借此,数据存储装置可以在不需要被拆装的情况下,或者送至维修站的情况下,自动执行数据存储装置修复的程序,以大幅度改善处理数据存储装置修复所花费的时间与便利性。

以上所述,仅是本发明的较佳实施例而已,并非对本发明作任何形式上的限制,虽然本发明已以较佳实施例揭露如上,然而并非用以限定本发明,任何熟悉本专业的技术人员,在不脱离本发明技术方案范围内,当可利用上述揭示的方法及技术内容作出些许的更动或修饰为等同变化的等效实施例,但凡是未脱离本发明技术方案的内容,依据本发明的技术实质对以上实施例所作的任何简单修改、等同变化与修饰,均仍属于本发明技术方案的范围内。

- 数据存储装置控制器、数据存储装置、以及用于控制数据存储装置的方法

- 数据存储装置、数据处理系统及数据存储装置的操作方法