发射驱动器与泵单元

文献发布时间:2023-06-19 11:57:35

技术领域

本申请实施例关于一种发射驱动器与泵单元。

背景技术

电子装置已成为现代人必不可少的必需品,无论工作、学习或是娱乐。随着便携式电子装置的蓬勃发展,消费者不仅追求更好的电子特性,例如更高的显示品质、更高的响应速度、更长的使用寿命或更高的可靠性,而且对更加多元化的产品的功能或稳定性有更高的期望。

发明内容

本申请实施例提供一种发射驱动器与泵单元,借以有效地增加改善发射信号的稳定性或发射驱动器的操作稳定性。

本申请实施例提供一种发射驱动器,包括闩锁电路与缓冲电路。闩锁电路接收第一信号、第二信号与第一时脉信号。闩锁电路包括第一输出端与第二输出端。闩锁电路的第一输出端依据第一时脉信号,输出第三信号。闩锁电路的第二输出端依据第一时脉信号,输出与第三信号相反的第四信号。缓冲电路包括第一输入端、第二输入端与第三输出端。缓冲电路的第一输入端接收第三信号。缓冲电路的第二输入端接收第四信号。缓冲电路的第三输出端依据第三信号与第四信号,输出发射信号。

本申请实施例另提供一种泵单元,包括电容、第一晶体管、第二晶体管与第三晶体管。电容具有第一端与第二端,电容的第一端接收第一信号。第一晶体管具有第一端、第二端与第一栅极端,第一晶体管的第一端耦接电容的第二端,第一晶体管的第二端接收第二信号,第一晶体管的第一栅极端耦接电容的第一端。第二晶体管具有第三端、第四端与第二栅极端,第二晶体管的第三端耦接电容的第一端,第二晶体管的第四端输出一输出信号,第二晶体管的第二栅极端接收第三信号。第三晶体管具有第五端、第六端与第三栅极端,第三晶体管的第五端耦接第二晶体管的第三端,第三晶体管的第六端耦接第二晶体管的第四端,第三晶体管的第三栅极端耦接第三晶体管的第五端。

附图说明

为让本发明的上述目的、特征和优点能更明显易懂,以下结合附图对本发明的具体实施方式作详细说明,其中:

图1为依据本申请的一实施例的电子装置的示意图。

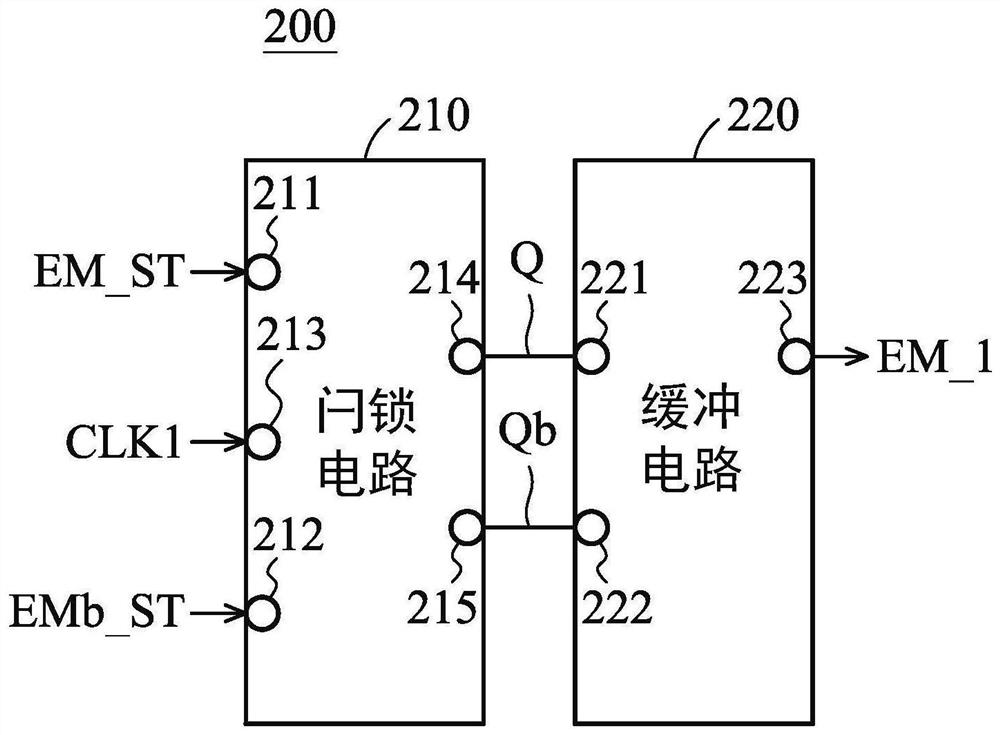

图2为依据本申请的一实施例的发射驱动器的示意图。

图3为图2的发射驱动器的电路图。

图4为图2的发射驱动器的另一示例电路图。

图5A~5C为依据本申请的一实施例的泵单元的电路图。

图6为依据本申请的一实施例的发射驱动器的另一示意图。

图7为依据本申请的一实施例的发射驱动器的耦接关系的示意图。

图8为图6的发射驱动器的电路图。

图9为图6的发射驱动器的另一示例电路图。

图10为图6的发射驱动器的另一示例电路图。

图11为依据本申请的一实施例的发射驱动器的耦接关系的另一示意图。

图12为图6的发射驱动器的另一示例电路图。

图13A~13C为依据本申请的一实施例的泵单元的操作示意图。

图13D~13F为依据本申请的一实施例的泵单元的另一操作示意图。

图14为依据本申请的一实施例的发射驱动器的时序图。

图15为依据本申请的一实施例的发射驱动器的另一时序图。

图16为依据本申请的一实施例的发射驱动器的另一时序图。

图17为依据本申请的一实施例的发射驱动器的另一时序图。

图18为依据本申请的一实施例的发射驱动器的另一示意图。

图19为依据本申请的一实施例的发射驱动器的另一时序图。

图20为依据本申请的一实施例的发射驱动器的另一示意图。

图21为依据本申请的一实施例的发射驱动器的另一时序图。

图中元件标号说明:

100:电子装置

110:电源单元

120:电子单元

130:数据驱动器

140:扫描驱动器

150,200,600,710,1800,2000:发射驱动器

210,610,1810,2010:闩锁电路

220,1820,2020:缓冲电路

211,212,213,221,222:输入端

214,215,223,611,612,621:输出端

410:上拉单元

420,910,1210:开关

430,920:泵单元

440,930:反馈开关

450:重置开关

VDD:电源

Td,Ts,Te:开关

LD:发光单元

EM_ST,EMb_ST,Q,Qb,VST,EM_n-1:信号

CLK1,CLK2,CK0C,CK1C:时脉信号

EM_1,EM_2,EM_0,EM_n:发射信号

EMb_1,EMb_2:互补发射信号

M1,M2,M3,M4,M5,M6,M7,M8,M9,M10,M11,M12,M13,M14,M15,M16,M17,M18,M19,M20,M20,M21,M22,M23,M24,M25,M26,M27,M28,M29,M30,M31,M32,M33,M34,M35,M36,M37:晶体管

VGH,VGL:电压

Cb1,Cb2,Cb3,C1,C2,C3,C4,C5,C6:电容

RES:重置信号

H:高逻辑位准

L:低逻辑位准

Extra-L:特低逻辑位准

T11,T12,T13,T14,T21,T22,T23,T24,T25,T26,T31,T32,T33,T34,T35,T41,T42,T43,T44,T45,T46:时间

1401,1402,1403,1404,1501,1502,1503,1504,1601,1602,1603,1604,1701,1702,1703,1704,1901,1902,2101,2102:区域

具体实施方式

为让本申请的目的、特征或优点能更明显易懂,下文特举出实施例,并配合所附附图,做详细的说明。为了使读者能容易了解及附图的简洁,本申请中的多张附图可能只绘出整个装置的一部分,且附图中的特定元件并非依照实际比例绘图。

本申请说明书提供不同的实施例来说明本申请不同实施方式的技术特征。其中,实施例中的各元件的配置、数量及尺寸是为说明之用,并非用以限制本申请。另外,若实施例与附图中元件标号出现重复,是为了简化说明,并非意指不同实施例之间的关联性。

再者,说明书与权利要求书中所使用的序数例如“第一”、“第二”等的用词,以修饰权利要求书的元件,其本身并不意含及代表该请求组件有任何之前的序数,也不代表某一请求元件与另一请求元件的顺序、或是制造方法上的顺序,这些序数的使用仅用来使具有某命名的一请求元件得以和另一具有相同命名的请求元件能作出清楚区分。

在本申请中,各实施例间特征只要不违背发明精神或相冲突,均可任意混合搭配使用。

图1为依据本申请的一实施例的电子装置的示意图。请参考图1,电子装置100可以包括电源单元110与电子单元120。电源单元110提供电源VDD,其中电源VDD的电压可例如是系统电压。在一实施例中,电子装置100可以包括有机发光二极管(organic light-emitting diode,OLED)、无机发光二极管(light-emitting diode,LED)、量子点(quantumdot,QD)、荧光材料、磷光材料、其他适合的材料或上述材料的组合,但本申请不限于此。无机发光二极管可例如包括次毫米发光二极管(mini light emitting diode,mini LED)微发光二极管(micro light emitting diode,micro LED)或量子点发光二极管(quantumdot light emitting diode,QLED/QDLED)。在一些实施例中,电子装置100可以是显示装置、感测装置、照明装置、天线装置、拼接装置、可挠式装置、其他适合的装置、或上述装置的组合,但本申请不限于此。当电子装置100是显示装置时,电子单元120可以是像素(pixel),但本申请不限于此。

在图1中,电子单元120的数量为一个,但本申请不限于此。在一些实施例中,电子装置100可以包括排列于一或多行(column)及/或一或多列(row)(例如矩阵(matrix))的多个电子单元、多条数据线(图未示)与多条扫描线(图未示)。一个电子单元120可以包括开关Td、开关Ts、开关Te、数据驱动器130所控制的数据线、扫描线、发射线(emission line)与发光单元LD。扫描线可以由扫描驱动器140控制。发射线可以由发射驱动器150控制。开关Td可以耦接电源单元110。在一些实施例中,开关Td可以是薄膜晶体管(thin film transistor,TFT),但本申请不限于此。

开关Te可以耦接开关Td。在一些实施例中,开关Te可以是薄膜晶体管,但本申请不限于此。另外,开关Te的栅极端Te可以耦接发射驱动器150。

发光单元LD可以耦接开关Te。进一步来说,发光单元LD的第一端(例如阳极端)可以耦接开关Te的第一端,而发光单元LD的第二端(例如阴极端)可以耦接参考电压VSS(例如接地电压)。在一些实施例中,发光单元LD可以是有机发光二极管(OLED)或无机发光二极管(LED),例如次毫米发光二极管(mini LED)、微发光二极管(micro LED)、量子点发光二极管(QLED/QD-LED)等,但本申请不限于此。

开关Ts可以耦接开关Td、数据驱动器130与扫描驱动器140。在一些实施例中,开关Ts可以是薄膜晶体管,但本申请不限于此。进一步来说,开关Ts的第一端可以通过对应数据线耦接数据驱动器130,开关Ts的第二端可以耦接开关Td的栅极端,开关Ts的栅极端可以通过对应扫描线耦接扫描驱动器140。

图2为依据本申请的一实施例的发射驱动器的示意图。在本实施例中,发射驱动器200例如可以是图1的发射驱动器150。请参考图2,发射驱动器200可以包括闩锁电路210与缓冲电路220。

闩锁电路210可以包括输入端211、输入端212、输入端213、输出端214与输出端215。闩锁电路210的输入端211可以接收信号EM_ST。闩锁电路210的输入端212可以接收信号EMb_ST。闩锁电路210的输入端213可以接收时脉信号CLK1。

闩锁电路210的输出端214可以依据时脉信号CLK1,输出信号Q。举例来说,当时脉信号CLK1为低逻辑位准“L”时,闩锁电路210的输出端214输出与信号EM_ST相同的信号Q。当时脉信号CLK1为高逻辑位准“H”时,闩锁电路210的输出端214维持信号Q的逻辑位准。

闩锁电路210的输出端215可以依据时脉信号CLK1,输出与信号Q相反的信号Qb。举例来说,当时脉信号CLK1为低逻辑位准“L”时,闩锁电路210的输出端215输出与信号EMb_ST相同的信号Qb。当时脉信号CLK1为高逻辑位准“H”时,,闩锁电路210的输出端215维持信号Qb的逻辑位准。在本实施例中,当时脉信号CLK1为低逻辑位准“L”时,表示发射驱动器200操作于闩锁模式。此时,信号EMb_ST为与信号EM_ST相反的互补信号。

缓冲电路220可以包括输入端221、输入端222与输出端223。缓冲电路220的输入端221可以耦接闩锁电路210的输出端214,并接收信号Q。缓冲电路220的输入端222可以耦接闩锁电路210的输出端215,并接收信号Qb。缓冲电路220的输出端223可以依据信号Q与信号Qb,输出发射信号EM_1。举例来说,当信号Q为高逻辑位准“H”且信号Qb为低逻辑位准“L”时,发射信号EM_1为高逻辑位准“H”。当信号Q为低逻辑位准“L”且信号Qb为高逻辑位准“H”时,发射信号EM_1为低逻辑位准“L”。

图3为图2的发射驱动器的电路图。请参考图3,闩锁电路210可以包括晶体管M1与晶体管M2。晶体管M1具有第一端、第二端与栅极端。晶体管M1的第一端可以耦接闩锁电路210的输入端211,并接收信号EM_ST。晶体管M1的第二端可以耦接闩锁电路210的输出端214。晶体管M1的栅极端可以耦接闩锁电路210的输入端213,并接收时脉信号CLK1。

晶体管M2具有第一端、第二端与栅极端。晶体管M2的第一端可以耦接闩锁电路210的输入端212,并接收信号EMb_ST。晶体管M2的第二端可以耦接闩锁电路210的输出端215。晶体管M2的栅极端可以耦接闩锁电路210的输入端213,并接收时脉信号CLK1。

缓冲电路220可以包括晶体管M3与晶体管M4。晶体管M3具有第一端、第二端与栅极端。晶体管M3的第一端可以接收一电压VGH。晶体管M3的第二端可以耦接缓冲电路220的输出端223。晶体管M3的栅极端可以耦接缓冲电路220的输入端222,亦即晶体管M3的栅极端耦接闩锁电路210的输出端215。

晶体管M4具有第一端、第二端与栅极端。晶体管M4的第一端可以耦接缓冲电路220的输出端223。晶体管M4的第二端可以接收电压VGL。晶体管M4的栅极端可以耦接缓冲电路220的输入端221,亦即晶体管M4的栅极端耦接闩锁电路210的输出端214。在本实施例中,电压VGL是低于电压VGH。举例来说,电压VGH可以是系统电压,而VGL可以是接地电压。在本实施例中,缓冲电路220可以进一步包括电容Cb1。电容Cb1可以耦接于晶体管M4的第一端与栅极端之间。

图4为图2的发射驱动器的另一示例电路图。请参考图4,闩锁电路210可以包括晶体管M1、晶体管M2、上拉单元(pull-up unit)410、开关420、泵单元(pump unit)430、反馈开关(feedback switch)440与重置开关(reset switch)450。另外,缓冲电路220包括晶体管M3与晶体管M4。在本实施例中,图4的晶体管M1、晶体管M2、晶体管M3和晶体管M4与图3的晶体管M1、晶体管M2、晶体管M3和晶体管M4相同或相似,可以参考图3的实施例的说明,故在此不再赘述。在一些实施例中,当泵单元430包括(一或多个)P型晶体管时,泵单元430可以是泵升压单元(pump-up unit),但本申请不限于此。在另一些实施例中,当泵单元430包括(一或多个)N型晶体管时,泵单元430可以是泵降压单元(pump-down unit),但本申请不限于此。

上拉单元410可以耦接于晶体管M1的第二端与晶体管M2的第二端之间。当信号Q或信号Qb为高逻辑位准“H”时,上拉单元410可操作以维持稳定。

在本实施例中,上拉单元410可以包括晶体管M5与晶体管M6。晶体管M5具有第一端、第二端与栅极端。晶体管M5的第一端可以接收电压VGH。晶体管M5的第二端可以耦接晶体管M1的第二端。晶体管M5的栅极端可以耦接晶体管M2的第二端。

晶体管M6具有第一端、第二端与栅极端。晶体管的第一端M6可以接收电压VGH。晶体管M6的第二端可以耦接晶体管M5的栅极端。晶体管M6的栅极端可以耦接晶体管M5的第二端。

开关420可以耦接于晶体管M1的第二端与泵单元430之间。开关420可以操作以保护闩锁电路210的输入端211与输出端214之间的晶体管(例如晶体管M1),进而隔离用于有效自举(effective bootstrap)的信号Q。

在本实施例中,开关420可以包括晶体管M7。晶体管M7具有第一端、第二端与栅极端。开关M7的第一端M7可以耦接晶体管M1的第二端M1。晶体管M7的第二端可以耦接泵单元430。晶体管M7的栅极端可以接收电压VGL。

泵单元430可以耦接于开关420与闩锁电路210的输出端214之间。在本实施例中,泵单元430可以包括电容C1、晶体管M8、晶体管M9与晶体管M10。电容C1具有第一端与第二端。电容C1的第一端C1可以耦接开关420(例如晶体管M7的第二端)。

晶体管M8具有第一端、第二端与栅极端。晶体管M8的第一端可以耦接电容C1的第二端。晶体管M8的第二端可以接收时脉信号CLK2。晶体管M8的栅极端可以耦接电容C1的第一端。

晶体管M9具有第一端、第二端与栅极端。晶体管M9的第一端可以耦接电容C1的第一端。晶体管M9的第二端可以耦接输出端214。晶体管M9的栅极端可以接收时脉信号CLK1。

晶体管M10具有第一端、第二端与栅极端。晶体管M10的第一端可以耦接晶体管M9的第一端。晶体管M10的第二端可以耦接晶体管M9的第二端。晶体管M10的栅极端可以耦接晶体管M10的第一端。泵单元430可以操作以增强用于晶体管M10的栅极端的特低电压。

反馈开关440可以耦接于晶体管M1的第二端与闩锁电路210的输出端223之间。在闩锁电路210闩锁信号之后,反馈开关440可以操作以将信号Q的电压位准维持为发射信号EM_1。

在本实施例中,反馈开关440可以包括晶体管M11。晶体管M11具有第一端、第二端与栅极端。开关M11的第一端可以耦接缓冲电路220的输出端223。晶体管M11的第二端可以耦接晶体管M1的第二端。晶体管M11的栅极端可以接收时脉信号CLK2。

重置开关450可以耦接闩锁电路210的输出端215与晶体管M2的第二端。在本实施例中,重置开关450可以包括晶体管M12。晶体管M12具有第一端、第二端与栅极端。晶体管M12的第一端可以耦接输出端215与晶体管M2的第二端。晶体管M12的第二端可以接收电压VGL。晶体管M12的栅极端可以接收重置信号RES。

在图4中,闩锁电路210可以包括上拉单元410、开关420、泵单元430、反馈单元440与重置开关450,但本申请实施例不限于此。在一些实施例中,使用者可以视其需求,选择上拉单元410、开关420、泵单元430、反馈单元440与重置开关450的至少一个或是上述元件的组合。

举例来说,在一些实施例中,上拉单元410、开关420、泵单元430、反馈开关440与重置开关450的至少一个可以省略,但本申请不限于此。

在图4中,包括有电容C1、晶体管M8、晶体管M9与晶体管M10的泵单元430是本申请的一个示例性实施例,但本申请实施例不限于此。在一些实施例中,泵单元430可以包括电容C1与晶体管M8,如图5A所示。在图5A中,电容C1的第一端可以耦接图4的闩锁电路210的输出端214。晶体管M8的第一端可以耦接电容C1的第二端。晶体管M8的第二端可以接收时脉信号CLK2。晶体管M8的栅极端可以耦接电容C1的第一端。

在一些实施例中,泵单元430可以包括电容C1,如图5B所示。在图5B中,电容C1的第一端可以耦接图4的闩锁电路210的输出端214,且电容C1的第二端可以接收时脉信号CLK2。

在一些实施例中,泵单元430可以包括电容C1、晶体管M9与晶体管M10,如图5C所示。在图5C中。电容C1的第二端C1可以接收时脉信号CLK2。晶体管M9的第一端可以耦接电容C1的第一端。晶体管M9的第二端可以耦接图4的闩锁电路210的输出端214。晶体管M9的栅极端可以接收时脉信号CLK1。晶体管M10的第一端M10可以耦接晶体管M9的第一端。晶体管M10的第二端可以耦接晶体管M9的第二端。晶体管M10的栅极端可以耦接晶体管M10的第一端。

图6为依据本申请的一实施例的发射驱动器的另一示意图。在本实施例中,发射驱动器600也例如是图1的发射驱动器150。请参考图6,发射驱动器600可以包括闩锁电路610与缓冲电路620。闩锁电路610可以包括输入端211、输入端212、输入端213、输出端214与输出端215。在本实施例中,图6的闩锁电路610与图2的闩锁电路210相同或相似,可以参考图2的实施例的说明,故在此不再赘述。

缓冲电路620可以包括输入端221、输入端222、输出端223与输出端621。图6的输入端221、输入端222和输出端223与图2的输入端221、输入端222和输出端223相同或相似,可以参考图2的实施例的说明,故在此不再赘述。

缓冲电路620的输出端621可以依据信号Q与信号Qb,输出与发射信号EM_1相反的一互补发射信号EMb_1至另一发射驱动器710,如图7所示。在图7中,发射驱动器600可以依据信号Q与信号Qb(如图2所示),产生发射信号EM_1与互补发射信号EMb_1。接着,发射信号EM_1与互补发射信号EMb_1会传送至下一个发射驱动器710,使得发射驱动器710可以依据发射信号EM_1与互补发射信号EMb_1,产生发射信号EM_2与互补发射信号EMb_2。

图8为图6的发射驱动器的电路图。请参考图8,闩锁电路610可以包括晶体管M1与晶体管M2。图8的晶体管M1和晶体管M2与图3的晶体管M1和晶体管M2相同或相似,故在此不再赘述。

缓冲电路620可以包括晶体管M3、晶体管M4、晶体管M13、晶体管M14、电容Cb1与电容Cb2。图8的晶体管M3、晶体管M4和电容Cb1与图3的晶体管M3、晶体管M4和电容Cb1相同或相似,故在此不再赘述。

晶体管M13具有第一端、第二端与栅极端。晶体管M13的第一端可以接收电压VGH。晶体管M13的第二端可以耦接输出端621。晶体管M13的栅极端可以耦接闩锁电路610的输出端214。

晶体管M14具有第一端、第二端与栅极端。晶体管M14的第一端可以耦接输出端621。晶体管M14的第二端可以接收电压VGL。晶体管M14的栅极端可以耦接闩锁电路610的输出端215。电容Cb2可以耦接于晶体管M14的第一端与栅极端之间。

图9为图6的发射驱动器的另一示例电路图。请参考图9,闩锁电路610可进一步包括输出端611与输出端612。闩锁电路610可以包括晶体管M1、晶体管M2、上拉电路410、开关420、泵单元430、反馈开关440、重置开关450、开关910、泵单元920与反馈开关930。在本实施例中,图9的晶体管M1、晶体管M2、上拉单元410、开关420、泵单元430、反馈开关440和重置开关450与图4的晶体管M1、晶体管M2、上拉单元410、开关420、泵单元430、反馈开关440和重置开关450相同或相似,故在此不再赘述。在本实施例中,闩锁电路610的输出端611可进一步耦接晶体管M1的第二端。

开关910可以耦接于晶体管M2的第二端与泵单元920之间。开关910可以操作以保护闩锁电路610的输入端212与输出端612之间的晶体管(例如晶体管M2),进而隔离用于有效自举的信号Qb。

在本实施例中,开关910可以包括晶体管M15。晶体管M15具有第一端、第二端与栅极端。晶体管M15的第一端可以耦接晶体管M2的第二端。晶体管M15的第二端可以耦接泵单元920。晶体管M15的栅极端可以接收电压VGL。

泵单元920可以耦接于开关910与输出端612之间。在本实施例中,泵单元920可以包括电容C2、晶体管M16、晶体管M17与晶体管M18。电容C2具有第一端与第二端。电容C2的第一端可以耦接开关910(例如晶体管M15的第二端)。

晶体管M16具有第一端、第二端与栅极端。晶体管M16的第一端可以耦接电容C2的第二端。晶体管M16的第二端可以接收时脉信号CLK2。晶体管M16的栅极端可以耦接电容C2的第一端。

晶体管M17具有第一端、第二端与栅极端。晶体管M17的第一端可以耦接电容C2的第一端。晶体管M17的第二端可以耦接输出端612。晶体管M17的栅极端可以接收时脉信号CLK1。

晶体管M18具有第一端、第二端与栅极端。晶体管M18的第一端可以耦接晶体管M17的第一端。晶体管M18的第二端可以耦接晶体管M17的第二端。晶体管M18的栅极端可以耦接晶体管M17的第一端。泵单元920可以操作以增强用于晶体管M18的栅极端的特低电压(extra-low voltage)。

反馈开关930可以耦接于晶体管M2的第二端与缓冲电路620的输出端621之间。在闩锁电路610闩锁信号之后,反馈开关930可以操作以将信号Qb的电压位准维持为互补发射信号EMb_1的电压位准。

在本实施例中,反馈开关930可以包括晶体管M19。晶体管M19具有第一端、第二端与栅极端。晶体管M19的第一端可以耦接缓冲电路620的输出端621。晶体管M19的第二端可以耦接晶体管M2的第二端。晶体管M19的栅极端可以接收时脉信号CLK2。

缓冲电路620可以包括晶体管M3、晶体管M4、晶体管M13、晶体管M14、电容Cb1与电容Cb2。图9的晶体管M3、晶体管M4和电容Cb1与图8的晶体管M3、晶体管M4和电容Cb1相同或相似,故在此不再赘述。

在本实施例中,图9的缓冲电路620与图8的缓冲电路620之间的差异在于晶体管M13的栅极端可以耦接闩锁电路610的输出端611,以及晶体管M14的栅极端可以耦接闩锁电路的输出端612。

在图9中,包括电容C2、晶体管M16、晶体管M17与晶体管M18的泵单元920是本申请的一种示例性实施例,但本申请实施例不限于此。在一些实施例中,泵单元920可以包括电容C1与晶体管M8,如图5A所示。电容C1与晶体管M8的耦接关系相似于图5A的实施例的电容C1与晶体管M8的耦接关系,故在此不再赘述。在一些实施例中,泵单元920可以包括电容C1,如图5B所示。电容C1的耦接关系相似于图5B的实施例的电容C1的耦接关系,故在此不再赘述。在一些实施例中,泵单元920可以包括电容C1、晶体管M9与晶体管M10,如图5C所示。电容C1、晶体管M9与晶体管M10的耦接关系相似于图5C的实施例的电容C1、晶体管M9与晶体管M10的耦接关系,故在此不再赘述。

图10为图6的发射驱动器的另一示例电路图。请参考图10。在本实施例中,图10的发射驱动器600相似于图8的发射驱动器600。图10的发射驱动器600与图8的发射驱动器600之间的差异在于缓冲电路620可进一步接收时脉信号CLK2。缓冲电路620的输出端621可依据信号Q、信号Qb与时脉信号CLK2,输出一互补发射信号EMb_1至另一发射驱动器710,如图11所示。

闩锁电路610可以包括晶体管M1与晶体管M2。图10的晶体管M1和晶体管M2与图8的晶体管M1和晶体管M2相同或相似,故在此不再赘述。

缓冲电路620可以包括晶体管M3、晶体管M4、晶体管M13与晶体管M14。图10的晶体管M3、晶体管M4和晶体管M13与图8的晶体管M3、晶体管M4和晶体管M13相同或相似,故在此不再赘述。

晶体管M14具有第一端、第二端与栅极端。晶体管M14的第一端可以耦接输出端621。晶体管M14的第二端可以接收时脉信号CLK2。晶体管M1的栅极端可以耦接闩锁电路610的输出端215。电容Cb2可以耦接于晶体管M14的第一端与栅极端之间。

图12为图6的发射驱动器的另一示例电路图。请参考图12,闩锁电路610可进一步包括输出端611与输出端612。闩锁电路610可以包括晶体管M1、晶体管M2、上拉单元410、开关420、泵单元430、反馈开关440、重置开关450与开关1210。

开关1210可以耦接于晶体管M2的第二端与闩锁电路610的输出端612之间。开关1210可以操作以保护闩锁电路610的输入端210与输出端612之间的晶体管(例如晶体管M2),进而隔离用于有效自举的信号Qb。

在本实施例中,开关1210可以包括晶体管M20。晶体管M20具有第一端、第二端与栅极端。晶体管M20的第一端可以耦接晶体管M2的第二端。晶体管M20的第二端可以耦接闩锁电路610的输出端612。晶体管M20的栅极端可以接收电压VGL。

缓冲电路620可以包括晶体管M3、晶体管M4、晶体管M13、晶体管M14、电容Cb1与电容Cb2。图12的晶体管M3、晶体管M4、晶体管M13、晶体管M14、电容Cb1和电容Cb2与图10的晶体管M3、晶体管M4、晶体管M13、晶体管M14、电容Cb1和电容Cb2相同或相似,故在此不再赘述。

由图12可以看出,发射驱动器600的元件的数量可以减少,以减少电路成本或减少电路尺寸(布局区域(layout area))。

图13A~13C为依据本申请的一实施例的泵单元的操作示意图。在图13A~13C,信号EM_ST为低逻辑位准“L”,时脉信号CLK1与时脉信号CLK2为互补。在图13A中,当时脉信号CLK1为低逻辑位准“L”且时脉信号CLK2为高逻辑位准“H”时,晶体管M1与晶体管M9导通。接着,电容C1的第一端与晶体管M8的栅极端为低逻辑位准“L”,且晶体管M8导通。此时,晶体管M10不导通。接着,低逻辑位准“L”由晶体管M9输出,且信号Q下降至低逻辑位准“L”。

在图13B中,当时脉信号CLK1为高逻辑位准“H”且时脉信号CLK2为低逻辑位准“L”时,晶体管M1与晶体管M9不导通,而电容C1的第一端与晶体管M8的栅极端仍为低逻辑位准“L”。由于晶体管M8仍导通,因此电容C1的第二端接收具有低逻辑位准“L”的时脉信号。据此,通过电容C1的第一端和第二端之间的电容耦合,电容C1的第一端可以下降至特低(extra-low)逻辑位准“Extra-L”。由于电容C1的第一端为特低逻辑位准,因此晶体管M10导通。接着,特低逻辑位准“Extra-L”由晶体管M10输出,且信号Q变为特低逻辑位准“Extra-L”。

在图13C中,当时脉信号CLK1为低逻辑位准“L”且时脉信号CLK2为高逻辑位准“H”时,晶体管M1导通,而晶体管M9不导通。接着,电容C1的第一端与晶体管M8的栅极端为低逻辑位准“L”,且晶体管M8导通。此时,晶体管M10不导通。由于晶体管M9与晶体管M1不导通,因此信号Q仍维持特低逻辑位准“Extra-L”。

图13D~13F为依据本申请的一实施例的泵单元的另一操作示意图。在图13D~13F中,信号EM_ST为高逻辑位准“H”,时脉信号CLK1与时脉信号CLK2为互补。在图13D中,当时脉信号CLK1为低逻辑位准“L”且时脉信号CLK2为高逻辑位准“H”时,晶体管M1与晶体管M9导通。接着,电容C1的第一端与晶体管M8的栅极端为高逻辑位准“H”,且晶体管M8与晶体管M10不导通。接着,高逻辑位准“H”由晶体管M9输出,且信号Q上升至高逻辑位准“H”。

在图13E中,当时脉信号CLK1为高逻辑位准“H”且时脉信号CLK2为低逻辑位准“L”时,晶体管M1与晶体管M9不导通。电容C1的第一端与晶体管M8的栅极端仍为高逻辑位准“H”,且晶体管M8与晶体管M10仍不导通。接着,信号Q仍维持高逻辑位准“H”。

在图13F中,当时脉信号CLK1为低逻辑位准“L”且时脉信号CLK2为高逻辑位准“H”时,晶体管M1与晶体管M9导通。接着,电容C1的第一端与晶体管M8的栅极端仍为高逻辑位准“H”,且晶体管M8与晶体管M10仍不导通。接着,信号Q仍维持高逻辑位准“H”。

图14为依据本申请的一实施例的发射驱动器的时序图。图14的时序图可以对应图3的发射控制器200与图8的发射控制器600。在图14中,信号EM_ST与信号的工作周期(dutycycle)可以逐渐地增加,但本申请实施例不限于此。在一些实施例中,信号EM_ST与信号EMb_ST的工作周期可以是固定的。在本实施例中,当发射控制器操作于闩锁模式(亦即时脉信号为低逻辑位准“L”)时,信号EMb_ST为与信号EM_ST相反的互补信号。

请参考图3、图8和图14。在时间T11(例如初始化时间),信号EM_ST为低逻辑位准“L”、信号EMb_ST为高逻辑位准“H”及时脉信号CLK1为低逻辑位准“L”,晶体管M1与晶体管M2导通。接着,信号Q为低逻辑位准“L”且信号Qb为高逻辑位准“H”。据此,晶体管M4(图3和图8)与晶体管M13(图8)导通,晶体管M3(图3和图8)与晶体管M14(图8)不导通,发射信号EM_1(图3和图8)为低逻辑位准“L”,且互补发射信号EMb_1(图8)为高逻辑位准“H”。

在时间T12,由于时脉信号CLK1为高逻辑位准“H”,因此晶体管M1与晶体管M2不导通。据此,信号Q、信号Qb、发射信号EM_1与互补发射信号EMb_1维持相同的逻辑位准。在时间T13,信号EM_ST为高逻辑位准“H”、信号EMb_ST为低逻辑位准“L”及时脉信号CLK1为低逻辑位准“L”,晶体管M1与晶体管M2导通。接着,信号Q为高逻辑位准“H”且信号Qb为低逻辑位准“L”。据此,晶体管M3(图3和图8)与晶体管M14(图8)导通,晶体管M4(图3和图8)与晶体管M13(图8)不导通,发射信号EM_1(图3和图8)为高逻辑位准“H”且互补发射信号EMb_1(图8)为低逻辑位准“L”。由于电容Cb2(图8)为自举电容(bootstrap capacitor),因此信号Qb可以减少一逻辑位准,且信号Qb(图8)可以维持特低逻辑位准。

在时间T14,由于时脉信号CLK1为高逻辑位准“H”,因此晶体管M1与晶体管M2导通。据此,信号Q、信号Qb、发射信号EM_1与互补发射信号EMb_1维持相同的逻辑位准。在时间T15,信号EM_ST为低逻辑位准“L”、信号EMb_ST为高逻辑位准“H”及时脉信号CLK1为低逻辑位准“L”,晶体管M1与晶体管M2导通。接着,信号Q为低逻辑位准“L”且信号Qb为高逻辑位准“H”。据此,晶体管M4(图3和图8)与晶体管M13(图8)导通,晶体管M3(图3和图8)与晶体管M14(图8)不导通,发射信号EM_1(图3和图8)为低逻辑位准“L”,且互补发射信号EMb_1(图8)为高逻辑位准“H”。由于电容Cb1(图3和图8)可以是自举电容,因此信号Q的逻辑位准可进一步减少一逻辑位准,且信号Q(图3和图8)可以维持特低逻辑位准。对于剩余时间的描述,本领域技术人员可以参考如上时间T12~T15的描述,故在此不再赘述。

由图14可以看出,当信号Q或信号Qb下降至低逻辑位准时,发射驱动器200或发射驱动器600可以将信号Q或信号Qb维持为特低逻辑位准,如图14的区域1401、区域1402、区域1403与区域1404所示。如此一来,可以有效地改善发射信号EM_1与互补发射信号EMb_1的稳定性或发射驱动器200或发射驱动器600的操作稳定性。

图15为依据本申请的一实施例的发射驱动器的另一时序图。图15的时序图可以对应图4的发射驱动器200及/或图9的发射驱动器600。在图15中,信号EM_ST与信号EMb_ST的工作周期可以逐渐地增加,但本申请实施例不限于此。在一些实施例中,信号EM_ST与信号EMb_ST的工作周期可以是固定的。在本实施例中,当发射驱动器操作于闩锁模式(亦即,时脉信号CLK1为低逻辑位准“L”)时,信号EMb_ST为与信号EM_ST相反的互补信号。

请参考图4、图9与图15。在时间T21(例如初始化时间),信号EM_ST为低逻辑位准“L”、信号EMb_ST为高逻辑位准“H”、时脉信号CLK1为低逻辑位准“L”以及晶体管M1、晶体管M2、晶体管M8(图4和图9)、晶体管M9(图4和图9)与晶体管M17(图9)导通。接着,信号Q为低逻辑位准“L”,且信号Qb为高逻辑位准“H”。据此,晶体管M4(图4和图9)与晶体管M13(图9)导通,晶体管M3(图4和图9)与晶体管M14(图9)不导通,发射信号EM_1(图4和图9)为低逻辑位准“L”,且互补发射信号EMb_1(图9)为高逻辑位准“H”。

在时间T22,由于时脉信号CLK1为高逻辑位准“H”,因此晶体管M1、晶体管M2、晶体管M9(图4和图9)与晶体管M17(图9)不导通。据此,信号Q、信号Qb、发射信号EM_1与互补发射信号EMb_1维持相同的逻辑位准。在时间T23,信号EM_ST为高逻辑位准“H”、信号EMb_ST为低逻辑位准“L”及时脉信号CLK1为低逻辑位准“L”,晶体管M1、晶体管M2、晶体管M9(图4和图9)、晶体管M16(图9)与晶体管M17(图9)导通。接着,信号Q为高逻辑位准“H”,且信号Qb为低逻辑位准“L”。据此,晶体管M3(图4和图9)与晶体管M14(图9)导通,晶体管M4(图4和图9)与晶体管M13(图9)不导通,发射信号EM_1(图4和图9)为高逻辑位准“H”,且互补发射信号EMb_1(图9)为低逻辑位准“L”。由于电容Cb2(图9)可以为自举电容,因此信号Qb的逻辑位准可进一步减少一逻辑位准,且信号Qb(图9)可以维持特低逻辑位准。

在时间T24,由于时脉信号CLK1为高逻辑位准“H”,因此晶体管M1、晶体管M2、晶体管M9(图4和图9)与晶体管M17(图9)不导通。据此,信号Q与发射信号EM_1维持相同的逻辑位准。此时,由于晶体管M16导通且时脉信号CLK2为低逻辑位准,因此通过电容C2的电容耦合,电容C2的第一端可以下降至特低逻辑位准“Extra-L”,如图13B所示。由于电容C2的第一端为特低逻辑位准“Extra-L”,因此晶体管M18导通。接着,特低逻辑位准“Extra-L”由晶体管M18输出,且信号Qb可以减少另一逻辑位准,如图15的区域1501所示。如此一来,信号Qb可进一步维持为特低逻辑位准,以改善互补发射信号EMb_1的稳定性或发射驱动器200或发射驱动器600的操作稳定性。

在时间T25,信号EM_ST为低逻辑位准“L”,信号EMb_ST为高逻辑位准“H”,时脉信号CLK1为低逻辑位准“L”,晶体管M1、晶体管M2、晶体管M8(图4和图9)、晶体管M9(图4和图9)与晶体管M17(图9)导通。接着,信号Q为低逻辑位准“L”,且信号Qb为高逻辑位准“H”。据此,晶体管M4(图4和图9)与晶体管M13(图9)导通,晶体管M3(图4和图9)与晶体管M14(图9)不导通,发射信号EM_1(图4和图9)为低逻辑位准“L”,且互补发射信号EMb_1(图9)为高逻辑位准“H”。由于电容Cb1(图4和图9)可以是自举电容,信号Q可以减少一逻辑位准,且信号Q(图4和图9)可以维持特低逻辑位准。

在时间T26,由于时脉信号CLK1为高逻辑位准“H”,因此晶体管M1、晶体管M2、晶体管M9(图4和图9)与晶体管M17(图9)不导通。据此,信号Qb与互补发射信号EMb_1维持相同的逻辑位准。此时,由于晶体管M8导通且时脉信号CLK2为低逻辑位准“L”,因此通过电容C1的电容耦合,电容C1的第一端会下降至特低逻辑位准“Extra-L”,如图13B所示。由于电容C1的第一端为特低逻辑位准“Extra-L”,因此晶体管M10导通。接着,特低逻辑位准“Extra-L”由晶体管M10输出,且信号Q可以减少另一逻辑位准,如图15的区域1502所示。如此一来,信号Q可进一步维持特低逻辑位准,以改善互补发射信号EMb_1的稳定性或发射驱动器200或发射驱动器600的操作稳定性。对于剩余时间的描述,本领域技术人员可以参考如上时间T22~T26的描述,故在此不再赘述。

由图15可以看出,当信号Q或信号Qb下降至低逻辑位准时,发射驱动器200或发射驱动器600可以将信号Q或信号Qb维持为特低逻辑位准,如图15中借助于泵单元430与泵单元920的区域1501、区域1502、区域1503与区域1504所示。如此一来,可以有效地改善发射信号EM_1与互补发射信号EMb_1的稳定性或发射驱动器200或发射驱动器600的操作稳定性。

图16为依据本申请的一实施例的发射驱动器的另一时序图。图16的时序图可以对应图10的发射驱动器600。在图16中,信号EM_ST与信号EMb_ST的工作周期可以逐渐地增加,但本申请实施例不限于此。在一些实施例中,信号EM_ST与信号EMb_ST可以是固定的。在本实施例中,当发射驱动器操昨于闩锁模式(亦即,时脉信号CLK1为低逻辑位准“L”)时,信号EMb_ST为与信号EM_ST相反的互补信号。

请参考图10与图16,时间T31和时间的T32的操作与时间T11和时间T12的操作相同或相似,故在此不再赘述。

在时间T33,信号EM_ST为高逻辑位准“H”,信号EMb_ST为低逻辑位准“L”,时脉信号CLK1为低逻辑位准“L”及时脉信号CLK2为高逻辑位准“H”,而晶体管M1与晶体管M2导通。接着,信号Q为高逻辑位准“H”,且信号Qb为低逻辑位准“L”。据此,晶体管M3与晶体管M14导通,晶体管M4与晶体管M13不导通,发射信号EM_1为高逻辑位准“H”,且互补发射信号EMb_1为高逻辑位准“H”。

在时间T34,由于时脉信号CLK1为高逻辑位准“H”,因此晶体管M1与晶体管M2不导通。据此,信号Q与发射信号EM_1维持相同的逻辑位准。此时,晶体管M14仍导通且时脉信号CLK2为低逻辑位准“L”,而互补发射信号EMb_1下降至低逻辑位准“L”。由于电容Cb2可以是自举电容,因此信号Qb可以减少一逻辑位准,且信号Qb可以维持特低逻辑位准,如图16的区域1601所示。

在时间T35,信号EM_ST为低逻辑位准“L”,信号EMb_ST为高逻辑位准“H”,时脉信号CLK1为低逻辑位准“L”,时脉信号CLK2为高逻辑位准“H”,而晶体管M1与晶体管M2导通。接着,信号Q为低逻辑位准“L”,且信号Qb为高逻辑位准“H”。据此,晶体管M4与晶体管M13导通,晶体管M3与晶体管M14不导通,发射信号EM_1为低逻辑位准“L”,且互补发射信号EMb_1为高逻辑位准“H”。由于电容Cb1可以是自举电容,因此信号Q可以减少一逻辑位准,且信号Q可以维持特低逻辑位准,如图16的区域1602所示。对于剩余时间的描述,本领域技术人员可以参考如上时间T32~T35的描述,故在此不再赘述。

由图16可以看出,当信号Q或信号Qb下降至低逻辑位准时,发射驱动器600可以将信号Q或信号Qb维持为特低逻辑位准,如图16的区域1601、区域1602、区域1603与区域1604所示。如此一来,可以有效地改善发射信号EM_1与互补发射信号的稳定性或发射驱动器600的操作稳定性。

图17为依据本申请的一实施例的发射驱动器的另一时序图。图17的时序图可以对应图12的发射驱动器600。在图17中,信号EM_ST与信号EMb_ST的工作周期可以逐渐地增加,但本申请实施例不限于此。在一些实施例中,信号EM_ST与信号的工作周期可以是固定的。在本实施例中,当发射驱动器操作于闩锁模式(亦即,时脉信号CLK1为低逻辑位准“L”)时,信号EMb_ST为与信号EM_ST相反的互补信号。

请参考图12与图17。在时间T41(例如初始化时间),信号EM_ST为低逻辑位准“L”,信号EMb_ST为高逻辑位准“H”,时脉信号CLK1为低逻辑位准“L”,而晶体管M1、晶体管M2、晶体管M8与晶体管M9导通。接着,信号Q为低逻辑位准“L”,且信号Qb为高逻辑位准“H”。据此,晶体管M4与晶体管M13导通,晶体管M3与晶体管M14不导通,发射信号EM_1为低逻辑位准“L”,互补发射信号EMb_1为高逻辑位准“H”。

在时间T42,由于时脉信号CLK1为高逻辑位准“H”,因此晶体管M1、晶体管M2与晶体管M9不导通。据此,信号Q、信号Qb、发射信号EM_1与互补发射信号EMb_1维持相同的逻辑位准。在时间T43,信号EM_ST为高逻辑位准“H”,信号EMb_ST为低逻辑位准“L”,时脉信号CLK1为低逻辑位准“L”,时脉信号CLK2为高逻辑位准“H”,而晶体管M1、晶体管M2与晶体管M9导通。接着,信号Q为高逻辑位准“H”,且信号Qb为低逻辑位准“L”。

在时间T44,由于时脉信号CLK1为高逻辑位准“H”,因此晶体管M1、晶体管M2与晶体管M9不导通。据此信号Q与发射信号EM_1维持相同的逻辑位准。此时,晶体管M14仍导通且时脉信号CLK2为低逻辑位准“L”,而互补发射信号EMb_1下降至低逻辑位准“L”。由于电容Cb2可以是自举电容,因此信号Qb可以减少一逻辑位准,且信号Qb可以维持特低逻辑位准,如图17的区域1701所示。

在时间T45,信号EM_ST为低逻辑位准“L”,信号EMb_ST为高逻辑位准“H”,时脉信号CLK1为低逻辑位准“L”,时脉信号CLK2为高逻辑位准“H”,而晶体管M1、晶体管M2、晶体管M8与晶体管M9导通。接着,信号Q为低逻辑位准“L”,且信号Qb为高逻辑位准“H”。据此,晶体管M4与晶体管M13导通,晶体管M3与晶体管M14不导通,发射信号EM_1为低逻辑位准“L”,且互补发射信号EMb_1为高逻辑位准“H”。由于电容Cb1可以是自举电容,因此信号Q可以减少一逻辑位准,且信号Q可以维持特低逻辑位准。

在时间T46,由于时脉信号CLK1为高逻辑位准“H”,因此晶体管M1、晶体管M2与晶体管M9不导通。据此,信号Qb与互补发射信号EMb_1维持相同的逻辑位准。此时,由于晶体管M8导通且时脉信号CLK2为低逻辑位准“L”,因此通过电容C1的电容耦合,电容C1的第一端下降至特低逻辑位准“Extra-L”,如图13B所示。由于电容C1的第一端为特低逻辑位准“Extra-L”,因此晶体管M10导通。接着,特低逻辑位准“Extra-L”由晶体管M10输出,且信号Q可以减少另一逻辑位准,如图17的区域1702所示。如此一来,信号Q可进一步维持为特低逻辑位准,以改善发射信号EM_1的稳定性或发射驱动器600的稳定性。对于剩余时间的描述,本领域技术人员可以参考如上时间T42~T46的描述,故在此不再赘述。

由图17可以看出,当信号Q或信号Qb下降至低逻辑位准时,发射驱动器600可以将信号Q或信号Qb维持为特低逻辑位准,如图17的区域1701、区域1702、区域1703与区域1704所示。如此一来,可以有效地改善发射信号EM_1与互补发射信号EMb_1的稳定性或发射驱动器600的操作稳定性。

在上述实施例中,发射驱动器200或发射驱动器600使用泵单元430,但本申请实施例不限于此。泵单元430可以使用于其他的发射驱动器,并可达成相同的效果。

图18为依据本申请的一实施例的发射驱动器的另一示意图。请参考图18,发射驱动器1800可以包括闩锁电路1810与缓冲电路1820。闩锁电路1810可以依据信号VST、时脉信号CLK1与时脉信号CLK2,产生信号Q和与信号Q相反的信号Qb。缓冲电路1820可以依据信号Q与信号Qb,产生发射信号EM_0。

另外,闩锁电路1810可以包括晶体管M20、晶体管M21、晶体管M22、晶体管M23、晶体管M24、晶体管M25、电容C3、电容C4与泵单元430。晶体管M20、晶体管M21、晶体管M22、晶体管M23、晶体管M24、晶体管M25、电容C3、电容C4与泵单元430的耦接关系如图18所示,故在此不再赘述。泵单元430的操作可以如图13A~13F所示,故在此不再赘述。

进一步来说,缓冲电路1820可以包括晶体管M26、晶体管M27与电容Cb3。晶体管M26、晶体管M27与电容Cb3的耦接关系如图18所示,故在此不再赘述。如此一来,信号Q可进一步维持为特低逻辑位准,以改善发射信号EM_0的稳定性或发射驱动器1800的操作稳定性。

图19为依据本申请的一实施例的发射驱动器的另一时序图。图19的时序图可以对应图18的发射驱动器1800。在图19中,发射信号EM_0的工作周期可以逐渐地增加,但本申请实施例不限于此。在一些实施例中,发射信号EM_0的工作周期可以是固定的。

由图19可以看出,当信号Q下降至低逻辑位准时,发射驱动器1800可以将信号Q维持为特低逻辑位准,如图19的区域1901与区域1902所示。如此一来,可以有效地改善发射信号EM_0的稳定性或发射驱动器1800的操作稳定性。

图20为依据本申请的一实施例的发射驱动器的另一示意图。请参考图20,发射驱动器2000可以包括闩锁电路2010与缓冲电路2020。闩锁电路2010可以依据信号EM_n-1、时脉信号CK0C与时脉信号CK1C,产生信号Q和与信号Q相反的信号Qb。缓冲电路2020可以依据信号Q与信号Qb,产生发射信号EM_n。

另外,闩锁电路2010可以包括晶体管M28、晶体管M29、晶体管M30、晶体管M31、晶体管M32、晶体管M33、晶体管M34、晶体管M35、电容C5、电容C6与泵单元430。晶体管M28、晶体管M29、晶体管M30、晶体管M31、晶体管M32、晶体管M33、晶体管M34、晶体管M35、电容C5、电容C6与泵单元430的耦接关系如图20所示,故在此不再赘述。泵单元430的操作如图13A~13F所示,故在此不再赘述。

进一步来说,缓冲电路2020可以包括晶体管M36与晶体管M37。晶体管M36与晶体管M37的耦接关系如图20所示,故在此不再赘述。如此一来,信号Q的逻辑位准可进一步维持为特低逻辑位准,以改善发射信号EM_n的稳定性或发射驱动器2000的操作稳定性。

图21为依据本申请的一实施例的发射驱动器的另一时序图。图21的时序图可以对应图20的发射驱动器2000。在图21中,信号EM_n-1的工作周期可以逐渐地增加,但本申请实施例不限于此。在一些实施例中,信号EM_n-1的工作周期可以是固定的。

由图21可以看出,当信号Q下降至低逻辑位准时,发射驱动器2000可以将信号Q维持为特低逻辑位准,如图21的区域2101与区域2102所示。如此一来,可以有效地改善发射信号EM_n的稳定性或发射驱动器2000的操作稳定性。

综上所述,依据本申请实施例的发射驱动器与泵单元,闩锁电路接收第一信号、第二信号与第一时脉信号,并依据第一时脉信号输出第三信号以及依据第一时脉信号输出与第三信号相反的第四信号。缓冲电路接收第三信号与第四信号,并依据第三信号与第四信号,输出发射信号。另外,当第三信号下降至低逻辑位准时,泵单元可以将信号维持为特低逻辑位准。如此一来,可以有效地增加发射信号的稳定性或发射驱动器的操作稳定性。

虽然本发明已以较佳实施例揭示如上,然其并非用以限定本发明,任何本领域技术人员,在不脱离本发明的精神和范围内,当可作些许的修改和完善,因此本发明的保护范围当以权利要求书所界定的为准。

- 发射驱动器与泵单元

- 发射驱动器与具有该发射驱动器的有机发光显示装置