系统级封装方法及结构

文献发布时间:2023-06-19 11:57:35

技术领域

本发明涉及半导体封装技术领域,特别是涉及一种系统级封装方法及结构。

背景技术

半导体封装是整个半导体工艺过程中极为重要的一部分,封装质量的好坏直接决定了产品是否能够流入市场。

根据不同的产品需求,有时会需要在器件中引入较大的电流,但是这种电流通常是超过一般引线材料的熔断电流,致使难以完成封装。一种可能的接近方案是改变引线材料,研发新的引线,但这无疑大大的增加了成本。

发明内容

本发明的目的在于,提供一种系统级封装方法及结构,采用简单的引线实现大电流器件的封装。

为解决上述技术问题,根据本发明的第一方面,提供一种系统级封装结构,包括:

基板,贴片MOS,所述基板上具有基板焊垫,所述贴片MOS具有源极焊垫,所述基板焊垫与所述源极焊垫之间通过多跟引线连接。

可选的,对于所述的系统级封装结构,相邻引线间距大于等于所述引线的直径。

可选的,对于所述的系统级封装结构,所述贴片MOS的源极可接入的电流大于等于3安培。

可选的,对于所述的系统级封装结构,所述源极焊垫包括分布有多个间隔设置的凸起,所述引线焊接在所述凸起上。

根据本发明的第二方面,提供一种系统级封装方法,包括:

将多跟引线逐一焊接在一个贴片MOS的源极焊垫与基板的基板焊垫之间。

可选的,对于所述的系统级封装方法,采用激光焊接工艺进行焊接。

可选的,对于所述的系统级封装方法,在将多跟引线逐一焊接在一个贴片MOS的源极焊垫与基板的基板焊垫之间之前,还包括:

将所述源极焊垫制备呈包括多个间隔设置的凸起的结构。

可选的,对于所述的系统级封装方法,将所述引线焊接在所述凸起上。

本发明提供的系统级封装方法及结构中,将基板焊垫与源极焊垫之间通过多跟引线连接,由此采用常规引线即可实现对源极大电流的施加,结构简单,效果优良,极大的节省了成本。

附图说明

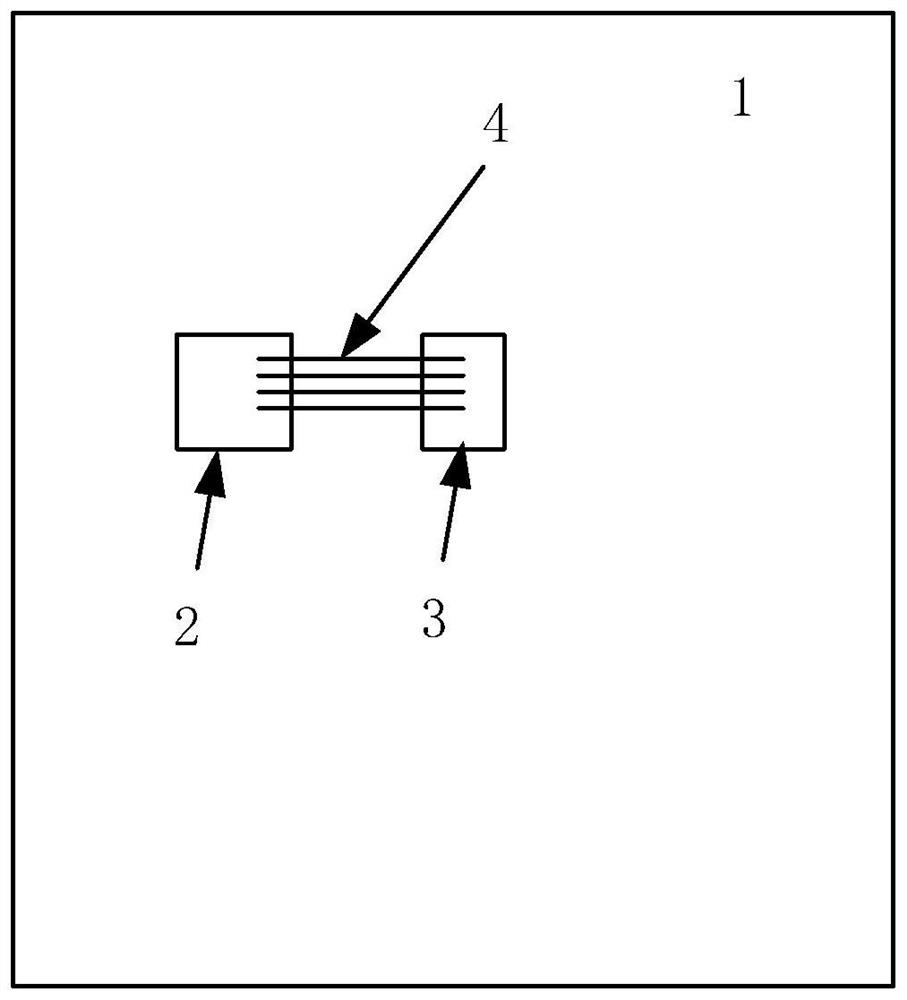

图1为本发明实施例中系统级封装结构的示意图;

图2为本发明实施例中源极焊垫的示意图。

具体实施方式

下面将结合示意图对本发明的系统级封装方法及结构进行更详细的描述,其中表示了本发明的优选实施例,应该理解本领域技术人员可以修改在此描述的本发明,而仍然实现本发明的有利效果。因此,下列描述应当被理解为对于本领域技术人员的广泛知道,而并不作为对本发明的限制。

在下列段落中参照附图以举例方式更具体地描述本发明。根据下面说明和权利要求书,本发明的优点和特征将更清楚。需说明的是,附图均采用非常简化的形式且均使用非精准的比例,仅用以方便、明晰地辅助说明本发明实施例的目的。

请参考图1,本发明提供一种系统级封装结构,包括:

基板1,贴片MOS,所述基板上具有基板焊垫3,所述贴片MOS具有源极焊垫2,所述基板焊垫3与所述源极焊垫2之间通过多跟引线4连接。

其中贴片MOS与基板1的设置为本领域技术人员所熟知,本发明中不进行详述,也未在图中对贴片MOS进行示意。

在本发明一个实施例中,相邻引线4间距大于等于所述引线4的直径。

所述引线4例如可以从金、银、铜、镍等材质中选择。

所述MOS的源极可接入的电流大于等于3安培。例如可以在3~10安培,例如4安培、5安培、6安培、7安培、8安培、9安培等,根据其他需求,还可以大于10安培。

在一个实施例中,以接入9安培为例,金引线的熔断电流在1.74安培,根据现有工艺,是无法实现的。但是采用本发明的方法,例如采用6根引线进行连接,则可以使得每根引线上流经的电流在1.5安培,低于熔断电流,从而实现了封装需求。

进一步的,请参考图2,在本发明一个实施例中,所述源极焊垫2包括多个间隔设置的凸起21,所述引线焊接在所述凸起21上。

通过对所述源极焊垫2的特别设置,能够有效控制相邻引线之间的间距,防止引线之间过近,并降低操作难度。

此外,由于相邻凸起21之间具有间隔,能够有效防止焊接时相邻焊点41之间的接触,并降低焊接产生的应力。

在本发明中,还提供一种系统级封装方法,包括:

将所述源极焊垫制备呈包括多个间隔设置的凸起的结构;

将多跟引线逐一焊接在一个贴片MOS的源极焊垫与基板的基板焊垫之间。

例如,可以采用激光焊接工艺进行焊接。此外,焊接还可以是其他形式,并不限于此。

进一步的,将所述引线焊接在所述凸起上。

综上所述,本发明提供的系统级封装方法及结构中,将基板焊垫与源极焊垫之间通过多跟引线连接,由此采用常规引线即可实现对源极大电流的施加,结构简单,效果优良,极大的节省了成本。

显然,本领域的技术人员可以对本发明进行各种改动和变型而不脱离本发明的精神和范围。这样,倘若本发明的这些修改和变型属于本发明权利要求及其等同技术的范围之内,则本发明也意图包含这些改动和变型在内。

- 用于芯片系统级封装的方法和芯片系统级封装结构

- 带有散热结构的大尺寸芯片系统级封装结构及其制作方法