芯片封装结构及其制作方法

文献发布时间:2023-06-19 11:57:35

技术领域

本发明涉及一种封装结构及其制作方法,尤其是涉及一种芯片封装结构及其制作方法。

背景技术

利用扇出式多频带天线晶圆级封装的设计,可以让电子线路微缩化,并大幅降低电性的插入损耗。在未来电子产品在传输频率与操作速度越来越快下,伴随而来的芯片散热问题也越来越重要。然而,在前述的扇出式多频带天线晶圆级封装的制作中,芯片的主动表面是朝上(face-up)以背面接合至作为天线接地图案的第一重配置线路层,而后再于芯片的主动表面上制作与焊球电性连接的第二重配置线路层。因此,在上述的制作方法中无法加入散热块或散热鳍片来对芯片进行散热,因而无法解决扇出式多频带天线晶圆级封装的散热问题。

发明内容

本发明是针对一种芯片封装结构,其可具有较佳的散热效果。

本发明还针对一种芯片封装结构的制作方法,用以制作上述的芯片封装结构。

根据本发明的实施例,芯片封装结构包括至少一芯片、至少一导热元件、封装胶体以及重配置线路层。每一芯片具有彼此相对的主动表面与背面以及设置于主动表面上的多个电极。导热元件设置于每一芯片的背面上。封装胶体包覆芯片与导热元件,且具有彼此相对的上表面与下表面。每一芯片的每一电极的底表面切齐于封装胶体的下表面。封装胶体暴露出每一导热元件的顶表面。重配置线路层配置于封装胶体的下表面上,且电性连接每一芯片的电极。

在根据本发明的实施例的芯片封装结构中,芯片封装结构还包括至少一导电通孔、至少一第一接垫以及至少一第二接垫。导电通孔贯穿封装胶体且连接上表面与下表面。第一接垫配置于封装胶体的上表面上,且电性连接每一导电通孔的第一端。第二接垫配置于封装胶体的下表面上,且电性连接每一导电通孔的第二端,其中重配置线路层电性连接第二接垫。

在根据本发明的实施例的芯片封装结构中,芯片封装结构还包括天线结构层,配置于封装胶体的上表面上,且包括介电层以及多个天线图案。介电层具有暴露出导热元件的至少一开口,且介电层覆盖封装胶体的上表面与第一接垫。天线图案内埋于介电层且切齐于介电层相对远离封装胶体的表面。天线图案与第一接垫电性连接。

在根据本发明的实施例的芯片封装结构中,至少一芯片为至少一射频芯片(radiofrequency,RF)。

在根据本发明的实施例的芯片封装结构中,至少一芯片包括第一芯片与第二芯片,且天线图案对应第一芯片设置。

在根据本发明的实施例的芯片封装结构中,第一芯片为射频芯片,而第二芯片为基频芯片(baseband chip)。

在根据本发明的实施例的芯片封装结构中,至少一芯片为至少一基频芯片。

在根据本发明的实施例的芯片封装结构中,芯片封装结构还包括多个焊球,配置于重配置线路层的多个扇出接垫上,且与重配置线路层电性连接。

在根据本发明的实施例的芯片封装结构中,每一导热元件于每一芯片的背面上的正投影面积小于背面的面积。

在根据本发明的实施例的芯片封装结构中,芯片封装结构还包括至少一热界面材料,配置于导热元件与芯片之间。导热元件通过热界面材料而固定于芯片上。

根据本发明的实施例,芯片封装结构的制作方法,其包括以下步骤。提供已形成有黏着层的载板。提供至少一芯片及至少一导热元件。每一芯片具有彼此相对的主动表面与背面以及设置于主动表面上的多个电极。每一导热元件设置于每一芯片的背面上。接合芯片于载板上,其中每一芯片的电极直接接触黏着层。形成封装胶体于载板上,以覆盖黏着层且包覆芯片与导热元件。移除部分封装胶体,以使封装胶体暴露出每一导热元件的顶表面。移除载板与黏着层,而暴露出每一芯片的电极与封装胶体的下表面。每一芯片的每一电极的底表面切齐于封装胶体的下表面。形成重配置线路层于封装胶体的下表面上。重配置线路层电性连接每一芯片的电极。

在根据本发明的实施例的芯片封装结构的制作方法中,于移除载板与黏着层之后,且于形成重配置线路层之前,还包括以下步骤。形成至少一导电通孔以贯穿封装胶体且连接封装胶体相对于下表面的上表面与下表面。形成至少一第一接垫于封装胶体的上表面上,其中第一接垫电性连接每一导电通孔的第一端。形成至少一第二接垫于封装胶体的下表面上,其中第二接垫电性连接每一导电通孔的第二端。

在根据本发明的实施例的芯片封装结构的制作方法中,于形成重配置线路层之前,还包括形成天线结构层于封装胶体的上表面上。天线结构层包括介电层以及多个天线图案。介电层具有暴露出导热元件的至少一开口,且介电层覆盖封装胶体的上表面与第一接垫。天线图案内埋于介电层且切齐于介电层相对远离封装胶体的表面。天线图案与第一接垫电性连接。

在根据本发明的实施例的芯片封装结构的制作方法中,至少一芯片为至少一射频芯片。

在根据本发明的实施例的芯片封装结构的制作方法中,至少一芯片包括第一芯片与第二芯片。天线图案对应第一芯片设置。

在根据本发明的实施例的芯片封装结构的制作方法中,第一芯片为射频芯片,而第二芯片为基频芯片。

在根据本发明的实施例的芯片封装结构的制作方法中,至少一芯片为至少一基频芯片。

在根据本发明的实施例的芯片封装结构的制作方法中,于形成重配置线路层之后,还包括:形成多个焊球于重配置线路层的多个扇出接垫上,其中焊球与重配置线路层电性连接。

在根据本发明的实施例的芯片封装结构的制作方法中,每一导热元件于每一芯片的背面上的正投影面积小于背面的面积。

在根据本发明的实施例的芯片封装结构的制作方法中,芯片封装结构的制作方法,还包括提供至少一热界面材料于导热元件与芯片之间,其中导热元件通过热界面材料而固定于芯片上。

基于上述,在本发明的芯片封装结构的设计中,芯片的背面配置有导热元件,且封装胶体暴露出导热元件的顶表面。藉此,芯片所产生的热可通过导热元件快速地传递至在外界,因而使得本发明的芯片封装结构可具有较佳地散热效果。此外,重配置线路层配置于封装胶体的下表面上且电性连接芯片的电极,使得本发明的芯片封装结构可具有较佳的电性表现。简言之,本发明的芯片封装结构可同时兼顾电性与散热的表现,可使芯片的功能维持正常不过热,进而有效地延长芯片封装结构的使用寿命。

为让本发明的上述特征和优点能更明显易懂,下文特举实施例,并配合附图作详细说明如下。

附图说明

包含附图以便进一步理解本发明,且附图并入本说明书中并构成本说明书的一部分。附图说明本发明的实施例,并与描述一起用于解释本发明的原理。

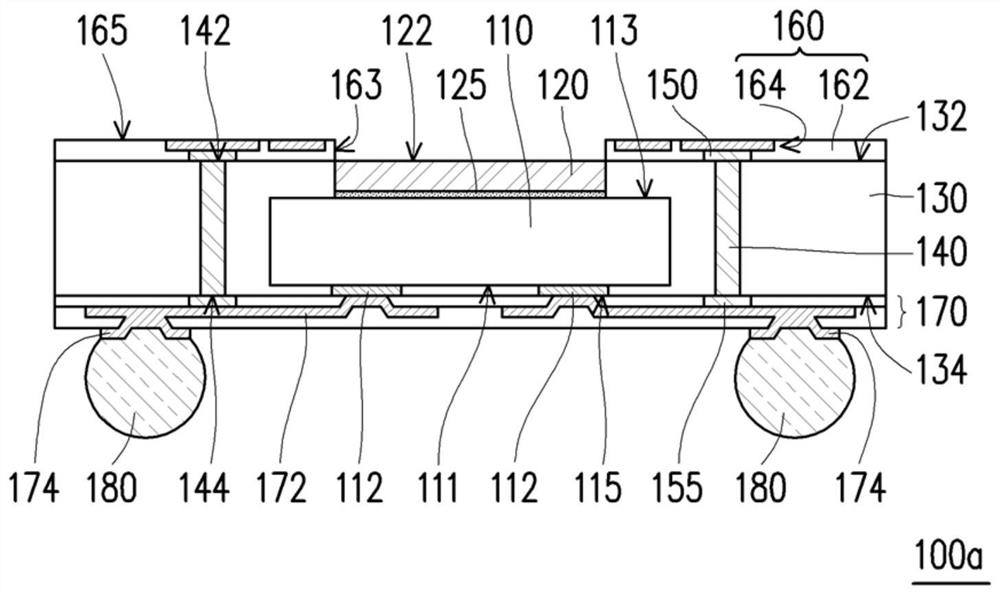

图1A至图1J为本发明的一实施例的一种芯片封装结构的制作方法的剖面示意图;

图2为图1J的芯片封装结构的俯视示意图;

图3为本发明的一实施例的一种芯片封装结构的剖面示意图;

图4为本发明的另一实施例的一种芯片封装结构的剖面示意图;

图5为本发明的又一实施例的一种芯片封装结构的剖面示意图。

附图标号说明

10:载板;

12:黏着层;

100a、100b、100c、100d:芯片封装结构;

110、110a:芯片;

111:主动表面;

112:电极;

113、113a:背面;

115:底表面;

120、120a、120b:导热元件;

122:顶表面;

125、127:热界面材料;

130、130a:封装胶体;

132:上表面;

134:下表面;

140:导电通孔;

142:第一端;

144:第二端;

150:第一接垫;

155:第二接垫;

160:天线结构层;

162:介电层;

163:开口;

164:天线图案;

164a:贴片天线;

164b:偶极天线;

165:表面;

170:重配置线路层;

172:图案化线路层;

174:扇出接垫;

180:焊球。

具体实施方式

现将详细地参考本发明的示范性实施例,示范性实施例的实例说明于附图中。只要有可能,相同元件符号在附图和描述中用来表示相同或相似部分。

图1A至图1J为本发明的一实施例的一种芯片封装结构的制作方法的剖面示意图。图2为图1J的芯片封装结构的俯视示意图。关于本实施例的芯片封装结构的制作方法,首先,请参考图1A,提供已形成有黏着层12的载板10。此处,黏着层12例如是双面热解黏胶带(thermal release tape),但不以此为限。

接着,请参考图1B,提供至少一芯片(示意地示出一个芯片110)及至少一导热元件(示意地示出一个导热元件120)。每一芯片110具有彼此相对的主动表面111与背面113以及设置于主动表面111上的多个电极112。每一导热元件120设置于每一芯片110的背面113上。更进一步来说,可提供至少一热界面材料(Thermal Interface Material,TIM)(示意地示出一个热界面材料125)于导热元件120与芯片110之间,其中导热元件120可通过热界面材料125而固定于芯片110上。如图1B所示,导热元件120于芯片110的背面113上的正投影面积小于背面113的面积。此处,芯片110具体化为射频(radio frequency,RF)芯片,而导热元件120例如是散热器(Heat Spreader),但不以此为限。

接着,请参考图1C,接合芯片110于载板10上,其中每一芯片110的电极112直接接触黏着层12。此处,芯片110及其上的导热元件120是以主动表面111朝下(face-down)的方式接合于载板10的黏着层12上。

接着,请参考图1D,形成封装胶体130a于载板10上,以覆盖黏着层12且包覆芯片110与导热元件120。此时,封装胶体130a完全包覆该芯片110与导热元件120,意即导热元件120的顶表面122亦被封装胶体130所覆盖。

接着,请同时参考图1D与图1E,通过例如是研磨的方式,来移除部分封装胶体130a,以使封装胶体130暴露出导热元件120的顶表面122。此处,导热元件120的顶表面122实质上切齐于封装胶体130的上表面132。

接着,请同时参考图1E与图1F,移除载板10与黏着层12,而暴露出芯片110的电极112与封装胶体130相对于上表面132的下表面134。此处,芯片110的每一电极112的底表面115实质上切齐于封装胶体130的下表面134。

接着,请同时参考图1G与图1H,通过例如是激光钻孔的方式形成通孔于封装胶体130内,且通过电镀填孔的方式,而形成至少一导电通孔(示意地示出二个导电通孔140)以贯穿封装胶体130、形成至少一第一接垫(示意地示出二个第一接垫150)于封装胶体130的上表面132上以及形成至少一第二接垫(示意地示出二个第二接垫155)于封装胶体140的下表面134上。导电通孔140连接上表面132与下表面134,而第一接垫150电性连接每一导电通孔140的第一端142,且第二接垫155电性连接每一导电通孔140的第二端144。此处,导电通孔140的材质、第一接垫150的材质以及第二接垫155的材质相同,例如是铜,但不以此为限。

之后,请同时参考图1I与图2,形成天线结构层160于封装胶体130的上表面132上。天线结构层160包括介电层162以及多个天线图案164。介电层162具有暴露出导热元件120的至少一开口(示意地示出一个开口163),且介电层162覆盖封装胶体130的上表面132与第一接垫150。此处,介电层162例如是感光性介电层(Photo-Imageable Dielectric layer),而开口163例如是通过蚀刻的方式所形成,但不以此为限。天线图案164内埋于介电层162且切齐于介电层162相对远离封装胶体130的表面165,其中天线图案164与第一接垫150电性连接。此处,天线图案164包括例如是多个贴片天线(patch antenna)164a以及多个偶极天线(dipole antenna)164b,且天线图案164的材质例如是铜,但不以此为限。

最后,请参考图1J,形成重配置线路层170于封装胶体130的下表面134上,其中重配置线路层170电性连接芯片110的电极112。由于重配置线路层170的图案化线路172在封装胶体130上的正投影面积大于芯片110在封装胶体130上的正投影面积,因此图案化线路172可视为种扇出线路。紧接着,形成多个焊球180于重配置线路层170的多个扇出接垫174上,其中焊球180与重配置线路层170电性连接。最后,可以通过单体化制程(singulationprocess),以形成至少一个如图1J所示的芯片封装结构100a,而完成芯片封装结构100a的制作。

在结构上,请再参考图1J,本实施例的芯片封装结构100a包括芯片110、导热元件120、封装胶体130以及重配置线路层170。芯片110例如是射频芯片,且其具有彼此相对的主动表面111与背面113以及设置于主动表面111上的电极112。导热元件120可通过热界面材料125而设置且固定于芯片110的背面113上,其中导热元件120于芯片110的背面113上的正投影面积小于背面113的面积。封装胶体130包覆芯片110与导热元件120,且具有彼此相对的上表面132与下表面134。导热元件120的顶表面122切齐于封装胶体130的上表面132。芯片110的电极112的底表面115切齐于封装胶体130的下表面134。重配置线路层170配置于封装胶体130的下表面134上,且电性连接芯片110的电极112。

再者,本实施例的芯片封装结构100a还包括导电通孔140、第一接垫150以及第二接垫155。导电通孔140贯穿封装胶体130且连接上表面132与下表面134。第一接垫150配置于封装胶体130的上表面132上,且电性连接每一导电通孔140的第一端142。第二接垫155配置于封装胶体130的下表面134上,且电性连接每一导电通孔140的第二端144,其中重配置线路层170的图案化线路层172电性连接第二接垫155。

此外,本实施例的芯片封装结构100a还包括天线结构层160,配置于封装胶体130的上表面132上,且包括介电层162以及天线图案164。介电层162具有暴露出导热元件120的开口163,且介电层162覆盖封装胶体130的上表面132与第一接垫150。天线图案164内埋于介电层162且切齐于介电层162相对远离封装胶体130的表面165,且天线图案164与第一接垫150电性连接。另外,本实施例的芯片封装结构100a还还包括焊球180,配置于重配置线路层170的扇出接垫174上且与重配置线路层170电性连接。

相较于习知以芯片的主动表面朝上(face-up)的制作方式,由于本实施例的芯片110及其上的导热元件120是以主动表面111朝下(face-down)的方式接合于载板10的黏着层12上,且芯片110的背面113配置有导热元件120,其中封装胶体130及天线结构层160的介电层162的开口163皆暴露出导热元件120的顶表面122。藉此,芯片110所产生的热可通过导热元件120快速地传递至在外界,因而使得本实施例的芯片封装结构100a可具有较佳地散热效果。此外,重配置线路层170是配置于封装胶体130的下表面134上且电性连接芯片110的电极112,而导电通孔140、第一接垫150与第二接垫155电性连接天线结构层160与重配置线路层170,使得本实施例的芯片封装结构100a可具有较佳的电性表现。简言之,本实施例的芯片封装结构100a可同时兼顾电性与散热的表现,可使芯片110的功能维持正常不过热,保持天线图案164的辐射强度与增益,进而有效地延长芯片封装结构100a的使用寿命。换言之,本实施例的芯片封装结构100a可视为是一种散热增强型扇出式天线封装的芯片封装结构。

在此必须说明的是,下述实施例沿用前述实施例的元件标号与部分内容,其中采用相同的标号来表示相同或近似的元件,并且省略了相同技术内容的说明。关于省略部分的说明可参考前述实施例,下述实施例不再重复赘述。

图3为本发明的一实施例的一种芯片封装结构的剖面示意图。请同时参考图1J以及图3,本实施例的芯片封装结构100b与图1J的芯片封装结构100a相似,两者的差异在于:本实施例的导热元件包括第一导热元件120a与第二导热元件120b。第一导热元件120a通过热界面材料125而固定于芯片110的背面113上,其中第一导热元件120a例如是散热器。第二导热元件120b通过热界面材料127而固定于第一导热元件120a上,其中第二导热元件120b例如是散热鳍片。此处,第一导热元件120a位于热界面材料125与热界面材料127之间,且热界面材料127与封装胶体130的上表面132共平面,但不以此为限。由于本实施例的芯片封装结构100b包括第一导热元件120a与第二导热元件120b,可搭配在高性能的芯片110上,藉此来提高整体芯片封装结构100b的散热效果。

图4为本发明的另一实施例的一种芯片封装结构的剖面示意图。请同时参考图1J以及图4,本实施例的芯片封装结构100c与图1J的芯片封装结构100a相似,两者的差异在于:本实施例的芯片封装结构100c没有设置天线结构层160,且本实施例的芯片110a具体化为基频芯片(baseband-chip)。导热元件120通过热界面材料125而固定于芯片110a的背面113a上。

在制程上,在图1F的步骤之后,即移除载板10与黏着层12,而暴露出芯片110的电极112与封装胶体130相对于上表面132的下表面134之后,直接接续图1J的步骤,即形成重配置线路层170于封装胶体130的下表面134上、形成焊球180于重配置线路层170的扇出接垫174上以及进行单体化程序等步骤。

图5为本发明的又一实施例的一种芯片封装结构的剖面示意图。请同时参考图1J以及图5,本实施例的芯片封装结构100d与图1J的芯片封装结构100a相似,两者的差异在于:本实施例的至少一芯片包括芯片110(可视为是第一芯片)与芯片110a(可视为是第二芯片),且天线图案164对应芯片110设置。举例来说,天线图案164环绕芯片110的周围设置;或者是,天线图案164于封装胶体130的上表面132上的正投影完全重叠或局部重叠于芯片110于封装胶体130的上表面132上的正投影。天线图案164于封装胶体130的上表面132上的正投影不重叠于芯片110a于封装胶体130的上表面132上的正投影。此处,芯片110为射频芯片,而芯片110a为基频芯片。也就是说,于对应基频芯片处没有设置天线图案164。

此外,本实施例的导热元件包括第一导热元件120a与第二导热元件120b。第一导热元件120a通过热界面材料125而固定于芯片110、110a的背面113、113a上,其中第一导热元件120a例如是散热器。第二导热元件120b通过热界面材料127而固定于第一导热元件120a上,其中第二导热元件120b例如是散热鳍片。此处,第一导热元件120a位于热界面材料125与热界面材料127之间,且热界面材料127与封装胶体130的上表面132共平面,但不以此为限。由于本实施例的芯片封装结构100d包括第一导热元件120a与第二导热元件120b,可搭配在高性能的芯片110、110a上,藉此来提高整体芯片封装结构100d的散热效果。

综上所述,在本发明的芯片封装结构的设计中,芯片的背面配置有导热元件,且封装胶体暴露出导热元件的顶表面。藉此,芯片所产生的热可通过导热元件快速地传递至在外界,因而使得本发明的芯片封装结构可具有较佳地散热效果。此外,重配置线路层配置于封装胶体的下表面上且电性连接芯片的电极,使得本发明的芯片封装结构可具有较佳的电性表现。简言之,本发明的芯片封装结构可同时兼顾电性与散热的表现,可使芯片的功能维持正常不过热,进而有效地延长芯片封装结构的使用寿命。

最后应说明的是:以上各实施例仅用以说明本发明的技术方案,而非对其限制;尽管参照前述各实施例对本发明进行了详细的说明,本领域的普通技术人员应当理解:其依然可以对前述各实施例所记载的技术方案进行修改,或者对其中部分或者全部技术特征进行等同替换;而这些修改或者替换,并不使相应技术方案的本质脱离本发明各实施例技术方案的范围。

- 芯片封装结构的制作方法、芯片封装结构及半导体器件

- 一种芯片封装结构的制作方法及芯片封装结构