芯片封装结构及其制作方法

文献发布时间:2023-06-19 12:02:28

技术领域

本发明涉及一种封装结构及其制作方法,且特别涉及一种芯片封装结构及其制作方法。

背景技术

在熟知的无核心制程中,是先以黏着胶或用镀铜封边方式结合局部的载板的边缘与局部的线路板的边缘。另一习知做法为用一内含玻纤布的薄基板(厚度例如是100微米),双面各接着一片铜箔以及附着于其上的可剥除的超薄铜箔(厚度例如是3微米至5微米)作为载板。在线路板经过多道制程后,切除载板与线路板之间具有黏着胶或镀铜封边的部分,以获得用于封装制程的线路板。然而,在熟知的无核心制程中,部分的载板与部分的线路板需切除,因此,将缩小线路板的尺寸且切除后的载板无法重复使用,导致制造成本增加。

为了解决上述的问题,习知以不锈钢板来作为载体的基础,在线路结构的制作过程中,不锈钢板除了能够提供良好的稳定性外,于拆板时不须经过裁切,因此可以重复使用,进而能够有效地节省制造成本。然而,不锈钢板的体积很大也很重,于制作过程中,常常不易搬运,且其边角较为锐利,常会造成基板本身或机台的损坏。

此外,在习知的芯片封装结构的制作方法中,是先在芯片上方压合或压贴介电层,其例如是预浸料(Prepreg,PP)。接着,利用雷射烧蚀的方式,在介电层内制作通孔(Via)并连接芯片的电极,以完成扇出型封装结构(Fan out packaging structure)。然而,透过介电层而制作出的扇出型封装,在结构上与制程上较为复杂,且成本较高。

发明内容

本发明是针对一种芯片封装结构及其制作方法,其在制作上较为安全且简便,且可有效降低制造成本及提升产品良率。

根据本发明的实施例,芯片封装结构的制作方法包括以下步骤。提供载板。载板具有容置凹槽且包括基材以及溅镀于基材上的不锈钢层。配置芯片于载板的容置凹槽内。芯片具有彼此相对的主动表面与背面以及设置于主动表面上的多个电极。形成线路结构层于载板上,其中线路结构层包括图案化线路以及多个导电通孔。图案化线路透过导电通孔与芯片的电极电性连接。形成封装胶体以覆盖芯片的主动表面及线路结构层,其中芯片的主动表面与封装胶体的底面共平面。移除载板以暴出线路结构层。

在根据本发明的实施例的芯片封装结构的制作方法中,基材的材料包括片状的玻纤树脂基材、卷状的玻纤树脂基材或卷状的不锈钢基材。

在根据本发明的实施例的芯片封装结构的制作方法中,还包括:配置芯片于载板的容置凹槽内之前,形成金属层于不锈钢层上。移除载板时,同时移除金属层。

在根据本发明的实施例的芯片封装结构的制作方法中,形成线路结构层于载板上的步骤,包括:形成第一图案化光致抗蚀剂层于金属层上。第一图案化光致抗蚀剂层暴露出芯片的电极及部分金属层。溅镀第一金属层及第一金属层上的第二金属层于第一图案化光致抗蚀剂层上,以及其所暴露出的芯片的电极及金属层上。形成第二图案化光致抗蚀剂层于第二金属层上,其中第二图案化光致抗蚀剂层位于第一图案化光致抗蚀剂层的上方,且暴露出部分第二金属层。进行电镀程序,以于第二图案化光致抗蚀剂层上,以及其所暴露出的第二金属层上形成导电材料层。移除第一图案化光致抗蚀剂层、第二图案化光致抗蚀剂层、部分第一金属层及部分第二金属层,而形成线路结构层且暴露出金属层。线路结构层的图案化线路包括多个内引脚及多个外引脚。内引脚彼此分离且位于芯片的上方。外引脚连接内引脚且延伸配置于金属层上。

在根据本发明的实施例的芯片封装结构的制作方法中,封装胶体覆盖部分金属层与芯片的主动表面,且包覆内引脚与导电通孔。

在根据本发明的实施例的芯片封装结构的制作方法中,还包括:于移除载板时,暴露出于芯片的背面以及其上的金属层。形成表面处理层于芯片的背面上的金属层上。

在根据本发明的实施例的芯片封装结构的制作方法中,载板还具有多个凹口,其中凹口环绕容置凹槽,而不锈钢层与基材共形设置。

在根据本发明的实施例的芯片封装结构的制作方法中,还包括:配置芯片于载板的容置凹槽内之前,形成金属层于不锈钢层上。金属层填满凹口而定义出多个导电凸块。移除载板时,同时暴露出位于封装胶体的底面上的导电凸块以及芯片的背面上的部分金属层。

在根据本发明的实施例的芯片封装结构的制作方法中,形成线路结构层于载板上的步骤,包括:形成第一图案化光致抗蚀剂层于金属层上。第一图案化光致抗蚀剂层暴露出芯片的电极及部分金属层。溅镀第一金属层及第一金属层上的第二金属层于第一图案化光致抗蚀剂层上,以及其所暴露出的芯片的电极及金属层上。形成第二图案化光致抗蚀剂层于第二金属层上,其中第二图案化光致抗蚀剂层位于第一图案化光致抗蚀剂层的上方,且暴露出部分第二金属层。进行电镀程序,以于第二图案化光致抗蚀剂层上,以及其所暴露出的第二金属层上形成导电材料层。移除第一图案化光致抗蚀剂层、第二图案化光致抗蚀剂层、部分第一金属层及部分第二金属层,而形成线路结构层且暴露出金属层。

在根据本发明的实施例的芯片封装结构的制作方法中,封装胶体覆盖金属层及芯片的主动表面,且包覆图案化线路与导电通孔。

在根据本发明的实施例的芯片封装结构的制作方法中,还包括:移除载板之后,形成表面处理层于导电凸块的周围表面以及位于芯片的背面上的金属层上。

根据本发明的实施例,芯片封装结构包括线路结构层、芯片以及封装胶体。线路结构层包括图案化线路以及多个导电通孔。芯片具有彼此相对的主动表面与背面以及设置于主动表面上的多个电极。图案化线路透过导电通孔与芯片的电极电性连接。封装胶体覆盖芯片的主动表面及线路结构层,其中芯片的主动表面与封装胶体的底面共平面。

在根据本发明的实施例,芯片封装结构的图案化线路包括多个内引脚及多个外引脚。内引脚彼此分离且位于芯片的上方。封装胶体包覆内引脚与导电通孔,而外引脚连接内引脚且延伸至封装胶体外。

在根据本发明的实施例,芯片封装结构还包括表面处理层,配置于芯片的背面及连接背面与主动表面的侧表面上的金属层上。

在根据本发明的实施例,芯片封装结构还包括多个导电凸块,配置于封装胶体的底面上,且透过导电通孔与图案化线路电性连接。

在根据本发明的实施例,芯片封装结构还包括表面处理层,配置于芯片的背面及连接背面与主动表面的侧表面上的金属层上以及导电凸块的周围表面上。

基于上述,在本发明的芯片封装结构的制作方法中,是透过溅镀的方式来形成不锈钢层于载板的基材,因此在线路结构层的制作过程中,能够提供良好的稳定性。再者,透过溅镀方式所形成的不锈钢层,相较于习知的不锈钢板而言,可具有较小的体积与重量,并保持不锈钢膜与其上镀铜膜可以用机械方式分离的特性,且在操作上较为安全且简便。此外,分离载板以暴露出线路结构层时不须经过裁切,因此载板可以重复使用,进而能够有效地节省制造成本。

为让本发明的上述特征和优点能更明显易懂,下文特举实施例,并配合所附附图作详细说明如下。

附图说明

包含附图以便进一步理解本发明,且附图并入本说明书中并构成本说明书的一部分。附图说明本发明的实施例,并与描述一起用于解释本发明的原理。

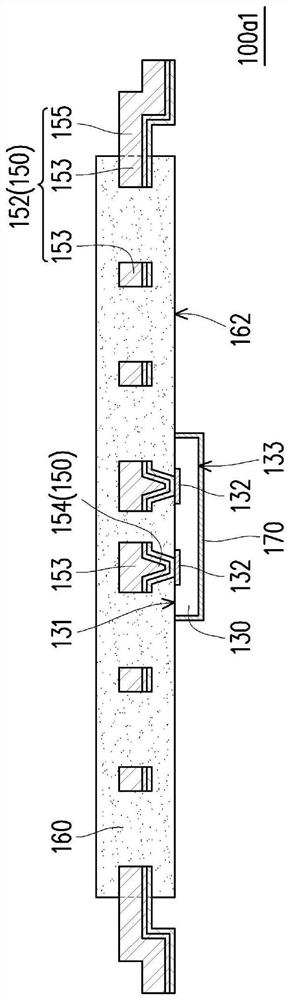

图1A至图1I绘示为本发明的一实施例的一种芯片封装结构的制作方法的剖面示意图;

图1J绘示为本发明的一实施例的一种芯片封装结构的剖面示意图;

图2A至图2I绘示为本发明的另一实施例的一种芯片封装结构的制作方法的剖面示意图;

图2J绘示为本发明的另一实施例的一种芯片封装结构的剖面示意图。

附图标号说明

100a1、100a2、100b1、100b2:芯片封装结构;

110a、110b:载板;

112、112’:基材;

114、114’:不锈钢层;

120、120’、170:金属层;

130:芯片;

131:主动表面;

132:电极;

133:背面;

135:侧表面;

140:第一金属层;

145:第二金属层;

150、150’:线路结构层;

150a:导电材料层;

152、152’:图案化线路;

153:内引脚;

154、154’:导电通孔;

155:外引脚;

160、160’:封装胶体;

162、162’:底面;

170’、172:表面处理层;

C、C’:容置凹槽;

C1:凹口;

P1、P1’:第一图案化光致抗蚀剂层;

P2、P2’:第二图案化光致抗蚀剂层;

S:周围表面;

T:导电凸块。

具体实施方式

现将详细地参考本发明的示范性实施例,示范性实施例的实例说明于附图中。只要有可能,相同元件符号在图式和描述中用来表示相同或相似部分。

图1A至图1I绘示为本发明的一实施例的一种芯片封装结构的制作方法的剖面示意图。关于本实施例的芯片封装结构的制作方法,首先,请参考图1A,提供载板110a,其中载板110a具有容置凹槽C且包括基材112以及溅镀于基材112上的不锈钢层114。此处,基材112可由玻纤树脂基板及配置于玻纤树脂基板相对两侧的铜箔所组成硬质基材;或者是,可由卷状的玻纤树脂基板,或是卷状的不锈钢基板;或者是,已电镀有钛层与铜层的玻璃基板,上述皆属于本发明所欲保护的范围。不锈钢层114的材料例如是使用SUS 304或其他适合的型号等,其中不锈钢层114的厚度例如是介于0.05微米至0.5微米之间。换言之,不锈钢层114可视为是不锈钢薄膜。

接着,请再参考图1A,形成金属层120于不锈钢层114上。此处,金属层120与载板110a共形设置,其中金属层120的材质例如是铜,但不以此为限。

接着,请参考图1B,配置芯片130于载板110a的容置凹槽C内,其中芯片130具有彼此相对的主动表面131与背面133以及设置于主动表面131上的多个电极132。此处,芯片130是位于对应于载板110a的容置凹槽C的金属层120上,且电极132的材质例如是铝,但不以此为限。

接着,请参考图1C,形成第一图案化光致抗蚀剂层P1于金属层120上,其中第一图案化光致抗蚀剂层P1暴露出芯片130的电极132及部分金属层120。

接着,请参考图1D,溅镀第一金属层140及第一金属层140上的第二金属层145于第一图案化光致抗蚀剂层P1上,以及其所暴露出的芯片130的电极132及金属层120上。此处,第一金属层140例如是钛层,而第二金属层145例如是铜层;或者是,第一金属层140例如是铬层,而第二金属层145例如是铜层。

接着,请参考图1E,形成第二图案化光致抗蚀剂层P2于第二金属层145上,其中第二图案化光致抗蚀剂层P2位于第一图案化光致抗蚀剂层P1的上方,且暴露出部分第二金属层145。此处,第一图案化光致抗蚀剂层P1的图案不同于第二图案化光致抗蚀剂层P2的图案。

接着,请参考图1F,以第二金属层145作为电镀种子层,进行电镀程序,以于第二图案化光致抗蚀剂层P2上,以及其所暴露出的第二金属层145上形成导电材料层150a。

接着,请同时参考图1F与图1G,移除第一图案化光致抗蚀剂层P1、第二图案化光致抗蚀剂层P2、部分第一金属层140及部分第二金属层145,而形成线路结构层150且暴露出金属层120。至此,已形成线路结构层150于载板110a上,其中线路结构层150包括图案化线路152以及多个导电通孔154,而图案化线路152透过导电通孔154与芯片130的电极132电性连接。此处,线路结构层150的图案化线路152包括多个内引脚153及多个外引脚155,其中内引脚153彼此分离且位于芯片130的上方,而外引脚155连接内引脚153且延伸配置于金属层120上。此外,导电通孔154是由剩下的第一金属层140、剩下的第二金属层145及部分导电材料层150a所构成。由上述的内容可得知,本实施例未使用介电层来制作线路结构层,而是在去除光致抗蚀剂后,即会使线路的部分悬空而形成空气桥(Air bridge)结构,此时线路结构层150可视为一种导线架。

之后,请参考图1H,形成封装胶体160以覆盖芯片130的主动表面131及线路结构层150,其中芯片130的主动表面131与封装胶体160的底面162共平面。此处,封装胶体160覆盖部分金属层120与芯片130的主动表面131,且包覆内引脚153与导电通孔154。

最后,请同时参考图1H与图1I,移除载板110a及部份金属层120,以暴出封装胶体160的底面162。此处,移除载板110a的方式例如是封装胶体160朝下放置于一真空平台(未绘示)上,利用真空吸附封装胶体160。另外,利用机构固定封装胶体160,且从位在载板110a上的金属层120沿着和不锈钢层114的介面分离。相较于习知的拆除载板的方式,本实施例的载板110a不须经过裁切,因此载板110a可以重复使用,进而能够有效地节省制造成本。此外,移除金属层120的方式例如是蚀刻。至此,已完成导线架型态的芯片封装结构100a1的制作。

在结构上,请再参考图1I,芯片封装结构100a1包括线路结构层150、芯片130以及封装胶体160。线路结构层150包括图案化线路152以及导电通孔154。芯片130具有彼此相对的主动表面131与背面133以及设置于主动表面131上的电极132。图案化线路152包括内引脚153及外引脚155,其中内引脚153彼此分离且位于芯片130的上方,且图案化线路152的内引脚153透过导电通孔154与芯片130的电极132电性连接。封装胶体160覆盖芯片130的主动表面131及线路结构层150,其中封装胶体160包覆内引脚153与导电通孔154,而外引脚155连接内引脚153且延伸至封装胶体160外。特别是,芯片130的主动表面131与封装胶体160的底面162共平面。

简言之,在本实施例的芯片封装结构100a1的制作方法中,是透过溅镀的方式来形成不锈钢层114于载板110a的基材112,因此在线路结构层150的制作过程中,能够提供良好的稳定性。再者,透过溅镀方式所形成的不锈钢层114,相较于习知的不锈钢板而言,可具有较小的积体与重量,且在操作上较为安全且简便。此外,分离载板100a时不须经过裁切,因此载板100a可以重复使用,进而能够有效地节省制造成本。

图1J绘示为本发明的一实施例的一种芯片封装结构的剖面示意图。本实施例沿用前述实施例的元件标号与部分内容,其中采用相同的标号来表示相同或近似的元件,并且省略了相同技术内容的说明。关于省略部分的说明可参照前述实施例,本实施例不再重复赘述。

请参考图1J,于图1H移除载板110a后,仅移除部分金属层120,但保留芯片130的侧面135及背面133的金属层,成为金属层170。然后,在金属层170上形成表面处理层172于芯片130的背面133上,其中表面处理层172配置于金属层170上。此处,表面处理层172的材质例如是锡,但不以此为限。至此,已完成导线架型态的芯片封装结构100a2的制作。

由于本实施例的芯片封装结构100a2具有设置芯片130的背面133上的金属层170,因此金属层170可直接作为防电磁干扰的屏蔽层。相较于习知须额外设置屏蔽板或接地板而言,本实施例的芯片封装结构100a2可具有较薄的封装厚度且可降低制程费用。

图2A至图2I绘示为本发明的另一实施例的一种芯片封装结构的制作方法的剖面示意图。关于本实施例的芯片封装的制作方法,首先,请参考图2A,提供载板110b,其中载板110b具有容置凹槽C’以及多个环绕容置凹槽C’的凹口C1。载板110b包括基材112’以及溅镀于基材112’上的不锈钢层114’。此处,不锈钢层114’与基材112’共形设置。此处,基材112’可由玻纤树脂基板及配置于玻纤树脂基板相对两侧的铜箔所组成硬质基材;或者是,卷状玻纤树脂基板和卷式不锈钢基板;或者是,已电镀有钛层与铜层的玻璃基板,上述皆属于本发明所欲保护的范围。不锈钢层114’的材料例如是使用SUS 304或其他适合的型号等,其中不锈钢层114’的厚度例如是介于0.05微米至0.5微米之间。换言之,不锈钢层114’可视为是不锈钢薄膜。

接着,请参考图2B,形成金属层120’于不锈钢层114’上,其中金属层120’填满凹口C1而定义出多个导电凸块T。此处,金属层120’的材质例如是铜,但不以此为限。

紧接着,请再参考图2B,配置芯片130于载板110b的容置凹槽C’内,其中芯片130具有彼此相对的主动表面131与背面133以及设置于主动表面131上的多个电极132。此处,芯片130是位于对应于载板110b的容置凹槽C’的金属层120’上,且电极132的材质例如是铝,但不以此为限。

接着,请参考图2C,形成第一图案化光致抗蚀剂层P1’于金属层120’上,其中第一图案化光致抗蚀剂层P1’暴露出芯片130的电极132及部分金属层120’。

接着,请参考图2D,溅镀第一金属层140及第一金属层140上的第二金属层145于第一图案化光致抗蚀剂层P1’上,以及其所暴露出的芯片130的电极132及金属层120’上。此处,第一金属层140例如是钛层,而第二金属层145例如是铜层;或者是,第一金属层140例如是铬层,而第二金属层145例如是铜层。

接着,请参考图2E,形成第二图案化光致抗蚀剂层P2’于第二金属层145上,其中第二图案化光致抗蚀剂层P2’位于第一图案化光致抗蚀剂层P1’的上方,且暴露出部分第二金属层145。此处,第一图案化光致抗蚀剂层P1’的图案不同于第二图案化光致抗蚀剂层P2’的图案。

接着,请参考图2F,以第二金属层145作为电镀种子层,进行电镀程序,以于第二图案化光致抗蚀剂层P2’上,以及其所暴露出的第二金属层145上形成导电材料层150a’。

接着,请同时参考图2F与图2G,移除第一图案化光致抗蚀剂层P1’、第二图案化光致抗蚀剂层P2’、部分第一金属层140及部分第二金属层145,而形成线路结构层150’且暴露出金属层120’。线路结构层150’包括图案化线路152’以及多个导电通孔154’,其中图案化线路152’透过导电通孔154’与芯片130的电极132电性连接。此处,导电通孔154’是由剩下的第一金属层140、剩下的第二金属层145及部分导电材料层150a’所构成。至此,已形成线路结构层150’于载板110b上。

之后,请参考图2H,形成封装胶体160’以覆盖芯片130的主动表面131及线路结构层150’,其中芯片130的主动表面131与封装胶体160’的底面162’共平面。

最后,请同时参考图2H与图2I,移除载板110b时,同时暴露出位于封装胶体160’的底面162’上的导电凸块T以及芯片130的背面133上的部分金属层120’。此处,封装胶体160’覆盖金属层120’及芯片130的主动表面131,且包覆图案化线路152’与导电通孔154’。

此处,移除载板110b的方式例如是封装胶体160’朝下放置于一真空平台(未绘示)上,利用真空吸附封装胶体160’。另外,利用机构固定封装胶体160’,且从位在载板110b上的金属层120’沿着和不锈钢层114的介面分离。相较于习知的拆除载板的方式,本实施例的载板110b不须经过裁切,因此载板110b可以重复使用,进而能够有效地节省制造成本。此外,移除金属层120’的方式例如是蚀刻。至此,已完成四方扁平无外引脚(quad flat no-lead,QFN)型态的芯片封装结构100b1的制作。

在结构上,请再参考图2I,芯片封装结构100b1包括线路结构层150’、芯片130以及封装胶体160’。线路结构层150’包括图案化线路152’以及导电通孔154’。芯片130具有彼此相对的主动表面131与背面133以及设置于主动表面131上的电极132。图案化线路152’透过导电通孔154’与芯片130的电极132电性连接。封装胶体160’覆盖芯片130的主动表面131及线路结构层150’。特别是,芯片130的主动表面131与封装胶体160’的底面162’共平面。此外,本实施例的芯片封装结构100b1还包括导电凸块T,其中导电凸块T配置于封装胶体160’的底面162’上,且透过导电通孔154与图案化线路152’电性连接。

图2J绘示为本发明的一实施例的一种芯片封装结构的剖面示意图。本实施例沿用前述实施例的元件标号与部分内容,其中采用相同的标号来表示相同或近似的元件,并且省略了相同技术内容的说明。关于省略部分的说明可参照前述实施例,本实施例不再重复赘述。

请参考图2J,于图2I的步骤之后,亦可形成表面处理层170’于导电凸块T的周围表面S以及位于芯片130的背面133上的金属层120’上。此处,表面处理层170’的材质例如是锡,但不以此为限。至此,已完成四方扁平无外引脚(QFN)型态的的芯片封装结构100b2的制作。

由于本实施例的芯片封装结构100b2具有配置于芯片130的背面133及连接背面133与主动表面131的侧表面135上以及导电凸块T的周围表面S上的表面处理层170’,因此表面处理层170’可直接作为防电磁干扰的屏蔽层。相较于习知须额外设置屏蔽板或接地板而言,本实施例的芯片封装结构100b2可具有较薄的封装厚度且可降低制程费用。

综上所述,在本发明的芯片封装结构的制作方法中,是透过溅镀的方式来形成不锈钢层于载板的基材,因此在线路结构层的制作过程中,能够提供良好的稳定性。再者,透过溅镀方式所形成的不锈钢层,相较于习知的不锈钢板而言,可具有较小的体积与重量,且在操作上较为安全且简便。此外,分离载板以暴露出线路结构层时不须经过裁切,因此载板可以重复使用,进而能够有效地节省制造成本。另外,在本发明的一些芯片封装结构的实施例中,亦可增设表面处理层来作为防电磁干扰的屏蔽层,可具有较薄的封装厚度且可降低制程费用。

最后应说明的是:以上各实施例仅用以说明本发明的技术方案,而非对其限制;尽管参照前述各实施例对本发明进行了详细的说明,本领域的普通技术人员应当理解:其依然可以对前述各实施例所记载的技术方案进行修改,或者对其中部分或者全部技术特征进行等同替换;而这些修改或者替换,并不使相应技术方案的本质脱离本发明各实施例技术方案的范围。

- 芯片封装结构的制作方法、芯片封装结构及半导体器件

- 一种芯片封装结构的制作方法及芯片封装结构