半导体模块的制造方法

文献发布时间:2023-06-19 12:14:58

技术领域

本发明涉及半导体模块的制造方法。

背景技术

以往,作为存储装置已知有DRAM(Dynamic Random Access Memory,动态随机存取存储器)等易失性存储器(RAM)。DRAM追求运算装置(以下称逻辑芯片)的高性能化、能够应对数据量的增大的大容量化。因此,通过存储器(存储器单元阵列、存储器芯片)的微型化和平面方向地增设单元来实现大容量化。另一方面,由于微型化所带来的对于噪声的脆弱性、晶模面积的增加等,此类大容量化已达极限。

因此,最近开发了通过层叠多个平面的存储器来进行三维化(3D化)从而实现大容量化的技术。提出了例如将两个晶圆层叠的晶圆制造方法(例如参照专利文献1)。

现有技术文献

专利文献

专利文献1:日本特开平11-297650号公报。

发明内容

发明要解决的问题

在专利文献1记载的半导体晶圆的制造方法中,用热熔粘接剂接合两个晶圆。而且,在专利文献1记载的半导体晶圆的制造方法中,两个晶圆在分别被研磨而变薄之后彼此剥离。

然而,在层叠了多个的存储器中,优选层叠的存储器彼此更牢固地接合而不容易分离。与此相对,在专利文献1记载的半导体晶圆的制造方法中,两个晶圆以最终被剥离为前提,因此没有设为难以分离。

此外,各存储器中与其他存储器的接合面的外周侧端部一般形成为朝径向的外侧弯曲的弯曲面。由此,即使相向的存储器的接合面互相接合,各个存储器的接合面的外周侧端部维持彼此分离的状态。因此,与形成为平面的情况相比,层叠的存储器的接合面的外周侧端部形成容易分离的结构。

本发明的目的在于,提供一种能够抑制层叠了的存储器彼此分离的半导体模块的制造方法。

用于解决问题的方案

本发明涉及一种半导体模块的制造方法,所述半导体模块层叠了多个电路模块,所述电路模块具有基板和在所述基板的厚度方向的一个面上配置的布线层,所述半导体模块的制造方法具有:在所述电路模块的外周侧端部形成槽部的步骤,所述槽部在厚度方向贯通所述布线层并到达所述基板的中部;将形成有所述槽部的电路模块组成一对,使彼此的所述布线层相向,并且使所述槽部在厚度方向对齐的步骤;通过接合一对所述电路模块的所述布线层来接合一对所述电路模块的步骤;将在一个所述电路模块的所述基板的面中与配置了所述布线层的配置面相反的反面研磨至超过所述槽部的底面的步骤;将研磨了的一个所述电路模块的比所述槽部更靠外周侧的端部去除的步骤。

此外,在形成所述槽部的步骤中,优选沿着所述布线层的外周形成所述槽部。

此外,在形成所述槽部的步骤中,优选在所述布线层的外周端的径向内侧形成所述槽部。

此外,半导体模块的制造方法优选还具有:将在去除一个所述电路模块的所述端部的步骤中去除了一个所述电路模块的端部的一对所述电路模块作为一组,通过将所述电路模块的研磨后的所述反面彼此接合来将两组所述电路模块彼此接合的步骤;将一个组的所述电路模块的另一个所述电路模块的反面研磨至超过所述槽部的底面的步骤;将研磨了的一个组的所述电路模块的比所述槽部更靠外周侧的端部去除的步骤。

此外,优选的是,在将两组所述电路模块彼此接合的步骤中,进一步在研磨步骤中研磨了的另一个所述电路模块的反面依次接合一个或多个其他组的所述电路模块,在将一个组的所述电路模块研磨的步骤中,进一步在每次接合其他组的所述电路模块时,都将沿着厚度方向配置在最外侧的所述电路模块的反面研磨至超过所述槽部的底面,在去除一个组的所述电路模块的所述端部的步骤中,进一步在每次接合其他组的所述电路模块时,都将研磨了的所述电路模块的比所述槽部更靠外周侧的端部去除。

发明效果

根据本发明,能够提供一种能够抑制层叠了的存储器彼此分离的半导体模块的制造方法。

附图说明

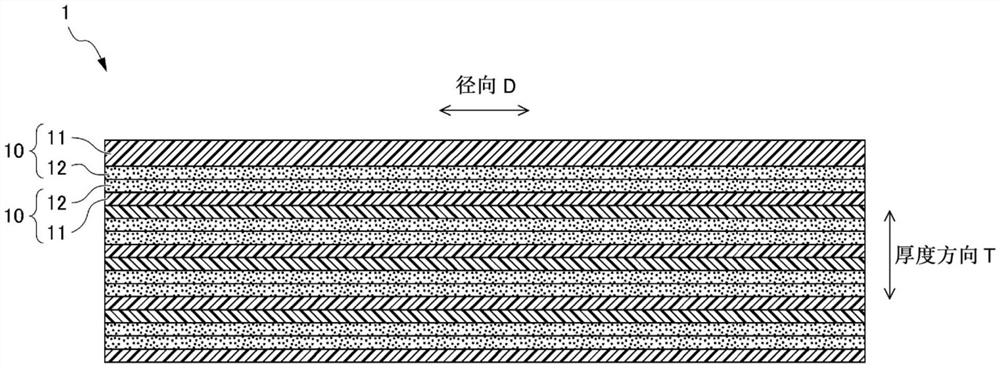

图1示出本发明的一个实施方式涉及的半导体模块的概要侧视图。

图2示出一个实施方式的半导体模块的制造方法的电路模块的概要侧视图。

图3示出在一个实施方式的半导体模块的制造方法中形成有槽部的电路模块的概要侧视图。

图4示出在一个实施方式的半导体模块的制造方法中接合了的一对电路模块的概要侧视图。

图5是在一个实施方式的半导体模块的制造方法中一对电路模块的概要侧视图,示出去除了一个电路模块的端部的概要侧视图。

具体实施方式

以下,参照图1~图5说明本发明涉及的一个实施方式的半导体模块1的制造方法。

首先,参照图1说明通过本实施方式的半导体模块1的制造方法制造的半导体模块1。

半导体模块1是例如构成层叠型DRAM等的芯片。具体地,本实施方式涉及的半导体模块1以层叠的状态构成DRAM等。如图1所示,半导体模块1具有多个电路模块10。半导体模块1是层叠多个电路模块10而构成的。

电路模块10形成为板状。电路模块10具有基板11和布线层12。电路模块10例如是存储器。

基板11例如是Si基板。基板11例如形成为俯视圆形。在本实施方式中,将基板11的厚度方向T的一个面作为配置面来进行说明,此外,在本实施方式中,将基板11的厚度方向T的另一个面(与配置面相反的面)作为反面来进行说明。基板11的反面构成为平面。此外,在本实施方式中,基板11构成为10μm以下的厚度。

布线层12是包含导体层(未图示)和硅氧化膜(未图示)的层。布线层12例如在导体层的周围配置硅氧化膜而形成。在本实施方式中,布线层12配置在基板11的厚度方向T的一个面上。具体地,在本实施方式中,布线层12配置在基板11的配置面上。布线层12的面中与基板11相向的面相反的面构成为平面。

根据上述电路模块10,彼此使布线层12相向而接合的一对电路模块10为一组。此时,布线层12的面中与基板11相向的面相反的面为接合面。即,布线层12彼此的接合面的外周侧端部构成为平面。因此,一对电路模块10的布线层12彼此的接合面的外周侧端部成为平面彼此接合的结构。然后,通过多组电路模块10以基板11的反面互相接合,从而构成半导体模块1。

基板11的反面是与其他组的电路模块10的基板11的接合面。即,基板11的反面的外周侧端部构成为平面。因此,多组电路模块10的基板11彼此的外周侧端部成为平面彼此接合的结构。

接下来,参照图2~图5说明本实施方式涉及的半导体模块1的制造方法。本实施方式涉及的半导体模块1的制造方法具有:形成槽部13的步骤;对齐的步骤;接合一对电路模块10的步骤;研磨一个电路模块10的步骤;去除一个电路模块10的端部的步骤。此外,本实施方式涉及的半导体模块1的制造方法还具有:将两组电路模块10彼此接合的步骤;研磨一个组的电路模块10的步骤;去除一个组的电路模块10的端部的步骤。

首先,实施形成槽部13的步骤。例如,准备如图2所示的在基板11的配置面上配置了布线层12的电路模块10。该电路模块10的基板11和布线层12的外周侧端部构成为弯曲面。然后,如图3所示,在电路模块10的外周侧端部形成槽部13,所述槽部13在布线层12的厚度方向T贯通并到达基板11的中部。具体地,槽部13沿着布线层12的外周形成。此外,槽部13形成在布线层12的外周端的径向D内侧。槽部13例如通过使电路模块10在面内方向旋转,并且使用切割刀100将电路模块10的外周端部沿着外周切削而形成。在本实施方式中,槽部13形成为将从基板11的表面到底面B的深度设为20μm以上。此外,在本实施方式中,槽部13形成在距基板11的外周端2mm以上的径向D的内侧的位置。而且,在本实施方式中,使用宽度为60μm以下的切割刀100来形成槽部13。此外,电路模块10的布线层12在形成槽部13之前例如利用CMP(Chemical Mechanical Polishing,化学机械研磨)研磨至规定的厚度。

接下来,执行对齐步骤。如图4所示,在对齐步骤中,将形成有槽部13的电路模块10组成一对,使彼此的布线层12相向,并且将槽部13在厚度方向T对齐。由此,一对电路模块10的各自的槽部13配置为使底面B相向的状态。此外,在一对电路模块10的布线层12中比槽部13更靠外周侧的布线层12配置在彼此相向的位置。

接下来,执行接合一对电路模块10的步骤。在接合一对电路模块10的步骤中,接合一对电路模块10的布线层12。由此,槽部13的径向D的内侧的布线层12彼此接合。此外,槽部13的径向D的外侧的布线层12也彼此接合。

接下来,执行研磨一个电路模块10的步骤。在研磨一个电路模块10的步骤中,将一个电路模块10的基板11的面中与布线层12布线的配置面相反的反面研磨至超过槽部13的底面B。

接下来,执行去除一个电路模块10的端部的步骤。如图5所示,在去除一个电路模块10的端部的步骤中,将研磨了的电路模块10的比槽部13更靠外周侧的端部去除。由此,去除一个电路模块10的基板11以及布线层12的外周侧端部。另外,布线层12的外周侧端部彼此以弯曲面接合。因此,一个电路模块10的布线层12虽然与另一个电路模块10的布线层12接合,但能够从另一个电路模块10的布线层12分离。

接下来,执行将两组电路模块10彼此接合的步骤。具体地,将在去除端部的步骤中去除了一个电路模块10的端部的一对电路模块10作为一组,通过将研磨了的电路模块10的反面接合来将两组电路模块10彼此接合。

接下来,执行研磨一个组的电路模块10的步骤。具体地,将一个组的电路模块10的另一个电路模块10的反面研磨至超过槽部13的底面B。

接下来,执行去除一个组的电路模块10的端部的步骤。具体地,将研磨了的一个组的电路模块10的比槽部13更靠外周侧的端部去除。

通过重复将两组电路模块10彼此接合的步骤、研磨一个组的电路模块10的步骤以及去除一个组的电路模块10的端部的步骤,将规定数量的组的电路模块10层叠。具体地,在将两组电路模块10彼此接合的步骤中,在研磨步骤中研磨了的另一个电路模块10的反面依次接合一个或多个其他组的电路模块10。

在将一个组的电路模块10研磨的步骤中,在每次接合其他组的电路模块10时,都将沿着厚度方向T配置在外侧的电路模块10的基板11的反面研磨至超过槽部13的底面B。即,将厚度方向T两端的任意一个电路模块10的反面研磨至超过槽部13的底面B。

在去除一个组的电路模块10的端部的步骤中,在每次接合其他组的电路模块10时,都将研磨了的电路模块10的比槽部13更靠外周侧的端部去除。另外,在层叠了规定数量的组的电路模块10的情况下,在将一个组的电路模块10研磨的步骤中,将厚度方向T的两端的电路模块10的基板11的反面研磨至超过槽部13的底面B。在去除一个组的电路模块10的端部的步骤中,将研磨了的两端的电路模块10的比槽部13更靠外周侧的端部。

根据如上所述的第一实施方式涉及的半导体模块1的制造方法,起到以下的效果。

(1)一种半导体模块1的制造方法,为层叠了多个电路模块10的半导体模块1的制造方法,多个电路模块10具有基板11和在基板11的厚度方向T的一个面上配置的布线层12,半导体模块1的制造方法具有:在电路模块10的外周侧端部形成槽部13的步骤,槽部13在厚度方向T贯通布线层12并到达基板11的中部;将形成有槽部13的电路模块10组成一对,使彼此的布线层12相向,并且使槽部13在厚度方向T对齐;通过接合一对电路模块10的布线层12来接合一对电路模块10的步骤;将在一个电路模块10的基板11的面中与配置了布线层12的配置面相反的反面研磨至超过槽部13的底面B的步中路;将研磨了的一个电路模块10的比槽部13更靠外周侧的端部去除的步骤。由此,布线层12的接合面的外周侧的端部能以平面彼此接合。与接合了的布线层12的外周侧的端部仍为弯曲面状态的情况相比,能够更牢固地接合布线层12。因此,能够抑制层叠的存储器(电路模块10)彼此分离,能够提高半导体模块1的成品率。

(2)在形成槽部13的步骤中,槽部13沿着布线层12的外周形成。由此,能够去除布线层12的弯曲面,且能够使布线层12的弯曲面的去除位置最优化。即,能够减少布线层12的弯曲面以外的平面的去除量。

(3)在形成槽部13的步骤中,槽部13形成在布线层12的外周端的径向D内侧。由此,能够以配置在比槽部13更靠外周侧的布线层12彼此接合的状态研磨电路模块10。因此,在电路模块10的研磨中,能够抑制电路模块10的端部的破裂等,能够提高半导体模块1的成品率。此外,即使在将基板11研磨至超过槽部13的底面B的情况下,一个电路模块10的外周侧端部也维持与另一个电路模块10的布线层12接合的状态。因此,由于能够抑制一个电路模块10的外周侧端部飞散,从而能够抑制灰尘分散。

(4)半导体模块1的制造方法还具有:将在去除端部的步骤中去除了一个电路模块10的端部的一对电路模块10组成一组,通过将研磨了的电路模块10的反面接合来将两组电路模块10彼此接合的步骤;将一个组的电路模块10的另一个电路模块10的反面研磨至超过槽部13的底面B的步骤;将研磨了的一个组的电路模块10的比槽部13更靠外周侧的端部去除的步骤。由此,由于能够在一组电路模块10接合另一组电路模块10,能够得到层叠数更多的半导体模块1。

(5)在将两组电路模块10彼此接合的步骤中,进一步在研磨步骤中研磨了的另一个电路模块10的反面依次接合一个或多个其他组的电路模块10,在将一个组的电路模块10研磨的步骤中,进一步在每次接合其他组的电路模块10时,都将沿着厚度方向T配置在最外侧的电路模块10的反面研磨至超过槽部13的底面B,在去除一个组的电路模块10的端部的步骤中,进一步在每次接合其他组的电路模块10时,都将研磨了的电路模块10的比槽部13更靠外周侧的端部去除。由此,能够层叠任意组的电路模块10。即使在增加了层叠的电路模块10的情况下,也能够抑制层叠的存储器(电路模块10)彼此分离。

以上,对本发明的半导体模块的制造方法的优选的各实施方式进行了说明,但本发明不限于上述实施方式,能够适当变更。

例如,在上述实施方式中,层叠的电路模块10的数量能够任意设定。例如,在层叠两片电路模块10的情况下,在研磨一个电路模块10的步骤中,能通过研磨一对电路模块10的双方的基板11的反面来制造半导体模块1。此外,在层叠两组以上电路模块10的情况下,也可以研磨厚度方向T的两端的任意电路模块10。在此情况下,能够将追加接合的组的电路模块10的反面进一步接合在研磨了的电路模块10的基板11的反面。

此外,在上述实施方式中,将电路模块10作为俯视圆形进行了说明,但是不限于此。例如,电路模块10能形成为俯视方形等任意形状。在此情况下,槽部13也沿着电路模块10的外周侧端部形成。

此外,在上述实施方式中,作为半导体模块1的一个例子说明了DRAM,但是不限于此。半导体模块1可以是SRAM、广泛而言包含非易失性RAM(例如MRAM、ReRAM、FeRAM等)的所有RAM(Random Access Memory,随机存取存储器)。此外,也可以是MPU、ASIC、FPGA等逻辑元件。

附图标记说明

1:半导体模块

10:电路模块

11:基板

12:布线层

13:槽部

B:底面

D:径向

T:厚度方向

- 半导体模块制造方法、电子装置制造方法、半导体模块和电子装置

- 用于制造散热板的方法、散热板、用于制造半导体模块的方法及半导体模块