存储装置以及相关闪存控制器

文献发布时间:2023-06-19 12:18:04

技术领域

本发明是关于一存储装置,尤指一种存储装置的故障转移(failover)机制。

背景技术

固态硬盘(solid-state drive,SSD)是一种使用集成电路组件来存储数据的存储装置,而且固态硬盘在企业应用诸如数据中心(data center)中变得相当热门。为了在企业应用中提供更高的可用性,系统通常具有故障转移机制以容许两个主装置或两个服务器去存取固态硬盘,也就是说若因为操作系统崩溃或是硬盘损坏等问题造成主要(primary)服务器存取固态硬盘失败,待命的服务器能立即取代主服务器以避免服务中断。

传统的故障转移机制使用双端口(dual-port)固态硬盘以容许两个服务器同时存取,然而,双端口固态硬盘具有两个闪存控制器在内部,且相当昂贵。因此,为了降低制造成本,带有快捷外设互连(Peripheral Component Interconnect Express,简称PCIe)开关的单端口(single-port)固态硬盘可被用来取代双端口固态硬盘的功能,然而,PCIe开关相当昂贵,且PCIe开关的尺寸太大而难以装进单端口固态硬盘中。因此,如何使用单端口固态硬盘来提供故障转移机制遂成为热门的议题。

发明内容

因此,本发明的一目的在于提供一种用于单端口固态硬盘的故障转移机制,并且所述单端口固态硬盘本身不具有用来与两个主装置沟通的PCIe开关,以解决上述问题。

依据本发明一实施例,提供了一种包含有一连接器以及一闪存控制器的存储装置。所述连接器是用来连接一第一主装置以及一第二主装置。所述闪存控制器是用来基于一选择信号选择所述第一主装置及所述第二主装置的其中一者,而所述闪存控制器仅处理来自所述第一主装置及所述第二主装置中被选择的主装置的指令,并且基于所述指令存取一闪存模块。例如,所述存储装置可为一单端口固态硬盘,且所述第一主装置及所述第二主装置不被容许同时通过所述闪存控制器存取所述闪存模块。另外,所述第一主装置在一开始与所述闪存控制器沟通,以及当所述闪存控制器接收到指出所述第二主装置已被选择的所述选择信号时,所述闪存控制器自所述第二主装置接收一参考时钟信号以及一重设信号,而所述闪存控制器被配置成处理来自所述第二主装置的指令,并且停止处理来自所述第一主装置的指令。

依据本发明另一实施例,揭示了一种闪存控制器,其中所述闪存控制器是用来存取一闪存模块,且所述闪存控制器是内建于一单端口固态硬盘。所述闪存控制器包含一存储器以及一微处理器,其中所述存储器可用来存储一程序代码,以及所述微处理器可用来执行所述程序代码以通过一控制逻辑电路存取所述闪存模块。所述闪存控制器耦接至一第一主装置以及一第二主装置,所述微处理器接收用来自所述第一主装置及所述第二主装置中选择其一的一选择信号,而所述微处理器仅处理来自所述第一主装置及所述第二主装置中的所被选择的主装置的指令,并且基于所述指令存取所述闪存模块,其中所述微处理器不被允许同时处理来自所述第一主装置与第二主装置的指令。另外,所述闪存控制器在一开始与所述第一主装置沟通,以及当所述微处理器接收到指出所述第二主装置已被选择的所述选择信号时,所述微处理器自所述第二主装置接收一参考时钟信号以及一重设信号,而所述微处理器配置所述闪存控制器处理来自所述第二主装置的指令,并且停止处理来自所述第一主装置的指令。

附图说明

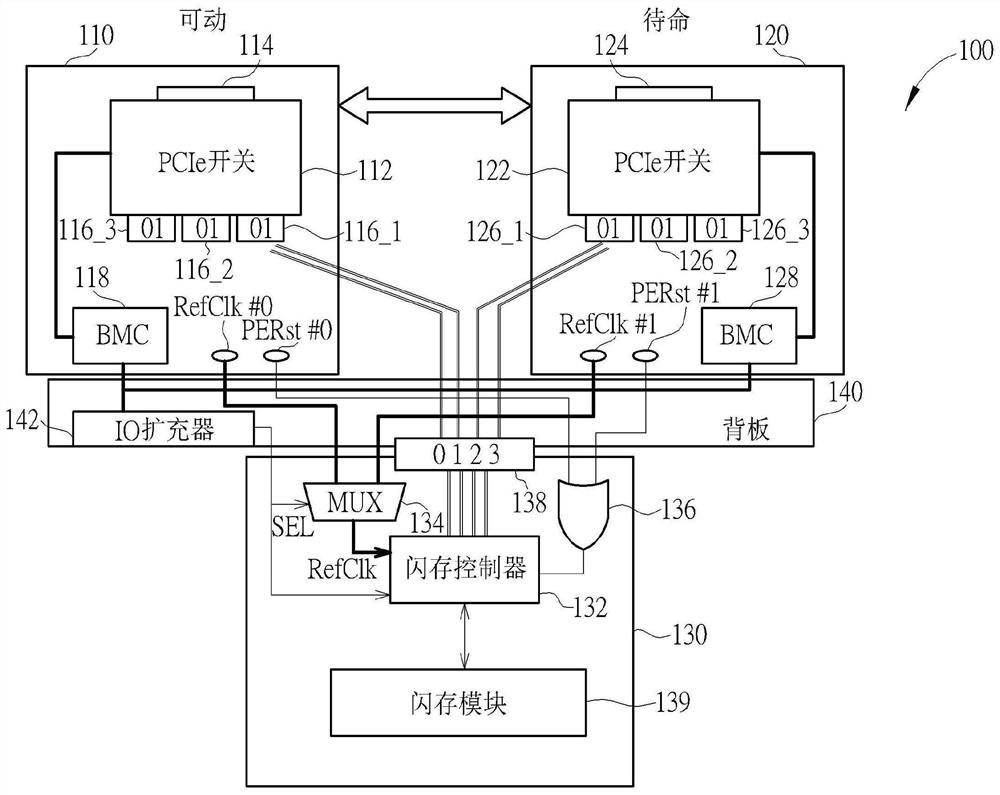

图1为依据本发明一实施例的一系统的示意图。

图2依据本发明一实施例展示所述系统的故障转移过程。

图3为依据本发明一实施例的所述系统的故障转移过程的流程图。

图4为依据本发明一实施例的一闪存控制器的示意图。

其中,附图标记说明如下:

100 系统

110、120 主装置

112、122 PCIe开关

114、124 上游端口

116_1、116_2、116_3、126_1、126_2、126_3 下游端口

118、128 基板管理控制器

130 固态硬盘

132 闪存控制器

134 复用器

136 逻辑电路

138 连接器

139 闪存模块

140 背板

142 IO扩充器

SEL 选择信号

RefClk、RefClk#0、RefClk#1 输出参考时钟信号

PERst#0、PERst#1 重设信号

300,302,304,306,308,310 步骤

412 微处理器

412M 只读存储器

412C 程序码

414 控制逻辑电路

416 随机存取存储器

418 传输接口电路

432 编码器

434 解码器

436 随机化器

438 解随机化器

具体实施方式

图1为依据本发明一实施例的系统100的示意图。如图1所示,系统100包含两个主装置110及120、一存储装置诸如一固态硬盘130、以一及背板(backplane)140。主装置110包含至少一PCIe开关112以及一基板管理控制器(baseboard management controller,BMC)118(在图示中标示为“BMC”以求简明),且PCIe开关112包含一上游(upstream)端口114以及复数个下游(downstream)端口(在本实施例中,PCIe开关112包含三个下游端口116_1~116_3),其中上游端口114是用来连接主装置110中的一处理电路诸如一中央处理单元(central processing unit,CPU),而下游端口116_1~116_3中的每一者是用来将外部的装置连接主装置110。主装置120包含至少一PCIe开关122以及一基板管理控制器128在图示中标示为“BMC”以求简明,且PCIe开关122包含一上游端口124以及复数个下游端口(在本实施例中,PCIe开关122包含三个下游端口126_1~126_3),其中上游端口124是用来连接主装置120中的一处理电路诸如一中央处理单元,而下游端口126_1~126_3中的每一者是用来将外部的装置连接主装置120。固态硬盘130包含一闪存控制器132、一复用器(multiplexer)134(在图示中标示为“MUX”以求简明)、一逻辑电路136、一连接器138以及一闪存模块139,而背板140包含一输出/输入(input/output,简称IO)扩充器142。在本实施例中,系统110可被应用在一数据中心,也就是说固态硬盘130是用来存储并通过局域网络(localarea network,LAN)或互联网输出数据,以及主装置110及120中的一者是用来通过背板140存取固态硬盘130。

在本实施例中,固态硬盘130的连接器138为包含有四个通道(lane)的“8639连接器”或“U.2连接器”,而这些通道中的两个通道(例如通道#0及通道#1)耦接至主装置110的下游端口116_1,并且其他两个通道(例如通道#2及通道#3)耦接至主装置120的下游端口126_1。固态硬盘130是一个单端口固态硬盘,也就是说固态硬盘130仅有一个闪存控制器132,并且仅有闪存控制器132被容许接收来自主装置110/120的指令(例如读取指令或写入指令)以存取闪存模块139。需注意的是闪存控制器132可为安装在固态硬盘130中的一印刷电路板(printed circuit board,PCB)上的一单封装(single package),并且这个单封装仅包含一个用于存取闪存模块139的裸晶。换言之,在固定硬盘130作为所述单端口固态硬盘的情形下,固态硬盘130不能同时被主装置110及120存取,也就是说固态硬盘130在同一时间仅接收来自一个主装置110/120(主装置110及120的其中一者)的指令。在本实施例中,闪存控制器132被配置成于同一时间仅使用所述四个通道中的其中两者来与主装置110/120(主装置110及120的其中一者)沟通,例如,闪存控制器132被配置成使用连接器138的通道#0及通道#1的信号/数据。

在系统100的运作中,假设主装置110是正在存取固态硬盘的可动(active)装置而主装置120是无法存取固态硬盘130的待命装置,基板管理控制器118是用来控制IO扩充器142以生成一选择信号SEL给复用器134以及闪存控制器132。此时,主装置110生成一参考时钟信号RefClk#0以及一重设信号PERst#0,而复用器134依据选择信号SEL选择参考时钟信号RefClk#0作为一输出参考时钟信号RefClk,并且闪存控制器132使用输出参考时钟信号RefClk来执行其运作;而闪存控制器132另通过逻辑电路136接收PERst#0以重设其内部配置。另外,闪存控制器132另自复用器134接收选择信号SEL以得知主装置110及120的哪一者是可动的,以供闪存控制器132进行适当的配置。需注意的是主装置120(待命装置)不会生成一参考时钟信号RefClk#1以及一重设信号PERst#1。在闪存控制器132的配置被重设后,主装置110的中央处理单元能通过PCIe开关112的上游端口114以及下游端口116_1、以及连接器138将指令发送至闪存控制器132,并且闪存控制器132依据来自主装置110的指令存取闪存模块139。此时,因为闪存控制器132被配置成仅使用通道#0及通道#1来与主装置110沟通,因此通道#2及通道#3是被除能的(disable)(也就是说闪存控制器132不处理对应于通道#2及通道#3的信号)。

在图1所示的实施例中,若主装置110突然存取固态硬盘130失败,例如,因为主装置110的操作系统崩溃、主装置110内的硬盘损坏、下游端口116_1被除能、或任何其他失败原因,系统100能立即执行故障转移机制,即主装置120取代主装置110。特别是,参照图2,因为主装置110及120总是互相沟通,主装置120能检测主装置110是否可以存取固态硬盘130,例如,主装置120自主装置110接收到指出一故障转移指令的一特别信号、及/或主装置120未接收到周期性地自主装置110发送的信号、及/或主装置120发送一信号至主装置110但并未接收到回复、或是任意其他错误检测机制,主装置120能判断出主装置110存取固态硬盘130失败。一旦主装置120判断主装置110存取固态硬盘130失败,主装置120的中央处理单元通知基板管理控制器128以和基板管理控制器118沟通已尝试除能PCIe开关112的下游端口116_1,并且主装置120的中央处理单元通知基板管理控制器128以控制IO扩充器142以生成指出主装置120已被选择的选择信号SEL给复用器134以及闪存控制器132。此时,主装置120生成参考时钟信号RefClk#1以及重设信号PERst#1,并且复用器134依据选择信号SEL选择参考时钟信号RefClk#1以作为所述输出参考时钟信号RefClk,而闪存控制器132使用所述参考时钟信号RefClk执行其运作;而闪存控制器132另通过逻辑电路136接收重设信号PERst#1以重设其内部配置。另外,闪存控制器132另自复用器134接收选择信号SEL以得知主装置120成为可动装置而主装置110成为待命装置,以供闪存控制器132进行适当的配置。需注意的是主装置110(待命装置)不会生成参考时钟信号RefClk#0以及重设信号PERst#0。在PCIe开关112的下游端口116_1被除能后,主装置120致能(enable)PCIe开关112的下游端口126_1。需注意的是,因为闪存控制器132被配置成仅使用连接器138的通道#0及通道#1,且主装置120原本对应于连接器138的通道#2及通道#3,因此闪存控制器可进行一通道反转运作以成功地和主装置120沟通。也就是说,在连接器138中的对应于原来的通道#0的引脚(pin)被配置成对应于通道#3,在连接器138中的对应于原来的通道#1的引脚被配置成对应于通道#2,在连接器138中的对应于原来的通道#2的引脚被配置成对应于通道#1,以及在连接器138中的对应于原来的通道#3的引脚被配置成对应于通道#0。另外,PCIe开关122的下游端口126_1的通道被配置成对应于连接器138的通道,例如,PCIe开关122可发送训练信号至闪存控制器132以判断这些通道是否匹配(match),若这些通道不匹配,PCIe开关122也可执行通道反转运作以使在下游端口126_1中的对应于原来的通道#0的引脚被配置成对应于通道#1,以及在下游端口126_1中的对应于原来的通道#1的引脚被配置成对应于通道#0。在闪存控制器132以及PCIe开关122的配置被重设后,主装置120的中央处理单元能通过PCIe开关122的上游端口124以及下游端口126_1、以及连接器138将指令发送至闪存控制器132,并且闪存控制器132依据来自主装置120的指令存取闪存模块139。

另外,因为闪存控制器132总是被配置成仅使用通道#0及通道#1来和主装置110/120沟通,其他的通道诸如通道#2及通道#3应被控制为除能的以避免固态硬盘130的错误运作。在一实施例中,通道#2及通道#3可被主装置110/120除能。在另一实施例中,通道#2及通道#3可被闪存控制器132除能,例如,若闪存控制器132接收到的选择信号SEL指出主装置110是可动的,且上述通道被配置成如图1所示,闪存控制器132直接致能通道#0及通道#1并且除能通道#2及通道#3;而若闪存控制器132接收到的选择信号SEL指出主装置120是可动的且上述通道原本被配置成如图1所示,闪存控制器132首先进行通道反转运作已将上述通道配置成如图2所示,并且在通道反转运作完成后接着致能通道#0及通道#1并且除能通道#2及通道#3。

综上所述,藉由增加复用器134并且将闪存控制器132设计成具有上述故障转移机制,系统100能单纯地使用固态硬盘130(单端口固态硬盘)达到高可用性的目的,而且固态硬盘130不具有任何PCIe开关在其内。因此,本发明的实施例中的系统100中的固态硬盘130具有较高的可用性以及较低的制造成本。

图3为依据本发明一实施例的系统100的故障转移过程的流程图。参考上述实施例,所述流程如下所述。

步骤300:流程开始。

步骤302:一第一主装置充当一可动装置而一第二主装置充当一待命装置,并且所述第一主装置存取一固态硬盘。

步骤304:所述第二主装置判断所述第一主装置无法存取所述固态硬盘,并且所述第二主装置除能所述第一主装置的下游端口。

步骤306:所述第二主装置控制所述固态硬盘使用来自所述第二主装置的一参考时钟。

步骤308:所述第二主装置发送一重设信号以重设所述固态硬盘的一闪存控制器。

步骤310:所述第二主装置致能PCIe开关的下游端口,并且开始存取固态硬盘。

图4为依据本发明一实施例的闪存控制器132的示意图。如图1所示,闪存控制器132可包含一处理电路诸如一微处理器412、一存储单元诸如一只读存储器(read-onlymemory,ROM)412M、一控制逻辑电路414、一随机存取存储器(random-access memory,RAM)416、以及一传输接口电路418,其中以上组件可通过一总线互相耦接。随机存取存储器416是由一静态随机存取存储器(Static RAM,SRAM)来实施,但本发明不限于此。随机存取存储器416可用来提供内部存储空间给闪存控制器132,例如,随机存取存储器416可被用来当作一缓冲存储器以供缓冲数据。另外,本实施例中的只读存储器412M是用来存储一程序码412C,而微处理器412是用来执行程序码412C以控制闪存模块139的存取。请注意,在某些例子中,程序码412C可被存储在随机存取存储器416或任何类型的存储器中。此外,控制逻辑电路414可用来控制闪存模块139,并且可包含一编码器432、一解码器434、一随机化器(randomizer)436、一解随机化器(de-randomizer)438以及其他电路。传输接口电路418可符合一特定通信标准(例如串行高级技术附件(Serial Advanced TechnologyAttachment,简称串行ATA或SATA)标准、外设组件互联(Peripheral ComponentInterconnect,简称PCI)标准、PCIe标准、通用快闪存储(Universal Flash Storage,简称UFS)标准等),并且可依据所述特定通信标准进行通信,例如通过连接器138来和主装置110/120进行通信。

在本实施例中,因为固态硬盘130仅包含一个包含有图4所示的组件的闪存控制器132,沟通于主装置110/120与闪存模块139之间的全部指令或数据均必须要通过图4所示的由微处理器412控制的原件处理,且闪存模块139的全部区域均是配置成由单一的闪存控制器139来存取。

总结来说,在本发明的系统中,藉由提供固态硬盘中的复用器并且设计闪存控制器以具有上述故障转移机制,所述系统能单纯地使用单端口固态硬盘达成高可用性的目的,并且固态硬盘不具有任何PCIe开关在其内。因此,系统100中的固态硬盘具有较高的可用性以及较低的制造成本。

以上所述仅为本发明的优选实施例而已,并不用于限制本发明,对于本领域的技术人员来说,本发明可以有各种更改和变化。凡在本发明的精神和原则之内,所作的任何修改、等同替换、改进等,均应包含在本发明的保护范围之内。

- 存储装置以及相关闪存控制器

- 闪存存储装置中闪存控制器与闪存芯片之间的连接方法