电压检测电路以及上电复位电路

文献发布时间:2023-06-19 12:21:13

相关申请

本申请享受以日本专利申请2020-30941号(申请日:2020年2月26日)为基础申请的优先权。本申请通过参照该基础申请而包含基础申请的所有内容。

技术领域

本发明的一实施方式涉及电压检测电路以及上电复位电路。

背景技术

具有伴随着细微化而以2V以下的低电压驱动的存储器芯片、信号处理芯片。

发明内容

本发明将要解决的课题在于,提供能够以简易的电路构成、高精度地检测电压的电压检测电路以及上电复位电路。

实施方式的电压检测电路具备:串联连接于电源电压节点与基准电压节点之间的第一晶体管以及第一电阻;串联连接于电源电压节点与基准电压节点之间的第二晶体管以及第二电阻;串联连接于电源电压节点与基准电压节点之间的第三晶体管以及第三电阻;以及输出与第三晶体管以及第三电阻的连接节点的电压相应的信号的信号生成部,在电源电压节点的电压电平上升的电源接通时,在第一至第三晶体管之中,第二晶体管最先接通,第三晶体管关断,接着,在第一晶体管以及第一电阻中流过电流,第二晶体管关断,并且第三晶体管接通,信号生成部在第三晶体管接通时使信号的逻辑转变。

附图说明

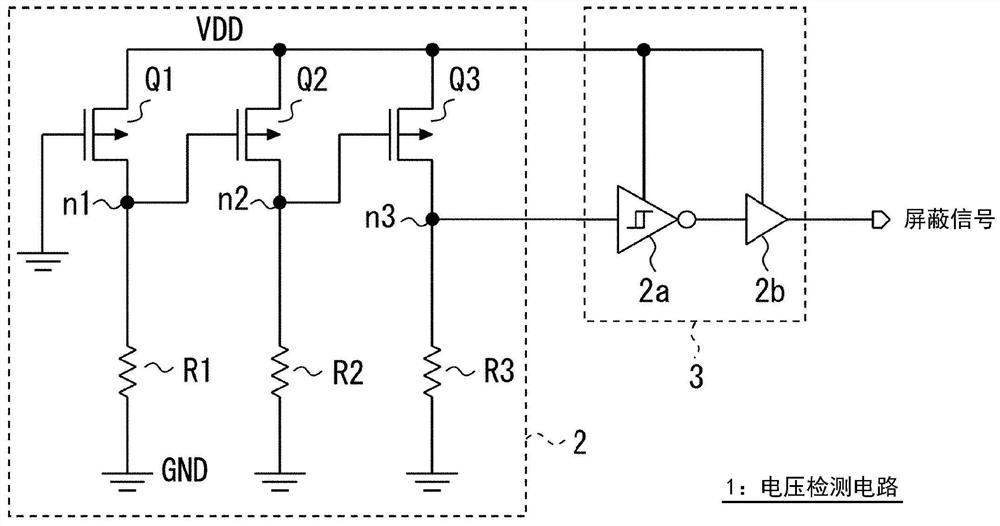

图1是第一实施方式的电压检测电路的电路图。

图2是对图1的电路构成追加了第四晶体管与第四电阻的电压检测电路的电路图。

图3是图2的电压检测电路内的多个节点的电压波形图。

图4是图2的电压检测电路内的多个节点的电流波形图。

图5是第二实施方式的电压检测电路的电路图。

图6是第三实施方式的电压检测电路的电路图。

图7是表示POR电路的一个例子的电路图。

附图标记说明

1电压检测电路,2电压检测部,3信号生成部,11第一屏蔽信号生成部,12第二屏蔽信号生成部,13信号合成部,R1第一电阻,R2第二电阻,R3第三电阻,R4第四电阻,R5第五电阻,Q1第一晶体管,Q2第二晶体管,Q3第三晶体管,Q4第四晶体管。

具体实施方式

以下,参照附图,对电压检测电路的实施方式进行说明。以下,以电压检测电路的主要的构成部分为中心进行说明,但在电压检测电路中可能存在未图示或者说明的构成部分、功能。以下的说明并非排除未图示或者说明的构成部分、功能。

(第一实施方式)

图1是第一实施方式的电压检测电路1的电路图。图1的电压检测电路1生成在后述的上电复位(以下,POR)电路中使用的屏蔽信号。

图1的电压检测电路1具备电压检测部2与信号生成部3。电压检测部2具有第一晶体管Q1~第三晶体管Q3和第一电阻R1~第三电阻R3。

第一晶体管Q1以及第一电阻R1串联连接于电源电压节点VDD与基准电压节点GND之间。第二晶体管Q2以及第二电阻R2串联连接于电源电压节点VDD与基准电压节点GND之间。第三晶体管Q3以及第三电阻R3串联连接于电源电压节点VDD与基准电压节点GND之间。

电源电压节点VDD与基准电压节点GND的具体的电压电平是任意的。以下,主要说明基准电压节点GND为接地节点(例如0V)的例子。

第三晶体管Q3根据第二晶体管Q2以及第二电阻R2的连接节点n2的电压而接通或者关断。第二晶体管Q2根据第一晶体管Q1以及第一电阻R1的连接节点n1的电压而接通或者关断。

在电源接通时,电源电压节点VDD的电压电平逐渐上升。伴随着电源电压节点VDD的电压电平的上升,在第一晶体管Q1~第三晶体管Q3之中,第二晶体管Q2最先接通,第三晶体管Q3关断,接着,在第一晶体管Q1以及第一电阻R1中流过电流,第二晶体管Q2关断,并且第三晶体管Q3接通。

信号生成部3生成屏蔽信号。更具体而言,在第三晶体管Q3接通时,信号生成部3使屏蔽信号的逻辑转变。例如屏蔽信号在电源刚接通之后为高电平,在电源电压VDD的电压电平上升至某种程度时,转变为低电平。以下,对高电平为屏蔽状态、低电平为屏蔽解除状态的情况进行说明。另外,这只是一个例子,也可以是高电平为解除状态,低电平为屏蔽状态。信号生成部3例如具有逻辑反转元件。作为逻辑反转元件,也可以为了避免噪声带来的影响而设置施密特触发型的逆变器2a与缓冲器2b。

图1的电压检测电路1示出了第一晶体管Q1~第三晶体管Q3均为p型MOS晶体管的例子,但也可以由n型MOS晶体管构成第一晶体管Q1~第三晶体管Q3。虽然将使第一晶体管Q1~第三晶体管Q3为n型MOS晶体管的情况下的电路图省略,但连接于电源电压节点VDD与接地节点之间的晶体管Q1~Q3、电阻R1~R3的连接关系与图1相反。以下,主要说明第一晶体管Q1~第三晶体管Q3为p型MOS晶体管的情况。

第一晶体管Q1~第三晶体管Q3的尺寸并不一定相同。例如也可以使第二晶体管Q2的尺寸最大,接着是第三晶体管Q3的尺寸,且使第一晶体管Q1的尺寸最小。这里,尺寸是晶体管的栅极宽度与栅极长度的至少一方的大小。例如栅极宽度越大,晶体管的尺寸越大,晶体管越容易流过更多的电流。如此,通过改变晶体管的尺寸,能够改变每个晶体管的电流的流动容易度。

第一电阻R1~第三电阻R3的电阻值不一定相同。例如可以是,第一电阻R1使电阻值大于第二电阻R2与第三电阻R3,第二电阻R2与第三电阻R3的电阻值设为相同程度。

接下来,对图1的电压检测电路1的动作进行说明。在图1的电压检测电路1的电源电压节点VDD的电压电平从接地电平起逐渐上升的情况下,首先尺寸最大的第二晶体管Q2的栅极-源极间被施加电压,开始在源极-漏极间流过电流,第二晶体管Q2接通。若第二晶体管Q2接通,则第二晶体管Q2的漏极电压(节点n2的电压)上升,第三晶体管Q3关断。通过第三晶体管Q3关断,使得第三晶体管Q3的漏极电压(节点n3的电压)维持接地电平,不再担心从信号生成部3输出的屏蔽信号保持高电平地转变。

之后,若电源电压节点VDD的电压电平进一步上升,则第一晶体管Q1的栅极-源极间电压超过阈值,开始在源极-漏极间流过电流,第一晶体管Q1的漏极电压(节点n1的电压)上升。由此,第二晶体管Q2的栅极电压上升,因此第二晶体管Q2从接通转变为关断。若第二晶体管Q2关断,则第二晶体管Q2的漏极电压(节点n2的电压)、即第三晶体管Q3的栅极电压降低,第三晶体管Q3接通。若第三晶体管Q3接通,则第三晶体管Q3的漏极电压(节点n3的电压)上升,从信号生成部3输出的屏蔽信号从高变化为低。

这里,为了在第一晶体管Q1的源极-漏极间开始流过电流后使第二晶体管Q2可靠地关断,可考虑设置与第一晶体管Q1构成电流反射镜电路的其他晶体管。

图2是对图1的电路构成追加了第四晶体管Q4与第四电阻R4的电压检测电路1a的电路图。图2的电压检测电路1a中的第四晶体管Q4以及第四电阻R4串联连接于电源电压节点VDD(例如电源电压节点VDD)与基准电压节点GND(例如接地节点)之间。

第四晶体管Q4例如可以具有与第一晶体管Q1相同的尺寸。另外,第四电阻R4的电阻值也可以比第一电阻R1小,也可以与第一电阻R1~第三电阻R3为相同程度。

图3是图2的电压检测电路1a内的多个节点的电压波形图,图4是图2的电压检测电路1a内的多个节点的电流波形图。图3的横轴是时间,纵轴是电压[V]。图4的横轴是时间,纵轴是电流[mA]。图3中图示了电源电压节点VDD的波形w1、第一晶体管Q1的漏极电压的波形w2、第二晶体管Q2的漏极电压的波形w3、第三晶体管Q3的漏极电压的波形w4、第四晶体管Q4的漏极电压的波形w5、从信号生成部3输出的屏蔽信号波形w6。图4中图示了第一晶体管Q1的源极-漏极电流波形w7、第二晶体管Q2的源极-漏极电流波形w8、第三晶体管Q3的源极-漏极电流波形w9、第四晶体管Q4的源极-漏极电流波形w10。

接下来,一边参照图3以及图4,一边对图2的电压检测电路1a的动作进行说明。若电源电压节点VDD的电压电平从接地电平起逐渐上升(图3的波形w1),则在尺寸最大的第二晶体管Q2的源极-漏极间流过电流(波形w8),第二晶体管Q2接通。由此,第二晶体管Q2的漏极电压上升(波形w3),第三晶体管Q3关断,第三晶体管Q3的漏极电压维持接地电位(波形w4)。由此,从信号生成部3输出的屏蔽信号成为高电平,并成为与电源电压VDD相应的电压电平。

若电源电压节点VDD的电压电平进一步上升,则第四晶体管Q4与第一晶体管Q1的源极-漏极电流逐渐增大(波形w7、w10),第一晶体管Q1的漏极电压上升,第二晶体管Q2关断,第二晶体管Q2的漏极电压降低(波形W3)。由此,第三晶体管Q3接通,第三晶体管Q3的漏极电压迅速地上升(波形w4)。若第三晶体管Q3接通,则从信号生成部3输出的屏蔽信号降低至接地电平(波形w6)。

如此,在本实施方式中,在电源电压节点VDD的电压电平较低的期间,强制地关断第三晶体管Q3,因此从信号生成部3输出的屏蔽信号持续维持高电平。若电源电压节点VDD的电压电平提高到某种程度,则第三晶体管Q3从关断切换为接通,因此从信号生成部3输出的屏蔽信号转变为低电平,成为屏蔽解除状态。

最近的存储器芯片、信号处理芯片等大多伴随着细微化而以2V以下的低电压驱动。另外,根据芯片内的电路模块,有使用不同的电压电平的电源电压的情况。

在刚对这些芯片接通了电源电压之后,电压电平不稳定,因此设有强制地使各电路模块复位的POR信号。到POR信号成为规定的逻辑而POR状态被解除为止,一般不使芯片内的各电路模块动作。

在生成POR信号的POR电路中,除了设置用于检测电源电压是否到达规定的阈值电压的比较器之外,大多设置有屏蔽信号生成部。屏蔽信号生成部生成防止POR信号的转变的屏蔽信号,直到电源电压电平稳定为止,以便即使在比较器误动作的情况下,POR状态也不会立刻被解除。

然而,若如最近那样,以低电源电压动作的芯片增加,则屏蔽信号生成部的动作变得不稳定,导致使屏蔽状态解除的电源电压电平变动。例如原本POR电路内的比较器在成为能够正确地输出比较结果的状态之后,屏蔽信号应该解除屏蔽状态,但有可能在比较器成为可正确地输出比较结果的状态之前解除。在该情况下,有可能尽管电源电压电平较低,POR状态也被解除,芯片发生误动作。

图1以及图2的电压检测电路1、1a内的主要部分仅由p型MOS晶体管与电阻构成,因此能够简化电路构成。另外,由于仅由p型MOS晶体管的特性与电阻的相对偏差来决定使屏蔽信号转变的电源电压VDD的电压电平,因此与以往的屏蔽信号生成部相比,能够大幅度抑制使屏蔽信号转变的电源电压VDD的电压电平的偏差。因而,通过将从本实施方式的电压检测电路1、1a输出的信号用作屏蔽信号而构成POR电路,能够简化POR电路的电路构成,并且能够抑制对POR信号进行屏蔽的信号的电源电压依赖性。

(第二实施方式)

第二实施方式能够调整屏蔽信号将屏蔽状态解除的电源电压VDD的电压电平。

图5是第二实施方式的电压检测电路1b的电路图。在图5中,对与图2共用的电路部件标注相同的附图标记,以下,以不同点为中心进行说明。

图5的电压检测电路1b除了图2的电路构成之外,还具备并联连接在第四晶体管Q4的源极-漏极间的第五电阻R5。

通过设置第五电阻R5,第一晶体管Q1以及第四晶体管Q4的栅极电压Vg(节点n4的电压)由以下的式(1)表示。

Vg=VDD×R4/(R4+R5)…(1)

根据式(1)可知,第一晶体管Q1以及第四晶体管Q4的栅极电压Vg通过设置第五电阻R5而成为与电阻R4和电阻R5的电阻比相应的电压。与上述电压检测电路1、1a相比,若电源电压VDD不进一步变高,则第一晶体管Q1以及第四晶体管Q4不再接通,因此第二晶体管Q2也不会关断,可进一步提高使屏蔽信号转变的电源电压VDD的电压电平。

另外,第五电阻R5可以是电阻值固定的电阻,也可以是可变的电阻。只要设置可变电阻,就能够根据需要而切换解除屏蔽状态的电源电压VDD的电压电平。

如此,在第二实施方式中,由于在第四晶体管Q4的源极-漏极间并联连接第五电阻R5,因此能够根据第五电阻R5的电阻值而调整解除屏蔽状态的电源电压VDD的电压电平。

(第三实施方式)

第三实施方式的电压检测电路1c生成两种电源电压所对应的屏蔽信号。

图6是第三实施方式的电压检测电路1c的电路图。图6的电压检测电路1c具备第一屏蔽信号生成部11、第二屏蔽信号生成部12、以及信号合成部13。

第一屏蔽信号生成部11生成第一电源电压用的第一屏蔽信号。第二屏蔽信号生成部12生成比第一电源电压低的第二电源电压用的第二屏蔽信号。第一屏蔽信号生成部11与第二屏蔽信号生成部12的电路构成除了电源电压电平不同之外,与图1、图2或者图5的电压检测电路1、1a、1b相同。以下,说明第一屏蔽信号生成部11与第二屏蔽信号生成部12为与图2的电压检测电路1a相同的电路构成的情况。

更详细地说,第一屏蔽信号生成部11将图2的电压检测电路1a的电源电压VDD改变为第一电源电压HV。第二屏蔽信号生成部12将图2的电压检测电路1a的电源电压VDD改变为第二电源电压LV。第一电源电压HV与第二电源电压LV的具体的电压电平是任意的,但例如也可以是,第一电源电压HV为2V左右,第二电源电压LV为1.2V左右。

在第一电源电压HV超过第一阈值电压为止,第一屏蔽信号生成部11与图2的电压检测电路1a相同,按照第二晶体管Q2接通→第三晶体管Q3关断→第一晶体管Q1以及第四晶体管Q4的源极-漏极间电流增加的顺序动作。若第一电源电压HV超过第一阈值电压,则第二晶体管Q2关断,第三晶体管Q3接通,第一屏蔽信号从低转变为高。

同样,在第二电源电压LV超过第二阈值电压为止,第二屏蔽信号生成部12与图2的电压检测电路1a相同,按照第二晶体管Q2接通→第三晶体管Q3关断→第一晶体管Q1以及第四晶体管Q4的源极-漏极间电流增加的顺序动作。若第二电源电压LV超过第二阈值电压,则第二晶体管Q2关断,第三晶体管Q3接通,第二屏蔽信号从低转变为高。

信号合成部13在第一屏蔽信号为高、并且第二屏蔽信号为高时生成成为低的屏蔽信号。信号合成部13例如能够由双输入的NAND逻辑门构成。

图6的电压检测电路1c能够内置于POR电路。图7是表示POR电路5的一个例子的电路图。图7的POR电路5具备第一比较器6、第二比较器7、屏蔽信号生成电路8、以及POR信号生成部9。屏蔽信号生成电路8与图6的电压检测电路1c相同地构成。

第一比较器6检测第一电源电压HV是否超过第一阈值电压。也可以取代将第一电源电压HV直接与第一阈值电压比较,而是将第一电源电压HV转换为更低的电压,然后与第一阈值电压所对应的电压比较。例如第一比较器6输出表示用电阻R101、R102将第一电源电压HV分压后的电压是否为VBIAS电压以上的信号。若用电阻R101、R102将第一电源电压HV分压后的电压成为VBIAS电压以上,则第一比较器6输出从低转变为高的信号。

第二比较器7检测第二电源电压LV是否超过了第二阈值电压。也可以取代将第二电源电压LV直接与第二阈值电压比较,而是将第二电源电压LV转换为更低的电压,然后与第二阈值电压所对应的电压比较。例如第二比较器7输出表示用电阻R103、R104将第二电源电压LV分压后的电压是否为VBIAS电压以上表示的信号。若用电阻R103、R104将第二电源电压LV分压后的电压成为VBIAS电压以上,则第二比较器7输出从低转变为高的信号。

POR信号生成部9在第一比较器6与第二比较器7的输出信号均为高、并且从屏蔽信号生成电路8输出的屏蔽信号为低时,生成成为高的POR信号。POR信号在低时为上电复位状态,在高时为上电复位解除状态。

第一比较器6变为高是在第一电源电压HV为第一阈值电压以上的情况下。第二比较器7变为高是在第二电源电压LV为第二阈值电压以上的情况下。屏蔽信号变为低是在屏蔽状态被解除了的情况。由此,POR电路5在第一电源电压HV为第一阈值电压以上的情况下、并且在第二电源电压LV为第二阈值电压以上的情况下、并且在屏蔽状态被解除了的情况下,解除上电复位状态。

如此,在第三实施方式中,在具备两种电源电压的情况下,按照每个电源电压,以与图1、图2或者图5的电压检测电路1、1a、1b相同的电路生成第一以及第二屏蔽信号,合成第一以及第二屏蔽信号,生成最终的屏蔽信号。由此,在所有的电源电压到达了希望的电压电平的情况下,能够使屏蔽信号的逻辑转变而解除屏蔽状态。通过在POR电路5中使用利用本实施方式生成的屏蔽信号,能够抑制POR信号的误开放,提高POR信号的可靠性。

本公开的方式并不限定于上述各个实施方式,也包含本领域技术人员可想到的各种变形,本公开的效果也并不限定于上述内容。即,能够在不脱离权利要求书所规定的内容及其从等价物导出的本公开的概念性思想与主旨的范围内进行各种追加、变更以及部分的删除。

- 电压检测电路以及上电复位电路

- 一种上电复位电压稳定的上电复位电路