时钟校准电路和可编程逻辑芯片

文献发布时间:2023-06-19 12:21:13

技术领域

本申请涉及集成电路技术领域,尤其涉及一种时钟校准电路和可编程逻辑芯片。

背景技术

可编程逻辑芯片包含多个电路单元,电路单元可在与其对应的时钟信号到来时工作。

对于多个同步工作的电路单元来说,其时钟信号应同时达到。然而,因工艺、温度、电压、时钟信号的传输路径等原因,导致本应同步工作的多个电路单元之间存在一定延迟。

发明内容

本申请实施例提供了一种时钟校准电路和可编程逻辑芯片,以改善上述问题。

第一方面,提供一种时钟校准电路,时钟校准电路包括:第一延时电路,第一延时电路包括至少一个第一延时单元和与所述至少一个第一延时单元对应的第一控制电路,至少一个第一延时单元在所述第一控制电路的控制下向鉴相器输入第一输出时钟。第二延时电路,第二延时电路包括至少一个第二延时单元和与所述至少一个第二延时单元对应的第二控制电路,至少一个第二延时单元在所述第二控制电路的控制下向所述鉴相器输入第二输出时钟。鉴相器,计算第一输出时钟和所述第二输出时钟的相位之差得到比较结果,在比较结果大于或等于相位阈值时,将比较结果反馈至第一延时电路和/或第二延时电路,所述第一控制电路根据比较结果控制至少一个第一延时单元调节第一输出时钟,以向鉴相器输入新的第一输出时钟,和/或,所述第二控制电路根据比较结果控制至少一个第二延时单元调节所述第二输出时钟,以向鉴相器输入新的第二输出时钟,直至新的第一输出时钟与新的第二输出时钟的相位之差小于相位阈值。

第二方面,提供一种可编程逻辑芯片,包括多个电路单元以及第一方面所述的时钟校准电路,电路单元包括时钟输出端;每两个电路单元与一个时钟校准电路对应,时钟校准电路的第一延时电路的输入端和与其对应的一个电路单元的时钟输出端电连接、第二延时电路的输入端和与其对应的另一个电路单元的时钟输出端电连接。

本申请实施例提供的时钟校准电路和可编程逻辑芯片中,时钟校准电路的第一延时电路以及第二延时电路可以分别与两个电路单元中时钟电路的时钟输出端电连接,用以接收与其电连接的时钟电路的时钟信号,并对接收到的时钟信号进行调节,调节后分别将第一输出时钟和第二输出时钟发送至鉴相器,经鉴相器比较得到比较结果后,若比较结果仍然大于或等于相位阈值,则可以向第一延时电路和/或第二延时电路反馈比较结果,以使得第一延时电路和/或第二延时电路继续调节时钟信号的延时时间,直至新的第一输出时钟与新的第二输出时钟的相位之差小于所述相位阈值,从而改善多个电路单元间信号延时的问题。

附图说明

为了更清楚地说明本申请实施例的技术方案,下面将对实施例中所需要使用的附图作简单地介绍,应当理解,以下附图仅示出了本申请的某些实施例,因此不应被看作是对范围的限定,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其他相关的附图。

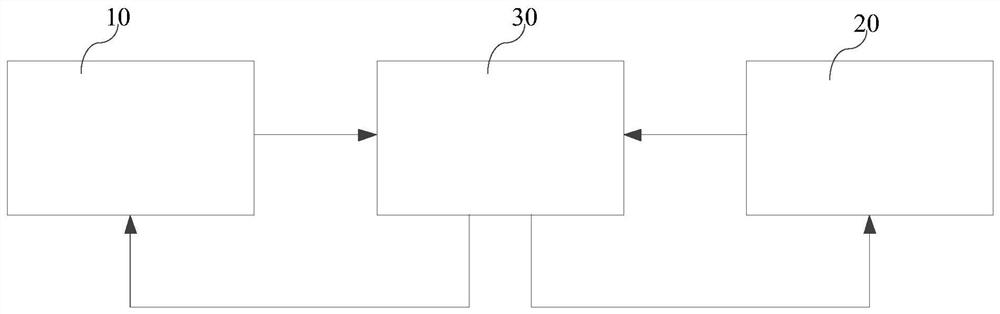

图1为本申请实施例提供的时钟校准电路的电路连接关系图;

图2a为本申请实施例提供的时钟校准电路的电路连接关系图;

图2b为本申请实施例提供的时钟校准电路的电路连接关系图;

图3为本申请实施例提供的可编程逻辑芯片的电路连接关系图;

图4为本申请实施例提供的第一延时单元和第三延时单元的电路连接关系图;

图5为本申请实施例提供的第二延时单元和第四延时单元的电路连接关系图;

图6为本申请实施例提供的时钟校准电路的电路连接关系图。

具体实施方式

为使本申请实施例的目的、技术方案和优点更加清楚,下面将结合本申请实施例中的附图,对本申请实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例是本申请一部分实施例,而不是全部的实施例。通常在此处附图中描述和示出的本申请实施例的组件可以以各种不同的配置来布置和设计。需要说明的是,在不冲突的情况下,本申请的实施例中的特征可以相互结合。

如图1所示,本申请实施例提供一种时钟校准电路100,时钟校准电路100包括第一延时电路10、第二延时电路20、以及鉴相器30。

如图2a和图2b所示,第一延时电路10,第一延时电路10包括至少一个第一延时单元11和与至少一个第一延时单元11对应的第一控制电路12,至少一个第一延时单元11在第一控制电路12的控制下向鉴相器30输入第一输出时钟。

第二延时电路20,第二延时电路20包括至少一个第二延时单元21和与至少一个第二延时单元21对应的第二控制电路22,至少一个第二延时单元21在第二控制电路22的控制下向鉴相器30输入第二输出时钟。

如图1所示,鉴相器30,计算第一输出时钟和第二输出时钟的相位之差得到比较结果,在比较结果大于或等于相位阈值时,将比较结果反馈至第一延时电路10和/或第二延时电路20,第一控制电路12根据比较结果控制至少一个第一延时单元11调节第一输出时钟,以向鉴相器输入新的第一输出时钟,和/或,第二控制电路根据比较结果控制至少一个第二延时单元21调节第二输出时钟,以向鉴相器30输入新的第二输出时钟,直至新的第一输出时钟与新的第二输出时钟的相位之差小于相位阈值。

如图3所示,时钟校准电路可以应用于可编程逻辑芯片,可编程逻辑芯片包括多个电路单元200,多个电路单元200均包括时钟电路201,每两个电路单元200的两个时钟电路201可以利用时钟校准电路100来校准。其中,时钟电路201包括时钟输出端,可以使第一延时电路10与第一个时钟电路201的时钟输出端电连接,以接收第一个时钟电路10的第一输入时钟,使第二延时电路20与第二个时钟电路201的时钟输出端电连接,以接收第二个时钟电路201的第二输入时钟。

在一些实施例中,在第一延时电路10包括多个第一延时单元11的情况下,如图2a所示,第一控制电路12可以包括多个第一控制单元,多个第一控制单元与第一延时单元11一一对应且电连接,第一控制单元用于向与其对应的第一延时单元11输入控制信号。

或者,在第一延时电路10包括多个第一延时单元11的情况下,如图2b所示,第一控制电路12可以包括多个输出引脚,多个输出引脚与第一延时单元11对应且电连接,第一控制电路12用于通过输出引脚向与其对应的第一延时单元11输入控制信号。第一控制电路12通过不同输出引脚向不同第一延时单元11输入的控制信号可以相同,也可以不相同。

在一些实施例中,第一延时电路10接收到第一个时钟电路201输出的第一输入时钟后,至少一个第一延时单元11可以在第一控制电路12的控制下向鉴相器30输入第一输出时钟。其中,至少一个第一延时单元11可以在第一控制电路12的控制下对接收的时钟信号延时或不延时。

示例的,第一延时单元11的个数为3个,第一个第一延时单元11在第一控制电路12的控制下延时,第二个第一延时单元11在第一控制电路12的控制下不延时,第三个第一延时单元11在第一控制电路12的控制下不延时。

在一些实施例中,至少一个第一延时单元11的最大延时时长与第一延时单元11的具体组成电路有关,在此不进行限定。可选的,每个第一延时单元11的最大延时时长可以是25皮秒。

在第一延时单元11的个数为多个的情况下,多个第一延时单元11的最大延时时长可以相同,也可以不相同。

在一些实施例中,在第二延时电路20包括多个第二延时单元21的情况下,如图2a所示,第二控制电路22可以包括多个第二控制单元,多个第二控制单元与第二延时单元21一一对应且电连接,第二控制单元用于向与其对应的第二延时单元21输入控制信号。

或者,在第二延时电路20包括多个第二延时单元21的情况下,如图2b所示,第二控制电路22可以包括多个输出引脚,多个输出引脚与第二延时单元21对应且电连接,第二控制电路22用于通过输出引脚向与其对应的第二延时单元21输入控制信号。第二控制电路22通过不同输出引脚向不同第二延时单元21输入的控制信号可以相同,也可以不相同。

在一些实施例中,第二延时电路20接收到第二个时钟电路201输出的第二输入时钟后,至少一个第二延时单元21可以在第二控制电路22的控制下向鉴相器30输入第二输出时钟。其中,至少一个第二延时单元21可以在第二控制电路22的控制下对接收的时钟信号延时或不延时。

示例的,第二延时单元21的个数为3个,第一个第二延时单元21在第二控制电路22的控制下延时,第二个第二延时单元21在第二控制电路22的控制下延时,第三个第二延时单元21在第二控制电路22的控制下不延时。

在一些实施例中,至少一个第二延时单元21的最大延时时长与第二延时单元21的具体组成电路有关,在此不进行限定。可选的,每个第二延时单元21的最大延时时长可以是25皮秒。

在第一延时单元11的个数为多个的情况下,多个第一延时单元11的最大延时时长可以相同,也可以不相同。

在一些实施例中,本实施例为了方便区分,将每两个电路单元200的时钟电路201分别命名为第一个时钟电路201和第二个时钟电路201,然而,本领域的技术人员应该知道,任意一个电路单元200的时钟电路201可以作为第一其他电路单元200的时钟电路201第一个时钟电路201或第二个时钟电路201。

在一些实施例中,第一延时单元11的个数与第二延时单元的个数可以相同,也可以不相同。第一延时单元11的最大延时时长与第二延时单元21的最大延时时长可以相同,也可以不相同。

在一些实施例中,在第一延时单元11的个数为多个的情况下,不对多个第一延时单元11的连接关系进行限定。可选的,多个第一延时单元11之间可以串联。

在第二延时单元21的个数为多个的情况下,不对多个第二延时单元21的连接关系进行限定。可选的,多个第二延时单元21之间可以串联。

在一些实施例中,不对相位阈值的具体数值进行限定,可选的,在第一延时单元11和第二延时单元12的最大延时时长均为25皮秒的情况下,相位阈值可以是25皮秒,即,在比较结果大于或等于25皮秒时,需要第一延时电路10和/或第二延时电路20在第一输出时钟和/或第二输出时钟的基础上,再次调节第一输出时钟和/或第二输出时钟,并输入至鉴相器30,直至比较结果小于25皮秒。

示例的,在比较结果为26皮秒的情况下,鉴相器30可以仅将比较结果反馈至第一延时电路10或第二延时电路20,且只需一个第一延时单元11或一个第二延时单元21即可使得更新后的比较结果小于25皮秒。

在比较结果为50皮秒的情况下,鉴相器30可以仅将比较结果反馈至第一延时电路10和/或第二延时电路20,具体的,与第一延时单元11和第二延时单元12的个数以及第一延时单元11与第一延时单元11之间的连接关系、第二延时单元12与第二延时单元12之间的连接关系有关。

在另一些实施例中,第一输出时钟与第二输出时钟的比较结果也可以小于相位阈值,在此情况下,鉴相器30可无需再向第一延时电路10和第二部延时电路20反馈比较结果。

在一些实施例中,时钟校准电路100还可以包括状态机60,状态机60的输入端与鉴相器30的输出端电连接、输出端分别与第一延时电路10和第二延时电路20电连接,状态机60可以间隔一定时间采集比较结果,并在比较结果大于或等于相位阈值时,将比较结果反馈至第一延时电路10和/或第二延时电路20。

本申请实施例提供一种时钟校准电路100,时钟校准电路100的第一延时电路10以及第二延时电路可以分别与两个电路单元200中时钟电路201的时钟输出端电连接,用以接收与其电连接的时钟电路201的时钟信号,并对接收到的时钟信号进行调节,调节后分别将第一输出时钟和第二输出时钟发送至鉴相器30,经鉴相器30比较得到比较结果后,若比较结果仍然大于或等于相位阈值,则可以向第一延时电路10和/或第二延时电路20反馈比较结果,以使得第一延时电路10和/或第二延时电路20继续调节时钟信号的延时时间,直至新的第一输出时钟与新的第二输出时钟的相位之差小于所述相位阈值,从而改善多个电路单元间信号延时的问题。

如图4所示,本申请另一实施例提供一种时钟校准电路100,在前述实施例的基础上详细介绍第一延时单元11和第二延时单元12的具体电路结构。

至少一个第一延时电路10包括串联的多个第一延时单元11,第一延时单元11包括选择器111和第一缓冲器112。

第一个第一延时单元的选择器111的第一输入端与第一时钟信号输入端电连接、第二输入端通过第一缓冲器112与第一时钟信号输入端电连接、控制端和第一控制电路电连接。其他每一个第一延时单元的选择器的输入端与上一个第一延时单元的选择器111的输出端电连接、控制端和第一控制电路12电连接。最后一个第一延时单元的输出端与鉴相器30的输入端电连接。

以第一个第一延时单元为例,第一个第一延时单元的第一输入端与第一时钟信号输入端电连接,可以直接接收第一时钟信号;第一个第一延时单元的第二输入端与通过第一缓冲器112与第一时钟信号输入端电连接,可以接收第一时钟信号经延时后的时钟信号。

在此基础上,第一个第一延时单元的选择器111可以在第一控制电路12的控制下,选择输出第一输入端接收的第一时钟信号,或者输出第二输入端接收的第一时钟信号经延时后的时钟信号。

同理,其他第一延时单元的第一输入端可以直接接收前一个第一延时单元输出的时钟信号、第二输入端可以接收前一个第一延时单元输出的时钟信号经第一缓冲器112延时的时钟信号。其他第一延时单元的选择器111可以在第一控制电路12的控制下,选择输出第一输入端接收的前一个第一延时单元输出的时钟信号,或者输出第二输入端接收的前一个第一延时单元输出的时钟信号经第一缓冲器112延时的时钟信号。

在一些实施例中,比较结果可以包括第一输出时钟和第一调节信号。鉴相器30的输出端分别与第一个第一延时单元的选择器111的第一输入端和第二输入端、以及第一控制电路12电连接,鉴相器30用于在比较结果大于或等于相位阈值时,将第一输出时钟输入至第一个第一延时单元的选择器111、将第一调节信号输入至第一控制电路12。

这样一来,若比较结果大于或等于相位阈值,且鉴相器30将比较结果反馈至第一延时电路10,则第一个第一延时单元可以接收第一输出时钟,并且串联的多个第一延时单元11可以在第一控制电路12的控制下,再次对第一输出时钟进行延时。

如图5所示,至少一个第二延时电路20包括串联的多个第二延时单元21,第二延时单元包括选择器211和第二缓冲器212。

第一个第二延时单元的选择器211的第一输入端与第二时钟信号输入端电连接、第二输入端通过第一缓冲器212与第二时钟信号输入端电连接、控制端和第二控制电路22电连接。其他每一个第二延时单元的选择器211的输入端与上一个第二延时单元的选择器211的输出端电连接、控制端和第二控制电路22电连接。最后一个第二延时单元的输出端与鉴相器30的输入端电连接。

以第一个第二延时单元为例,第一个第二延时单元的第一输入端与第二时钟信号输入端电连接,可以直接接收第二时钟信号;第一个第二延时单元的第二输入端与通过第二缓冲器212与第二时钟信号输入端电连接,可以接收第二时钟信号经延时后的时钟信号。

在此基础上,第一个第二延时单元的选择器211可以在第二控制电路22的控制下,选择输出第一输入端接收的第二时钟信号,或者输出第二输入端接收的第二时钟信号经延时后的时钟信号。

同理,其他第二延时单元的第一输入端可以直接接收前一个第二延时单元输出的时钟信号、第二输入端可以接收前一个第二延时单元输出的时钟信号经缓冲器212延时的时钟信号。其他第二延时单元的选择器111可以在第二控制电路22的控制下,选择输出第一输入端接收的前一个第二延时单元输出的时钟信号,或者输出第二输入端接收的前一个第二延时单元输出的时钟信号经第二缓冲器212延时的时钟信号。

在一些实施例中,比较结果可以包括第二输出时钟和第二调节信号。鉴相器30的输出端分别与第一个第二延时单元的选择器211的第一输入端和第二输入端、以及第二控制电路22电连接,鉴相器30用于在比较结果大于或等于相位阈值时,将第二输出时钟输入至第一个第二延时单元的选择器211、将第一调节信号输入至第一控制电路12。

这样一来,若比较结果大于或等于相位阈值,且鉴相器30将比较结果反馈至第二延时电路20,则第一个第二延时单元可以接收第一输出时钟,并且串联的多个第二延时单元21可以在第二控制电路22的控制下,再次对第二输出时钟进行延时。

如图6所示,本申请实施例还提供一种时钟校准电路100,在前述任一实施例的基础上,时钟校准电路100还包括第三延时电路40和第四延时电路50。

第三延时电路40包括至少一个第三延时单元41和与至少一个第三延时单元41对应的第三控制电路42;第三延时电路40的输入端与第一时钟信号输入端电连接、输出端与第一个第一延时电路10的第一输入端和第二输入端电连接,第三延时电路40用于接收第一时钟信号输入端输入的第一输入时钟,并根据第一输入时钟的传输路径校准第一输入时钟。

第四延时电路50包括至少一个第四延时单元51和与至少一个第四延时单元51对应的第四控制电路52。第四延时电路50的输入端与第二时钟信号输入端电连接、输出端与第一个第二延时电路20的第一输入端和第二输入端电连接,第四延时电路50用于接收第二时钟信号输入端输入的第二输入时钟,并根据第二时钟信号的传输路径校准第二输入时钟。

在确定两个电路单元200的时钟所经过的路径、且两个路径长度不同的情况下,可能会因路径长度不同,导致两个时钟信号中的一个延时较多。在此情况下,可以根据两个时钟信号各自的路径长度,确定可以通过第三延时电路40和/或第四延时电路50所需延时的时长,之后,通过第三延时电路40和/或第四延时电路50对与第一输入时钟和/或第二输入时钟进行延时。

在一些实施例中,在第三延时电路40包括多个第三延时单元41的情况下,参考图2a所示,第三控制电路42可以包括多个第三控制单元,多个第三控制单元与第三延时单元41一一对应且电连接,第三控制单元用于向与其对应的第三延时单元41输入控制信号。

或者,如图4所示,第三控制电路42可以包括多个输出引脚,多个输出引脚与第三延时单元41对应且电连接,第三控制电路42用于通过输出引脚向与其对应的第三延时单元41输入控制信号。第三控制电路42通过不同输出引脚向不同第三延时单元41输入的控制信号可以相同,也可以不相同。

在一些实施例中,第三延时电路40接收到第一输入时钟后,至少一个第三延时单元41可以在第三控制电路42的控制下对接收的时钟信号延时或不延时。

示例的,第三延时单元41的个数为2个,第一个第三延时单元41在第三控制电路42的控制下延时,第二个第三延时单元41在第三控制电路42的控制下不延时。

在一些实施例中,至少一个第三延时单元41的最大延时时长与第三延时单元41的具体组成电路有关,在此不进行限定。可选的,每个第三延时单元41的最大延时时长可以是100皮秒。

在第三延时单元41的个数为多个的情况下,多个第三延时单元41的最大延时时长可以相同,也可以不相同。

在一些实施例中,在第四延时电路50包括多个第四延时单元51的情况下,参考图2a所示,第四控制电路52可以包括多个第四控制单元,多个第四控制单元与第四延时单元51一一对应且电连接,第四控制单元用于向与其对应的第四延时单元51输入控制信号。

或者,在第四延时电路50包括多个第四延时单元51的情况下,如图5所示,第四控制电路52可以包括多个输出引脚,多个输出引脚与第四延时单元51对应且电连接,第四控制电路52用于通过输出引脚向与其对应的第四延时单元51输入控制信号。第四控制电路52通过不同输出引脚向不同第四延时单元51输入的控制信号可以相同,也可以不相同。

在一些实施例中,第四延时电路50接收到第二输入时钟后,至少一个第四延时单元51可以在第四控制电路52的控制下对接收的时钟信号延时或不延时。

示例的,第四延时单元51的个数为2个,第一个第四延时单元51在第四控制电路52的控制下延时,第二个第四延时单元51在第四控制电路52的控制下延时。

在一些实施例中,至少一个第四延时单元51的最大延时时长与第四延时单元51的具体组成电路有关,在此不进行限定。可选的,每个第四延时单元51的最大延时时长可以是100皮秒。

在第四延时单元51的个数为多个的情况下,多个第四延时单元51的最大延时时长可以相同,也可以不相同。

在一些实施例中,第三延时单元41的个数与第二延时单元的个数可以相同,也可以不相同。第三延时单元41的最大延时时长与第四延时单元51的最大延时时长可以相同,也可以不相同。

在一些实施例中,在第三延时单元41的个数为多个的情况下,不对多个第三延时单元41的连接关系进行限定。可选的,多个第三延时单元41之间可以串联。

在第四延时单元51的个数为多个的情况下,不对多个第四延时单元51的连接关系进行限定。可选的,多个第四延时单元51之间可以串联。

在一些实施例中,如图4所示,至少一个第三延时电路40包括串联的多个第三延时单元41,第三延时单元41包括选择器411和第三缓冲器412。第一个第三延时单元的选择器411的第一输入端与第一时钟信号输入端电连接、第二输入端通过第三缓冲器412与第一时钟信号输入端电连接、控制端和第三控制电路42电连接。其他每一个第三延时单元的选择器411的输入端与上一个第三延时单元的选择器411的输出端电连接、控制端和第三控制电路42电连接。最后一个第三延时单元的输出端与第一延时电路10的第一个第一延时单元电连接。

如图5所示,至少一个第四延时电路50包括串联的多个第四延时单元51,第四延时单元51包括选择器511和第四缓冲器512。第一个第四延时单元的选择器511的第一输入端与第二时钟信号输入端电连接、第二输入端通过第四缓冲器512与第二时钟信号输入端电连接、控制端和第四控制电路52电连接。其他每一个第四延时单元的选择器511的输入端与上一个第四延时单元的选择器511的输出端电连接、控制端和第四控制电路52电连接。最后一个第四延时单元的输出端与第二延时电路20的第一个第二延时单元电连接。

以第一个第三延时单元为例,第一个第三延时单元的第一输入端与第一时钟信号输入端电连接,可以直接接收第一时钟信号;第一个第三延时单元的第二输入端与通过第三缓冲器412与第一时钟信号输入端电连接,可以接收第一时钟信号经延时后的时钟信号。

在此基础上,第一个第三延时单元的选择器411可以在第三控制电路42的控制下,选择输出第一输入端接收的第一时钟信号,或者输出第二输入端接收的第一时钟信号经延时后的时钟信号。

同理,其他第三延时单元的第一输入端可以直接接收前一个第三延时单元出的时钟信号、第二输入端可以接收前一个第三延时单元输出的时钟信号经第三缓冲器412延时的时钟信号。其他第三延时单元的选择器411可以在第三控制电路42的控制下,选择输出第一输入端接收的前一个第三延时单元输出的时钟信号,或者输出第二输入端接收的前一个第三延时单元输出的时钟信号经第三缓冲器412延时的时钟信号。

本申请实施例中,还可以使第三延时电路40中每个第三延时单元41的最大延时时长大于第一延时电路10中每个第一延时单元11的最大延时时长,以调节因时钟路径长度不同导致的时钟延时,进一步的,由于第一延时单元11的最大延时小于第三延时单元41的最大延时时长,还可以利用第一延时单元11对时钟信号进行精细调节。还可以使第四延时电路50中每个第四延时单元51的最大延时时长大于第二延时电路20中每个第二人延时单元21的最大延时时长,以调节因时钟路径长度不同导致的时钟延时,进一步的,由于第二延时单元21的最大延时小于第四延时单元51的最大延时时长,还可以利用第二延时单元21对时钟信号进行精细调节。

如图3所示,本申请实施例还提供一种可编程逻辑芯片,包括多个电路单元200以及多个如前述任一实施例所述的时钟校准电路100,电路单元200包括时钟输出端。每两个电路单元200与一个时钟校准电路100对应,时钟校准电路100的第一延时电路10的输入端和与其对应的一个电路单元200的时钟输出端电连接、第二延时电路20的输入端和与其对应的另一个电路单元200的时钟输出端电连接。

可编程逻辑芯片可以是现场可编程门阵列(Field-Programmable Gate Array,简称FPGA)芯片或复杂可编程逻辑器件(Complex Programmable Logic Device,简称CPLD)等。

本申请实施例提供的可编程逻辑芯片的解释说明和有益效果与前述实施例的解释说明和有益效果相同,在此不再赘述。

最后应说明的是:以上实施例仅用以说明本申请的技术方案,而非对其限制;尽管参照前述实施例对本申请进行了详细的说明,本领域的普通技术人员当理解:其依然可以对前述各实施例所记载的技术方案进行修改,或者对其中部分技术特征进行等同替换;而这些修改或者替换,并不驱使相应技术方案的本质脱离本申请各实施例技术方案的精神和范围。

- 时钟校准电路和可编程逻辑芯片

- 一种可编程配置逻辑块中的单粒子加固时钟控制电路及控制方法