基板处理方法及利用该基板处理方法制造的半导体器件

文献发布时间:2023-06-19 12:25:57

技术领域

本发明涉及半导体器件的制造,更详细地说,涉及在具有凹槽的基板上形成钨薄膜的基板处理方法及利用该基板处理方法制造的半导体器件。

背景技术

近来,随着对存储装置的高容量和低功耗的需求,正在进行非挥发性的同时无需刷新的新一代存储装置的相关研究。对于这种新一代存储装置要求具有DRAM(DynamicRandom Access Memory,动态随机存储器)的高集成度、闪存的非挥发性、SRAM(StaticRAM,静态RAM)的高速性等。作为新一代存储装置提出了PRAM(Phase change RAM,相变RAM)、NFGM(Nano Floating Gate Memory,纳米浮栅存储器)、PoRAM(Polymer RAM,聚合物RAM)、MRAM(Magnetic RAM,磁性RAM)、FeRAM(Ferroelectric RAM,铁电RAM)、RRAM(Resistive RAM,电阻式RAM)等来作为符合上述的要求的新一代存储装置。

再则,随着半导体器件的集成度提高,半导体器件的组件的设计规则正在减少。在高度微缩(scaling)的半导体器件中多条布线和在其间插入的多个埋藏式电极(BuriedContact;BC)的形成工艺变得越来越复杂和困难。例如,因为单元(cell)区域与周边(peri)区域的结构差异形成台阶,因此在后续工艺中引起图案缺陷。

尤其是,在COP(Cell On Peri)结构的NAND器件中使用钨(W)金属作为下部布线的情况下,需具有低电阻率。而钨金属为了具有低电阻率,应沉积具有相对较大的晶粒尺寸(Grain Size)的钨(W)薄膜。在该情况下,存在在CMP(Chemical Mechanical Polishing,化学机械研磨)之后可出现诸如接缝(seam)或者空隙(void)的缺陷(defect)的可能性非常高的问题。

另外,在沉积晶粒尺寸比较小的钨薄膜的情况下,可密集地填充图案内部,但是存在提高薄膜的电阻率的问题。

发明内容

(要解决的问题)

本发明是用于解决上述的问题的,目的在于提供一种在半导体器件中可形成具有低电阻率的钨薄膜的基板处理方法及利用该基板处理方法制造的半导体器件。然而,这种课题仅是举例的,不得由此限定本发明的范围。

(解决问题的手段)

本发明的一观点的基板处理方法可包括如下的步骤:将具有凹槽的基板装载到腔室内;在所述凹槽的内壁上形成含钨(W)的成核层;在所述成核层上形成部分性填充所述凹槽内部的第一钨块体层;在所述第一钨块体层上形成晶体转换层;及在所述晶体转换层上形成晶粒尺寸相对小于所述第一钨块体层的第二钨块体层,以将所述凹槽内部全部填充。

根据所述基板处理方法,形成所述晶体转换层的步骤可包括将WF

根据所述基板处理方法,形成所述晶体转换层的步骤可包括:在将WF

根据所述基板处理方法,形成所述晶体转换层的步骤可包括除了源气体以外还将H

根据所述基板处理方法,形成所述成核层的步骤、形成所述第一钨块体层的步骤、形成所述晶体转换层的步骤及形成所述第二钨块体层的步骤可以是在所述腔室内通过原位(in-situ)工艺形成的步骤。

根据所述基板处理方法,所述晶体转换层可具有

根据所述基板处理方法,形成所述晶体转换层的步骤为,在所述凹槽区域的开口部被所述第一钨块体层堵住之前可形成所述晶体转换层。

根据所述基板处理方法,形成所述晶体转换层的步骤为,在所述凹槽区域的开口部被所述第一钨块体层堵住1/2至2/3的区域之前可形成所述晶体转换层。

根据所述基板处理方法,形成所述成核层的步骤可包括在将WF

根据所述基板处理方法,形成所述第一钨块体层的步骤可包括将WF

根据所述基板处理方法,形成所述第二钨块体层的步骤可包括将WF

本发明的另一观点的半导体器件可包括:基板,具有凹槽;成核层,含钨(W),并且形成在所述凹槽的内壁上;第一钨块体层,形成在所述成核层上,以部分性填充所述凹槽内部;晶体转换层,形成在所述第一钨块体层上;及第二钨块体层,晶粒尺寸相对小于所述第一钨块体层,并且在所述晶体转换层上形成,以将所述凹槽内部全部填充。

根据所述半导体器件,所述晶体转换层可具有

根据所述半导体器件,所述晶体转换层为可形成在所述凹槽区域内部的宽度的1/2至2/3区域内。

(发明的效果)

根据如上述构成的本发明的一实施例,在可提供一种在半导体器件中可形成具有低电阻率并且没有接缝(seam)或者空隙(void)的钨薄膜的基板处理方法及利用该基板处理方法制造的半导体器件。当然,本发明的范围不限于该效果。

附图说明

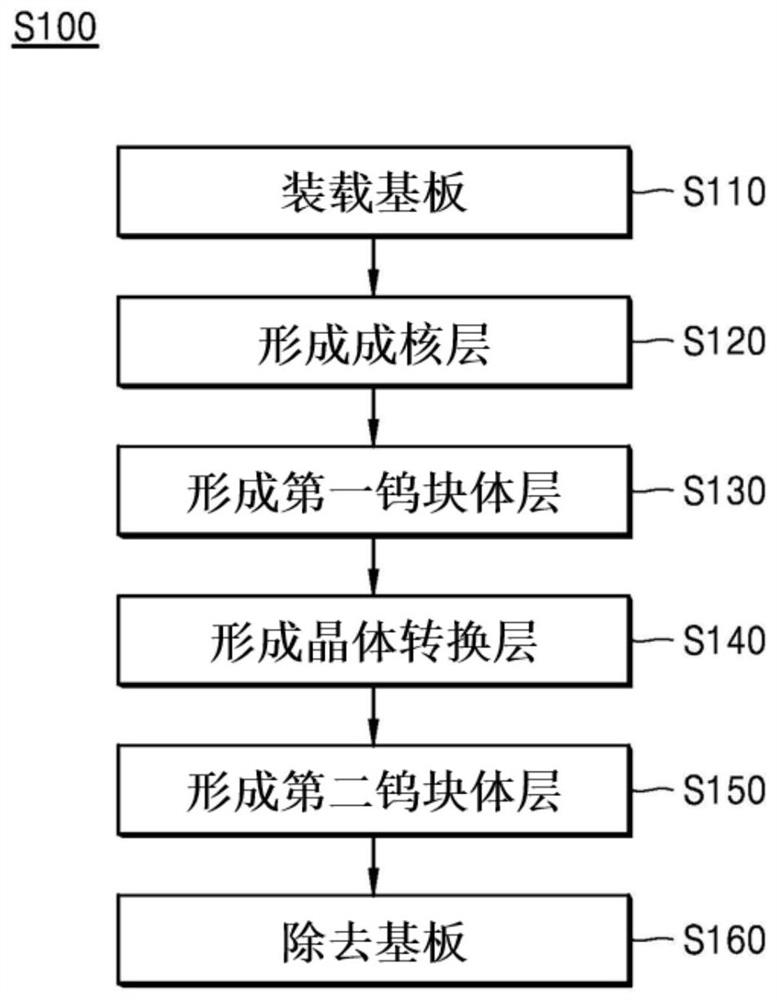

图1是概略示出本发明的一实施例的基板处理方法的工艺流程图。

图2是概略示出用于说明本发明的一实施例的基板处理方法的半导体器件的结构的图。

图3是用扫描电子显微镜分析通过本发明的实验例的基板处理方法制造的半导体器件样本的微小组织的图片。

具体实施方式

以下,参照附图详细说明本发明的优选的各种实施例。

本发明的实施例是为了将本发明更加完整地告知给在该技术领域中具有常规知识的人而提供的,以下实施例可变现成各种其他形态,并且本发明的范围不限于以下的实施例。相反,这些实施例是为了更加彻底且完整地公开本发明并且将本发明的思想完整地传达给技术人员而提供的。另外,为了说明的便利及明确性,在附图中夸张示出了各层的厚度或者大小。

以下,参照概略示出本发明的理想实施例的附图说明本发明的实施例。在附图中,例如根据制造技术及/或者公差(tolerance)可预测示出的形状的变形。从而,本发明思想的实施例不限于在本说明书示出的区域的特定形状来解释,应包括诸如通过制造引起的形状变化。

图1是概略示出本发明的一实施例的基板处理方法的工艺流程图。

参照图1,基板处理方法S100可依次执行装载基板的步骤S110、形成成核层的步骤S120、形成第一钨块体层的步骤S130、形成晶体转换层的步骤S140、形成第二钨块体层的步骤S150及除去基板的步骤S160的工艺。对于各个步骤的具体说明将参照图2在以下进行说明。另一方面,所述基板处理方法S100在各个步骤之间还可包括吹扫及抽气步骤。

另外,形成成核层的步骤S120至形成第二钨块体层的步骤S150可在腔室内通过原位(in-situ)工艺执行。作为一示例,所述原位(in-situ)工艺是指在由一个以上的腔室构成的单一装置内在第一腔室中连续执行这些步骤。

作为另一示例,可包括每个步骤在各个腔室内执行的方式。

可包括在第一腔室内执行形成成核层的步骤S120之后在第二腔室内执行形成第一钨块体层的步骤S130,之后在第三腔室内执行形成晶体转换层的步骤S140之后在第四腔室内执行形成第二钨块体层的步骤S150的方式。在以原位方式进行的情况下,可防止或者最少化在沉积工艺和蚀刻工艺之间暴露在大气压下的步骤,因此防止形成不必要的氧化膜,可期待将工艺的效率性最大化的效果。

图2是概略示出用于说明本发明的一实施例的基板处理方法的半导体器件的结构的图。

首先,参照图2的(b)至(d),在COP(Cell On Peri)结构的NAND器件的情况下,纵横比在1︰1至1︰1.5左右的基板100形成的凹槽(hole)的内壁上可依次沉积并填充含钨(W)的成核层210及钨块体层220a、220b。在此,基板100可包括例如晶片(wafer),所述凹槽可具有剖面相互面对的内壁和连接内壁的底面。内壁可与底面垂直形成,但是也可以是与底面形成预定的倾斜度的倾斜形成。再则,所述凹槽可包括孔形状或者以沟槽形成延长形成的结构。

另一方面,如图2的(b)所示,在钨(W)块体层220a的晶粒小的情况下,间隙填充(Gap-fill)特性和接合特性得到改善,但是存在电阻率非常高的问题。在将钨(W)金属用作下部布线的情况下,需具有低电阻特性,因此为了降低界面的接触电阻(contactresistance),如图2的(c)所示钨(W)块体层220b的晶粒尺寸必须大。然而,在该情况下,虽然电阻率得到了改善,但是间隙填充(Gap-fill)特性和接合特性会相对变差。再则,因为在之后执行的CMP工艺,如图2的(d)所示因为执行CMP,在钨块体层的上面可出现诸如接缝(seam)或者空隙(void)的缺陷D。

为了解决该问题,在本发明中,介入晶体转换层,以在沉积钨块体层的工艺步骤之间能够改变钨块体层的晶粒尺寸,进而在CMP工艺之后没有缺陷问题的同时可期待电阻率改善效果。

参照图2的(a),半导体器件可包括:基板100,具有凹槽;成核层210,含钨(W)并且形成在所述凹槽的内壁上;第一钨块体层220,形成在成核层210上,以部分性填充所述凹槽内部;晶体转换层230,形成在第一钨块体层220上;及第二钨块体层240,晶粒尺寸相对小于第一钨块体层220,并且形成在晶体转换层230上,以将所述凹槽内部全部填充。

具体说明可制造半导体器件的基板处理方法,可将具有凹槽的基板100装载于工艺腔室内。之后,可在所述凹槽的内壁上形成含钨(W)的成核层210。

作为一示例,成核层210可通过将源气体、吹扫气体、反应气体等供应于基板上的原子层沉积法(ALD;Atomic Later Deposition)形成。所述原子层沉积法为不仅可适用于按时间将源气体、吹扫气体及反应气体等不连续地供应于配置有基板100的腔室内进而实现沉积的时分法,也可适用于在空间性间隔源气体、吹扫气体及反应气体等的同时连续供应这些气体的系统内依次移动基板进而实现沉积的空间分割方式。

成核层210可以是将WF

在形成成核层210之前,还可形成防钨层(未示出)。所述防钨层防止在基板内扩散钨,例如可使用依次沉积Ti/TiN的或者除此之外依次沉积金属和氮化物层的。

然后,在成核层210上可形成部分性填充所述凹槽内部的第一钨块体层220。作为一示例,第一钨块体层220可利用化学气相沉积工艺(CVD;Chemical Vapor Deposion)形成,也可利用等离子体增强化学气相沉积(PECVD;Plasma Enhanced Chemical VaporDeposition)形成。将在WF

与以往不同,第一钨块体层220只填充凹槽内部的一部分,之后可在第一钨块体层220上形成晶体转换层230。晶体转换层230在所述凹槽区域的开口部被第一钨块体层220完全堵住之前形成。例如,所述凹槽区域内部的宽度被第一钨块体层220填充1/2至2/3区域之前可形成所述晶体转换层230。在此,所述宽度是指凹槽的侧壁之间的距离,在凹槽的侧壁为倾斜的形状的情况下,是指凹槽的最上部的侧壁之间的距离。也就是说,所述凹槽区域的中心部先被填充之前引入晶体转换层230,用晶粒尺寸小的膜密集地填充所述凹槽区域的中心部,进而可将在所述凹槽区域的中心部出现的缺陷最小化。

晶体转换层230可具有

另一方面,晶体转换层230可利用与形成成核层210的方法相同的方法形成,即原子层沉积方法(ALD)。作为一示例,将WF

作为另一示例,晶体转换层230可分两个工艺形成。在将WF

另一方面,在所述实施例中,在执行形成晶体转换层230的工艺的途中,除了已供应的气体以外还可将H

最后,为了将凹槽内部全部填充,可在晶体转换层230上形成晶粒尺寸相对小于第一钨块体层220的第二钨块体层240。第二钨块体层240可以是执行与第一钨块体层220相同的工艺而形成的。作为一示例,将WF

在形成第二钨块体层240之后,从工艺腔室除去基板100之后执行CMP(ChemicalMechanical Polishing)工艺,进而高于基板100最上部面形成的含钨的层的一部分被蚀刻并去除。

以下,参照附图说明用于帮助理解本发明的实验例。但是,以下的实施例只是用于理解本发明,不得只由以下的实验例限定本发明。

实验例1

作为具有利用现有技术的基板处理方法制造的钨块体层的比较例样本,将B

实验例2

作为用于与实验例1比较的样本,与实验例1同样地形成了成核层及钨块体层。之后,供应B

实验例3

作为用于与实验例1及实验例2比较的样本,与实验例2同样地形成了成核层及钨块体层。之后,代替B

实验例4

与实验例2同样地形成了成核层、钨块体层及晶体转换层。之后,供应WF

实验例5

作为用于与实验例4比较的样本,与实验例3同样地形成了成核层、钨块体层及晶体转换层。之后,供应WF

在此,在300torr的真空度下沉积所述钨块体层,并且利用扫描电子显微镜晶(SEM)分析比较了晶体转换层的气体的种类及晶体转换层的沉积前/后的表面及剖面微小组织。

图3是用扫描电子显微镜分析通过本发明的实验例的基板处理方法制造的半导体器件样本的微小组织的图片。

比较分析了所述实验例样本的电阻率及RMS值。如下表1整理了各个样本的物理特性。

表1

参照图3,可确认到:实验例1至实验例3的情况没有大变化。相反,实验例4的情况为,若利用B

参照表1,与各个样本的微小组织结果相同,可确认到实验例1至实验例3没有大变化。相反,实验例4的情况为,相比于实验例2及实验例3电阻率值提高至11.0μΩ·㎝,但是表面粗糙度值降低至

另一方面,在所述实验例中,以与实验例4样本相同的方式制造样本,其中改变各个晶体转换层的厚度来制造样本,比较分析了各个的电阻率及RMS值。如下表2整理了各个样本的物理特性。在下表中,实验例6为没有晶体转换层而是通过CVD工艺利用B

表2

参照表2,实验例6的情况为,具有最低的电阻率8.9μΩ·㎝,并且表面粗糙度(RMS)的值最大

尤其是,随着晶体转换层的厚度增厚,电阻率逐渐提高,而表面粗糙度的值则保持了类似的水平。从而,确认到:晶体转换层的厚度可以形成为

另外,实验例11至实验例14形成了

表3

参照表3,确认到:随着利用SiH

另外,可确认到:相比于使用单层晶体转换层的样本,使用形成双层结构的晶体转换层(分别供应B

目前为止,本发明为,作为各种实施例说明了介入晶体转换层没有诸如接缝或者空隙的缺陷并且电阻率低的基板处理方法。另一方面,利用上述的基板处理方法可实现具有将钨金属用作下部布线的COP(Cell On Peri)结构的NAND器件。

参照在附图示出的实施例说明了本发明,但是这仅是示例性的,在该技术领域具有常规知识的人员可理解为由此可进行各种变形及同等的其他实施例。从而,本发明的真正的技术保护范围应由权利要求书的范围内的技术思想定义。

- 基板处理方法及利用该基板处理方法制造的半导体器件

- 基板处理方法及其基板处理装置、半导体器件制造方法