用于零知识证明的证明方法、系统、电子设备和存储介质

文献发布时间:2023-06-19 13:45:04

技术领域

本发明涉及零知识证明的技术领域,尤其是涉及一种用于零知识证明的证明方法、系统、电子设备和计算机可读存储介质。

背景技术

零知识证明是指证明者能够在不透露任何有用信息的前提下,使验证者相信某个论断是正确的。零知识证明方法广泛应用于区块链、多方安全计算(MPC)、隐私计算等场景中。

现有的零知识证明方法有多种多样,包括交互式证明方法和非交互式证明(Non-Interactive Linear Proofs,简称为NILP)方法,其中非交互式证明方法不需要借助证明者和验证者之间的交互来产生证明,相对于交互式证明方法具有显著的优点。在非交互式证明方法中,零知识简洁非交互式知识证明(zero knowledge Succinct Non-interactiveArgument of Knowledge,简称为zk-SNARK)是当前常用的一类非交互式零知识证明方法,比较具有代表性的证明方法例如Groth16证明算法。

Groth16证明系统使用二次算术运算(Quadratic Arithmetic Program,简称为QAP)表示一阶约束系统(Rank-1 Constraint System,简称为R1CS)实例的可满足性。完整的Groth16证明系统包括三个过程,分别为设置过程、证明过程和验证过程。其中,对于每个QAP实例,设置过程仅运行一次,设置过程将创建证明密钥和验证密钥,证明密钥和验证密钥对证明者和验证者均公开;验证过程则使用验证密钥检查一个证明,以决定是接受还是拒绝该证明。证明过程则需要根据证明密钥生成一个证明,该过程主要包括两个计算部分,分别为FFT计算和MultiExp计算,涉及大量的计算,耗时比较长。

目前,Groth16证明方法已在开源项目bellperson实现,该开源项目中证明过程主要使用GPU进行计算。采用该开源项目提供的实现方案,即使配备AMD的7542型号64核CPU和Nvidia的2080Ti系列GPU的计算机系统,仍然需要花费几十分钟的时间才能完成具有亿级数量的电路约束的零知识证明。

发明内容

为了加快零知识证明的生成,本申请实施例提供了一种用于零知识证明的证明方法、系统、电子设备和计算机可读存储介质。

第一方面,本申请实施例提供了一种用于零知识证明的证明方法,包括:

获取证明参数和待证明数据,对所述证明参数和所述待证明数据进行电路合成处理,得到R1CS数据,其中,用于电路合成处理的电路包括至少一个子电路,所述R1CS数据包括至少一个R1CS子数据,每个所述子电路用于构造一个所述R1CS子数据;

当存在尚未被FFT计算处理的所述R1CS子数据时,基于所述R1CS子数据,使用GPU进行FFT计算处理,得到所述R1CS子数据对应的多项式数据;

当存在尚未被FFT计算处理的所述R1CS子数据时,基于所述R1CS子数据及所述R1CS子数据对应的多项式数据,使用CPU进行MultiExp计算处理,得到所述R1CS子数据对应的证明分量;

当所有的R1CS子数据均已被FFT计算处理时,基于所述R1CS子数据及所述R1CS子数据对应的多项式数据,使用所述CPU和所述GPU并行进行MultiExp计算处理,得到所述R1CS子数据对应的证明分量;

基于所述R1CS数据中所有的R1CS子数据对应的证明分量,生成证明。

通过上述方式,保证了CPU和GPU的计算资源得到最大化的利用,加快零知识证明的生成。

在其中的一些实施例中,所述CPU为多核多线程CPU,所述CPU使用至少一个线程进行MultiExp计算处理,其中,每个线程包括多个协程,所述多个协程用于并发处理一个所述R1CS子数据对应的证明分量。

通过上述方式,多协程并发处理一个R1CS子数据,能够保障各个R1CS子数据能够按照一定的顺序有序地被计算,有利于加快CPU的资源调度和回收。

在其中的一些实施例中,所述CPU为多核多线程CPU,所述CPU使用多个线程进行MultiExp计算处理,其中,所述多个线程用于并行处理一个所述R1CS子数据对应的证明分量。

通过上述方式,对不同的证明分量对应的MultiExp计算过程进行资源隔离,可以加快整个证明过程的速度。

在其中的一些实施例中,基于所述R1CS子数据,使用GPU进行FFT计算处理,得到所述R1CS子数据对应的多项式数据包括:

使用GPU对所述至少一个R1CS子数据依次进行FFT计算处理,得到与各所述R1CS子数据对应的多项式数据。

通过上述方式,可以减少资源竞争和冲突,加快GPU的资源回收的效率。

在其中的一些实施例中,基于所述R1CS子数据及所述R1CS子数据对应的多项式数据,使用CPU进行MultiExp计算处理,得到所述R1CS子数据对应的证明分量包括:

基于所述R1CS子数据,使用CPU进行MultiExp计算处理,得到所述R1CS子数据对应的证明分量的第一分量数据,其中,所述第一分量数据与所述R1CS子数据对应的多项式数据无关;

基于所述R1CS子数据及所述R1CS子数据对应的多项式数据,使用CPU进行MultiExp计算处理,得到所述R1CS子数据对应的证明分量的第二分量数据,其中,所述第二分量数据所述R1CS子数据对应的多项式数据相关;

基于所述第一分量数据和所述第二分量数据,获取所述R1CS子数据对应的证明分量。

通过上述方式,将MultiExp计算处理的过程可以进一步分成与多项式数据无关的第一分量数据的计算过程,以及与多项式数据相关的第二分量数据的计算过程,其中,与多项式数据无关的第一分量数据可以在进行FFT计算时并行计算,从而进一步提高各个证明分量的计算速度。

第二方面,本申请实施例提供了一种用于零知识证明的证明系统,包括:输入装置、电路、GPU和CPU,所述输入装置与所述电路连接,所述电路与所述CPU连接,所述CPU与所述GPU连接,其中,

所述输入装置,用于获取证明参数和待证明数据;

所述电路包括至少一个子电路,所述电路用于对所述证明参数和所述待证明数据进行电路合成处理,得到R1CS数据,其中,所述R1CS数据包括至少一个R1CS子数据,每个所述子电路用于构造一个所述R1CS子数据;

所述GPU用于当存在尚未被当存在尚未被FFT计算处理的所述R1CS子数据时,基于所述R1CS子数据进行FFT计算处理,得到所述R1CS子数据对应的多项式数据;以及所述GPU用于当所有的R1CS子数据均已被FFT计算处理时,基于所述R1CS子数据及所述R1CS子数据对应的多项式数据,与所述CPU并行进行MultiExp计算处理,得到所述R1CS子数据对应的证明分量;

所述CPU用于当存在尚未被FFT计算处理的所述R1CS子数据时,基于所述R1CS子数据及所述R1CS子数据对应的多项式数据进行MultiExp计算处理,得到所述R1CS子数据对应的证明分量;以及所述CPU用于当所有的R1CS子数据均已被FFT计算处理时,基于所述R1CS子数据及所述R1CS子数据对应的多项式数据,与所述GPU并行进行MultiExp计算处理,得到所述R1CS子数据对应的证明分量;

所述CPU,还用于基于所述R1CS数据中所有的R1CS子数据对应的证明分量,生成证明。

在其中的一些实施例中,所述CPU为多核多线程CPU,所述CPU使用至少一个线程进行MultiExp计算处理,其中,每个线程包括多个协程,所述多个协程用于并发处理一个所述R1CS子数据对应的证明分量。

在其中的一些实施例中,所述CPU为多核多线程CPU,所述CPU使用多个线程进行MultiExp计算处理,其中,所述多个线程用于并行处理一个所述R1CS子数据对应的证明分量。

第三方面,本申请实施例提供了一种电子设备,包括存储器、处理器以及存储在所述存储器中并可在所述处理器上运行的计算机程序,所述处理器执行所述计算机程序时实现如第一方面所述的用于零知识证明的证明方法的步骤。

第四方面,本申请实施例提供了一种计算机可读存储介质,所述计算机可读存储介质存储有计算机程序,所述计算机程序被处理器执行时实现如第一方面所述的用于零知识证明的证明方法的步骤。

综上所述,通过本申请实施例提供的用于零知识证明的证明方法、系统、电子设备和计算机可读存储介质,当存在尚未被FFT计算处理的R1CS子数据时,基于R1CS子数据,使用GPU进行FFT计算处理,得到R1CS子数据对应的多项式数据;以及基于R1CS子数据及R1CS子数据对应的多项式数据,使用CPU进行MultiExp计算处理,得到R1CS子数据对应的证明分量。当所有的R1CS子数据均已被FFT计算处理时,基于R1CS子数据及R1CS子数据对应的多项式数据,使用CPU和GPU并行进行MultiExp计算处理,得到R1CS子数据对应的证明分量;最后基于R1CS数据中所有的R1CS子数据对应的证明分量,生成证明。本申请实施例相较于相关技术中证明过程主要在GPU中计算的方式而言,至少能够加快零知识证明的生成。

附图说明

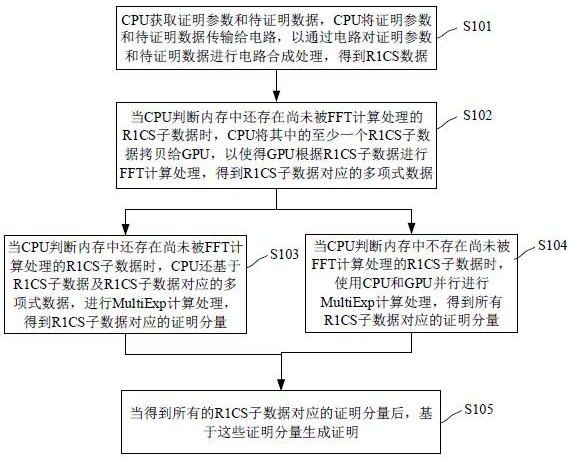

图1是本申请实施例提供的用于零知识证明的证明方法的流程图。

图2是相关技术提供的零知识证明的证明方法的示意图。

图3是本申请实施例提供的零知识证明的证明方法的示意图。

图4是本申请实施例提供的用于零知识证明的证明系统的结构框图。

图5是本申请实施例提供的电子设备的示意图。

具体实施方式

为更清楚地理解本申请的目的、技术方案和优点,下面结合附图和实施例,对本申请进行了描述和说明。

除另作定义外,本申请所涉及的技术术语或者科学术语应具有本申请所属技术领域具备一般技能的人所理解的一般含义。在本申请中的“一”、“一个”、“一种”、“该”、“这些”等类似的词并不表示数量上的限制,它们可以是单数或者复数。在本申请中所涉及的术语“包括”、“包含”、“具有”及其任何变体,其目的是涵盖不排他的包含;例如,包含一系列步骤或模块(单元)的过程、方法和系统、产品或设备并未限定于列出的步骤或模块(单元),而可包括未列出的步骤或模块(单元),或者可包括这些过程、方法、产品或设备固有的其他步骤或模块(单元)。在本申请中所涉及的“连接”、“相连”、“耦接”等类似的词语并不限定于物理的或机械连接,而可以包括电气连接,无论是直接连接还是间接连接。在本申请中所涉及的“多个”是指两个或两个以上。“和/或”描述关联对象的关联关系,表示可以存在三种关系,例如,“A和/或B”可以表示:单独存在A,同时存在A和B,单独存在B这三种情况。通常情况下,字符“/”表示前后关联的对象是一种“或”的关系。在本申请中所涉及的术语“第一”、“第二”、“第三”等,只是对相似对象进行区分,并不代表针对对象的特定排序。

Groth16证明系统包括三个过程,分别为设置过程、证明过程和验证过程。本申请实施例提供了一种用于零知识证明的证明方法,目的是优化Groth16的证明过程,以加快零知识证明的产生。

一个QAP实例可以用如下关系式表示:

其中,

用QAP问题表示,上述关系式定义了公开信息

从上述表达式可以看出,已知

其中,

Groth16算法的证明过程的计算可以分为FFT计算部分和MultiExp计算两个部分。

其中,FFT计算的目的是将电路合成产生的R1CS数据转换成QAP问题的描述。对于 一个QAP实例,根据公式(1),在选定域S上,已知

在已知域T以及相应的

MultiExp计算的目的则是基于QAP问题的描述生成证明。在MultiExp计算中,证明 者选择两个随机数r、s,并计算证明

其中,

其中,

图1是本申请实施例提供的用于零知识证明的证明方法的流程图,如图1所示,该流程包括如下步骤:

步骤S101,CPU获取证明参数和待证明数据,CPU将证明参数和待证明数据传输给电路,以通过电路对证明参数和待证明数据进行电路合成处理,得到R1CS数据,其中,用于电路合成处理的电路包括至少一个子电路,R1CS数据包括至少一个R1CS子数据,每个子电路用于构造一个R1CS子数据。

其中,证明参数在设置过程中生成,可以是事先通过多方安全计算(MPC)生成的公共参考串(Common Reference String,简称为CRS)数据。证明参数经过R1CS电路进行合成(Synthesize),R1CS电路为事先构造的电路。本实施例中用于电路合成处理的电路包括至少一个子电路,每个子电路用于构造一个R1CS子数据。在本实施例中,通过将电路拆分为至少一个子电路,进而可以由每个子电路构造的R1CS子数据分别生成证明分量,可以使得每个生成证明分量的计算过程占用较小的资源,便于对生成证明分量的过程进行并行化处理,从而缩短生成证明的整体时长。

步骤S102,CPU判断内存中是否存在尚未被FFT计算处理的R1CS子数据,若存在,则将其中的至少一个R1CS子数据拷贝给GPU,以使得GPU根据R1CS子数据进行FFT计算处理,得到R1CS子数据对应的多项式数据。

由于FFT计算中涉及到大量并行的计算,采用GPU进行FFT计算处理,可以显著缩短FFT计算处理的耗时。

步骤S103,同时,当CPU判断内存中还存在尚未被FFT计算处理的R1CS子数据时,CPU还基于R1CS子数据及R1CS子数据对应的多项式数据,进行MultiExp计算处理,得到R1CS子数据对应的证明分量。

步骤S104,当CPU判断内存中不存在尚未被FFT计算处理的R1CS子数据,即所有的R1CS子数据均已被FFT计算处理时,CPU将拷贝至少一个R1CS子数据及其对应的多项式数据给GPU,以使得GPU基于R1CS子数据及其对应的多项式数据进行MultiExp计算处理。同时,CPU也基于剩余的R1CS子数据及其对应的多项式数据进行MultiExp计算处理。通过使用CPU和GPU并行进行MultiExp计算处理,得到所有R1CS子数据对应的证明分量。

步骤S105,当得到所有的R1CS子数据对应的证明分量后,基于这些证明分量生成证明。其中,最终生成的证明可以为这些证明分量的集合,也可以是由这些证明分量运算而得到的一个证明结果。

通过上述的步骤,将电路拆分成至少一个子电路,从而将一个证明的生成过程变为生成多个证明分量的过程以实现多个证明分量的计算。在进行证明分量的生成过程中,优先使用GPU进行FFT计算,并且在GPU进行FFT计算同时使用CPU进行MultiExp计算。由于MultiExp计算耗时通常大于FFT计算的耗时,当所有FFT计算已经完成而MultiExp计算尚未完成时,CPU又将MultiExp计算的一部分任务分配给GPU,以实现CPU和GPU并行地进行剩余的MultiExp计算。通过上述的步骤,保证了CPU和GPU的计算资源得到最大化的利用,加快零知识证明的生成。

图2是相关技术提供的零知识证明的证明方法的示意图,如图2所示的相关技术中,证明参数和待证明数据经电路合成处理后,首先由GPU进行FFT计算,此时CPU空闲;当GPU的FFT计算结束后,再由CPU和GPU进行MultiExp计算。采用该证明方法,在配置有8张Nvidia的2080Ti系列GPU的计算机设备中,执行一个具有亿级数量的电路约束的零知识证明任务,需要大约40分钟时间。

图3是本申请实施例提供的零知识证明的证明方法的示意图,如图3所示,在本申 请实施例中,证明参数和待证明数据经电路合成处理后,由GPU进行FFT计算,在第一个R1CS 子数据对应的多项式数据尚未计算得到时,CPU可以空闲,也可以同时进行部分MultiExp计 算,例如进行与

如前,由公式(3)、公式(4)和公式(5)可知,证明

步骤S103-1,CPU基于R1CS子数据进行MultiExp计算处理,得到R1CS子数据对应的证明分量的第一分量数据,其中,第一分量数据与R1CS子数据对应的多项式数据无关。

步骤S103-2,CPU基于R1CS子数据及R1CS子数据对应的多项式数据,进行MultiExp计算处理,得到R1CS子数据对应的证明分量的第二分量数据,其中,第二分量数据R1CS子数据对应的多项式数据相关。

步骤S103-3,CPU基于第一分量数据和第二分量数据,获取R1CS子数据对应的证明分量。

具体而言,第一分量数据包括:

在其中的一些实施例中,上述的CPU为多核多线程CPU,CPU使用至少一个线程进行MultiExp计算处理,其中,每个线程包括多个协程,多个协程用于并发处理一个R1CS子数据对应的证明分量。其中,在每个线程中进行MultiExp计算时,该线程中的多个协程并发进行上述的第一分量数据和/或第二分量数据的计算。通过多协程并发处理一个R1CS子数据,能够保障各个R1CS子数据能够按照一定的顺序有序地被计算,有利于加快CPU的资源调度和回收。

在本申请实施例中,一个证明过程被分成了多个证明分量的计算过程,这些证明分量的计算过程可以看成是多个子任务的并行处理。多个子任务的并行处理,导致大量的资源竞争和冲突,进而导致整个证明过程因资源竞争和冲突而增加了耗时。因此,可以通过对各个证明分量的计算过程进行资源隔离,从而缓解资源竞争和冲突。在本实施例中,通过对不同的证明分量对应的MultiExp计算过程进行资源隔离以加快整个证明过程的速度,隔离的方式是每个MultiExp计算采用独立的线程。即本实施例中采用多核多线程CPU,该CPU使用多个线程进行MultiExp计算处理,其中,多个线程用于并行处理一个R1CS子数据对应的证明分量。

同样为了减少资源竞争和冲突,加快资源回收的效率,在一些实施例中对至少一个R1CS子数据进行FFT计算时,使用GPU对至少一个R1CS子数据依次进行FFT计算处理,得到与各R1CS子数据对应的多项式数据。

应理解,上述实施例中各步骤的序号的大小并不意味着执行顺序的先后,各过程的执行顺序应以其功能和内在逻辑确定,而不应对本发明实施例的实施过程构成任何限定。

本申请实施例还提供了一种用于零知识证明的证明系统,该系统可用于实现上述的用于零知识证明的证明方法,在上述方法实施例中已经进行过的描述,可以结合在本实施例中对证明系统的工作过程进行描述和说明,在此将不再赘述。

参照图4,该证明系统包括:输入装置41、电路42、GPU 44和CPU 43,其中,输入装置与电路连接,电路与CPU连接,CPU与GPU连接。

输入装置41,用于获取证明参数和待证明数据;

电路42包括至少一个子电路,电路42用于对证明参数和待证明数据进行电路合成处理,得到R1CS数据,其中,R1CS数据包括至少一个R1CS子数据,每个子电路用于构造一个R1CS子数据;

GPU 44用于当存在尚未被当存在尚未被FFT计算处理的R1CS子数据时,基于R1CS子数据进行FFT计算处理,得到R1CS子数据对应的多项式数据;以及GPU 44用于当所有的R1CS子数据均已被FFT计算处理时,基于R1CS子数据及R1CS子数据对应的多项式数据,与CPU 43并行进行MultiExp计算处理,得到R1CS子数据对应的证明分量;

CPU 43用于当存在尚未被FFT计算处理的R1CS子数据时,基于R1CS子数据及R1CS子数据对应的多项式数据进行MultiExp计算处理,得到R1CS子数据对应的证明分量;以及CPU 43用于当所有的R1CS子数据均已被FFT计算处理时,基于R1CS子数据及R1CS子数据对应的多项式数据,与GPU 44并行进行MultiExp计算处理,得到R1CS子数据对应的证明分量;

CPU 43,还用于基于R1CS数据中所有的R1CS子数据对应的证明分量,生成证明。

在其中的一些实施例中,CPU 43为多核多线程CPU,CPU 43使用至少一个线程进行MultiExp计算处理,其中,每个线程包括多个协程,多个协程用于并发处理一个R1CS子数据对应的证明分量。

在其中的一些实施例中,CPU 43为多核多线程CPU,CPU 43使用多个线程进行MultiExp计算处理,其中,多个线程用于并行处理一个R1CS子数据对应的证明分量。

本申请实施例还提供了一种电子设备,该电子设备可以是服务器,其内部结构图可以如图5所示。该电子设备包括通过系统总线54连接的处理器51、存储器52和网络接口53。其中,该电子设备的处理器51用于提供计算和控制能力。该电子设备的存储器52包括非易失性存储介质、内存储器。该非易失性存储介质存储有操作系统、计算机程序和数据库。该内存储器为非易失性存储介质中的操作系统和计算机程序的运行提供环境。该电子设备的网络接口53用于与外部的终端通过网络连接通信。该计算机程序被处理器执行时以实现如下步骤:

S1,获取证明参数和待证明数据,对证明参数和待证明数据进行电路合成处理,得到R1CS数据,其中,用于电路合成处理的电路包括至少一个子电路,R1CS数据包括至少一个R1CS子数据,每个子电路用于构造一个R1CS子数据;

S2,当存在尚未被FFT计算处理的R1CS子数据时,基于R1CS子数据,使用GPU进行FFT计算处理,得到R1CS子数据对应的多项式数据;

S3,当存在尚未被FFT计算处理的R1CS子数据时,基于R1CS子数据及R1CS子数据对应的多项式数据,使用CPU进行MultiExp计算处理,得到R1CS子数据对应的证明分量;

S4,当所有的R1CS子数据均已被FFT计算处理时,基于R1CS子数据及R1CS子数据对应的多项式数据,使用CPU和GPU并行进行MultiExp计算处理,得到R1CS子数据对应的证明分量;

S5,基于R1CS数据中所有的R1CS子数据对应的证明分量,生成证明。

该计算机程序被处理器执行时能实现上述方法实施例中任一种用于零知识证明的证明方法。

本申请实施例还提供了一种计算机可读存储介质,其上存储有计算机程序,计算机程序被处理器执行时实现以下步骤:

S1,获取证明参数和待证明数据,对证明参数和待证明数据进行电路合成处理,得到R1CS数据,其中,用于电路合成处理的电路包括至少一个子电路,R1CS数据包括至少一个R1CS子数据,每个子电路用于构造一个R1CS子数据;

S2,当存在尚未被FFT计算处理的R1CS子数据时,基于R1CS子数据,使用GPU进行FFT计算处理,得到R1CS子数据对应的多项式数据;

S3,当存在尚未被FFT计算处理的R1CS子数据时,基于R1CS子数据及R1CS子数据对应的多项式数据,使用CPU进行MultiExp计算处理,得到R1CS子数据对应的证明分量;

S4,当所有的R1CS子数据均已被FFT计算处理时,基于R1CS子数据及R1CS子数据对应的多项式数据,使用CPU和GPU并行进行MultiExp计算处理,得到R1CS子数据对应的证明分量;

S5,基于R1CS数据中所有的R1CS子数据对应的证明分量,生成证明。

该计算机程序被处理器执行时能实现上述方法实施例中任一种用于零知识证明的证明方法。

本领域普通技术人员可以理解实现上述实施例方法中的全部或部分流程,是可以通过计算机程序来指令相关的硬件来完成,的计算机程序可存储于一非易失性计算机可读取存储介质中,该计算机程序在执行时,可包括如上述各方法的实施例的流程。其中,本发明所提供的各实施例中所使用的对存储器、存储、数据库或其它介质的任何引用,均可包括非易失性和/或易失性存储器。非易失性存储器可包括只读存储器(ROM)、可编程ROM(PROM)、电可编程ROM(EPROM)、电可擦除可编程ROM(EEPROM)或闪存。易失性存储器可包括随机存取存储器(RAM)或者外部高速缓冲存储器。作为说明而非局限,RAM以多种形式可得,诸如静态RAM(SRAM)、动态RAM(DRAM)、同步DRAM(SDRAM)、双数据率SDRAM(DDRSDRAM)、增强型SDRAM(ESDRAM)、同步链路(Synchlink) DRAM(SLDRAM)、存储器总线(Rambus)直接RAM(RDRAM)、直接存储器总线动态RAM(DRDRAM)、以及存储器总线动态RAM(RDRAM)等。

应该明白的是,这里描述的具体实施例只是用来解释这个应用,而不是用来对它进行限定。根据本申请提供的实施例,本领域普通技术人员在不进行创造性劳动的情况下得到的所有其它实施例,均属本申请保护范围。

显然,附图只是本申请的一些例子或实施例,对本领域的普通技术人员来说,也可以根据这些附图将本申请适用于其他类似情况,但无需付出创造性劳动。另外,可以理解的是,尽管在此开发过程中所做的工作可能是复杂和漫长的,但是,对于本领域的普通技术人员来说,根据本申请披露的技术内容进行的某些设计、制造或生产等更改仅是常规的技术手段,不应被视为本申请公开的内容不足。

“实施例”一词在本申请中指的是结合实施例描述的具体特征、结构或特性可以包括在本申请的至少一个实施例中。该短语出现在说明书中的各个位置并不一定意味着相同的实施例,也不意味着与其它实施例相互排斥而具有独立性或可供选择。本领域的普通技术人员能够清楚或隐含地理解的是,本申请中描述的实施例在没有冲突的情况下,可以与其它实施例结合。

以上实施例仅表达了本申请的几种实施方式,其描述较为具体和详细,但并不能因此而理解为对专利保护范围的限制。应当指出的是,对于本领域的普通技术人员来说,在不脱离本申请构思的前提下,还可以做出若干变形和改进,这些都属于本申请的保护范围。因此,本申请的保护范围应以权利要求为准。

- 用于零知识证明的证明方法、系统、电子设备和存储介质

- 一种零知识证明方法及装置、电子设备、存储介质