一种高密度计数型质谱仪探测器的检出电路系统

文献发布时间:2023-06-19 18:25:54

技术领域

本发明属于质谱仪技术领域,具体涉及一种高密度计数型质谱仪探测器的检出电路系统。

背景技术

质谱仪通常采用电子倍增器作为检测离子个数的传感器。电子倍增器收到离子轰击后,经过逐级放大后最终形成毫安级的电流信号。计数型探测器检出电路系统将该信号转化为电压,并通过放大和比较,最终输出一个脉冲信号,该信号宽度一般为几纳秒至几百纳秒不等,信号宽度由电子倍增器确定。脉冲信号通过微处理单片机或者FPGA(FieldProgrammable Gate Array,现场可编程的门阵列)进行计数,单位时间内的计数最终通过上位机软件转换为样品的浓度。

如上所说,现有的计数型探测器检出电路系统,通过对放大和比较后脉冲信号的进行计数。在这种情况下,如果前端离子轰击的离子时间间隔足够小,就会存在输出信号堆叠的情况。在这种情况下现有的电路检出系统只能检出一个脉冲(如图1所示),从而导致信号的丢失,进而影响整个系统的灵敏度。

进一步的,由于样品浓度增加时,所检测的离子浓度也会增加,上述堆叠现象也会愈发严重。堆叠现象影响计数从本质上可以理解为系统无法连续检测信号的能力,即当离子间的时间间隔小于倍增器输出的信号宽度时,堆叠现象就会产生,我们把这个时间称作检测系统的死时间,死时间越大对技数丢失的影响也就越大。

对于计数型探测器检出电路系统,当所检测到的离子间的时间间隔是随机的(在固定浓度下),如果检测器系统两个入射离子几乎同时到达同一探测器时,因产生的脉冲叠加,而不被记录,导致计数丢失的现象,我们称之为瘫痪型计数丢失和非瘫痪型计数丢失

y=xe

其中t为上述描述中检测系统的死时间。

而非瘫痪型计数型探测器检出电路系统为第一个输入脉冲将产生一个输出脉冲,并将使电路失效一段时间t。在电路重新启用之前到达的任何附加脉冲将不被计算。在任何时间间隔t后,任何非零的输入事件数将导致一个输出脉冲。其系统检出的计数率(y)和系统输入的计数率(x)的函数对应关系如下:

如上所述,本系统属于瘫痪型计数型探测器检出电路系统,基于上述公式分别计算当输入的离子浓度为10

发明内容

本发明为了解决现有计数型探测器检出电路系统在离子时间小于电子倍增器输出信号时,电子倍增器输出的信号发生堆积,从而导致比较器输出的脉冲发生堆积,丢失计数,使计数型探测器检出电路系统引入检测盲区(死时间)的问题,提供了一种高密度计数型质谱仪探测器的检出电路系统,包含电流电压转换电路和放大电路,放大电路输入端与电流电压转换电路输出端连接,还包括:

低阈值比较电路,所述低阈值比较电路的一输入端连接放大电路的输出端,所述低阈值比较电路的另一输入端连接第一阈值电压,所述第一阈值电压设定值为基线噪声的1.2倍-1.5倍;

高阈值比较电路,所述高阈值比较电路的一输入端连接放大电路的输出端,所述高阈值比较电路的另一输入端连接第二阈值电压;

进一步的,还包括TDC电路,用于计算低阈值比较电路触发形成的脉冲信号的宽度,所述TDC电路输入端与低阈值比较电路输出端连接。

进一步的,还包括微处理器单片机或FPGA电路,用于计数和信号判断,所述微处理器单片机或FPGA电路的一输入端与TDC电路输出端连接,所述微处理器单片机或FPGA电路的另一输入端与高阈值比较电路输出端连接。

进一步的,所述计数和信号判断为计算高阈值比较电路和低阈值比较电路所触发的检测信号数量,并将信号判断为正常信号和堆积信号。

进一步的,所述正常信号为TDC电路计算所得的脉宽长度为单个信号宽度。

进一步的,所述堆积信号为两种,当高阈值比较电路触发或TDC电路计算所得的宽度大于或等于正常信号宽度1.5倍时均判定为堆积信号。

本发明的优点如下:

(1)本发明通过高低阈值两个比较电路和计算脉冲输出的宽度来辨别堆积信号并推算所堆积的个数,从而避免在堆积发生时出现丢数。当计数型探测器检出电路系统不再存在计数死时间的情况时,将不再存在瘫痪型计数丢失和非瘫痪型计数丢失,从而使计数型探测器检出电路系统的计数更加靠近真实离子数量,避免因为信号堆叠引起的计数丢失。

(2)提高了计数型探测器检出电路系统的灵敏度,特别是计数率超过10

(3)提高了计数型探测器检出电路系统在高剂量检测中的可行性。

附图说明

图1为现有探测器检出电路系统信号堆叠示意图;

图2为信号宽度为20纳秒和100纳秒情况下的信号计数丢失数据图;

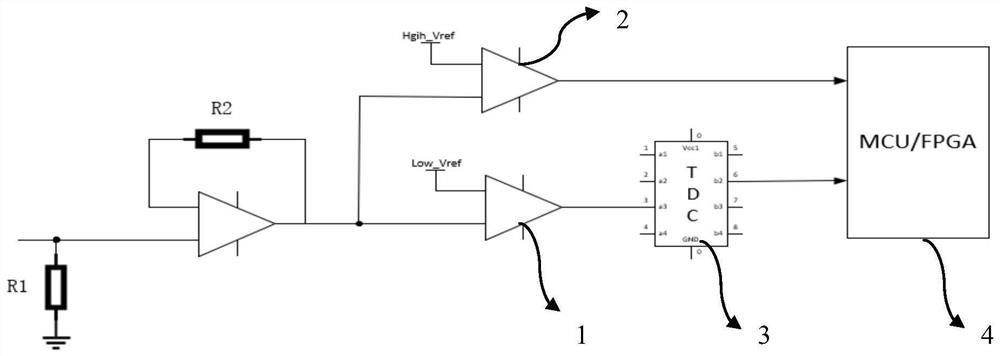

图3为本发明的检出电路系统电路图;

图4为第二个信号在第一个信号达峰时出现的曲线示意图;

图5为第二个信号早于第一个信号达峰时出现的曲线示意图;

图6为第二个信号晚在第一个信号达峰时出现的曲线示意图;

图7为三种类堆积情况下的系统响应示意图。

图中:1-低阈值比较电路,2-高阈值比较电路,3-TDC(Time-to-DigitalConverter)电路,4-微处理器单片机或者FPGA电路。

具体实施方式

下面结合附图和实施例对本发明的技术方案做进一步的说明。

本发明涉及一种高密度计数型质谱仪探测器的检出电路系统,如图3所示为本发明的硬件电路图,硬件电路部分包含电流电压转换电路和放大电路,电流电压转换电路输出端连接放大电路输入端,还包含低阈值比较电路1,高阈值比较电路2,TDC(Time-to-Digital Converter)电路3,微处理器单片机或者FPGA电路4,其中:

低阈值比较电路1,用于触发倍增器输出的检测信号并去除基线噪声干扰,所述低阈值比较电路1的一输入端连接放大电路的输出端,所述低阈值比较电路1的另一输入端连接第一阈值电压,所述第一阈值电压设定值为基线噪声的1.2倍-1.5倍;

高阈值比较电路2,所述高阈值比较电路2的一输入端连接放大电路的输出端,所述高阈值比较电路2的另一输入端连接第二阈值电压,所述第二阈值电压设定值高于单个信号的峰值;

TDC电路3,用于计算低阈值比较电路1触发形成的脉冲信号的宽度,所述TDC电路3输入端与低阈值比较电路1输出端连接。

微处理器单片机或FPGA电路4,用于计数和信号判断,所述微处理器单片机或FPGA电路4的一输入端与TDC电路3输出端连接,所述微处理器单片机或FPGA电路4的另一输入端与高阈值比较电路2输出端连接。

所述计数和信号判断为计算高阈值比较电路2和低阈值比较电路1所触发的检测信号数量,并将信号判断为正常信号和堆积信号。

所述正常信号为TDC电路3计算所得的脉宽长度为单个信号宽度,并允许正常的晃动范围。

所述堆积信号为两种,当高阈值比较电路2触发或TDC电路3计算所得的宽度大于或等于正常信号宽度1.5倍时均判定为堆积信号。

如上所述,本设计中通过高低阈值比较电路和TDC电路来甄别当离子检测时间间隔过短所引起的检测信号堆积情况,从而恢复发生堆积时的信号个数。电子倍增管输出的信号为类高斯信号,所以信号的达峰时间约等于信号宽度的50%。我们以第二个信号的到达时间为第一份信号的达峰时间进行讨论,共分为三种情况:

如图4所示为当第二个信号在第一个信号达峰时出现,此时由于信号叠加,叠加后的峰高刚好等于单个信号的峰高,宽度会等于正常信号的1.5倍;

如图5所示为当第二个信号早于第一个信号达峰时出现,则由于信号叠加,叠加后的峰高会高于单个信号的峰高,但是宽度会小于正常信号的1.5倍;

相反,如图6所示,如果第二个信号晚于第一个峰达峰后出现,则由于信号叠加,叠加后的峰高会小于于单个信号的峰高,但是两个信号叠加后宽度会大于正常信号的1.5倍。分别对应第二个信号在第一个信号达峰时出现,以及在达峰时间前后出现的情况,其中*曲线为第一个信号,+曲线为第二个信号,实线曲线为叠加后的曲线。因此本设计高阈值设定为略高于一个正常信号的峰值,将宽度的判断设定为略大于或等于正常信号的1.5倍。

如图7所示为本系统在上述三类堆积情况下系统响应的三种情况,其中单个信号时T0等于正常型号宽度;当第二个信号晚于第一个信号达峰或在第一个信号达峰时出现,高阈值比较器没有触发,但是低阈值输出脉冲宽度大于或等于正常信号的1.5倍;第二个信号早于第一个信号达峰时出现时,高阈值比较器产生触发信号,但是低阈值输出脉冲宽度小于正常信号的1.5倍。由此通过高阈值比较电路及低阈值比较电路和计算脉冲输出的TDC电路来辨别堆积信号并推算所堆积的个数,从而避免在堆积发生时出现丢数。

以上所述,仅为本发明的具体实施方式,但本发明的保护范围并不局限于此,熟悉该本领域的技术人员应该明白本发明包括但不限于上面具体实施方式中描述的内容。任何不偏离本发明的功能和结构原理的修改都将包括在权利要求书的范围中。

- 一种用于光电导型红外探测器阵列的读出电路系统

- 一种密封型拼接高计数率多气隙阻性板室探测器