栅极驱动装置

文献发布时间:2023-06-19 18:53:06

技术领域

本发明涉及一种显示器领域,且特别是有关于一种栅极驱动装置。

背景技术

薄膜晶体管液晶显示器(Thin Film Transistor Liquid Crystal Displays,TFT-LCDs)已成为现代显示科技产品的主流。相对于多晶硅薄膜晶体管(Poly-Si TFT),使用非晶硅薄膜晶体管(a-Si TFT)所制作的显示器能够降低生产成本,且能够在低温下制作在大面积的玻璃基板上,均匀性好且能提高生产速率。

随着系统整合式玻璃面板(System-on-Glass,SOG)的概念被陆续提出,近来许多产品将显示器驱动电路中的栅极驱动装置整合在玻璃基板上,即为GOA(Gate Driver onArray)电路。GOA具有诸多优势,除了可以减少显示器边框的面积以达成窄边框之外,更能够减少栅极扫描驱动IC的使用,降低购买IC成本及避免玻璃与IC贴合时断线问题,用以提升产品良率。

然而,当显示器应用在汽车产品上时,可能会遇到长期使用及广范的温度操作的问题,如在极端低温(例如是摄氏-40度)与极端高温(例如是摄氏70度)。由此可知,如何设计出在极端温度下仍具有高信赖性的驱动能力,是目前栅极驱动装置的开发重点之一。

发明内容

本发明提供一种具有高信赖性的栅极驱动装置。

本发明的栅极驱动装置包括多个栅极驱动单元。所述多个栅极驱动单元中的第n级栅极驱动单元包括电源电路、输出电路以及偏压控制电路。电源电路在第一时间区间反应于第n-m级复本信号将偏压节点的低偏压值充电至高偏压值。输出电路耦接于偏压节点。输出电路在第二时间区间反应于偏压节点的高偏压值以及对应的外部时钟提供第n级栅极驱动信号以及第n级复本信号。偏压控制电路耦接于偏压节点。偏压控制电路包括多个晶体管。偏压控制电路对所述多个晶体管的至少一者进行负偏压补偿操作,并在第一时间区间以及第二时间区间防止偏压节点的电压值下降。其中n以及m分别为正整数,并且n-m大于或等于1。

基于上述,第n级栅极驱动单元的偏压控制电路在第一时间区间以及第二时间区间防止偏压节点的电压值下降。除此之外,偏压控制电路还能够对所述多个晶体管的至少一者进行负偏压补偿操作。因此,栅极驱动装置能够在长期使用的情况下具有高信赖性的驱动能力。

为让本发明的上述特征和优点能更明显易懂,下文特举实施例,并配合所附图式作详细说明如下。

附图说明

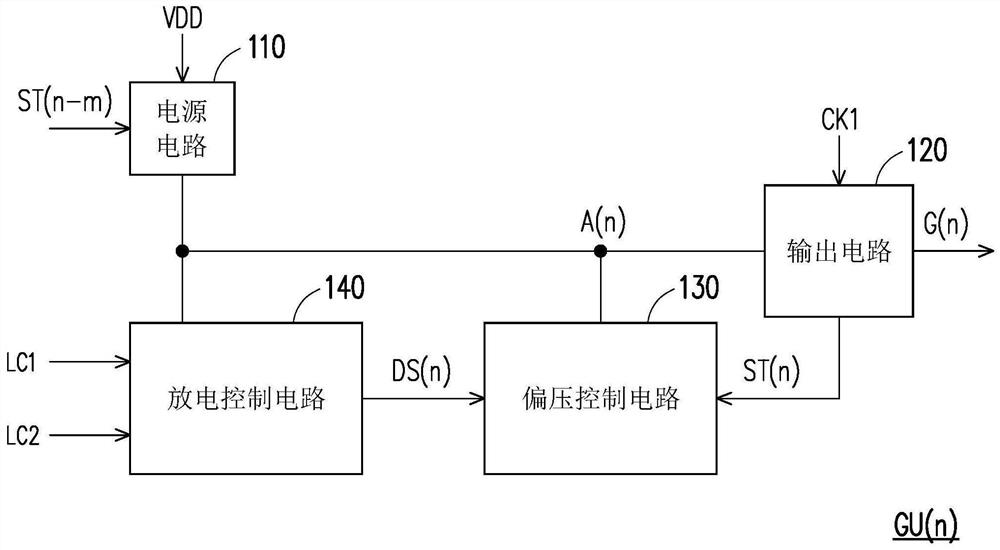

图1是依据本发明一实施例所绘示的栅极驱动装置的方块示意图。

图2是依据本发明一实施例所绘示的第n级栅极驱动单元的方块示意图。

图3是依据本发明一实施例所绘示的第n级栅极驱动单元的电路示意图。

图4是依据本发明一实施例所绘示的第n+1级栅极驱动单元的电路示意图。

图5是依据本发明一实施例所绘示的栅极驱动装置的部分时序图。

附图标记说明

100、200:栅极驱动装置

110、210、210’:电源电路

120、220、220’:输出电路

130、230、230’:偏压控制电路

140、240、240’:放电控制电路

231、231’:第一稳压及放电电路

232、232’:第二稳压及放电电路

A(n)、A(n+1):偏压节点

CK1、CK2、CK3、CK9、CK10:外部时钟

DS(n):第n级放电控制信号

DS(n+1):第(n+1)级放电控制信号

G(n):第n级栅极驱动信号

G(n+1):第(n+1)级栅极驱动信号

G(n+2):第(n+2)级栅极驱动信号

G(n+8):第(n+8)级栅极驱动信号

G(n+9):第(n+9)级栅极驱动信号

GU(n):第n级栅极驱动单元

GU(n+1):第(n+1)级栅极驱动单元

GU(n+2):第(n+2)级栅极驱动单元

GU(n+8):第(n+8)级栅极驱动单元

GU(n+9):第(n+9)级栅极驱动单元

LC1:第一参考信号

LC2:第二参考信号

M1~M4、M1’~M4’、M7、M7’、M10~M17、M10’~M17’:晶体管

M5、M5’、M6、M6’、M8、M8’、M9、M9’:稳压晶体管

ST(n):第n级复本信号

ST(n-m):第(n-m)级复本信号

ST(n-6):第(n-6)级复本信号

ST(n-7):第(n-7)级复本信号

ST(n-8):第(n-8)级复本信号

ST(n+1):第(n+1)级复本信号

ST(n+8):第(n+8)级复本信号

ST(n+9):第(n+9)级复本信号

ST(n+10):第(n+10)级复本信号

ST(n+11):第(n+11)级复本信号

ST(n+12):第(n+12)级复本信号

ST(n+13):第(n+13)级复本信号

ST(n+k):第(n+k)级复本信号

T1、T2、T3、T4:时间区间

VDD:系统高电压

VSS:系统低电压

具体实施方式

本发明的部分实施例接下来将会配合附图来详细描述,以下的描述所引用的组件符号,当不同附图出现相同的组件符号将视为相同或相似的组件。这些实施例只是本发明的一部份,并未揭示所有本发明的可实施方式。更确切的说,这些实施例只是本发明的专利申请范围中的范例。

请参考图1,图1是依据本发明第一实施例所绘示的栅极驱动装置的示意图。在本实施例中,栅极驱动装置100包括多个栅极驱动单元。举例来说,在所述多个栅极驱动单元当中,第n级栅极驱动单元GU(n)会依据外部时钟CK1、系统高电压VDD以及第(n-8)级复本信号ST(n-8)提供第n级栅极驱动信号G(n)以及第n级复本信号ST(n)。第(n-8)级复本信号ST(n-8)来自于第(n-8)级栅极驱动单元(未示出)。第(n+1)级栅极驱动单元GU(n+1)会依据外部时钟CK2、系统高电压VDD以及第(n-7)级复本信号ST(n-7)提供第(n+1)级栅极驱动信号G(n+1)以及第(n+1)级复本信号ST(n+1),第(n-7)级复本信号ST(n-7)来自于第(n-7)级栅极驱动单元(未示出)。依此类推。

请参考图2,图2是依据本发明第一实施例所绘示的第n级栅极驱动单元的方块示意图。在本实施例中,第n级栅极驱动单元G(n)包括电源电路110、输出电路120以及偏压控制电路130。电源电路110在第一时间区间反应于第n-m级复本信号ST(n-m)将偏压节点A(n)的低偏压值充电至高偏压值。在本实施例中,n以及m分别为正整数,并且n-m大于或等于1。在本实施例中,第n-m级复本信号ST(n-m)处于高电压位准的时间区间不与第n级复本信号ST(n)处于高电压位准的时间区间重叠。因此,m例如等于8,本发明并不以m的数值为限。偏压节点A(n)会更早被充电,如此一来,栅极驱动装置100的偏压节点A(n)能够在低温条件下达到足够的电压。

在本实施例中,输出电路120耦接于偏压节点A(n)。输出电路120在第二时间区间反应于偏压节点A(n)的高偏压值以及对应的外部时钟提供第n级栅极驱动信号G(n)以及第n级复本信号ST(n)。

在本实施例中,偏压控制电路130耦接于偏压节点A(n)。偏压控制电路130包括多个晶体管。偏压控制电路130在第一时间区间以及第二时间区间防止偏压节点A(n)的电压值下降。如此一来,第n级栅极驱动单元G(n)能够在高温条件下防止偏压节点A(n)发生电压泄漏。此外,偏压控制电路130还对所述多个晶体管的至少一者进行负偏压补偿操作。

一般来说,GOA电路是由多个非晶硅TFT来实现。以n型非晶硅TFT为例,n型非晶硅TFT在被导通的情况下,n型非晶硅TFT的门坎电压(threshold voltage)值会随着时间的推移而提升。因此,GOA电路的电路表现也会随着时间的推移而有所变化。在本实施例中,偏压控制电路130在稳定偏压节点A(n)的电压值,还能够在至少一时间区间对偏压控制电路130本身的至少一晶体管进行负偏压补偿操作,从而恢复被补偿的晶体管的门坎电压值。如此一来,栅极驱动装置能够在长期使用的情况下具有高信赖性的驱动能力。

在本实施例中,在第三时间区间,输出电路120将偏压节点A(n)的电压值下拉到低偏压值。此外,在第三时间区间,偏压控制电路130会反应于第n级放电控制信号DS(n)将偏压节点A(n)的低电压值对偏压节点A(n)以及输出电路120进行抗噪声操作。

在本实施例中,第n级栅极驱动单元GU(n)还包括放电控制电路140。放电控制电路140耦接于偏压节点A(n)。放电控制电路140反应于偏压节点A(n)的电压值、第一参考信号LC1以及第二参考信号LC2来提供第n级放电控制信号DS(n)。

在本实施例中,第一参考信号LC1的极性以及第二参考信号LC2的极性分别基于画框(frame)时间来反转。在同一画框时间中,第一参考信号LC1的极性相反于第二参考信号LC2的极性。举例来说,在第一画框时间中,第一参考信号LC1的极性为正极性。第一参考信号LC1具有高电压位准(如,15伏特)。在第一画框时间中,第二参考信号LC2的极性则为负极性。第二参考信号LC2具有低电压位准(如,-12伏特)。在第一画框时间后的第二画框时间,第一参考信号LC1的极性为负极性。第一参考信号LC1具有低电压位准(如,-12伏特)。在第二画框时间中,第二参考信号LC2的极性则为正极性。第二参考信号LC2具有高电压位准(如,15伏特)。

请参考图3,图3是依据本发明一实施例所绘示的第n级栅极驱动单元的电路示意图。在本实施例中,第n级栅极驱动单元GU(n)包括电源电路210、输出电路220、偏压控制电路230以及放电控制电路240。电源电路210包括晶体管M1。晶体管M1的第一端接收系统高电压VDD。晶体管M1的第二端耦接至偏压节点A(n)。晶体管M1的控制端接收第(n-8)级复本信号ST(n-8)。当接收到高电压位准的第(n-8)级复本信号ST(n-8)时,晶体管M1会将系统高电压VDD的电压值提供至偏压节点A(n),从而将偏压节点A(n)的电压值抬升到高偏压值。在另一方面,当接收到低电压位准的第(n-8)级复本信号ST(n-8)时,晶体管M1则不会将系统高电压VDD的电压值提供至偏压节点A(n)。

输出电路220包括晶体管M2~M4。晶体管M2的第一端接收外部时钟CK1。晶体管M2的控制端耦接于偏压节点A(n)。晶体管M2的第二端用以输出第n级栅极驱动信号G(n)。因此,输出晶体管M2会反应于偏压节点A(n)的高偏压值将外部时钟CK1作为第n级栅极驱动信号G(n),并输出第n级栅极驱动信号G(n)。晶体管M3的第一端接收外部时钟CK1。晶体管M3的控制端耦接于偏压节点A(n)。晶体管M3的第二端用以输出第n级复本信号ST(n)。因此,晶体管M3会反应于偏压节点A(n)的高偏压值将外部时钟CK1作为第n级复本信号ST(n),并输出第n级复本信号ST(n)。晶体管M4的第一端耦接于偏压节点A(n)。晶体管M4的第二端耦接于系统低电压VSS。晶体管M4的控制端接收第(n+k)级复本信号ST(n+k)。晶体管M4会依据第(n+k)级复本信号ST(n+k)将偏压节点A(n)的电压值下拉到系统低电压VSS。在本实施例中,k等于9。

在本实施例中,偏压控制电路230包括第一稳压及放电电路231。在第一时间区间以及第二时间区间,第一稳压及放电电路231反应于第n级放电控制信号DS(n)的低电压位准来维持偏压节点A(n)的电压值。在第三时间区间,第一稳压及放电电路231反应于第n级放电控制信号DS(n)的高电压位准以及第一参考信号LC1的低电压位准来下拉偏压节点A(n)的电压值。

在本实施例中,第一稳压及放电电路231包括稳压晶体管M5、M6。稳压晶体管M5的第一端耦接于偏压节点A(n)。稳压晶体管M5的第二端接收第n级复本信号ST(n),稳压晶体管M5的控制端接收第n级放电控制信号DS(n)。稳压晶体管M6的第一端耦接于稳压晶体管M5的第二端,稳压晶体管M6的第二端耦接于第一参考信号LC1,稳压晶体管M6的控制端接收第n级放电控制信号DS(n)。

在第一时间区间以及第二时间区间,被断开的稳压晶体管M6反应于第一参考信号LC1以及第n级放电控制信号DS(n)被进行负偏压补偿操作。也就是说,稳压晶体管M6反应于第一参考信号LC1的高电压位准以及第n级放电控制信号DS(n)的低电压位准被进行负偏压补偿操作。除此之外,在第二时间区间,第n级复本信号ST(n)的高电压位准可用以支撑位于被断开的稳压晶体管M5的第二端的电压值,以防止偏压节点A(n)在高温条件下发生电压泄漏。进一步地,第一稳压及放电电路231还可以通过第n级复本信号ST(n)的高电压位准以及被断开的稳压晶体管M5的第一端与第二端之间的寄生电容耦合效应抬升偏压节点A(n)的电压值。

在本实施例中,第一稳压及放电电路231还包括晶体管M7。晶体管M7的第一端耦接于晶体管M2的第二端。晶体管M7的第二端耦接于系统低电压VSS。晶体管M7的控制端接收第n级放电控制信号DS(n)。因此,第一稳压及放电电路231还能够反应于第n级放电控制信号DS(n)的高电压位准来下拉第n级栅极驱动信号G(n)的电压值。

在本实施例中,偏压控制电路230包括第二稳压及放电电路232。在第一时间区间以及第二时间区间,第二稳压及放电电路232反应于第n+a级放电控制信号DS(n+a)的低电压位准来维持偏压节点A(n)的电压值。在第三时间区间,第二稳压及放电电路232反应于第n+a级放电控制信号的高电压位准以及第二参考信号LC2的低电压位准来下拉偏压节点A(n)的电压值。a为1以及-1的其中一者。

在本实施例中,a为1。因此,在第一时间区间以及第二时间区间,第二稳压及放电电路232反应于第n+1级放电控制信号DS(n+1)的低电压位准来维持偏压节点A(n)的电压值。在第三时间区间,第二稳压及放电电路232反应于第n+1级放电控制信号DS(n+1)的高电压位准以及第二参考信号LC2的低电压位准来下拉偏压节点A(n)的电压值。

在本实施例中,第二稳压及放电电路232包括稳压晶体管M8、M9。稳压晶体管M8的第一端耦接于偏压节点A(n)。稳压晶体管M8的第二端接收第n+1级复本信号ST(n+1)。稳压晶体管M8的控制端接收第n+1级放电控制信号DS(n+1)。稳压晶体管M9的第一端耦接于稳压晶体管M8的第二端。稳压晶体管M9的第二端耦接于第二参考信号LC2。稳压晶体管M9的控制端接收第n+1级放电控制信号DS(n+1)。

在第一时间区间以及第二时间区间,被断开的稳压晶体管M9反应于第二参考信号LC2以及第n+1级放电控制信号DS(n+1)被进行负偏压补偿操作。也就是说,稳压晶体管M9反应于第二参考信号LC2的高电压位准以及第n+1级放电控制信号DS(n+1)的低电压位准被进行负偏压补偿操作。除此之外,在第二时间区间,第n级复本信号ST(n)的高电压位准可用以支撑位于被断开的稳压晶体管M8的第二端的电压值,以防止偏压节点A(n)在高温条件下发生电压泄漏。进一步地,第二稳压及放电电路232还可以通过第n级复本信号ST(n)的高电压位准以及被断开的稳压晶体管M8的第一端与第二端之间的寄生电容耦合效应抬升偏压节点A(n)的电压值。

在此值得一提的是,第一稳压及放电电路231以及第二稳压及放电电路232分别基于不同的放电控制信号以及不同的参考信号来运行。也就是说,第一稳压及放电电路231以及第二稳压及放电电路232可交替休息。

在本实施例中,第二稳压及放电电路232还包括晶体管M10。晶体管M10的第一端耦接于晶体管M2的第二端。晶体管M10的第二端耦接于系统低电压VSS。晶体管M10的控制端接收第n+1级放电控制信号DS(n+1)。因此,第二稳压及放电电路232还能够反应于第n+1级放电控制信号DS(n+1)的高电压位准来下拉第n级栅极驱动信号G(n)。

在本实施例中,放电控制电路240耦接于偏压控制电路230以及偏压节点A(n)。放电控制电路240包括晶体管M11~M15。晶体管M11的第一端以及晶体管M11的控制端接收第二参考信号LC2。晶体管M12的第一端接收第二参考信号LC2,晶体管M12的控制端耦接于晶体管M11的第二端。晶体管M13的第一端耦接于晶体管M11的第二端,晶体管M13的控制端耦接于偏压节点A(n),晶体管M13的第二端耦接于系统低电压VSS。晶体管M14的第一端耦接于晶体管M12的第二端。晶体管M14的控制端耦接于偏压节点A(n)。晶体管M14的第二端耦接于系统低电压VSS。晶体管M15的第一端接收第二参考信号LC2。晶体管M15的控制端接收第一参考信号LC1。晶体管M15的第二端耦接于晶体管M12的第二端。晶体管M14的第一端与晶体管M12的第二端的连接节点Q(n)被作为放电控制电路240的输出端。

在本实施例中,在第一时间区间以及第二时间区间,晶体管M13、M14会基于偏压节点A(n)的高偏压值被导通。节点Q(n)的电压值被下拉到系统低电压VSS。因此,在第一时间区间以及第二时间区间,不论第一参考信号LC1、第二参考信号LC2的电压位准,放电控制电路240会提供具有低电压位准的第n级放电控制信号DS(n)。在第一时间区间以及第二时间区间,当第一参考信号LC1处于高电压位准并且第二参考信号LC2处于低电压位准时,晶体管M15被导通。因此,节点Q(n)的电压值可以被确保为用以进行负偏压补偿的低电压位准(约-12伏特)。

在第三时间区间,晶体管M13、M14会基于偏压节点A(n)的低偏压值被断开。当第一参考信号LC1处于高电压位准并且第二参考信号LC2处于低电压位准时,节点Q(n)的电压值被下拉到低电压位准。因此,放电控制电路240会提供具有低电压位准的第n级放电控制信号DS(n)。也因此,在第三时间区间,第一稳压及放电电路231的晶体管M6被进行负偏压补偿。当第一参考信号LC1处于低电压位准并且第二参考信号LC2处于高电压位准时,节点Q(n)的电压值为高电压位准。因此,放电控制电路240会提供具有高电压位准的第n级放电控制信号DS(n)。此外,晶体管M15也会反应于第一参考信号LC1的低电压位准以及第二参考信号LC2的高电压位准被进行负偏压补偿。

放电控制电路240在第三时间区间提供具有特定电压位准(如,高电压位准)的第n级放电控制信号DS(n)。在第一画框时间后的第二画框时间,放电控制电路240在第三时间区间则会具有另一特定电压位准(如,低电压位准)的第n级放电控制信号DS(n)。

举例来说,当第一参考信号LC1处于低电压位准并且第二参考信号LC2处于高电压位准时,放电控制电路240在第三时间区间中提供具有高电压位准的第n级放电控制信号DS(n)。因此,在第三时间区间中,第一稳压及放电电路231的晶体管M5~M7会被导通以对偏压节点A(n)以及输出电路220进行抗噪声操作。此时,第二稳压及放电电路232不运行。稳压晶体管M9会被进行负偏压补偿操作。

另举例来说,当第一参考信号LC1处于高电压位准并且第二参考信号LC2处于低电压位准时,放电控制电路240在第三时间区间中提供具有低电压位准的第n级放电控制信号DS(n)。因此,在第三时间区间中,第一稳压及放电电路231不运行。稳压晶体管M6会被进行负偏压补偿操作。第二稳压及放电电路232则会反应于第n+1级放电控制信号DS(n+1)的高电压位准以及第二参考信号LC2的低电压位准来对偏压节点A(n)以及输出电路220进行抗噪声操作。也就是说,第一稳压及放电电路231以及第二稳压及放电电路232可基于画框时间交替休息。

此外,放电控制电路240还包括晶体管M16、M17。晶体管M16的第一端耦接于所述晶体管M11的第二端。晶体管M16的控制端耦接于第n+a级放电控制电路的偏压节点。晶体管M16的第二端耦接于系统低电压VSS。晶体管M17的第一端耦接于所述第二晶体管M12的第二端。晶体管M17的控制端耦接于第n+a级放电控制电路的偏压节点。晶体管M17的第二端耦接于系统低电压VSS。a为1以及-1的其中一者。

在本实施例中,a为1。因此,晶体管M16的控制端以及晶体管M17的控制端会耦接于第n+1级放电控制电路的偏压节点A(n+1)。

请参考图4,图4是依据本发明一实施例所绘示的第n+1级栅极驱动单元的电路示意图。在本实施例中,第n+1级栅极驱动单元GU(n+1)包括电源电路210’、输出电路220’、偏压控制电路230’以及放电控制电路240’。电源电路210’包括晶体管M1’。晶体管M1’的第一端接收系统高电压VDD。晶体管M1’的第二端耦接至偏压节点A(n+1)。晶体管M1’的控制端接收第(n-7)级复本信号ST(n-7)。当接收到高电压位准的第(n-7)级复本信号ST(n-7)时,晶体管M1’会将系统高电压VDD的电压值提供至偏压节点A(n+1),从而将偏压节点A(n+1)的电压值抬升到高偏压值。在另一方面,当接收到低电压位准的第(n-7)级复本信号ST(n-7)时,晶体管M1’则不会将系统高电压VDD的电压值提供至偏压节点A(n+1)。

输出电路220’包括晶体管M2’~M4’。晶体管M2’的第一端接收外部时钟CK2。晶体管M2’的控制端耦接于偏压节点A(n+1)。晶体管M2’的第二端用以输出第n+1级栅极驱动信号G(n+1)。因此,输出晶体管M2’会反应于偏压节点A(n+1)的高偏压值将外部时钟CK2作为第n+1级栅极驱动信号G(n+1),并输出第n+1级栅极驱动信号G(n+1)。晶体管M3’的第一端接收外部时钟CK2。晶体管M3’的控制端耦接于偏压节点A(n+1)。晶体管M3’的第二端用以输出第n+1级复本信号ST(n+1)。晶体管M4’的第一端耦接于偏压节点A(n+1)。晶体管M4’的第二端耦接于系统低电压VSS。晶体管M4’的控制端接收第(n+10)级复本信号ST(n+10)。晶体管M4’会依据第(n+10)级复本信号ST(n+10)将偏压节点A(n+1)的电压值下拉到系统低电压VSS。

在本实施例中,偏压控制电路230’包括第一稳压及放电电路231’。在第一时间区间以及第二时间区间,第一稳压及放电电路231’反应于第n+1级放电控制信号DS(n+1)的低电压位准来维持偏压节点A(n+1)的电压值。在第三时间区间,第一稳压及放电电路231’反应于第n+1级放电控制信号DS(n+1)的高电压位准以及第二参考信号LC2的低电压位准来下拉偏压节点A(n+1)的电压值。

在本实施例中,第一稳压及放电电路231’包括稳压晶体管M5’、M6’。稳压晶体管M5’的第一端耦接于偏压节点A(n+1)。稳压晶体管M5’的第二端接收第n+1级复本信号ST(n+1)。稳压晶体管M5’的控制端接收第n+1级放电控制信号DS(n+1)。稳压晶体管M6’的第一端耦接于稳压晶体管M5’的第二端。稳压晶体管M6’的第二端耦接于第二参考信号LC2。稳压晶体管M6’的控制端接收第n+1级放电控制信号DS(n+1)。

在第一时间区间以及第二时间区间,稳压晶体管M6’反应于第二参考信号LC2的高电压位准以及第n+1级放电控制信号DS(n+1)的低电压位准被进行负偏压补偿操作。除此之外,在第二时间区间,第n+1级复本信号ST(n+1)的高电压位准可用以支撑位于被断开的稳压晶体管M5’的第二端的电压值,以防止偏压节点A(n+1)在高温条件下发生电压泄漏。进一步地,第一稳压及放电电路231’还可以通过第n+1级复本信号ST(n+1)的高电压位准以及被断开的稳压晶体管M5’的第一端与第二端之间的寄生电容耦合效应抬升偏压节点A(n+1)的电压值。

在本实施例中,第一稳压及放电电路231’还包括晶体管M7’。晶体管M7’的第一端耦接于晶体管M2’的第二端。晶体管M7’的第二端耦接于系统低电压VSS。晶体管M7’的控制端接收第n+1级放电控制信号DS(n+1)。因此,晶体管M7’会反应于第n+1级放电控制信号DS(n+1)的高电压位准来下拉第n+1级栅极驱动信号G(n+1)的电压值。

在本实施例中,偏压控制电路230’包括第二稳压及放电电路232’。在第一时间区间以及第二时间区间,第二稳压及放电电路232’反应于第n级放电控制信号DS(n)(a为-1)的低电压位准来维持偏压节点A(n+1)的电压值。在第三时间区间,第二稳压及放电电路232’反应于第n级放电控制信号DS(n)的高电压位准以及第一参考信号LC1的低电压位准来下拉偏压节点A(n+1)的电压值。

在本实施例中,第二稳压及放电电路232’包括稳压晶体管M8’、M9’。稳压晶体管M8’的第一端耦接于偏压节点A(n+1)。稳压晶体管M8’的第二端接收第n级复本信号ST(n)。稳压晶体管M8’的控制端接收第n级放电控制信号DS(n)。稳压晶体管M9’的第一端耦接于稳压晶体管M8’的第二端。稳压晶体管M9’的第二端耦接于第一参考信号LC1。稳压晶体管M9’的控制端接收第n级放电控制信号DS(n)。

在第一时间区间以及第二时间区间,被断开的稳压晶体管M9’反应于第一参考信号LC1的高电压位准以及第n级放电控制信号DS(n)的低电压位准被进行负偏压补偿操作。除此之外,在第二时间区间,第n+1级复本信号ST(n+1)的高电压位准可用以支撑位于被断开的稳压晶体管M8’的第二端的电压值,以防止偏压节点A(n+1)在高温条件下发生电压泄漏。进一步地,第二稳压及放电电路232’还可以通过第n+1级复本信号ST(n+1)的高电压位准以及被断开的稳压晶体管M8’的第一端与第二端之间的寄生电容耦合效应抬升偏压节点A(n+1)的电压值。

在此值得一提的是,第一稳压及放电电路231’以及第二稳压及放电电路232’分别基于不同的放电控制信号以及不同的参考信号来运行。也就是说,第一稳压及放电电路231’以及第二稳压及放电电路232’可交替休息。

在本实施例中,第二稳压及放电电路232’还包括晶体管M10’。晶体管M10’的第一端耦接于晶体管M2’的第二端。晶体管M10’的第二端耦接于系统低电压VSS。晶体管M10’的控制端接收第n级放电控制信号DS(n)。因此,晶体管M10’会反应于第n级放电控制信号DS(n)的高电压位准来下拉第n+1级栅极驱动信号G(n+1)的电压值。

在本实施例中,放电控制电路240’耦接于偏压控制电路230’以及偏压节点A(n+1)。放电控制电路240’包括晶体管M11’~M15’。晶体管M11’的第一端以及晶体管M11’的控制端接收第一参考信号LC1。晶体管M12’的第一端接收第一参考信号LC1。晶体管M12’的控制端耦接于晶体管M11’的第二端。晶体管M13’的第一端耦接于晶体管M11’的第二端,晶体管M13’的控制端耦接于偏压节点A(n+1),晶体管M13’的第二端耦接于系统低电压VSS。晶体管M14’的第一端耦接于晶体管M12’的第二端。晶体管M14’的控制端耦接于偏压节点A(n+1)。晶体管M14’的第二端耦接于系统低电压VSS。晶体管M15’的第一端接收第一参考信号LC1。晶体管M15’的控制端接收第二参考信号LC2。晶体管M15’的第二端耦接于晶体管M12’的第二端。晶体管M14’的第一端与晶体管M12’的第二端的连接节点Q(n+1)被作为放电控制电路240’的输出端。

在本实施例中,在第一时间区间以及第二时间区间,晶体管M13’、M14’会基于偏压节点A(n+1)的高偏压值被导通。节点Q(n+1)的电压值被下拉到系统低电压VSS。因此在第一时间区间以及第二时间区间,不论第一参考信号LC1、第二参考信号LC2的电压位准,放电控制电路240’会提供具有低电压位准的第n+1级放电控制信号DS(n+1)。在第一时间区间以及第二时间区间,当第一参考信号LC1处于低电压位准并且第二参考信号LC2处于高电压位准时,晶体管M15’被导通。因此,节点Q(n+1)的电压值可以被确保为用以进行负偏压补偿的低电压位准(约-12伏特)。

在第三时间区间,晶体管M13’、M14’会基于偏压节点A(n+1)的低偏压值被断开。当第一参考信号LC1处于低电压位准并且第二参考信号LC2处于高电压位准时,节点Q(n+1)的电压值被下拉到低电压位准。因此,放电控制电路240’会提供具有低电压位准的第n+1级放电控制信号DS(n+1)。此外,晶体管M15’也会反应于第一参考信号LC1的高电压位准以及第二参考信号LC2的低电压位准被进行负偏压补偿。也因此,在第三时间区间,第一稳压及放电电路231’的晶体管M6’被进行负偏压补偿。当第一参考信号LC1处于高电压位准并且第二参考信号LC2处于低电压位准时,节点Q(n+1)的电压值为高电压位准。因此,放电控制电路240会在第三时间区间提供具有高电压位准的第n级放电控制信号DS(n)。

举例来说,当第一参考信号LC1处于高电压位准并且第二参考信号LC2处于低电压位准时,放电控制电路240’在第三时间区间中提供具有高电压位准的第n+1级放电控制信号DS(n+1)。因此,在第三时间区间中,第一稳压及放电电路231’的晶体管M5’~M7’会被导通以对偏压节点A(n+1)以及输出电路220’进行抗噪声操作。此时,第二稳压及放电电路232’不运行。稳压晶体管M9’会被进行负偏压补偿操作。

另举例来说,当第一参考信号LC1处于低电压位准并且第二参考信号LC2处于高电压位准时,放电控制电路240’在第三时间区间中提供具有低电压位准的第n+1级放电控制信号DS(n+1)。因此,在第三时间区间中,第一稳压及放电电路231’不运行。稳压晶体管M6’会被进行负偏压补偿操作。第二稳压及放电电路232’则会反应于第n级放电控制信号DS(n)的高电压位准以及第一参考信号LC1的低电压位准来对偏压节点A(n+1)以及输出电路220’进行抗噪声操作。

此外,放电控制电路240’还包括晶体管M16’、M17’。晶体管M16’的第一端耦接于所述晶体管M11’的第二端。晶体管M16’的控制端耦接于第n级放电控制电路GU(n)的偏压节点A(n)。晶体管M16’的第二端耦接于系统低电压VSS。晶体管M17’的第一端耦接于所述第二晶体管M12’的第二端。晶体管M17’的控制端耦接于第n级放电控制电路GU(n)的偏压节点A(n)。晶体管M17’的第二端耦接于系统低电压VSS。

请同时参考图3以及图4,应注意的是,第n级放电控制电路GU(n)以及第n+1级放电控制电路GU(n+1)彼此相互耦接。因此,晶体管M11、M12以及晶体管M11’、M12’可依据画框时间而交替休息。也因此,第一稳压及放电电路231以及第二稳压及放电电路232能够交替休息。第一稳压及放电电路231’以及第二稳压及放电电路232’能够交替休息。因此,第n级放电控制电路GU(n)以及第n+1级放电控制电路GU(n+1)的寿命可以被大幅延长。

请同时参考图3、图4以及图5,图5是依据本发明一实施例所绘示的栅极驱动装置的部分时序图。在本实施例中,第一参考信号LC1的电压位准为高电压位准,第二参考信号LC2的电压位准为低电压位准。图5的时序图表示第n级放电控制电路GU(n)以及第n+1级放电控制电路GU(n+1)在一画框时间内的多个信号以及偏压节点A(n)、A(n+1)的时序。以第n级放电控制电路GU(n)为例,在时间区间T1,当接收到高电压位准的第(n-8)级复本信号ST(n-8)时,晶体管M1会将系统高电压VDD的电压值提供至偏压节点A(n),从而将偏压节点A(n)的电压值抬升到高偏压值。放电控制电路240的晶体管M13、M14反应于偏压节点A(n)的第一偏压值被导通,从而下拉放电控制电路240的输出端的电压位准,使得第(n)级放电控制信号DS(n)的电压值位于低电压位准。

在时间区间T1结束时,第(n-8)级复本信号ST(n-8)的电压值下降到低电位准。晶体管M1被断开。因此,偏压节点A(n)的电压值会维持于高偏压值。

在时间区间T2中,外部时钟CK1为高电压位准。晶体管M2会反应于偏压节点A(n)的电压位准将外部时钟CK1作为第n级栅极驱动信号G(n),并输出具有高电压位准的第n级栅极驱动信号G(n)。晶体管M3会反应于偏压节点A(n)的电压位准将外部时钟CK1作为第n级复本信号ST(n)。由于第n级复本信号ST(n)为高电压位准,因此偏压控制电路230会由电容耦合方式进一步抬升偏压节点A(n)的电压值。放电控制电路240的晶体管M13、M14被导通。因此,放电控制电路240会提供具有低电压位准的第n级放电控制信号DS(n)。

在时间区间T2,第一稳压及放电电路231的稳压晶体管M5、M6反应于第n级放电控制信号DS(n)的低电压位准被断开。第二稳压及放电电路232的稳压晶体管M8、M9反应于第n+1级放电控制信号DS(n+1)的低电压位准被断开。因此,偏压控制电路230依据第n级复本信号ST(n)的高电压值位准以防止偏压节点A(n)发生电压泄漏。

在时间区间T1以及时间区间T2,稳压晶体管M6会被进行负偏压补偿操作。

在时间区间T3中,外部时钟CK1由高电压位准转态到低电压位准。第n级栅极驱动信号G(n)以及第n级复本信号ST(n)为低电压位准。因此,偏压节点A(n)的电压值会下降至原来的高偏压值。

在时间区间T4中,放电晶体管M4会依据第(n+9)级复本信号ST(n+9)将偏压节点A(n)的电压值下拉到低偏压值。晶体管M13、M14被断开。在此画框时间中,第一参考信号LC1的电压位准为高电压位准。第二参考信号LC2的电压位准为低电压位准。放电控制电路240还是提供具有低电压位准的第n级放电控制信号DS(n)。第一稳压及放电电路231的稳压晶体管M5、M6依旧被断开。第一稳压及放电电路231的晶体管M7也被断开。因此,第一稳压及放电电路231不参与抗噪声操作。稳压晶体管M6依旧会被进行负偏压补偿操作。然而,放电控制电路240’会提供具有高电压位准的第n+1级放电控制信号DS(n+1)。因此,第二稳压及放电电路232反应于高电压位准的第n+1级放电控制信号DS(n+1)来进行抗噪声操作。

在一些画框时间中,第一参考信号LC1的电压位准为低电压位准。第二参考信号LC2的电压位准为高电压位准。因此,第一稳压及放电电路231会在时间区间T4中参与抗噪声操作。第二稳压及放电电路232则不会在时间区间T4中参与抗噪声操作。稳压晶体管M9则会被进行负偏压补偿操作。

综上所述,本发明的栅极驱动单元的偏压控制电路在第一时间区间以及第二时间区间防止偏压节点的电压值下降。除此之外,偏压控制电路还能够在任何时间区间对所述多个晶体管的至少一者进行负偏压补偿操作。因此,栅极驱动装置能够在长期使用的情况下具有高信赖性的驱动能力。

最后应说明的是:以上各实施例仅用以说明本发明的技术方案,而非对其限制;尽管参照前述各实施例对本发明进行了详细的说明,本领域的普通技术人员应当理解:其依然可以对前述各实施例所记载的技术方案进行修改,或者对其中部分或者全部技术特征进行等同替换;而这些修改或者替换,并不使相应技术方案的本质脱离本发明各实施例技术方案的范围。

- 栅极驱动器和包括该栅极驱动器的显示装置

- 栅极驱动电路、栅极驱动电路的控制方法和栅极驱动器

- 一种栅极驱动电路及其驱动方法、显示面板、显示装置

- 栅极驱动电路及其驱动方法、GOA单元电路及显示装置

- 移位寄存器单元、其驱动方法、栅极驱动电路及显示装置

- 栅极驱动单元、栅极驱动电路、栅极驱动方法和显示装置

- 栅极驱动单元、栅极驱动方法、栅极驱动电路和显示装置