半导体装置、保护电路及半导体装置的制造方法

文献发布时间:2023-06-19 19:00:17

[相关申请的参照]

本申请享受以日本专利申请2021-149536号(申请日:2021年9月14日)及日本专利申请2021-201871号(申请日:2021年12月13日)为基础申请的优先权。本申请通过参照该基础申请而包含基础申请的全部内容。

技术领域

本发明的实施方式涉及一种半导体装置、保护电路及半导体装置的制造方法。

背景技术

在保护电子设备免受静电放电等浪涌的损伤的保护电路中,有时会设置进行开关动作以免浪涌向电子设备输入的晶体管、及用来保护该晶体管的保护电阻。作为形成这种保护电阻的方法,已知有利用硅化物块的方法。然而,若采用以往的方法,则存在难以控制保护电阻的尺寸的问题。

发明内容

本发明要解决的课题在于,提供一种尺寸控制性较高的保护电路及半导体装置的制造方法。

本发明的一个实施方式的半导体装置包含第1半导体层、第2半导体层、第3半导体层、栅极电极、第1层及绝缘层。第1半导体层具有第1导电型。第2半导体层设置于第1半导体层上,具有第2导电型。第3半导体层设置于第1半导体层上,与第2半导体层在第1方向上并排设置,具有第2导电型。栅极电极在第1半导体层上,设置于第2半导体层与第3半导体层之间。关于第1层,杂质浓度比第2半导体层低,设置于第1半导体层上,一端与第2半导体层相接。绝缘层设置于第1层上,一端与第2半导体层相接。

附图说明

图1是表示实施方式的保护电路的利用形态的一例的图。

图2是表示实施方式的保护电路的构成的一例的俯视图。

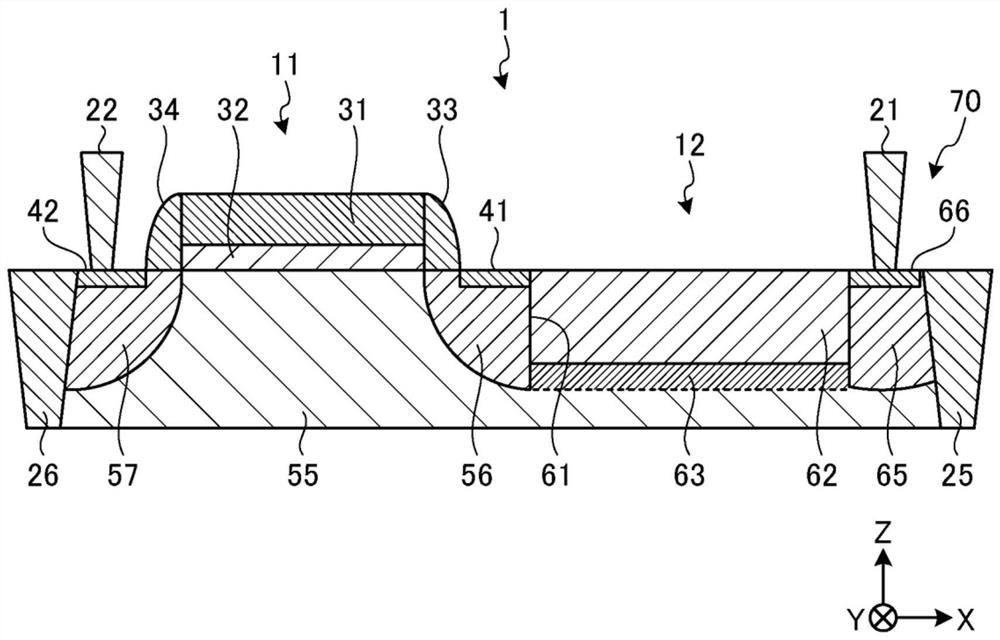

图3是实施方式的保护电路的图2中的A-A剖视图。

图4是实施方式的保护电路的图2中的B-B剖视图。

图5(A)~(E)是表示实施方式的半导体装置的制造方法的一例的图2中的B-B剖视图。

图6(A)~(E)是表示实施方式的半导体装置的制造方法的一例的图2中的C-C剖视图。

具体实施方式

下面,参照附图对本发明的实施方式进行说明。此外,并不由实施方式限定本发明。另外,实施方式的构成要素中包含业者可容易地想到者或实质上相同者。

图1是表示实施方式的保护电路1的利用形态的一例的图。本实施方式的保护电路1是保护指定的电子设备(例如,处理器、存储器等)免受静电放电(ESD:Electro-StaticDischarge)等浪涌的损伤者。在图1所例示的构成中,与作为保护对象的电子设备连接而供外部电流流通的导线10与接地电极之间并联连接有多个(在本例中为4个)保护电路1。

各保护电路1包含晶体管11与保护电阻12。晶体管11是根据浪涌电压或浪涌电流的大小而动作的开关元件,以在浪涌电流或浪涌电压超过阈值的情况下将浪涌电流向接地电极传导的方式动作。保护电阻12是连接于导线10与晶体管11之间的电阻,具有避免晶体管11因浪涌电流而受到损伤的效果。另外,保护电阻12是针对多个保护电路1分别设置的,通过各保护电阻12发挥使浪涌电流衰减的缓冲效果,能抑制浪涌电流集中于1个保护电路1(晶体管11)。

图1中例示出了晶体管11为N通道型MOSFET(Metal-Oxide-Semiconductor FieldEffect Transistor,金属氧化物半导体场效应电晶体)的情况,但晶体管11的构成并不限定于此。在晶体管11为N通道型MOSFET的情况下,晶体管11的漏极与保护电阻12连接,源极与接地电极连接,栅极被输入接地电压。下面,以晶体管11为N通道型MOSFET的情况为例进行说明。

图2是表示实施方式的保护电路1的构成的一例的俯视图。图3是实施方式的保护电路1的图2中的A-A剖视图。图4是实施方式的保护电路1的图2中的B-B剖视图。图中,X方向对应于纸面的左右方向(晶体管11与保护电阻12的排列方向),Y方向对应于与纸面正交的方向(晶体管11或保护电阻12的宽度方向),Z方向对应于与XY平面正交的方向(积层方向)。X方向是第1方向的一例,Y方向是第2方向的一例,Z方向是第3方向的一例。

如图2及图3所示,保护电路1包含晶体管11、保护电阻12、第1触点21、第2触点22、第1绝缘部25及第2绝缘部26。第1触点21与所述导线10连接,第2触点22与接地电极连接。

这里所例示的晶体管11是N通道型MOSFET,如图3所示,包含栅极电极31、氧化绝缘膜32、绝缘部33、34、漏极电极41、源极电极42(第1区域的一例)、P型半导体层55(第1半导体层的一例)、N型扩散层56(第2半导体层或扩散层的一例)、及N型扩散层57(第3半导体层的一例)。

P型半导体层55是根据输入至栅极电极31的电压而成为反相层的区域,以指定的浓度包含B等杂质。与漏极电极41接触的N型扩散层56和下述保护电阻12的电阻层63接触。与源极电极42接触的N型扩散层57经由第2触点22和接地电极连接。

如图2~图4所示,保护电阻12包含沟槽部61、绝缘层62、电阻层63(第1层的一例)、半导体层65(第4半导体层的一例)及硅化物层66。硅化物层66(第2区域的一例)与第1触点21及半导体层65接触。第1触点21、硅化物层66及半导体层65构成了将流经导线10(图1)的外部电流向保护电路1的内部传导的输入部70。此外,半导体层65可为与N型扩散层57相同的半导体层,也可为与N型扩散层57不同的半导体层。另外,半导体层65也可为具有比N型扩散层57高的电传导率的导电层。

沟槽部61在N型扩散层56中以将输入部70与晶体管11分开的方式形成。也就是说,沟槽部61是形成与所谓的STI(Shallow Trench Isolation,浅沟槽隔离)类似的构造者。在本实施方式的沟槽部61的内部形成有绝缘层62及电阻层63。本实施方式的沟槽部61如图4所示,沿着YZ平面的截面形状为倒梯形。也就是说,沟槽部61的开口部的宽度Wt大于沟槽部61的底部71的宽度Wb。

绝缘层62由绝缘性的材料构成,例如可将SiO

电阻层63是具有指定的电阻值(电传导率)的区域。电阻层63的电阻值被设定为能保护晶体管11免受从输入部70输入的浪涌电流的损伤的值。本实施方式的电阻层63的电阻值比N型扩散层56高,比绝缘层62低。

本实施方式的电阻层63及N型扩散层56含有P型半导体层55中包含的杂质(例如B等),电阻层63的杂质浓度低于N型扩散层56的杂质浓度。这种杂质浓度的调整可采用公知的离子注入法等相对较高精度地进行。此外,电阻层63中包含的杂质并不限定于所述者,会根据晶体管11的构成而变化。例如,在晶体管11为P通道型MOSFET的情况下,N型半导体层中包含的As、P等杂质会包含于电阻层及扩散层中。

另外,本实施方式的电阻层63形成于沟槽部61的底部71。通过将电阻层63形成于这样的位置,保护电阻12(保护电路1)的制造性提高,但电阻层63的形成位置并不限定于此。例如,电阻层63也可形成于沟槽部61的侧面部72或绝缘层62的中央部。

通过像上文所述的那样利用与STI类似的构造形成保护电阻12,与需要考虑液体的渗入量等的使用硅化物块的方法等相比,能提高保护电阻12的尺寸控制性。另外,通过这种尺寸控制性的提高,能削减设计上的多余裕度。另外,通过保护电阻12包含杂质浓度比N型扩散层56低的电阻层63的构造,能以比以往小的容量(X方向的长度)的保护电阻12实现与以往同等的电阻值。由此,能使保护电路1整体小型化。

下面,对如上所述的保护电路1的制造方法进行说明。

图5是表示实施方式的保护电路1的制造方法的一例的图2中的B-B剖视图。图6是表示实施方式的保护电路1的制造方法的一例的图2中的C-C剖视图。在图5(A)~(E)中,例示出了随着本实施方式的制造方法的进行,供形成保护电阻12的部分的YZ平面上的变化。在图6(A)~(E)中,例示出了随着本实施方式的制造方法的进行,供形成保护电阻12的部分的XZ平面上的变化。

首先,如图5(A)及图6(A)所示,在P型半导体层55的上表面形成非晶硅层101,在非晶硅层101上的指定部分(与电阻层63对应的部分)形成抗蚀(resist)102,然后进行RIE(Reactive Ion Etching,反应性离子蚀刻)。由此,如图5(B)及图6(B)所示,P型半导体层55上残留具有与图5(A)及图6(B)所示的抗蚀102的厚度相应的厚度的非晶硅层101。非晶硅层101例如为第1掩模(mask)层。

然后,如图5(B)及图6(B)所示,在残留有非晶硅层101的P型半导体层55上形成SiN层105,在SiN层105的外缘部形成抗蚀103,然后进行RIE。SiN层105例如是第2掩模层。这时,图5(B)所示的抗蚀102是与沟槽部61的Y方向上的外侧的区域对应的部分,图6(B)所示的抗蚀102是与沟槽部61的X方向上的外侧的区域(N型扩散层56及半导体层65)对应的部分。由此,如图5(C)及图6(C)所示,形成与图5(B)及图6(B)所示的抗蚀102的厚度相应的深度的沟槽部61。这时,从RIE处理的性质上来讲,距上表面的距离(深度)越大,越难加以蚀刻,因此沟槽部61的形状自然成为倒梯形。另外,只有图5(B)及图6(B)所示的非晶硅层101的厚度的P型半导体层55不被蚀刻,因此在沟槽部61的底部形成P型半导体层55向上方鼓出而成的凸状部110。凸状部110为由第1部与比第1部位于更深位置的第2部以第1部突出的方式形成的构造。

然后,如图5(C)及图6(C)所示,向沟槽部61的内部填充NSG(Non-doped SilicateGlass,无掺杂硅玻璃)等而形成绝缘层62。

然后,如图5(D)及图6(D)所示,在绝缘层62的外缘部形成抗蚀104,并进行离子注入,将由杂质(例如B等)离子化而成的离子化物质(例如BF

通过所述处理,如图5(E)及图6(E)所示,在沟槽部61的底部形成杂质浓度比N型扩散层56低的电阻层63。

以所述方式形成绝缘层62及电阻层63后,采用合适的半导体制造工艺形成半导体层65及硅化物层66,由此形成保护电阻12。然后,采用合适的半导体制造工艺形成晶体管11。晶体管11也可与半导体层65及硅化物层66同时形成。

如上所述,本实施方式的制造方法包含如下步骤:在N型扩散层56形成将输入部70与晶体管11分断的沟槽部61;在沟槽部61的底部形成凸状部110;及通过向凸状部110注入离子而形成电阻层63。由此,能高精度地控制保护电阻12的尺寸,从而能削减设计上的多余裕度。另外,能形成保护电阻12包含杂质浓度比N型扩散层56低的电阻层63的构造,因此能以比以往小的容量(X方向的长度)的保护电阻12实现与以往同等的电阻值。由此,能使保护电路1整体小型化。

已对本发明的若干实施方式进行了说明,但这些实施方式只是作为例子而提出,并未意图限定发明的范围。这些新颖的实施方式可采用其他各种形态加以实施,可在不脱离发明主旨的范围内进行各种省略、替换或变更。这些实施方式及其变形包含于发明的范围及主旨中,并且包含于权利要求书所记载的发明及其同等的范围内。

[符号的说明]

1 保护电路

10 导线

11 晶体管

12 保护电阻

21 第1触点

22 第2触点

25 第1绝缘部

26 第2绝缘部

31 栅极电极

32 氧化绝缘膜

33,34 绝缘部

41 漏极电极

42 源极电极

55 P型半导体层

56,57 N型扩散层

61 沟槽部

62 绝缘层

63 电阻层

65 半导体层

66 硅化物层

70 输入部

71 底部

72 侧面部

101 非晶硅层

102 抗蚀

105 SiN层

110 凸状部。