半导体结构及其形成方法

文献发布时间:2023-06-19 19:27:02

技术领域

本发明实施例涉及半导体制造领域,尤其涉及一种半导体结构及其形成方法。

背景技术

随着半导体工艺技术的逐步发展,半导体工艺节点遵循摩尔定律的发展趋势不断减小。为了适应工艺节点的减小,MOSFET场效应管的沟道长度也相应不断缩短。然而随着器件沟道长度的缩短,器件源极与漏极间的距离也随之缩短,因此栅极对沟道的控制能力变差,栅极电压夹断(pinch off)沟道的难度也越来越大,使得亚阈值漏电(subthresholdleakage)现象,即所谓的短沟道效应(SCE:short-channel effects)更容易发生。

因此,为了更好的适应器件尺寸按比例缩小的要求,半导体工艺逐渐开始从平面MOSFET向具有更高功效的三维立体式的晶体管过渡,如鳍式场效应晶体管(Fin Field-Effect Transistor,FinFET)。FinFET中,栅极至少可以从两侧对超薄体(鳍部)进行控制,与平面MOSFET相比,栅极对沟道的控制能力更强,能够很好的抑制短沟道效应;且FinFET相对于其他器件,与现有集成电路制造具有更好的兼容性。

发明内容

本发明实施例解决的问题是提供一种半导体结构及其形成方法,提高半导体结构的性能。

为解决上述问题,本发明实施例提供一种半导体结构,包括:衬底,包括第一器件区和第二器件区,所述第一器件区的器件工作电压小于所述第二器件区的器件工作电压;鳍部,分别位于所述第一器件区和第二器件区的衬底上,沿所述鳍部的延伸方向,所述鳍部包括沟道区、以及位于所述沟道区两侧的非沟道区,部分高度的所述鳍部作为底部鳍部,剩余高度的所述鳍部作为有效鳍部,所述有效鳍部位于所述底部鳍部的顶部,其中,所述第二器件区中沟道区的有效鳍部侧壁相对于同侧的非沟道区的鳍部侧壁向内缩进,所述第二器件区中沟道区的有效鳍部宽度小于非沟道区的鳍部宽度,且所述第一器件区中沟道区的有效鳍部宽度大于所述第二器件区中沟道区的有效鳍部宽度;隔离层,位于所述鳍部侧部的所述衬底上,所述隔离层覆盖所述底部鳍部的侧壁,且露出所述有效鳍部;栅极结构,位于所述隔离层上且横跨所述有效鳍部,所述栅极结构包括覆盖所述沟道区的有效鳍部顶部和侧壁的栅介质层、以及覆盖所述栅介质层的栅电极层,所述第二器件区的栅介质层厚度大于所述第一器件区的栅介质层厚度;侧墙,位于所述栅极结构的两侧并覆盖所述栅极结构的侧壁;源漏掺杂层,位于所述栅极结构两侧的有效鳍部中,且位于所述侧墙远离所述栅极结构的一侧。

相应的,本发明实施例还提供一种半导体结构的形成方法,包括:提供基底,包括衬底、以及位于所述衬底上的鳍部,所述衬底包括第一器件区和第二器件区,所述第一器件区的器件工作电压小于所述第二器件区的器件工作电压,沿所述鳍部的延伸方向,所述鳍部包括沟道区;在所述第二器件区中,对所述沟道区的鳍部进行减薄处理,用于减小所述沟道区的鳍部的宽度;对所述沟道区的鳍部进行减薄处理后,在所述基底上形成伪栅结构,所述伪栅结构横跨所述沟道区的鳍部,并覆盖所述沟道区的鳍部的部分顶部和部分侧壁,所述伪栅结构包括栅氧化层、以及覆盖所述栅氧化层的伪栅层;在所述伪栅层两侧的鳍部中形成源漏掺杂层;在所述衬底上形成覆盖所述源漏掺杂层的层间介质层,所述层间介质层覆盖所述伪栅层的侧壁并露出所述伪栅层的顶部;去除所述第一器件区的伪栅结构、以及所述第二器件区的伪栅层,在所述层间介质层中形成栅极开口;在所述栅极开口中形成栅极结构。

与现有技术相比,本发明实施例的技术方案具有以下优点:

本发明实施例提供的半导体结构中,所述第一器件区的器件工作电压小于所述第二器件区的器件工作电压,通过使所述第二器件区中,所述沟道区的有效鳍部侧壁相对于同侧的所述非沟道区的鳍部侧壁向内缩进,以减小所述第二器件区中沟道区的有效鳍部宽度,相应增大相邻沟道区的鳍部之间的空间,从而在所述第二器件区的栅介质层厚度相应大于所述第一器件区的栅介质层厚度的情况下,增大了在第二器件区中形成栅电极层的工艺窗口,提高了栅电极层在鳍部之间的覆盖能力或填充能力,进而有利于提高栅极结构的形成质量,而且,在所述第二器件区中,所述沟道区的有效鳍部侧壁相对于同侧的所述沟道区的底部鳍部侧壁向内缩进,也就是说,仅减小了所述沟道区的有效鳍部的宽度,源漏掺杂层位于栅极结构两侧的有效鳍部中,由于未减小所述非沟道区的鳍部宽度,这相应减小了对源漏掺杂层的影响,从而有利于确保源漏掺杂层的形成质量和体积,进而确保所述源漏掺杂层的性能;综上,本发明实施例提高了半导体结构的性能。

本发明实施例提供的半导体结构的形成方法中,第一器件区的器件工作电压小于第二器件区的器件工作电压,在层间介质层中形成栅极开口时,去除所述第一器件区的伪栅结构、以及所述第二器件区的伪栅层,也即所述第二器件区的栅极开口中保留栅氧化层,栅氧化层作为器件的栅介质层的一部分,这使得所述第二器件区的栅介质层厚度大于所述第一器件区的栅介质层厚度,因此,在基底上形成伪栅结构之前,在所述第二器件区中,对所述沟道区的鳍部进行减薄处理,用于减小所述沟道区的鳍部的宽度,以增大相邻沟道区的鳍部之间的空间,从而增大了在第二器件区的栅极开口中形成栅极结构的工艺窗口,提高了栅极结构在鳍部之间的覆盖能力或填充能力,进而有利于提高栅极结构的形成质量,而且,仅对所述沟道区的鳍部进行减薄处理,不对所述非沟道区的鳍部进行减薄处理,使所述非沟道区的鳍部维持初始宽度,源漏掺杂层形成于伪栅层两侧的鳍部中,也即源漏掺杂层形成于所述非沟道区的鳍部中,由于未减小所述非沟道区的鳍部宽度,这相应减小了对源漏掺杂层的影响,从而有利于确保源漏掺杂层的形成质量和体积,进而确保所述源漏掺杂层的性能;综上,本发明实施例提高了半导体结构的性能。

附图说明

图1是一种半导体结构的结构示意图;

图2至图5是本发明半导体结构一实施例的结构示意图;

图6至图37是本发明半导体结构的形成方法一实施例中各步骤对应的结构示意图。

具体实施方式

目前半导体结构的性能仍有待提高。现结合一种半导体结构的形成方法分析其性能有待提高的原因。

图1是一种半导体结构的结构示意图。

所述半导体结构包括:衬底10;鳍部20,凸立于所述衬底10上;隔离层30,位于所述鳍部20侧部的所述衬底10上,所述隔离层30覆盖所述鳍部20的部分侧壁;栅极结构40,位于所述隔离层30上,所述栅极结构40横跨所述鳍部20并覆盖所述鳍部20的部分的顶部和部分侧壁,所述栅极结构40包括栅介质层41、以及覆盖所述栅介质层41的栅电极层42。

在实际工艺中,所述衬底10通常包括多个器件区,分别用于形成不同工作电压的器件,例如,所述衬底10包括用于形成核心器件的核心区、以及用于形成高压器件的高压区,高压器件的工作电压大于核心器件的工作电压。

为了防止电击穿等问题,器件的工作电压越高,所对应的栅介质层41厚度则越大。相应的,在所述半导体结构的形成过程中,在栅介质层41厚度更大的器件区中,在形成栅介质层41后,相邻鳍部20之间的剩余空间越小,从而导致形成栅电极层42的工艺窗口较小,降低了栅电极层42在鳍部20之间的覆盖能力或填充能力,进而导致栅极结构40的形成质量变差,相应降低了半导体结构的性能。

为了解决所述技术问题,本发明实施例提供一种半导体结构,包括:衬底,包括第一器件区和第二器件区,所述第一器件区的器件工作电压小于所述第二器件区的器件工作电压;鳍部,分别位于所述第一器件区和第二器件区的衬底上,沿所述鳍部的延伸方向,所述鳍部包括沟道区、以及位于所述沟道区两侧的非沟道区,部分高度的所述鳍部作为底部鳍部,剩余高度的所述鳍部作为有效鳍部,所述有效鳍部位于所述底部鳍部的顶部,其中,所述第二器件区中沟道区的有效鳍部侧壁相对于同侧的非沟道区的鳍部侧壁向内缩进,所述第二器件区中沟道区的有效鳍部宽度小于非沟道区的鳍部宽度,且所述第一器件区中沟道区的有效鳍部宽度大于所述第二器件区中沟道区的有效鳍部宽度;隔离层,位于所述鳍部侧部的所述衬底上,所述隔离层覆盖所述底部鳍部的侧壁,且露出所述有效鳍部;栅极结构,位于所述隔离层上且横跨所述有效鳍部,所述栅极结构包括覆盖所述沟道区的有效鳍部顶部和侧壁的栅介质层、以及覆盖所述栅介质层的栅电极层,所述第二器件区的栅介质层厚度大于所述第一器件区的栅介质层厚度;侧墙,位于所述栅极结构的两侧并覆盖所述栅极结构的侧壁;源漏掺杂层,位于所述栅极结构两侧的有效鳍部中,且位于所述侧墙远离所述栅极结构的一侧。

通过使所述第二器件区中,所述沟道区的有效鳍部侧壁相对于同侧的所述非沟道区的鳍部侧壁向内缩进,以减小所述第二器件区中沟道区的有效鳍部宽度,相应增大相邻沟道区的鳍部之间的空间,从而在所述第二器件区的栅介质层厚度相应大于所述第一器件区的栅介质层厚度的情况下,增大了在第二器件区中形成栅电极层的工艺窗口,提高了栅电极层在鳍部之间的覆盖能力或填充能力,进而有利于提高栅极结构的形成质量,而且,在所述第二器件区中,所述沟道区的有效鳍部侧壁相对于同侧的所述沟道区的底部鳍部侧壁向内缩进,也就是说,仅减小了所述沟道区的有效鳍部的宽度,源漏掺杂层位于栅极结构两侧的有效鳍部中,由于未减小所述非沟道区的鳍部宽度,这相应减小了对源漏掺杂层的影响,从而有利于确保源漏掺杂层的形成质量和体积,进而确保所述源漏掺杂层的性能;综上,本发明实施例提高了半导体结构的性能。

为使本发明实施例的上述目的、特征和优点能够更为明显易懂,下面结合附图对本发明的具体实施例做详细的说明。

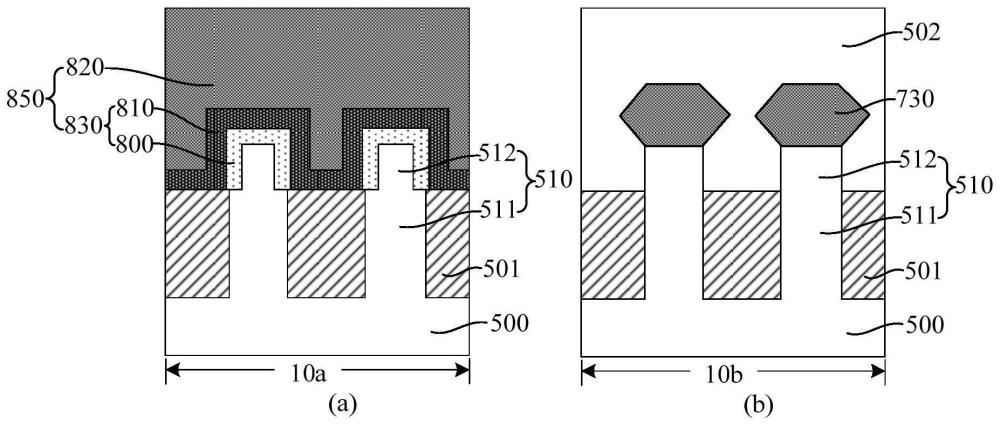

图2至图5是本发明半导体结构一实施例的结构示意图,图2为第一器件区的俯视图,图3(a)为图2沿AA1方向的剖视图,图3(b)为图2沿DD1方向的剖视图,图4为第二器件区的俯视图,图5(a)为图4沿BB1方向的剖视图,图5(b)为图4沿CC1方向的剖视图。

所述半导体结构包括:衬底500,包括第一器件区500A和第二器件区500B,所述第一器件区500A的器件工作电压小于所述第二器件区500B的器件工作电压;鳍部510,分别位于所述第一器件区500A和第二器件区500B的衬底500上,沿所述鳍部510的延伸方向,所述鳍部510包括沟道区10a、以及位于所述沟道区10a两侧的非沟道区10b,部分高度的所述鳍部510作为底部鳍部511,剩余高度的所述鳍部510作为有效鳍部512,所述有效鳍部512位于所述底部鳍部511的顶部,其中,所述第二器件区500B中沟道区10a的有效鳍部512侧壁相对于同侧的非沟道区10b的鳍部510侧壁向内缩进,所述第二器件区500B中沟道区10a的有效鳍部512宽度小于非沟道区10b的鳍部510宽度,且所述第一器件区500A中沟道区10a的有效鳍部512宽度大于所述第二器件区500B中沟道区10a的有效鳍部512宽度;隔离层501,位于所述鳍部510侧部的所述衬底500上,所述隔离层501覆盖所述底部鳍部511的侧壁,且露出所述有效鳍部512;栅极结构850,位于所述隔离层501上且横跨所述有效鳍部512,所述栅极结构850包括覆盖所述沟道区10a的有效鳍部512顶部和侧壁的栅介质层830、以及覆盖所述栅介质层830的栅电极层820,所述第二器件区500B的栅介质层830厚度大于所述第一器件区500A的栅介质层830厚度;侧墙(图未示),位于所述栅极结构850的两侧并覆盖所述栅极结构850的侧壁;源漏掺杂层730,位于所述栅极结构850两侧的有效鳍部512中,且位于所述侧墙远离所述栅极结构850的一侧。

所述衬底500用于为半导体结构的形成提供工艺平台。

所述衬底500的材料包括硅、锗、锗化硅、碳化硅、砷化镓、镓化铟、绝缘体上的硅或绝缘体上的锗。本实施例中,所述衬底500的材料为硅。

本实施例中,所述衬底500包括第一器件区500A和第二器件区500B,所述第一器件区500A的器件工作电压小于第二器件区500B的器件工作电压。

具体地,所述第一器件区500A用于形成核心器件,所述第二器件区500B用于形成高压(High Voltage)器件或者用于形成输入/输出(I/O)器件。

需要说明的是,核心器件主要指芯片内部所使用的器件,通常采用较低的工作电压(一般为1.0V、1.2V、1.5V和1.8V),输入/输出器件是芯片与外部接口交互时所使用的器件,这类器件的工作电压一般比较高,且取决于外部接口的兼容工作电压(一般为1.8V、2.5V、3.3V和5V)。

在其他实施例中,第一器件区和第二器件区还可以用于形成其他类型的器件。例如,第一器件区用于形成低压器件(LV device),第二器件区用于形成高压器件(HVdevice),低压器件的工作电压小于高压器件的工作电压。

本实施例中,所述半导体结构为鳍式场效应晶体管(FinFET),因此,所述衬底400上形成有鳍部510,所述鳍部510用于提供晶体管的沟道。

所述栅极结构850在衬底500上的投影与所述鳍部510在衬底500上的投影正交,因此,所述鳍部510沿延伸方向包括沟道区10a、以及位于所述沟道区10a两侧的非沟道区10b。

所述沟道区10a的位置处用于形成栅极结构850,从而通过栅极结构850控制器件导电沟道的开启或关断,所述非沟道区10b用于形成所述源漏掺杂层730。

具体地,所述鳍部510的材料包括硅、锗化硅、锗或Ⅲ-Ⅴ族半导体材料。所述鳍部510的材料根据晶体管的沟道导电类型和性能需求而定。本实施例中,所述鳍部510的材料为硅。作为一种示例,所述鳍部510和衬底500为一体结构。相应的,所述鳍部510和衬底500的材料相同,所述鳍部510的材料为硅。

所述隔离层501用于实现不同器件区之间的隔离作用。具体地,所述隔离层501为浅沟槽隔离(STI)结构。

所述隔离层501的材料为绝缘材料。例如,所述隔离层501的材料包括氧化硅、氮化硅、氮氧化硅和碳氮氧化硅中的一种或多种。作为一种示例,所述隔离层501的材料为氧化硅。

本实施例中,所述栅极结构501位于所述隔离层501上,所述栅极结构501仅覆盖露出于所述隔离层501的鳍部510的部分顶部和部分侧壁,因此,露出于所述隔离层501的鳍部510作为有效鳍部512,所述有效鳍部512用于提供晶体管工作的导电沟道。相应的,被所述隔离层501覆盖的所述鳍部510作为底部鳍部511。

结合参考图5(a),本实施例中,在第二器件区500B中,所述沟道区10a的有效鳍部512侧壁相对于同侧的所述非沟道区10b的鳍部510侧壁向内缩进,也就是说,在所述第二器件区500B中,沿垂直于所述鳍部510侧壁的方向(也即与鳍部510延伸方向相垂直的方向),所述沟道区10a的有效鳍部512宽度小于所述非沟道区10b的鳍部510宽度。

其中,所述第一器件区500A的器件工作电压小于所述第二器件区500B的器件工作电压,当器件的工作电压越大时,要求器件的栅介质层的厚度越大,也就是说,所述第二器件区500B的栅介质层830厚度大于所述第一器件区500A的栅介质层830厚度。

因此,通过使所述第二器件区500B中,所述沟道区10a的有效鳍部512侧壁相对于同侧的所述非沟道区10b的鳍部510侧壁向内缩进,以减小所述第二器件区500B中沟道区10a的有效鳍部512宽度,相应增大相邻沟道区10a的鳍部510之间的空间,从而在所述第二器件区500B的栅介质层830厚度相应大于所述第一器件区500A的栅介质层830厚度的情况下,增大了在第二器件区500B中形成栅电极层820的工艺窗口,提高了栅电极层820在鳍部510之间的覆盖能力或填充能力,进而有利于提高第二器件区500B的栅极结构850的形成质量,相应提高半导体结构的性能。

需要说明的是,在所述第二器件区500B中,所述沟道区10a的有效鳍部512侧壁相对于同侧的所述非沟道区10b的鳍部510侧壁向内缩进的尺寸不宜过小,也不宜过大。如果所述沟道区10a的有效鳍部512侧壁相对于同侧的所述非沟道区10b的鳍部510侧壁向内缩进的尺寸过小,则容易导致增大相邻沟道区10a的鳍部510之间的空间的效果不佳,从而导致增大在第二器件区500B中形成栅电极层820的工艺窗口的效果不佳;如果所述沟道区10a的有效鳍部512侧壁相对于同侧的所述非沟道区10b的鳍部510侧壁向内缩进的尺寸过大,则容易导致所述沟道区10a的有效鳍部512的宽度过小,这不仅容易导致器件的电学性能发生偏移,还容易降低所述沟道区10a的有效鳍部512的机械强度,相应增大所述沟道区10a的有效鳍部512发生变形的概率。为此,本实施例中,在所述第二器件区500B中,所述沟道区10a的有效鳍部512侧壁相对于同侧的所述非沟道区10b的鳍部510侧壁向内缩进1纳米至3纳米。例如,所述沟道区10a的有效鳍部512侧壁相对于同侧的所述非沟道区10b的鳍部510侧壁向内缩进1.5纳米、2纳米或2.5纳米。

其中,所述沟道区10a的有效鳍部512的宽度指的是:沿平行于衬底500表面且与所述鳍部510延伸方向相垂直的方向,所述有效鳍部512的横向尺寸。

本实施例中,在所述第二器件区500B中,所述沟道区10a的有效鳍部512侧壁相对于同侧的所述沟道区10a的底部鳍部511侧壁向内缩进,也就是说,所述沟道区10a的底部鳍部511侧部与同侧的所述非沟道区10b的底部鳍部511侧壁相齐平,因此,仅减小了所述沟道区10a的有效鳍部512的宽度,而所述底部鳍部511的宽度较大,这有利于确保鳍部510整体的机械强度。

而且,所述源漏掺杂层730位于所述栅极结构850两侧的有效鳍部512中,由于未减小所述非沟道区10b的鳍部宽度,这相应减小了对源漏掺杂层730的影响,从而有利于确保源漏掺杂层730的形成质量和体积,进而确保源漏掺杂层730的性能。

此外,在形成所述半导体结构的过程中,可以在形成隔离层501之后,对沟道区10a的有效鳍部512进行减薄处理,以减小所述沟道区10a的有效鳍部512的宽度,与在形成隔离层之前,对沟道区的有效鳍部和底部鳍部进行减薄处理的方案相比,本实施例中,所述有效鳍部512和隔离层501所围成空间的深宽比更小,有利于降低减薄处理的工艺难度,并提高减薄处理的工艺效果,从而有利于精确控制所述沟道区10a的有效鳍部512的宽度。

所述栅极结构850用于控制晶体管的导电沟道的开启或关断。本实施例中,所述栅极结构850横跨有效鳍部512,并覆盖沟道区10a的有效鳍部512的顶部和侧壁,从而实现对导电沟道的控制。

具体地,所述栅极结构850包括栅介质层830、以及覆盖所述栅介质层830的栅电极层820。

所述栅介质层830用于隔离所述栅电极层820和沟道。所述栅介质层830的材料包括HfO

本实施例中,所述栅极结构850为金属栅极结构。因此,栅介质层830包括高k栅介质层810。高k栅介质层810的材料为高k介质材料,其中,高k介质材料是指相对介电常数大于氧化硅相对介电常数的介电材料。具体地,所述高k栅介质层810的材料可以选自HfO

本实施例中,所述第二器件区500B的栅介质层830还包括位于高k栅介质层810和有效鳍部512之间的栅氧化层800。作为一种示例,所述栅氧化层800的材料为氧化硅。在其他实施例中,栅氧化层的材料还可以为氮氧化硅。

本实施例中,在所述第二器件区500B中,所述栅氧化层800覆盖有效鳍部512露出的底部鳍部511的顶部,从而减小底部鳍部对器件性能的影响。

本实施例以第一器件区500A的栅介质层830仅包括高k栅介质层810为例,而所述第二器件区500B的栅介质层830包括栅氧化层800、以及覆盖栅氧化层800的高k栅介质层810,因此,所述第二器件区500B的栅介质层830厚度大于所述第一器件区500A的栅介质层830厚度,以满足所述第一器件区500A和第二器件区500B的器件工作电压的不同需求。

在其他实施例中,在所述第一器件区中,所述栅介质层还包括位于所述高k栅介质层和有效鳍部之间的栅氧化层。其中,由于所述第一器件区的器件工作电压小于所述第二器件区的器件工作电压,因此,所述第一器件区的栅氧化层厚度小于所述第二器件区的栅氧化层厚度。

所述栅电极层820用于将所述栅极结构850的电性引出。所述栅电极层820的材料包括TiN、TaN、Ta、Ti、TiAl、W、Al、TiSiN和TiAlC中的一种或多种。

作为一种示例,所述栅电极层820包括功函数层以及覆盖功函数层的电极层。在其他实施例中,所述栅电极层也可以仅包括功函数层。其中,功函数层用于调节所形成晶体管的工作电压。可以理解的是,根据不同器件区的晶体管的性能需求,各器件区中功函数层的材料、厚度和膜层层数可以不相同。

本实施例中,沿鳍部510的延伸方向,所述第一器件区500A中的相邻所述栅极结构850具有第一节距(pitch),所述第二器件区500B中的相邻所述栅极结构850具有第二节距。此处的节距指的是:沿所述鳍部510的延伸方向,一个栅极结构850的宽度(width)与相邻栅极结构850的间距(space)之和。

由于所述第一器件区500A的器件工作电压小于所述第二器件区500B的器件工作电压,因此,沿所述鳍部510的延伸方向,所述第二器件区500B的栅极结构850宽度大于所述第一器件区500A的栅极结构850宽度,相应的,所述第二节距大于所述第一节距。

具体地,所述第二节距至少为所述第一节距的两倍,使得在所述第二器件区500B中,所述沟道区10a的有效鳍部512沿所述鳍部510延伸方向的长度较大,从而在对沟道区10a的有效鳍部512进行减薄处理的过程中,使得减薄处理的工艺窗口较大、减薄处理的工艺难度较低。例如,在减薄处理的过程中,通常需要采用具有掩膜开口的遮挡层,以定义所述减薄处理的区域,所述第二节距较大,这相应使得掩膜开口的尺寸、以及相邻掩膜开口沿鳍部510延伸方向的距离较大,从而提高了形成掩膜开口所采用的光刻工艺的工艺窗口,且易于通过掩膜开口对暴露的有效鳍部512进行减薄处理。

所述源漏掺杂层730用于作为所形成晶体管的源区或漏区。

具体地,所述源漏掺杂层730的掺杂类型与相对应的晶体管的沟道导电类型相同。当晶体管为PMOS晶体管时,源漏掺杂层730的材料包括掺杂有P型离子的锗化硅,P型离子包括B、Ga或In。当晶体管为NMOS晶体管时,源漏掺杂层730的材料包括掺杂有N型离子的硅或碳化硅,N型离子包括P、As或Sb。

所述侧墙用于保护所述栅极结构850的侧壁,还用于定义所述源漏掺杂层730的形成位置。对侧墙的描述,在此不再赘述。

本实施例中,所述半导体结构还包括:层间介质层502,位于所述栅极结构850侧部的基底上,并覆盖所述栅极结构850的侧壁。具体地,所述层间介质层502覆盖所述侧墙的侧壁。

所述层间介质层502用于实现相邻器件之间的电隔离。所述层间介质层502的材料为绝缘材料。本实施例中,所述层间介质层502的材料为氧化硅。在其他实施例中,层间介质层的材料还可以为氮化硅或氮氧化硅等其他介质材料。

图6至图37是本发明半导体结构的形成方法一实施例中各步骤对应的结构示意图。

参考图6和图7,图6(a)为第一器件区的俯视图,图6(b)为图6(a)沿AA1方向的剖视图,图7(a)为第二器件区的俯视图,图7(b)为图7(a)沿BB1方向的剖视图,提供基底(未标示),包括衬底100、以及位于所述衬底100上的鳍部110,所述衬底100包括第一器件区100A和第二器件区100B,所述第一器件区100A的器件工作电压小于所述第二器件区100B的器件工作电压,沿所述鳍部110的延伸方向,所述鳍部110包括沟道区10a。

所述衬底100用于为半导体结构的形成提供工艺平台。

所述衬底100的材料包括硅、锗、锗化硅、碳化硅、砷化镓、镓化铟、绝缘体上的硅或绝缘体上的锗。本实施例中,所述衬底100的材料为硅。

本实施例中,所述第一器件区100A的器件工作电压小于所述第二器件区100B的器件工作电压。

具体地,所述第一器件区100A用于形成核心器件,所述第二器件区100B用于形成高压(High Voltage)器件或者用于形成输入/输出器件。

在其他实施例中,第一器件区和第二器件区还可以用于形成其他类型的器件。例如,第一器件区用于形成低压器件,所述第二器件区用于形成高压器件,低压器件的工作电压小于高压器件的工作电压。

所述鳍部510用于提供鳍式场效应晶体管的沟道。后续形成的栅极结构在衬底100上的投影与所述鳍部110在衬底100上的投影正交,因此,所述鳍部110沿延伸方向包括沟道区10a、以及位于所述沟道区10a两侧的非沟道区10b。

所述沟道区10a的位置处用于形成栅极结构,从而通过栅极结构控制沟道的开启或关断,所述非沟道区10b用于形成源漏掺杂层。

本实施例中,沿所述鳍部110的延伸方向,所述第一器件区100A中的相邻所述沟道区10a具有第一节距,所述第二器件区100B中的相邻所述沟道区10a具有第二节距。此处的节距指的是:沿所述鳍部110的延伸方向,一个沟道区10a的宽度(width)与相邻沟道区10a的间距(space)之和。

由于所述第一器件区100A的器件工作电压小于所述第二器件区100B的器件工作电压,因此,沿所述鳍部110的延伸方向,所述第二器件区100B的栅极结构的宽度更大,相应的,所述第二器件区100B的沟道区10a宽度大于所述第一器件区100A的沟道区10a宽度,所述第二节距大于所述第一节距。

具体地,所述第二节距至少为所述第一节距的两倍,使得后续在所述第二器件区100B中,对沟道区10a的鳍部110侧壁进行减薄处理的过程中,增大所述减薄处理的工艺窗口、降低所述减薄处理的工艺难度。

例如,在减薄处理的过程中,通常需要采用具有掩膜开口的遮挡层,以定义所述减薄处理的区域,所述第二节距较大,这相应使得掩膜开口的尺寸、以及相邻掩膜开口沿鳍部110延伸方向的距离较大,从而增大了形成掩膜开口所采用的光刻工艺的工艺窗口,且易于通过掩膜开口对暴露的鳍部进行减薄处理。

所述鳍部110的材料包括硅、锗化硅、锗或Ⅲ-Ⅴ族半导体材料。所述鳍部110的材料根据晶体管的沟道导电类型和性能需求而定。本实施例中,所述鳍部110的材料为硅。

作为一种示例,所述鳍部110和衬底100为一体结构。相应的,所述鳍部110和衬底100的材料相同,所述鳍部110的材料为硅。

本实施例中,所述基底还包括位于所述鳍部110侧部的所述衬底100上的隔离层101,所述隔离层101的顶部低于所述鳍部110的顶部,所述隔离层101覆盖所述鳍部110的部分侧壁。

所述隔离层101用于实现不同器件区之间的隔离作用。具体地,所述隔离层101为浅沟槽隔离结构。

所述隔离层101的材料为绝缘材料。例如,所述隔离层101的材料包括氧化硅、氮化硅、氮氧化硅和碳氮氧化硅中的一种或多种。作为一种示例,所述隔离层101的材料为氧化硅。

需要说明的是,在形成鳍部110的步骤中,采用鳍部掩膜层作为刻蚀掩膜,因此,在形成所述隔离层101之前,所述鳍部110的顶部形成有鳍部掩膜层(图未示)。

作为一种示例,在形成所述隔离层101的过程中,去除所述鳍部掩膜层。

具体地,形成所述隔离层101的步骤包括:在所述鳍部110侧部的衬底100上形成隔离材料层(图未示),所述隔离材料层覆盖所述鳍部掩膜层;以所述鳍部掩膜层顶部作为停止位置,对所述隔离材料层进行平坦化处理(例如,化学机械研磨处理);在所述平坦化处理后,去除所述鳍部掩膜层;去除所述鳍部掩膜层后,回刻蚀部分厚度的剩余隔离材料层,形成隔离层。

在其他实施例中,根据形成隔离层的工艺流程,所述提供基底的步骤中,所述鳍部的顶部形成有鳍部掩膜层,也就是说,在形成所述隔离层后,保留所述鳍部掩膜层。相应的,在形成所述隔离层的过程中,对所述隔离材料层进行平坦化处理后,保留所述鳍部掩膜层。

参考图8至图12,图8(a)为第一器件区的俯视图,图8(b)为图8(a)沿AA1方向的剖视图,图9为第二器件区的俯视图,图10(a)为图9沿BB1方向的剖视图,图10(b)为图9沿CC1方向的剖视图,图11为第二器件区的俯视图,图12(a)为图11沿BB1方向的剖视图,图12(b)为图11沿CC1方向的剖视图,在所述第二器件区100B中,对所述沟道区10a的鳍部110进行减薄处理,用于减小所述沟道区10a的鳍部110的宽度。

此处鳍部110的宽度指的是:沿平行于衬底100表面且与鳍部110延伸方向相垂直的方向上,鳍部110的横向尺寸。

此外,如图11所示,图11采用虚线表示减薄处理之前,所述沟道区10a的鳍部110的侧壁轮廓。

所述第一器件区100A的器件工作电压小于所述第二器件区100B的器件工作电压,后续形成栅极结构时,所述第二器件区100B的栅介质层厚度相应大于所述第一器件区100A的栅介质层厚度,因此,通过在所述第二器件区100B中,减小所述沟道区10a的鳍部110的宽度,以增大相邻沟道区10a的鳍部110之间的空间,从而在所述第二器件区100B的栅介质层厚度大于所述第一器件区100A的栅介质层厚度的情况下,增大后续在第二器件区100B的栅极开口中形成栅极结构的工艺窗口,提高了栅极结构在鳍部110之间的覆盖能力或填充能力,进而有利于提高栅极结构的形成质量,相应提高半导体结构的性能。

本实施例中,所述衬底100上形成有隔离层101,因此,在所述第二器件区100B中,对所述隔离层101露出的所述10a的鳍部110进行减薄处理。

与在形成隔离层之前进行减薄处理的方案相比,本实施例中,露出于所述隔离层101的鳍部110与所述隔离层101所围成空间的深宽比更小,有利于降低减薄处理的工艺难度,并提高减薄处理的工艺效果,从而有利于精确控制减薄处理后,所述沟道区10a的鳍部110的宽度。

需要说明的是,在减薄处理过程中,仅减小所述隔离层101露出的沟道区10a的鳍部110宽度,被所述隔离层101覆盖的鳍部110因受到所述隔离层101的保护而维持初始宽度,这有利于确保鳍部110整体的机械强度。

还需要说明的是,仅对所述沟道区10a的鳍部110进行减薄处理,不对所述非沟道区10b的鳍部110进行减薄处理,使所述非沟道区10b的鳍部110维持初始宽度。后续在伪栅结构两侧的鳍部110中形成源漏掺杂层,所述源漏掺杂层相应形成于所述非沟道区10b的鳍部110中,由于未减小所述非沟道区10b的鳍部110宽度,这相应减小了对源漏掺杂层的影响,从而有利于确保源漏掺杂层的形成质量和体积,进而确保源漏掺杂层的性能。

此外,此时衬底100上仅形成有隔离层101和鳍部110,所述衬底100上的部件较少,与在去除伪栅结构以形成栅极开口后,再通过栅极开口对沟道区的鳍部进行减薄处理的方案相比,在形成伪栅结构之前,先进行减薄处理,有利于降低减薄处理的工艺复杂度(例如,用于定义减薄处理区域的遮挡层的形成难度更低)。

而且,在形成伪栅结构之前,对所述沟道区10a的鳍部110进行减薄处理,对现有制程的改动小,工艺兼容性高。

具体地,在所述第二器件区100B中,对所述沟道区10a的鳍部110进行减薄处理的步骤包括:如图8至图10所示,在所述衬底100上形成覆盖所述鳍部110的遮挡层200,所述遮挡层200中形成有位于所述第二器件区100B的掩膜开口210,所述掩膜开口210露出所述沟道区10a的鳍部110;如图11至图12所示,以所述遮挡层200为掩膜,对所述掩膜开口210露出的鳍部110进行减薄处理。

所述遮挡层200可以选取任意能够适用于作为掩膜的材料,且所述遮挡层200的材料选取为:所述鳍部110和遮挡层200之间具有刻蚀选择比,且去除所述遮挡层200的工艺对所述鳍部110和衬底100的损伤小。

此时衬底100上仅形成有隔离层101和鳍部110,这相应提高了选取所述遮挡层200的材料的灵活性。作为一种示例,所述遮挡层200的材料为光刻胶。

在其他实施例中,所述遮挡层也可以包括抗反射涂层、以及位于抗反射涂层顶部的光刻胶层,或者,所述遮挡层包括填充层、位于所述填充层顶部的抗反射涂层、以及位于抗反射涂层顶部的光刻胶层,或者,所述遮挡层包括旋涂氧化物(spin-on-oxide)层、以及位于所述旋涂氧化物层顶部的光刻胶层。其中,所述抗反射涂层的材料可以包括含硅的抗反射涂层(Si-ARC)材料,所述填充层的材料可以为旋涂碳(SOC)。

由前述记载可知,所述第二节距至少为所述第一节距的两倍,因此,所述掩膜开口210的开口尺寸较大,相邻掩膜开口210之间的距离也较大,这增大了形成所述掩膜开口210时所采用光刻工艺的工艺窗口。

本实施例中,采用刻蚀工艺,对所述沟道区10a的鳍部110侧壁进行减薄处理。

当所述刻蚀工艺对所述鳍部110和隔离层101的刻蚀选择比过小时,在所述减薄处理的过程中,容易损耗所述隔离层101,从而导致所述隔离层101的厚度减小、所述隔离层101的顶面平坦度降低,这不仅容易降低所述隔离层101的电隔离效果,还影响所述沟道区10a的鳍部110的有效高度,从而对半导体结构的性能产生不良影响。为此,本实施例中,所述刻蚀工艺对所述鳍部110和隔离层101的刻蚀选择比大于5:1。

其中,鳍部110的有效高度指的是:鳍部110中被栅极结构所覆盖的高度。

具体地,所述刻蚀工艺包括干法刻蚀工艺和湿法刻蚀工艺中的一种或两种。

需要说明的是,通过调节刻蚀参数,使得所述刻蚀工艺对所述鳍部110和隔离层101的刻蚀选择比能够满足工艺需求。而且,当采用干法刻蚀工艺时,通过调节刻蚀参数,能够调节纵向刻蚀速率和横向刻蚀速率的比值,从而对所述沟道区10a的鳍部110侧壁进行减薄处理。

还需要说明的是,对所述沟道区10a的鳍部110进行减薄处理的步骤中,所述鳍部110的单边减薄量d(如图12(a)所示)不宜过小,也不宜过大。如果所述鳍部110的单边减薄量d过小,则容易导致增大相邻沟道区10a的鳍部110之间的空间的效果不佳,从而导致增大后续在第二器件区100B中形成栅极结构的工艺窗口的效果不佳;如果所述鳍部110的单边减薄量d过大,则容易导致所述沟道区10a的有效鳍部的宽度过小,这不仅容易导致器件的电学性能发生偏移,还容易降低所述沟道区10a的有效鳍部的机械强度,增大所述沟道区10a的有效鳍部发生变形的概率。为此,本实施例中,在所述第二器件区100B中,对所述沟道区10a的鳍部110进行减薄处理的步骤中,所述鳍部110的单边减薄量d为1纳米至3纳米。例如,所述鳍部110的单边减薄量d为1.5纳米、2纳米或2.5纳米。其中,露出于所述隔离层101的鳍部作为有效鳍部。

本实施例中,对所述沟道区10a的鳍部110进行减薄处理后,还包括去除所述遮挡层200,从而为后续制程做准备。

需要说明的是,相比于所述鳍部110的高度,所述鳍部110的单边减薄量d较小,因此,在所述减薄处理的过程中,即使因所述鳍部110顶部被暴露在所述减薄处理的环境中而导致所述鳍部110的高度减小,所述鳍部110的高度减小量也较小,所述鳍部110的高度减小量对器件性能产生的影响较小。

在其他实施例中,当所述鳍部的顶部形成有鳍部掩膜层时,在所述减薄处理的过程中,所述鳍部掩膜层能够对所述鳍部顶部起到保护作用,从而有利于降低对所述鳍部的高度的影响。相应的,在该实施例中,对所述沟道区的鳍部进行减薄处理后,还包括去除所述鳍部掩膜层,从而为后续制程做准备。

参考图13至图19,图13(a)为第一器件区的俯视图,图13(b)为图13(a)沿AA1方向的剖视图,图14为第二器件区的俯视图,图15(a)为图14沿BB1方向的剖视图,图15(b)为图14沿CC1方向的剖视图,图16为第一器件区的俯视图,图17(a)为图16沿AA1方向的剖视图,图17(b)为图16沿DD1方向的剖视图,图18为第二器件区的俯视图,图19(a)为图18沿BB1方向的剖视图,图19(b)为图18沿CC1方向的剖视图,对所述沟道区10a的鳍部110进行减薄处理后,在所述基底上形成伪栅结构320,所述伪栅结构320横跨所述沟道区10a的鳍部110,并覆盖所述沟道区10a的鳍部110的部分顶部和部分侧壁,所述伪栅结构320包括栅氧化层300、以及覆盖所述栅氧化层300的伪栅层310。

以下结合附图,对形成所述伪栅结构320的步骤做详细说明。

结合参考图13至图15,在所述隔离层101露出的鳍部110表面形成栅氧化层300。

所述栅氧化层300用于作为第二器件区的100B的栅介质层的一部分。此外,后续去除伪栅层310时,所述栅氧化层300能够起到刻蚀停止层的作用,从而减小对鳍部110的损伤。

与先在去除伪栅层以形成栅极开口,再通过栅极开口进行减薄处理的方案相比,本实施例中,在形成栅氧化层300之前,对于所述第二器件区100B,已对所述沟道区10a的鳍部110进行减薄处理,因此,后续无需再去除所述第二器件区100B的栅氧化层300,从而简化了工艺步骤,降低了所述第二器件区100B的鳍部110受损的概率,而且,与目前工艺制程的兼容性高。

本实施例中,采用原位蒸汽生成(in-situ stream generation,ISSG)氧化工艺,在所述鳍部110表面形成栅氧化层300,从而有利于提高所述栅氧化层300的致密度和厚度均一性。

本实施例中,所述鳍部110的材料为硅,所述栅氧化层300由对所述鳍部110进行氧化所形成,所述栅氧化层300的材料相应为氧化硅。

如图15所示,在所述第二器件区100B中,在形成栅氧化层300后,相比于未经历减薄处理的鳍部110,经历所述减薄处理的鳍部110之间的剩余空间更大,而后续栅极结构还会形成在相邻鳍部110之间,因此,后续在所述第二器件区100B中形成栅极结构的工艺窗口更大。

本实施例中,部分高度的鳍部110作为底部鳍部,剩余高度的鳍部110作为有效鳍部,所述隔离层101覆盖底部鳍部的侧壁,并露出有效鳍部。其中,在所述第二器件区100B中,所述栅氧化层300覆盖有效鳍部露出的底部鳍部的顶部,从而减小底部鳍部对器件性能的影响。

结合参考图16至图19,在所述栅氧化层300上形成横跨所述沟道区10a的鳍部110的伪栅层310。

所述伪栅层310用于为后续形成栅极结构占据空间位置,所述伪栅层310和栅氧化层300构成伪栅结构320。

本实施例中,所述伪栅层310的材料为无定形硅。无定形硅易于被去除,且去除无定形硅的工艺对所述隔离层101的损耗较小。在其他实施例中,所述伪栅层的材料还可以为多晶硅或无定形碳等其他适用的材料。

本实施例中,通过刻蚀工艺对所述伪栅层310所对应的材料层进行图形化,以形成所述伪栅层310。

作为一种示例,通过刻蚀工艺对所述伪栅层310所对应的材料层进行图形化后,保留所述伪栅层310露出的栅氧化层300。

本实施例中,沿所述鳍部110的延伸方向,所述第二器件区100B的伪栅层310宽度大于所述第一器件区100A的伪栅层310宽度。

参考图20至图23,图20为第一器件区的俯视图,图21(a)为图20沿AA1方向的剖视图,图21(b)为图20沿DD1方向的剖视图,图22为第二器件区的俯视图,图23(a)为图22沿BB1方向的剖视图,图23(b)为图22沿CC1方向的剖视图,在所述伪栅层310两侧的鳍部110中形成源漏掺杂层330。

所述源漏掺杂层330用于作为所形成晶体管的源区或漏区。

具体地,刻蚀所述伪栅层310两侧的鳍部110,在所述鳍部110中形成凹槽后,通过外延工艺,在所述凹槽中形成所述源漏掺杂层330。

所述源漏掺杂层330的掺杂类型与相对应的晶体管的沟道导电类型相同。当晶体管为PMOS晶体管时,源漏掺杂层330的材料包括掺杂有P型离子的锗化硅,P型离子包括B、Ga或In。当晶体管为NMOS晶体管时,源漏掺杂层330的材料包括掺杂有N型离子的硅或碳化硅,N型离子包括P、As或Sb。

需要说明的是,在形成所述源漏掺杂层330之前,所述形成方法还包括:在所述伪栅层310的侧壁形成侧墙(图未示)。

所述侧墙用于保护所述伪栅层310的侧壁、以及后续形成的栅极结构的侧壁,还用于定义源漏掺杂层330的形成位置。对所述侧墙的描述,在此不再赘述。

还需要说明的是,根据工艺需求,在形成所述侧墙后,可以去除所述侧墙露出的栅氧化层300,也可以保留所述侧墙露出的栅氧化层300。相应的,当保留所述侧墙露出的栅氧化层300时,刻蚀所述伪栅层310两侧的鳍部110,在所述鳍部110中形成凹槽的步骤中,还刻蚀所述伪栅层310两侧的栅氧化层300。

参考图24至图25,图24(a)为第一器件区的俯视图,图24(b)为图24(a)沿AA1方向的剖视图,图25(a)为第二器件区的俯视图,图25(b)为图25(a)沿CC1方向的剖视图,在所述衬底100上形成覆盖所述源漏掺杂层330的层间介质层102,所述层间介质层102覆盖所述伪栅层310的侧壁并露出所述伪栅层310的顶部。

所述层间介质层102用于实现相邻器件之间的电隔离,所述层间介质层102还用于定义后续所形成的栅极结构的尺寸和位置。

所述层间介质层102的材料为绝缘材料。本实施例中,所述层间介质层102的材料为氧化硅。在其他实施例中,所述层间介质层的材料还可以为氮化硅或氮氧化硅等其他介质材料。

具体地,形成覆盖所述伪栅层310的层间介质材料层后,对所述层间介质材料层进行平坦化处理(例如,化学机械研磨处理),直至露出所述伪栅层310的顶部,剩余的层间介质材料层作为间介质层102。

参考图26至图33,图26为第一器件区的俯视图,图27(a)为图26沿AA1方向的剖视图,图27(b)为图26沿DD1方向的剖视图,图28为第二器件区的俯视图,图29(a)为图28沿BB1方向的剖视图,图29(b)为图28沿CC1方向的剖视图,图30为第一器件区的俯视图,图31(a)为图30沿AA1方向的剖视图,图31(b)为图30沿DD1方向的剖视图,图32为第二器件区的俯视图,图33(a)为图32沿BB1方向的剖视图,图33(b)为图32沿CC1方向的剖视图,去除所述第一器件区100A的伪栅结构320、以及所述第二器件区100B的伪栅层310,在所述层间介质层102中形成栅极开口350。

所述栅极开口350用于为后续形成栅极结构提供空间位置。

结合参考图26至图29,去除所述第一器件区100A和第二器件区100B的伪栅层310,在所述层间介质层102中形成栅极开口350。

具体地,可以采用干法刻蚀工艺和湿法刻蚀工艺中的一种或两种,去除所述伪栅层310。其中,在去除所述伪栅层310的过程中,以所述栅氧化层300的顶部作为刻蚀停止位置,从而减小对栅极开口350中的鳍部110的损伤。

结合参考图30至图33,去除所述伪栅层310后,去除所述第一器件区100A的栅极开口350露出的栅氧化层300,露出所述沟道区10a的鳍部110表面。

由前述记载可知,器件的工作电压越大,相对应的栅介质层厚度越大,所述第一器件区100A的器件工作电压小于所述第二器件区100B的器件工作电压,因此,通过去除所述第一器件区100A的栅氧化层300,以便后续在所述第二器件区100B形成厚度更小的栅介质层。

具体地,以前述进行减薄处理时采用的遮挡层200(如图8至图10所示)为第一遮挡层为例,去除所述第一器件区100A的栅极开口350露出的栅氧化层300的步骤包括:在所述第二器件区100B中形成第二遮挡层340,所述第二遮挡层340覆盖层间介质层102,并填充于栅极开口350中;以第二遮挡层340为掩膜,刻蚀去除所述第一器件区100A的栅极开口350中的栅氧化层300;去除所述第二遮挡层340。

所述第二遮挡层340可以选取任意能够适用于作为掩膜的材料。作为一种示例,所述第二遮挡层340的材料为光刻胶。

作为一种示例,可以采用干法刻蚀工艺,去除所述第一器件区100A的栅极开口350露出的栅氧化层300,从而提高去除所述栅氧化层300后的栅极开口350的侧壁平整度。

参考图34至图37,图34为第一器件区的俯视图,图35(a)为图34沿AA1方向的剖视图,图35(b)为图34沿DD1方向的剖视图,图36为第二器件区的俯视图,图37(a)为图36沿BB1方向的剖视图,图37(b)为图36沿CC1方向的剖视图,在所述栅极开口350中形成栅极结构450。

所述栅极结构450、以及位于所述栅极结构450下方的栅氧化层300共同用于控制沟道的开启或关断。

本实施例中,所述栅极结构450为金属栅极结构。因此,所述栅极结构450包括高k栅介质层410、以及覆盖所述高k栅介质层410的栅电极层400。

在所述第一器件区100A中,所述高k栅介质层410用于作为栅介质层,在所述第二器件区100B中,所述高k栅介质层410和栅氧化层300共同作为栅介质层,因此,所述第二器件区100B的栅介质层厚度大于所述第一器件区100A的栅介质层厚度。

所述栅介质层用于隔离所述栅电极层400和沟道。

所述高k栅介质层410的材料为高k介质材料,其中,高k介质材料是指相对介电常数大于氧化硅相对介电常数的介电材料。具体地,所述高k栅介质层410的材料可以选自HfO

所述栅电极层400用于将栅极结构450的电性引出。所述栅电极层400的材料包括TiN、TaN、Ta、Ti、TiAl、W、Al、TiSiN和TiAlC中的一种或多种。

由前述记载可知,在所述第二器件区100B的栅极开口350中,所述鳍部110之间的剩余空间更大,从而增大了形成所述栅电极层400的工艺窗口,进而提高了所述栅电极层400在相邻所述鳍部110之间的覆盖能力或填充能力。

作为一种示例,所述栅电极层400包括功函数层以及覆盖功函数层的电极层。在其他实施例中,所述栅电极层也可以仅包括功函数层。其中,功函数层用于调节所形成晶体管的工作电压。可以理解的是,根据不同器件区的晶体管的性能需求,各器件区的功函数层的材料、厚度和膜层层数可以不相同。

需要说明的是,本实施例以第一器件区100A的栅介质层仅包括高k栅介质层410为例,而所述第二器件区100B的栅介质层包括栅氧化层300、以及覆盖栅氧化层300的高k栅介质层410,因此,所述第二器件区100B的栅介质层厚度大于所述第一器件区100A的栅介质层厚度,以满足所述第一器件区100A和第二器件区100B的器件工作电压的不同需求。

还需要说明的是,以所述第二器件区的栅极开口露出的栅氧化层作为第一栅氧化层为例,在其他实施例中,在形成高k栅介质层之前,还可以包括:在所述第一器件区中,在所述栅极开口露出的鳍部表面形成第二栅氧化层。其中,由于所述第一器件区的器件工作电压小于所述第二器件区的器件工作电压,因此,所述第二栅氧化层厚度小于所述第一栅氧化层厚度。

虽然本发明披露如上,但本发明并非限定于此。任何本领域技术人员,在不脱离本发明的精神和范围内,均可作各种更动与修改,因此本发明的保护范围应当以权利要求所限定的范围为准。