一种可抵御多种故障注入的全数字传感器

文献发布时间:2023-06-19 19:35:22

技术领域

本发明涉及传感器技术领域,具体是一种可抵御多种故障注入的全数字传感器。

背景技术

在信息安全领域,故障注入是一种常用的攻击手段。攻击者通过对芯片施加时钟毛刺、提高时钟频率、施加电压毛刺、降低供电电压、加热、电磁干扰、激光注入等物理手段导致关键路径失效,从而导致信息泄露。为了抵御这种攻击,芯片内部需要内置各种传感器来侦测这种攻击,模拟传感器的局限在于,只能侦测其中一种或少数几种攻击方式。

发明内容

本发明的目的在于提供一种可抵御多种故障注入的全数字传感器,以解决上述背景技术中提出的问题。

为实现上述目的,本发明提供如下技术方案:

一种可抵御多种故障注入的全数字传感器,包含由多个延迟单元级联构成的总延迟线,所述总延迟线分为一长一短的两个延迟线,长延时线的信号输入端连接时钟信号clock,长延时线的信号输出端连接短延迟线。

作为本发明的进一步技术方案:所述延迟单元为可编程延时单元。

作为本发明的进一步技术方案:所述延迟单元包括反相器A1、异或门U1、异或门U2和异或门U3。

作为本发明的进一步技术方案:所述反相器A1的输入端连接编程信号TR和异或门U2的一个输入端,反相器A1的输出端连接异或门U1的一个输入端,异或门U1的另一个输入端连接异或门U2的另一个输入端和信号IN,异或门U2的输出端连接异或门U3的一个输入端,异或门U1的输出端输出信号PASS,异或门U3的另一个输入端连接信号ret,异或门U3的输出端输出信号out。

作为本发明的进一步技术方案:当延迟单元为长延时线的第一级时,信号IN为时钟信号clock,信号out连接短延迟线的输入端并输出延迟输出时钟C到D触发器,信号ret为后一级延迟单元中异或门U3的输出端输出信号out,信号PASS作为后一级延迟单元的信号IN;

当延迟单元为长延时线的中间级时,输入信号IN为上一级延迟单元中异或门U1的输出端输出信号PASS,信号PASS作为后一级延迟单元的信号IN;信号ret为后一级延迟单元的信号out,信号out作为上一级延时单元的信号ret;

当延迟单元为长延时线的最后一级时,输入信号IN为上一级延迟单元中异或门U1的输出端输出信号PASS,信号PASS作为本级延迟单元的信号ret;信号out作为上一级延时单元的信号ret。

作为本发明的进一步技术方案:当延迟单元为短延时线的第一级时,信号IN为长延时线输出信号,信号out输出时钟信号D到D触发器,信号ret为后一级延迟单元中异或门U3的输出端输出信号out,信号PASS作为后一级延迟单元的信号IN;

当延迟单元为短延时线的中间级时,输入信号IN为上一级延迟单元中异或门U1的输出端输出信号PASS,信号PASS作为后一级延迟单元的信号IN;信号ret为后一级延迟单元的信号out,信号out作为上一级延时单元的信号ret;

当延迟单元为短延时线的最后一级时,输入信号IN为上一级延迟单元中异或门U1的输出端输出信号PASS,信号PASS作为本级延迟单元的信号ret;信号out作为上一级延时单元的信号ret。

一种全数字传感器抵御多种故障注入的方法,采用上述全数字传感器,具体方法如下:首先将时钟信号clock送入延迟线,通过对信号TR[n-1:0]进行编程,产生一个可编程延迟输出时钟C,延迟输出时钟C再送入短延迟线产生延迟时钟D,需要延迟输出时钟C的延迟大于芯片中最长路径的延迟A,而延迟时钟D的延迟小于时钟信号clock的时钟周期B,延迟输出时钟C和延迟时钟D对时钟信号clock进行采样,根据采样结果判断是否受到攻击。

与现有技术相比,本发明的有益效果是:本发明采用标准单元设计一个可扩展的全数字传感器,可抵御施加时钟毛刺、提高时钟频率、施加电压毛刺、降低供电电压、加热、电磁干扰、激光注入这些攻击手段,具有面积小,应用广等特性。

附图说明

图1是延迟单元的结构示意图;

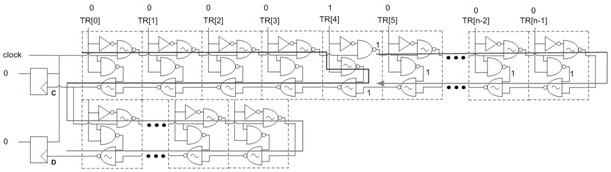

图2是本发明系统的整体结构示意图。

图3为时钟信号的波形图。

具体实施方式

下面将结合本发明实施例中的附图,对本发明实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例仅仅是本发明一部分实施例,而不是全部的实施例。基于本发明中的实施例,本领域普通技术人员在没有做出创造性劳动前提下所获得的所有其他实施例,都属于本发明保护的范围。

实施例1,请参阅图1-3,一种可抵御多种故障注入的全数字传感器,包含由多个延迟单元级联构成的总延迟线,所述总延迟线分为一长一短的两个延迟线,长延时线的信号输入端连接时钟信号clock,长延时线的信号输出端连接短延迟线。

其中,延迟单元为可编程延时单元。

如图1所示,延迟单元包括反相器A1、异或门U1、异或门U2和异或门U3。反相器A1的输入端连接编程信号TR和异或门U2的一个输入端,反相器A1的输出端连接异或门U1的一个输入端,异或门U1的另一个输入端连接异或门U2的另一个输入端和信号IN,异或门U2的输出端连接异或门U3的一个输入端,异或门U1的输出端输出信号PASS,异或门U3的另一个输入端连接信号ret,异或门U3的输出端输出信号out。

如图2所示,当延迟单元为长延时线的第一级时,信号IN为时钟信号clock,信号out连接短延迟线的输入端并输出延迟输出时钟C到D触发器,信号ret为后一级延迟单元中异或门U3的输出端输出信号out,信号PASS作为后一级延迟单元的信号IN;

当延迟单元为长延时线的中间级时,输入信号IN为上一级延迟单元中异或门U1的输出端输出信号PASS,信号PASS作为后一级延迟单元的信号IN;信号ret为后一级延迟单元的信号out,信号out作为上一级延时单元的信号ret;

当延迟单元为长延时线的最后一级时,输入信号IN为上一级延迟单元中异或门U1的输出端输出信号PASS,信号PASS作为本级延迟单元的信号ret;信号out作为上一级延时单元的信号ret。

当延迟单元为短延时线的第一级时,信号IN为长延时线输出信号,信号out输出时钟信号D到D触发器,信号ret为后一级延迟单元中异或门U3的输出端输出信号out,信号PASS作为后一级延迟单元的信号IN;

当延迟单元为短延时线的中间级时,输入信号IN为上一级延迟单元中异或门U1的输出端输出信号PASS,信号PASS作为后一级延迟单元的信号IN;信号ret为后一级延迟单元的信号out,信号out作为上一级延时单元的信号ret;

当延迟单元为短延时线的最后一级时,输入信号IN为上一级延迟单元中异或门U1的输出端输出信号PASS,信号PASS作为本级延迟单元的信号ret;信号out作为上一级延时单元的信号ret。

实施例2,在实施例1的基础上,本发明还公开了一种全数字传感器抵御多种故障注入的方法,采用实施例1中所述的全数字传感器,具体方法如下:首先将时钟信号clock送入延迟线,通过对信号TR[n-1:0]进行编程,产生一个可编程延迟输出时钟C,延迟输出时钟C再送入短延迟线产生延迟时钟D,需要延迟输出时钟C的延迟大于芯片中最长路径的延迟A,而延迟时钟D的延迟小于时钟信号clock的时钟周期B,延迟输出时钟C和延迟时钟D对时钟信号clock进行采样,根据采样结果判断是否受到攻击。

工作原理如下:首先通过对图2中TR[n-1:0]进行编程,产生一个可编程延迟输出时钟C,C再送入短延迟线产生延迟时钟D。保证C的延迟大于芯片中最长路径的延迟A的N倍,而D的延迟小于clock的时钟周期B的N倍。延迟时钟C,D对clock进行采样,根据采样结果判断是否受到攻击。

如图3所示,横轴箭头代表着时间轴,上边的粗刻度代表时间周期…Tj-1,Tj,Tj+1,Tj+2…,假设时钟周期为B,芯片的关键路径延迟为A。攻击者通过施加时钟毛刺,提高时钟频率,施加电压毛刺,降低供电电压,加热,电磁干扰,激光注入这些攻击手段,导致关键路径A的建立(setup)时间违例,电路失效,从而获取机密信息。

如图1所示构建基本延迟单元j0,如图2所示构建一长(上)一短(下)两条延迟线。长的延迟线可以通过TR进行编程(独热编码),短延迟线可采用固定级数延迟或者可编程延迟。关键路径A与周期B的差值(B-A)被称为裕量,这个裕量取决于实际电路的复杂程度,如果逻辑复杂,裕量往往很小,此时需要选择最小延迟的异或门来提高延迟单元的精度。

根据实际情况,对TR进行编程,保证延迟输出C的延迟大于A,且延迟输出D的延迟小于时钟周期B。延迟时钟C,D分别送入两个D触发器,对clock进行采样。根据图3,可以看出C,D采样值都是0。一旦芯片受到施加时钟毛刺,提高时钟频率,施加电压毛刺,降低供电电压,加热,电磁干扰,激光注入这些攻击。C,D两个都采样到0的状态随即被打破,从而能够侦测到攻击,进行报警。

对于本领域技术人员而言,显然本发明不限于上述示范性实施例的细节,而且在不背离本发明的精神或基本特征的情况下,能够以其他的具体形式实现本发明。因此,无论从哪一点来看,均应将实施例看作是示范性的,而且是非限制性的,本发明的范围由所附权利要求而不是上述说明限定,因此旨在将落在权利要求的等同要件的含义和范围内的所有变化囊括在本发明内。不应将权利要求中的任何附图标记视为限制所涉及的权利要求。

此外,应当理解,虽然本说明书按照实施方式加以描述,但并非每个实施方式仅包含一个独立的技术方案,说明书的这种叙述方式仅仅是为清楚起见,本领域技术人员应当将说明书作为一个整体,各实施例中的技术方案也可以经适当组合,形成本领域技术人员可以理解的其他实施方式。

- 使用阵列传感器以传感器的全分辨率测量多种类型数据的方法

- 一种可实现多种类型传输的故障注入装置