非易失性SRAM单元及数据读写方法

文献发布时间:2024-01-17 01:27:33

技术领域

本发明涉及半导体器件技术领域,更为具体地,涉及一种非易失性SRAM单元及数据读写方法。

背景技术

易失性内存介质SRAM(静态随机存取存储器),存储的信息掉电即消失,通过将忆阻介质RRAM(阻变随机存储器)设计组合到一起,可赋予SRAM非易失的特性。

对于非易失性存储介质RRAM,存在写入次数受限的问题。将RRAM与内存介质SRAM设计组合到一起,可从RRAM导入数据到SRAM。在一般运行时使用SRAM进行操作,在需要记录数据,使其掉电不消失时,对RRAM进行操作。

目前,现有技术中,虽然已经存在将RRAM与SRAM进行相互组合的现有技术,但是,在现有技术中一般使用的是7T2R,8T2R等单元结构,虽然都是将RRAM的值导入SRAM,但是,现有技术使用的T/R数量较多,存在整体功耗和面积大等问题。

发明内容

鉴于上述问题,本发明的目的是提供一种非易失性SRAM单元及数据读写方法,以解决目前的现有技术中,使用的T/R数量较多,存在整体功耗和面积大等问题。

本发明提供一种非易失性SRAM单元,包括:

SRAM存储单元,所述SRAM存储单元包括第一反相器和第二反相器;所述第一反相器与所述第二反相器首尾连接构成锁存结构;

RRAM电路,所述RRAM电路包括第三MOS管、第四MOS管和ReRAM结构;其中,所述第三MOS管的非栅极的两端分别连接位线电压V

传输电路,所述传输电路基于电压负载,有选择性地将所述SRAM存储单元电耦合到所述RRAM电路。

此外,优选的方案是,所述传输电路包括第五MOS管,所述第五MOS管的非栅极的一端与所述第三MOS管的一端和所述ReRAM结构的一端连接;所述第五MOS管的非栅极的另一端与第二反相器数据节点连接;所述第五MOS管的栅极连接有导通电压V

此外,优选的方案是,所述第三MOS管为NMOS管或PMOS管;和/或,所述第四MOS管为NMOS管或PMOS管;和/或,所述第五MOS管为NMOS管或PMOS管。

此外,优选的方案是,所述第一反相器包括:第一PMOS管和第一NMOS管;和/或,所述第二反相器包括:第二PMOS管和第二NMOS管。

此外,优选的方案是,所述第一PMOS管连接有第一核心电压V

此外,优选的方案是,所述第三MOS管的栅极连接有导通电压V

此外,优选的方案是,所述第四MOS管的栅极连接有字线电压V

本发明提供一种基于如上所述的非易失性SRAM单元的数据读写方法,包括:

关闭所述传输电路,使所述锁存结构处于不工作状态,并通过控制所述第三MOS管和所述第四MOS管的开启,使所述RRAM电路依次进入编程阶段、擦除阶段和读取阶段;

其中,当所述RRAM电路的读取阶段结束后,开启所述传输电路,使所述锁存结构处于正常工作状态,通过依次控制所述第四MOS管和所述第三MOS管的关闭和开启;以及,在所述RRAM电路的读取阶段读取到的所述ReRAM结构的阻态后,对所述SRAM存储单元进行置位,使所述SRAM存储单元进入下载阶段;

当所述SRAM存储单元的下载阶段完成后,保持所述锁存结构所处的正常工作状态,关闭所述第四MOS管,并开启所述传输电路和所述第三MOS管,根据所述SRAM存储单元的写入情况,对电路的位线BL端的电平进行调整,使所述SRAM存储单元进入写入阶段。

此外,优选的方案是,在所述RRAM电路的编程阶段,关闭所述传输电路,使所述锁存结构处于不工作状态,开启所述第三MOS管和所述第四MOS管,使编程信号从所述位线BL端经所述ReRAM结构传输至电路的源线SL端;在所述RRAM电路的擦除阶段,关闭所述传输电路,使所述锁存结构处于不工作状态,开启所述第三MOS管和所述第四MOS管,使擦除信号从所述源线SL端经所述ReRAM结构传输至所述位线BL端;在所述RRAM电路的读取阶段,关闭所述传输电路,使所述锁存结构处于不工作状态,开启所述第三MOS管和所述第四MOS管,使检测信号从所述位线BL端经所述ReRAM结构传输至所述源线SL端,再从所述源线SL端检测所述ReRAM结构的存储状态。

此外,优选的方案是,在所述SRAM存储单元的下载阶段,开启所述传输电路和所述第三MOS管,关闭所述第四MOS管,使所述锁存结构处于正常工作状态,此时,所述锁存结构的第一反相器数据节点被编程为1,所述第二反相器数据节点被编程为0;

然后,关闭所述第三MOS管,开启所述第四MOS管,若所述ReRAM结构处于高阻状态,则所述锁存结构的第一反相器数据节点为0,所述第二反相器数据节点为1;若所述ReRAM结构处于低阻状态,则所述锁存结构的第二反相器数据节点被拉到0,所述第一反相器数据节点为1;

在所述SRAM存储单元的写入阶段,开启所述传输电路和所述第三MOS管,关闭所述第四MOS管,使所述锁存结构处于正常工作状态;其中,

若往所述SRAM存储单元中写1,则使所述位线BL端置高电平,将所述锁存结构的第一反相器数据节点置为0,所述第二反相器数据节点置为1;

若往所述SRAM存储单元中写0,则使所述位线BL端置低电平,将所述锁存结构的第二反相器数据节点置为0,所述第一反相器数据节点置为1。

从上面的技术方案可知,本发明提供的非易失性SRAM单元及数据读写方法,通过组合RRAM和SRAM,解决了RRAM写入次数受限以及SRAM存储的信息掉电即消失的问题;在从RRAM导入数据到SRAM后,从SRAM引线到MOS管(晶体管),作为MOS管的开关信号,可以此来完成数据信号的开关功能;与现有技术相比较,减少了基于RRAM的nvSRAM单元所用的晶体管数量,将RRAM削减到每个SRAM单元搭配一个RRAM,极大程度的减少了整体功耗和面积。

为了实现上述以及相关目的,本发明的一个或多个方面包括后面将详细说明的特征。下面的说明以及附图详细说明了本发明的某些示例性方面。然而,这些方面指示的仅仅是可使用本发明的原理的各种方式中的一些方式。此外,本发明旨在包括所有这些方面以及它们的等同物。

附图说明

通过参考以下结合附图的说明,并且随着对本发明的更全面理解,本发明的其它目的及结果将更加明白及易于理解。在附图中:

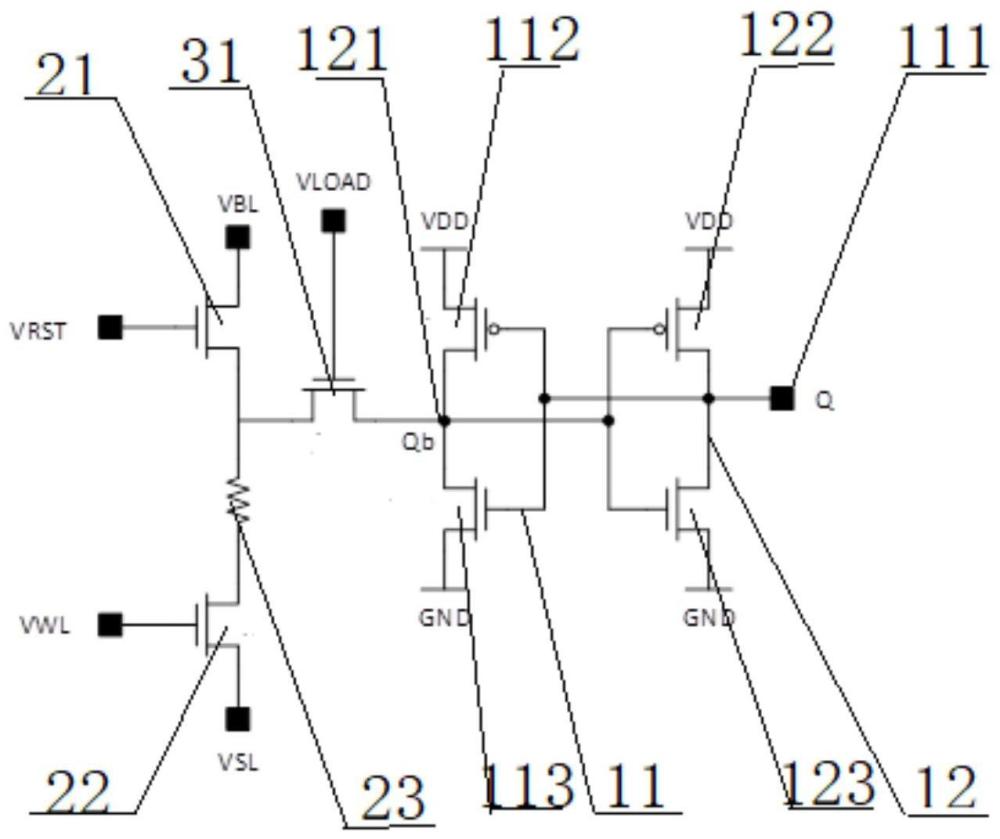

图1为根据本发明实施例的非易失性SRAM单元的结构示意图;

图2为根据本发明实施例的非易失性SRAM单元的数据读写方法的流程图。

在附图中,11-第一反相器,111-第一反相器数据节点,112-第一PMOS管,113-第一NMOS管,12-第二反相器,121-第二反相器数据节点,122-第二PMOS管,123-第二NMOS管,21-第三MOS管、22-第四MOS管,23-ReRAM结构,31-第五MOS管。

在所有附图中相同的标号指示相似或相应的特征或功能。

具体实施方式

在下面的描述中,出于说明的目的,为了提供对一个或多个实施例的全面理解,阐述了许多具体细节。然而,很明显,也可以在没有这些具体细节的情况下实现这些实施例。

针对前述提出的现有技术中,使用的T/R数量较多,存在整体功耗和面积大等问题,提出了一种非易失性SRAM单元及数据读写方法。

以下将结合附图对本发明的具体实施例进行详细描述。

为了说明本发明提供的非易失性SRAM单元及数据读写方法,图1示出了根据本发明实施例的非易失性SRAM单元的结构;图2示出了根据本发明实施例的非易失性SRAM单元的数据读写方法的流程。

如图1结合图2共同所示,本发明提供的非易失性SRAM单元,包括:

SRAM存储单元,SRAM存储单元包括第一反相器11和第二反相器12;第一反相器11与第二反相器12首尾连接构成锁存结构;

RRAM电路,RRAM电路包括第三MOS管21、第四MOS管22和ReRAM结构23;其中,第三MOS管21的非栅极的两端分别连接位线电压V

传输电路,传输电路基于电压负载,有选择性地将SRAM存储单元电耦合到RRAM电路。

为了更方便理解,在附图中,将第一反相器数据节点111标记为Q,第二反相器数据节点标记为Qb。

其中,位线电压V

通过组合RRAM和SRAM,解决了RRAM写入次数受限以及SRAM存储的信息掉电即消失的问题;在从RRAM导入数据到SRAM后,从SRAM引线到MOS管(晶体管),作为MOS管的开关信号,可以此来完成数据信号的开关功能;与现有技术相比较,减少了基于RRAM的nvSRAM单元所用的晶体管数量,将RRAM削减到每个SRAM单元搭配一个RRAM,极大程度的减少了整体功耗和面积。

作为本发明的一个优选实施例,传输电路包括第五MOS管31,第五MOS管31的非栅极的一端与第三MOS管21的一端和ReRAM结构23的一端连接;第五MOS管31的非栅极的另一端与第二反相器数据节点121连接;第五MOS管31的栅极连接有导通电压V

作为本发明的一个优选实施例,第三MOS管21为NMOS管或PMOS管;和/或,第四MOS管22为NMOS管或PMOS管;和/或,第五MOS管31为NMOS管或PMOS管。NMOS管和PMOS管的工作原理是相同的,仅仅是两个端的输入和输出相反,因此,第三MOS管21、第四MOS管22以及第五MOS管31可根据实际情况选取NMOS管和PMOS管。

例如,当第三MOS管21、第四MOS管22以及第五MOS管31均为NMOS管时,采用如图1的技术方案,第三MOS管21的漏极和源极分别连接位线电压V

作为本发明的一个优选实施例,第一反相器11包括:第一PMOS管112和第一NMOS管113;和/或,第二反相器12包括:第二PMOS管122和第二NMOS管123。反相器由一个PMOS管和一个NMOS管组成,用于将输入信号的相位反转180度。

作为本发明的一个优选实施例,第一PMOS管112连接有第一核心电压V

作为本发明的一个优选实施例,第三MOS管21的栅极连接有导通电压V

作为本发明的一个优选实施例,第四MOS管22的栅极连接有字线电压V

本发明提供的基于如上所述的非易失性SRAM单元的数据读写方法,包括:

S1、关闭传输电路,使锁存结构处于不工作状态,并通过控制第三MOS管21和第四MOS管22的开启,使RRAM电路依次进入编程阶段、擦除阶段和读取阶段;

S2、当RRAM电路的读取阶段结束后,开启传输电路,使锁存结构处于正常工作状态,通过依次控制第四MOS管22和第三MOS管21的关闭和开启;以及,在RRAM电路的读取阶段读取到的ReRAM结构23的阻态后,对SRAM存储单元进行置位,使SRAM存储单元进入下载阶段;

S3、当SRAM存储单元的下载阶段完成后,保持锁存结构所处的正常工作状态,关闭第四MOS管22,并开启传输电路和第三MOS管21,根据SRAM存储单元的写入情况,对电路的位线BL端的电平进行调整,使SRAM存储单元进入写入阶段。

具体的,当关闭第五MOS管31,使锁存结构不工作,通过第三MOS管21和第四MOS管22的开启,使RRAM电路依次进入编程阶段(RRAM Program)、擦除阶段(RRAM Erase)和读取阶段(RRAM Read);其中,当RRAM电路的读取阶段结束后,开启第五MOS管31,使锁存结构正常工作,通过依次控制第四MOS管22和第三MOS管21的关闭和开启,以及在RRAM电路的读取阶段读取到的ReRAM结构23的阻态,对SRAM存储单元进行置位,使SRAM存储单元进入下载阶段(SRAM Load);当SRAM存储单元的下载阶段完成后,保持锁存结构正常工作,关闭第四MOS管22,使第五MOS管31和第三MOS管21处于开启的状态,根据SRAM存储单元的写入情况,对电路的位线BL端的电平进行调整,使SRAM存储单元进入写入阶段(SRAM Write)。

作为本发明的一个优选实施例,在RRAM电路的编程阶段,关闭传输电路,使锁存结构处于不工作状态,开启第三MOS管21和第四MOS管22,使编程信号从位线BL端经ReRAM结构23传输至电路的源线SL端;在RRAM电路的擦除阶段,关闭传输电路,使锁存结构处于不工作状态,开启第三MOS管31和第四MOS管22,使擦除信号从源线SL端经ReRAM结构23传输至位线BL端;在RRAM电路的读取阶段,关闭传输电路,使锁存结构处于不工作状态,开启第三MOS管21和第四MOS管22,使检测信号从位线BL端经ReRAM结构23传输至源线SL端,再从源线SL端检测ReRAM结构23的存储状态。

作为本发明的一个优选实施例,在SRAM存储单元的下载阶段,开启传输电路和第三MOS管21,关闭第四MOS管22,使锁存结构处于正常工作状态,此时,锁存结构的第一反相器数据节点111被编程为1,第二反相器数据节点121被编程为0;

然后,关闭第三MOS管21,开启第四MOS管22,若ReRAM结构23处于高阻状态,则锁存结构的第一反相器数据节点111为0,第二反相器数据节点121为1;若ReRAM结构23处于低阻状态,则锁存结构的第二反相器数据节点121被拉到0,第一反相器数据节111点为1;

在SRAM存储单元的写入阶段,开启传输电路和第三MOS管21,关闭第四MOS管22,使锁存结构处于正常工作状态;其中,

若往SRAM存储单元中写1,则使位线BL端置高电平,将锁存结构的第一反相器数据节点111置为0,第二反相器数据节点121置为1;

若往SRAM存储单元中写0,则使位线BL端置低电平,将锁存结构的第二反相器数据节点121置为0,第一反相器数据节点111置为1。

具体的,SRAM存储单元的下载阶段的流程包括:开启第五MOS管31和第三MOS管21,关闭第四MOS管22,使锁存结构正常工作,使电路中的电流从位线BL端流经第三NMOS管21和第五NMOS管31,并通过第一反相器11的第一MOS管112,此时,锁存结构的第一反相器数据节点111被编程为1,第二反相器数据节点121被编程为0;关闭第三MOS管21,开启第四MOS管22,此时,电路中的电流从第一反相器数据节点111,流经第五MOS管31,若ReRAM结构23处于高阻状态,则电流几乎无法通过ReRAM结构23和第四MOS管22,此时锁存结构的第一反相器数据节点111为0,第二反相器数据节点121为1;若ReRAM结构23处于低阻状态,则电路中的电流通过ReRAM结构23和第四MOS管22流到源线SL端,锁存结构的第二反相器1数据节点121被拉到0,第一反相器数据节点111,即Q端为1;SRAM存储单元的写入阶段的流程包括:开启第五MOS管31和第三MOS管21,关闭第四MOS管22,使锁存结构正常工作;若往SRAM存储单元中写1,则使位线BL端置高电平,电路中的电流通过位线BL端流经第三MOS管21和第五MOS管31,将锁存结构的第一反相器数据节点111,即Qb置为0,第二反相器数据节点121即Q置为1;若往SRAM存储单元中写0,则使位线BL端置为低电平,电路中的电流从锁存结构的第二反相器数据节点121流经第五MOS管31和第三MOS管21到达位线BL端,将锁存结构的第二反相器数据节点121置为0,第一反相器数据节点111置为1。

通过上述具体实施方式可看出,本发明提供的非易失性SRAM单元及数据读写方法,通过组合RRAM和SRAM,解决了RRAM写入次数受限以及SRAM存储的信息掉电即消失的问题;在从RRAM导入数据到SRAM后,从SRAM引线到MOS管(晶体管),作为MOS管的开关信号,可以此来完成数据信号的开关功能;与现有技术相比较,减少了基于RRAM的nvSRAM单元所用的晶体管数量,将RRAM削减到每个SRAM单元搭配一个RRAM,极大程度的的减少了整体功耗和面积

如上参照附图以示例的方式描述了根据本发明提出的非易失性SRAM单元及数据读写方法。但是,本领域技术人员应当理解,对于上述本发明所提出的非易失性SRAM单元及数据读写方法,还可以在不脱离本发明内容的基础上做出各种改进。因此,本发明的保护范围应当由所附的权利要求书的内容确定。

- 非易失性SRAM数据加密装置

- 一种SRAM位元与非易失性存储位元组成的复合阵列模块及其读写控制方法

- 具有多个非易失性半导体存储单元的存储装置及其用于在具有较高残留寿命长度的存储单元中放置热数据而在具有较低残留寿命长度的存储单元中放置冷数据的控制方法